Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc806-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

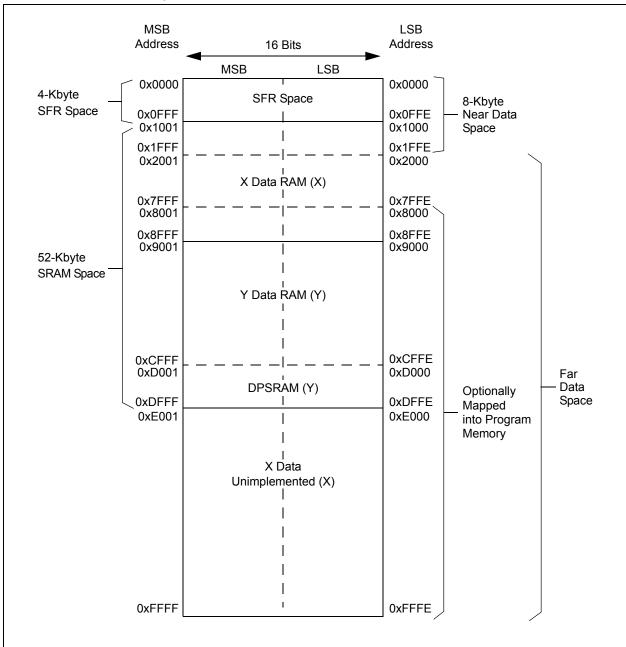

# FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33EP512(GP/MC/MU)806/810/814 DEVICES WITH 52-KBYTE RAM

#### 4.2.5 X AND Y DATA SPACES

The dsPIC33EPXXX(GP/MC/MU)806/810/814 core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The PIC24EPXXX(GP/GU)806/810/814 devices do not have a Y data space and a Y AGU. For these devices, the entire data space is treated as X data space.

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXX(GP/ GU)806/810/814 devices.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

#### 4.2.6 DMA RAM

Each dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 device contains 4 Kbytes of dual ported DMA RAM located at the end of Y data RAM and is part of Y data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA Controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU. When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

| Note 1: | DMA    | RAM     | can     | be   | used     | for  | general  |

|---------|--------|---------|---------|------|----------|------|----------|

|         | purpo  | se data | a stor  | age  | if the D | DMA  | function |

|         | is not | require | ed in a | an a | pplicat  | ion. |          |

2: On PIC24EPXXX(GP/GU)806/810/814 devices, DMA RAM is located at the end of X data RAM and is part of X data space.

## 4.3 Program Memory Resources

Many useful resources related to the Program Memory are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en554310                                        |

#### 4.3.1 KEY RESOURCES

- Section 4. "Program Memory" (DS70612) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

## 4.4 Special Function Register Maps

Table 4-1 through Table 4-72 provide mapping tables for all Special Function Registers (SFRs).

| TABLE        | 4-7:  | INIE   | RRUP   | CONT       | ROLLER  | REGIST  |        | FOR a       | SPIC33 | EPXXXGF  | '806 AN      | D PIC24     | PXXXG   | P806 DE   | VICES (     |             |        | JED)          |

|--------------|-------|--------|--------|------------|---------|---------|--------|-------------|--------|----------|--------------|-------------|---------|-----------|-------------|-------------|--------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9       | Bit 8  | Bit 7    | Bit 6        | Bit 5       | Bit 4   | Bit 3     | Bit 2       | Bit 1       | Bit 0  | All<br>Resets |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | )>      | _       |        | U2EIP<2:0   | >      | —        |              | U1EIP<2:0>  | •       | —         | -           | —           |        | 4440          |

| IPC17        | 0862  | _      | (      | C2TXIP<2:0 | )>      | _       | (      | C1TXIP<2:0  | >      | _        |              | DMA7IP<2:0  | >       | _         | C           | MA6IP<2:0   | >      | 4444          |

| IPC18        | 0864  | _      | _      | _          | _       | _       |        | _           | _      | _        | F            | SESMIP<2:   | 0>      | _         | _           | _           | _      | 4040          |

| IPC20        | 0868  | _      | l      | U3TXIP<2:0 | )>      | _       | ι      | J3RXIP<2:0  | >      | _        |              | U3EIP<2:0>  | •       | _         | _           | _           | _      | 4440          |

| IPC21        | 086A  | _      |        | U4EIP<2:0  | >       | _       |        | _           | _      | _        | _            | _           | _       | _         | _           | _           | _      | 4400          |

| IPC22        | 086C  | _      |        | SPI3IP<2:0 | >       | _       | 5      | SPI3EIP<2:0 | )>     | _        |              | U4TXIP<2:0  | >       | _         | ι           | J4RXIP<2:0> | >      | 4444          |

| IPC23        | 086E  | _      | _      | _          | _       | _       |        | _           | _      | _        |              | IC9IP<2:0>  |         | _         |             | C9IP<2:0>   |        | 4444          |

| IPC24        | 0870  | _      | _      | _          | _       | _       |        | _           | _      | _        | _            | _           | _       | _         | _           | _           | _      | 0044          |

| IPC29        | 087A  | _      | [      | DMA9IP<2:  | 0>      | _       | [      | DMA8IP<2:0  | )>     | _        | _            | _           | _       | _         | _           | _           | _      | 4400          |

| IPC30        | 087C  | _      |        | SPI4IP<2:0 | >       | _       | 5      | SPI4EIP<2:0 | )>     | _        | DMA11IP<2:0> |             |         | _         | D           | MA10IP<2:0  | >      | 4444          |

| IPC31        | 087E  | _      |        | IC11IP<2:0 | >       | _       | (      | C111P<2:0   | >      | _        |              | IC10IP<2:0> | >       | _         | OC10IP<2:0> |             | >      | 4444          |

| IPC32        | 0880  | _      | D      | MA13IP<2   | :0>     | _       | D      | MA12IP<2:   | 0>     | _        |              | IC12IP<2:0> | >       | _         | 0           | OC12IP<2:0> |        | 4444          |

| IPC33        | 0882  | _      |        | IC13IP<2:0 | >       | _       | (      | DC13IP<2:0  | >      | _        | _            | _           | _       | _         | D           | MA14IP<2:0  | >      | 4404          |

| IPC34        | 0884  | _      |        | IC15IP<2:0 | >       | _       | (      | DC15IP<2:0  | >      | _        |              | IC14IP<2:0> | >       | _         | 0           | 0C14IP<2:0> | >      | 4444          |

| IPC35        | 0886  | _      | _      | _          | _       | _       |        | ICDIP<2:0>  | •      | _        |              | IC16IP<2:0> | >       | _         | 0           | 0C16IP<2:0> | >      | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE       | COVTE  | SFTACERR | DIV0ERR      | DMACERR     | MATHERR | ADDRERR   | STKERR      | OSCFAIL     | —      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | _       | _      | —           | —      | -        | —            | —           | INT4EP  | INT3EP    | INT2EP      | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | _          | —       | _       | _      | —           | -      | —        | UAE          | DAE         | DOOVR   | _         | —           | _           | —      | 0000          |

| INTCON4      | 08C6  | _      | —      | _          | _       | _       | _      |             |        | —        |              | —           | _       | _         | —           |             | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | —      | —          | _       | _       |        | ILR         | <3:0>  |          |              |             | VE      | CNUM<7:0> |             |             |        | 0000          |

|              |       |        |        |            |         |         |        |             |        |          |              |             |         |           |             |             |        |               |

#### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXGP806 AND PIC24EPXXXGP806 DEVICES ONLY (CONTINUED)

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name | Addr. | Bit 15             | Bit 14            | Bit 13   | Bit 12                                                                                                       | Bit 11     | Bit 10 | Bit 9   | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Reset |

|-----------|-------|--------------------|-------------------|----------|--------------------------------------------------------------------------------------------------------------|------------|--------|---------|-------------|--------|--------|------------|--------|--------|-------|-------|-------|--------------|

| QEI1CON   | 01C0  | QEIEN              | _                 | QEISIDL  |                                                                                                              | PIMOD<2:0> |        | IMV<    | <1:0>       | _      |        | INTDIV<2:0 | >      | CNTPOL | GATEN | CCM   | <1:0> | 0000         |

| QEI1IOC   | 01C2  | QCAPEN             | FLTREN            |          | QFDIV<2:0>                                                                                                   |            | OUTFN  | VC<1:0> | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL | HOME   | INDEX | QEB   | QEA   | 000x         |

| QEI1STAT  | 01C4  | _                  | —                 | PCHEQIRQ | R PCHEQIEN PCLEQIRQ PCLEQIEN POSOVIRQ POSOVIEN PCIIRQ PCIIEN VELOVIRQ VELOVIEN HOMIRQ HOMIEN IDXIRQ IDXIEN ( |            |        |         |             |        |        |            | 0000   |        |       |       |       |              |

| POS1CNTL  | 01C6  |                    | POSCNT<15:0> 000  |          |                                                                                                              |            |        |         |             |        |        | 0000       |        |        |       |       |       |              |

| POS1CNTH  | 01C8  |                    | POSCNT<31:16> 00  |          |                                                                                                              |            |        |         |             |        |        |            |        | 0000   |       |       |       |              |

| POS1HLD   | 01CA  |                    |                   |          |                                                                                                              |            |        |         | POSHLD<15   | :0>    |        |            |        |        |       |       |       | 0000         |

| VEL1CNT   | 01CC  |                    |                   |          |                                                                                                              |            |        |         | VELCNT<15   | 0>     |        |            |        |        |       |       |       | 0000         |

| INT1TMRL  | 01CE  |                    |                   |          |                                                                                                              |            |        |         | INTTMR<15:  | 0>     |        |            |        |        |       |       |       | 0000         |

| INT1TMRH  | 01D0  |                    |                   |          |                                                                                                              |            |        |         | INTTMR<31:  | 16>    |        |            |        |        |       |       |       | 0000         |

| INT1HLDL  | 01D2  |                    |                   |          |                                                                                                              |            |        |         | INTHLD<15:  | 0>     |        |            |        |        |       |       |       | 0000         |

| INT1HLDH  | 01D4  |                    |                   |          |                                                                                                              |            |        |         | INTHLD<31:1 | 6>     |        |            |        |        |       |       |       | 0000         |

| INDX1CNTL | 01D6  |                    |                   |          |                                                                                                              |            |        |         | INDXCNT<15  | :0>    |        |            |        |        |       |       |       | 0000         |

| INDX1CNTH | 01D8  |                    |                   |          |                                                                                                              |            |        | I       | NDXCNT<31:  | 16>    |        |            |        |        |       |       |       | 0000         |

| INDX1HLD  | 01DA  |                    |                   |          |                                                                                                              |            |        |         | INDXHLD<15  | :0>    |        |            |        |        |       |       |       | 0000         |

| QEI1GECL  | 01DC  |                    |                   |          |                                                                                                              |            |        |         | QEIGEC<15   | 0>     |        |            |        |        |       |       |       | 0000         |

| QEI1ICL   | 01DC  |                    |                   |          |                                                                                                              |            |        |         | QEIIC<15:0  | >      |        |            |        |        |       |       |       | 0000         |

| QEI1GECH  | 01DE  |                    |                   |          |                                                                                                              |            |        |         | QEIGEC<31:  | 16>    |        |            |        |        |       |       |       | 0000         |

| QEI1ICH   | 01DE  |                    | QEIIC<31:16> 0000 |          |                                                                                                              |            |        |         |             |        |        |            |        |        |       |       |       |              |

| QEI1LECL  | 01E0  | QEILEC<15:0> 0000  |                   |          |                                                                                                              |            |        |         |             |        |        |            |        |        |       |       |       |              |

| QEI1LECH  | 01E2  | QEILEC<31:16> 0000 |                   |          |                                                                                                              |            |        |         |             |        |        |            |        |        |       |       |       |              |

#### TABLE 4-20: QEI1 REGISTER MAP FOR dsPIC33EPXXX(MC/MU)806/810/814 DEVICES ONLY

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|                | • · . | ••••••                              | .,     | -, 0/    |        |        |        |       |          |                                                 |          |       |              | -        | _     |        |       |               |

|----------------|-------|-------------------------------------|--------|----------|--------|--------|--------|-------|----------|-------------------------------------------------|----------|-------|--------------|----------|-------|--------|-------|---------------|

| File Name      | Addr. | Bit 15                              | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7                                           | Bit 6    | Bit 5 | Bit 4        | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE         | 0220  | UARTEN                              | _      | USIDL    | IREN   | RTSMD  | _      | UEN<  | <1:0>    | D> WAKE LPBACK ABAUD URXINV BRGH PDSEL<1:0> STS |          |       |              | STSEL    | 0000  |        |       |               |

| U1STA          | 0222  | UTXISEL1                            | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS                                           | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG        | 0224  | _                                   | _      | _        | _      | —      | _      | _     |          | UARTx Transmit Register                         |          |       |              |          |       | XXXX   |       |               |

| U1RXREG        | 0226  | _                                   | _      | _        |        | —      | _      | —     |          |                                                 |          | UART  | xReceive R   | egister  |       |        |       | 0000          |

| U1BRG          | 0228  |                                     |        |          |        |        |        | Baud  | Rate Gen | erator Pres                                     | scaler   |       |              |          |       |        |       | 0000          |

| U2MODE         | 0230  | UARTEN                              |        | USIDL    | IREN   | RTSMD  | —      | UEN<  | <1:0>    | WAKE                                            | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA          | 0232  | UTXISEL1                            | UTXINV | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS                                           | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG        | 0234  | —                                   |        |          |        | —      | —      | —     |          |                                                 |          | UART  | k Transmit F | Register |       |        |       | XXXX          |

| U2RXREG        | 0236  | _                                   |        |          |        | —      | _      | _     |          |                                                 |          | UART  | x Receive R  | Register |       |        |       | 0000          |

| U2BRG          | 0238  |                                     |        |          |        |        |        | Baud  | Rate Gen | erator Pres                                     | scaler   |       |              |          |       |        |       | 0000          |

| U3MODE         | 0250  | UARTEN                              | _      | USIDL    | IREN   | RTSMD  | —      | UEN<  | <1:0>    | WAKE                                            | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U3STA          | 0252  | UTXISEL1                            | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS                                           | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |

| <b>U3TXREG</b> | 0254  | —                                   | _      | _        | _      | —      | _      | —     |          |                                                 |          | UART  | x Transmit F | Register |       |        |       | xxxx          |

| <b>U3RXREG</b> | 0256  | —                                   | —      | —        | —      | —      | _      |       |          |                                                 |          | UART  | x Receive R  | legister |       |        |       | 0000          |

| U3BRG          | 0258  |                                     |        |          |        |        |        | Baud  | Rate Gen | erator Pres                                     | scaler   | -     | -            |          |       |        | -     | 0000          |

| U4MODE         | 02B0  | UARTEN                              | _      | USIDL    | IREN   | RTSMD  | _      | UEN<  | <1:0>    | WAKE                                            | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U4STA          | 02B2  | UTXISEL1                            | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS                                           | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |

| U4TXREG        | 02B4  | _                                   | _      | _        | _      | _      | _      | _     |          |                                                 |          | UART  | k Transmit F | Register |       |        |       | xxxx          |

| U4RXREG        | 02B6  | _                                   | _      | —        | _      | -      | _      | —     |          |                                                 |          | UART  | x Receive R  | legister |       |        |       | 0000          |

| U4BRG          | 02B8  | B8 Baud Rate Generator Prescaler 00 |        |          |        |        |        |       |          |                                                 |          | 0000  |              |          |       |        |       |               |

|                |       |                                     |        |          |        |        |        |       |          |                                                 |          |       |              |          |       |        |       |               |

#### TABLE 4-23: UART1, UART2, UART3 and UART4 REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 8.1 DMA Resources

Many useful resources related to DMA are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en554310                                        |

#### 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

## 8.2 DMA Control Registers

Each DMAC Channel x (where x = 0 through 14) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The DMA Interrupt Flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

#### REGISTER 11-12: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0          | R/W-0                        | R/W-0                                                                        | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0       |

|--------------|------------------------------|------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|-----------------|-------------|

| _            |                              |                                                                              |                            | OCFBR<6:0>        |                 |                 |             |

| bit 15       |                              |                                                                              |                            |                   |                 |                 | bit 8       |

| U-0          | R/W-0                        | R/W-0                                                                        | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0       |

|              |                              | 10110                                                                        |                            | OCFAR<6:0>        |                 | 10110           | 1010 0      |

| bit 7        |                              |                                                                              |                            |                   |                 |                 | bit 0       |

| Legend:      |                              |                                                                              |                            |                   |                 |                 |             |

| R = Readab   | le bit                       | W = Writable                                                                 | bit                        | U = Unimplem      | nented bit, rea | ad as '0'       |             |

| -n = Value a | t POR                        | '1' = Bit is set                                                             |                            | '0' = Bit is clea | ared            | x = Bit is unkr | nown        |

|              | (see Table 11-               | -2 for input pin                                                             |                            |                   | oo oonoop       | <u>g</u>        | In Pin bits |

|              | 1111111 = In<br>0000001 = In | -2 for input pin<br>aput tied to RP1<br>aput tied to CMI<br>aput tied to Vss | selection nun<br>I27<br>P1 |                   |                 |                 |             |

| bit 7        | 1111111 = In                 | put tied to RP1                                                              | selection nun<br>127<br>P1 |                   |                 |                 |             |

| REGISTER 11-16: | <b>RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15</b> |

|-----------------|---------------------------------------------------------|

|                 | (dsPIC33EPXXXMU806/810/814 DEVICES ONLY)                |

| U-0                                                                                                                                       | R/W-0        | R/W-0                                                     | R/W-0         | R/W-0           | R/W-0          | R/W-0                         | R/W-0 |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------|---------------|-----------------|----------------|-------------------------------|-------|--|--|

| —                                                                                                                                         |              |                                                           | ŀ             | HOME1R<6:0>     | .(1)           |                               |       |  |  |

| bit 15                                                                                                                                    |              |                                                           |               |                 |                |                               | bit 8 |  |  |

|                                                                                                                                           |              |                                                           |               |                 |                |                               |       |  |  |

| U-0                                                                                                                                       | R/W-0        | R/W-0                                                     | R/W-0         | R/W-0           | R/W-0          | R/W-0                         | R/W-0 |  |  |

|                                                                                                                                           |              |                                                           |               | INDX1R<6:0>     | (1)            |                               |       |  |  |

| bit 7                                                                                                                                     |              |                                                           |               |                 |                |                               | bit 0 |  |  |

| <u> </u>                                                                                                                                  |              |                                                           |               |                 |                |                               |       |  |  |

| Legend:<br>R = Readab                                                                                                                     | le hit       | W = Writable ł                                            | nit           | II = I Inimplen | nented hit re: | n' as he                      |       |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown |              |                                                           |               |                 |                |                               |       |  |  |

|                                                                                                                                           |              |                                                           |               |                 |                |                               |       |  |  |

|                                                                                                                                           | 11111111 =   | 1-2 for input pin a Input tied to RP1                     | 27            | iders)          |                |                               |       |  |  |

|                                                                                                                                           |              | Input tied to CMF<br>Input tied to Vss                    | 21            |                 |                |                               |       |  |  |

| bit 7                                                                                                                                     |              | nted: Read as '0                                          | )'            |                 |                |                               |       |  |  |

| bit 6-0                                                                                                                                   | (see Table 1 | D>: Assign QEI1<br>1-2 for input pin<br>Input tied to RP1 | selection num |                 | responding R   | Pn/RPIn Pin bits <sup>i</sup> | (1)   |  |  |

|                                                                                                                                           |              | Input tied to CMF<br>Input tied to Vss                    | 21            |                 |                |                               |       |  |  |

Note 1: These bits are available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

#### REGISTER 11-17: RPINR16: PERIPHERAL PIN SELECT INPUT REGISTER 16 (dsPIC33EPXXXMU806/810/814 DEVICES ONLY)

| U-0          | R/W-0         | R/W-0                                                                                    | R/W-0         | R/W-0            | R/W-0           | R/W-0            | R/W-0 |

|--------------|---------------|------------------------------------------------------------------------------------------|---------------|------------------|-----------------|------------------|-------|

|              |               |                                                                                          |               | QEB2R<6:0>(      | 1)              |                  |       |

| bit 15       |               |                                                                                          |               |                  |                 |                  | bit 8 |

|              |               |                                                                                          |               |                  |                 |                  |       |

| U-0          | R/W-0         | R/W-0                                                                                    | R/W-0         | R/W-0            | R/W-0           | R/W-0            | R/W-0 |

| —            |               |                                                                                          |               | QEA2R<6:0>(      | 1)              |                  |       |

| bit 7        |               |                                                                                          |               |                  |                 |                  | bit C |

|              |               |                                                                                          |               |                  |                 |                  |       |

| Legend:      |               |                                                                                          |               |                  |                 |                  |       |

| R = Readab   |               | W = Writable                                                                             |               | •                | nented bit, rea |                  |       |

| -n = Value a | at POR        | '1' = Bit is set                                                                         |               | '0' = Bit is cle | ared            | x = Bit is unkr  | nown  |

|              | 1111111 = I   | I-2 for input pin<br>nput tied to RP <sup>*</sup><br>nput tied to CM<br>nput tied to Vss | 127<br>P1     |                  |                 |                  |       |

| bit 7        | Unimplemer    | nted: Read as '                                                                          | 0'            |                  |                 |                  |       |

| bit 6-0      | (see Table 11 | Assign A (QE<br>I-2 for input pin<br>nput tied to RP <sup>2</sup>                        | selection nun |                  | n/RPIn Pin bil  | <sub>S</sub> (1) |       |

Note 1: These bits are available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

#### REGISTER 11-49: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |  |  |  |

|--------|-----|------------|-------|-------|--------|-------|-------|--|--|--|

| —      | —   |            |       | RP84  | R<5:0> |       |       |  |  |  |

| bit 15 |     |            |       |       |        |       | bit 8 |  |  |  |

|        |     |            |       |       |        |       |       |  |  |  |

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |  |  |  |

| _      | _   | RP82R<5:0> |       |       |        |       |       |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 7

| bit 13-8 | <b>RP84R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP84 Output Pin bits (see Table 11-3 for peripheral function numbers) |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6  | Unimplemented: Read as '0'                                                                                                               |

|          | RROOR (F.O. ) Design based Output Function is Assigned to RROO Output Dis hits                                                           |

bit 5-0 **RP82R<5:0>:** Peripheral Output Function is Assigned to RP82 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### REGISTER 11-50: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —      | —   |       | RP87R<5:0> |       |       |       |       |  |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |  |

| U-0   | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|------------|-------|-------|-------|-------|-------|--|

| —     | —   | RP85R<5:0> |       |       |       |       |       |  |

| bit 7 |     |            |       |       |       |       | bit 0 |  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP87R<5:0>:** Peripheral Output Function is Assigned to RP87 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP85R<5:0>:** Peripheral Output Function is Assigned to RP85 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 0

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

#### REGISTER 11-53: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------------|-------|-------|-------|-------|-------|

| —      | —   | RP101R<5:0> |       |       |       |       |       |

| bit 15 |     |             |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------------|-------|-------|-------|-------|-------|--|

| —     | —   | RP100R<5:0> |       |       |       |       |       |  |

| bit 7 |     |             |       |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 13-8 | RP101R<5:0>: Peripheral Output Function is Assigned to RP101Output Pin bits |

|----------|-----------------------------------------------------------------------------|

|          | (see Table 11-3 for peripheral function numbers)                            |

| bit 7-6  | Unimplemented: Read as '0'                                                  |

bit 5-0 **RP100R<5:0>:** Peripheral Output Function is Assigned to RP100 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### REGISTER 11-54: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | -   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|-------------|-------|-------|-------|-------|--|--|

| —     | —   |       | RP102R<5:0> |       |       |       |       |  |  |

| bit 7 |     |       |             |       |       |       | bit 0 |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP102R<5:0>:** Peripheral Output Function is Assigned to RP102 Output Pin bits (see Table 11-3 for peripheral function numbers)

## 12.2 Timer1 Control Register

| R/W-0              | U-0                                                                                                              | R/W-0                                                                                                        | U-0                       | U-0              | U-0                      | U-0                | U-0   |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------|------------------|--------------------------|--------------------|-------|--|--|--|--|

| TON <sup>(1)</sup> | _                                                                                                                | TSIDL                                                                                                        | _                         |                  | —                        | _                  |       |  |  |  |  |

| bit 15             |                                                                                                                  |                                                                                                              |                           |                  |                          |                    | bit 8 |  |  |  |  |

|                    |                                                                                                                  |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

| U-0                | R/W-0                                                                                                            | R/W-0                                                                                                        | R/W-0                     | U-0              | R/W-0                    | R/W-0              | U-0   |  |  |  |  |

|                    | TGATE                                                                                                            | TCKP                                                                                                         | S<1:0>                    | _                | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> | _     |  |  |  |  |

| bit 7              |                                                                                                                  |                                                                                                              |                           |                  |                          |                    | bit ( |  |  |  |  |

| Legend:            |                                                                                                                  |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

| R = Readable       | e bit                                                                                                            | W = Writable                                                                                                 | bit                       | U = Unimpler     | mented bit, read         | as '0'             |       |  |  |  |  |

| -n = Value at      | POR                                                                                                              | '1' = Bit is set                                                                                             |                           | '0' = Bit is cle | ared                     | x = Bit is unkno   | own   |  |  |  |  |

|                    |                                                                                                                  | o (1)                                                                                                        |                           |                  |                          |                    |       |  |  |  |  |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16-                                                                             | bit Timer1                                                                                                   |                           |                  |                          |                    |       |  |  |  |  |

| bit 14             | 0 = Stops 16-<br>Unimplemen                                                                                      |                                                                                                              | 0'                        |                  |                          |                    |       |  |  |  |  |

| bit 13             | -                                                                                                                |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    |                                                                                                                  | <b>TSIDL:</b> Timer1 Stop in Idle Mode bit<br>L = Discontinues module operation when device enters Idle mode |                           |                  |                          |                    |       |  |  |  |  |

|                    |                                                                                                                  | s module opera                                                                                               |                           |                  |                          |                    |       |  |  |  |  |

| bit 12-7           | Unimplemen                                                                                                       | ted: Read as '                                                                                               | 0'                        |                  |                          |                    |       |  |  |  |  |

| bit 6              | TGATE: Time                                                                                                      | GATE: Timer1 Gated Time Accumulation Enable bit                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    | <u>When TCS = 1:</u><br>This bit is ignored.                                                                     |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    | When TCS = 0:                                                                                                    |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    | 1 = Gated time accumulation is enabled                                                                           |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    | 0 = Gated tim                                                                                                    | e accumulatio                                                                                                | n is disabled             |                  |                          |                    |       |  |  |  |  |

| bit 5-4            | TCKPS<1:0> Timer1 Input Clock Prescale Select bits                                                               |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    | 11 = 1:256                                                                                                       |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    | 10 = 1:64<br>01 = 1:8                                                                                            |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    | 00 = 1:1                                                                                                         |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

| bit 3              | Unimplemen                                                                                                       | ted: Read as '                                                                                               | 0'                        |                  |                          |                    |       |  |  |  |  |

| bit 2              | TSYNC: Time                                                                                                      | er1 External Cl                                                                                              | ock Input Syn             | chronization Se  | elect bit <sup>(1)</sup> |                    |       |  |  |  |  |

|                    | When TCS = 1:                                                                                                    |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    | <ul> <li>1 = Synchronizes external clock input</li> <li>0 = Does not synchronize external clock input</li> </ul> |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    | 0 = Does not synchronize external clock input<br>When TCS = 0:                                                   |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

|                    | This bit is igno                                                                                                 |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

| bit 1              | TCS: Timer1                                                                                                      | Clock Source                                                                                                 | Select bit <sup>(1)</sup> |                  |                          |                    |       |  |  |  |  |

|                    | 1 = External c<br>0 = Internal cl                                                                                | clock from T1C<br>ock (FP)                                                                                   | K pin (on the             | rising edge)     |                          |                    |       |  |  |  |  |

|                    | Unimplemen                                                                                                       |                                                                                                              |                           |                  |                          |                    |       |  |  |  |  |

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

**Note 1:** When Timer1 is enabled in External Synchronous Counter mode (TCS = 1, TSYNC = 1, TON = 1), any attempts by user software to write to the TMR1 register are ignored.

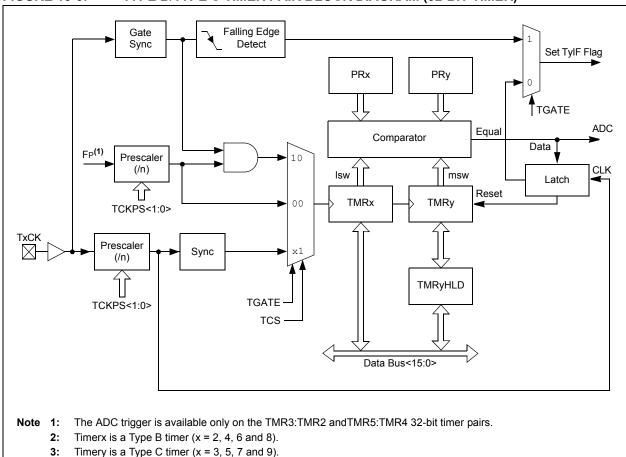

#### FIGURE 13-3: TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

#### 13.1 Timer Resources

Many useful resources related to timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en554310              |

#### 13.1.1 KEY RESOURCES

- Section 11. "Timers" (DS70362) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- · Development Tools

#### 14.2 Input Capture Control Registers

#### U-0 R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 U-0 ICSIDL ICTSEL<2:0> bit 15 bit 8 U-0 R/W-0 R/W-0 R/HC/HS-0 R/HC/HS-0 R/W-0 R/W-0 R/W-0 ICI<1:0> ICOV **ICBNE** ICM<2:0> bit 7 bit 0 Legend: R = Readable bit HC = Hardware Clearable bit HS = Hardware Settable bit '0' = Bit is cleared -n = Value at POR W = Writable bit U = Unimplemented bit, read as '0' bit 15-14 Unimplemented: Read as '0' bit 13 ICSIDL: Input Capture Stop in Idle Control bit 1 = Input capture will Halt in CPU Idle mode 0 = Input capture will continue to operate in CPU Idle mode bit 12-10 ICTSEL<12:10>: Input Capture Timer Select bits 111 = Peripheral clock (FP) is the clock source of the ICx 110 = Reserved 101 = Reserved 100 = Clock source of T1CLK is the clock source of the ICx (only the synchronous clock is supported) 011 = Clock source of T5CLK is the clock source of the ICx 010 = Clock source of T4CLK is the clock source of the ICx 001 = Clock source of T2CLK is the clock source of the ICx 000 = Clock source of T3CLK is the clock source of the ICx bit 9-7 Unimplemented: Read as '0' bit 6-5 ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111) 11 = Interrupt on every fourth capture event 10 = Interrupt on every third capture event 01 = Interrupt on every second capture event 00 = Interrupt on every capture event bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only) 1 = Input capture buffer overflow occurred 0 = No input capture buffer overflow occurred bit 3 ICBNE: Input Capture Buffer Not Empty Status bit (read-only) 1 = Input capture buffer is not empty, at least one more capture value can be read 0 = Input capture buffer is empty bit 2-0 ICM<2:0>: Input Capture Mode Select bits 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable) 110 = Unused (module disabled) 101 = Capture mode, every 16th rising edge (Prescaler Capture mode) 100 = Capture mode, every 4th rising edge (Prescaler Capture mode) 011 = Capture mode, every rising edge (Simple Capture mode) 010 = Capture mode, every falling edge (Simple Capture mode) 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode) 000 = Input capture module is turned off

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| R/W-0           | R/W-0                              | R/W-0                                 | U-0         | U-0                                     | U-0             | U-0               | U-0    |

|-----------------|------------------------------------|---------------------------------------|-------------|-----------------------------------------|-----------------|-------------------|--------|

| FRMEN           | SPIFSD                             | FRMPOL                                |             | _                                       |                 |                   | —      |

| bit 15          |                                    |                                       |             |                                         |                 |                   | bit 8  |

|                 |                                    |                                       |             |                                         |                 |                   |        |

| U-0             | U-0                                | U-0                                   | U-0         | U-0                                     | U-0             | R/W-0             | R/W-0  |

|                 |                                    | —                                     | —           |                                         |                 | FRMDLY            | SPIBEN |

| bit 7           |                                    |                                       |             |                                         |                 |                   | bit 0  |

|                 |                                    |                                       |             |                                         |                 |                   |        |

| Legend:         |                                    |                                       |             |                                         |                 |                   |        |

| R = Readable    | bit                                | W = Writable I                        | oit         | U = Unimpler                            | nented bit, rea | d as '0'          |        |

| -n = Value at F | POR                                | '1' = Bit is set                      |             | '0' = Bit is cleared x = Bit is unknown |                 |                   |        |

|                 |                                    |                                       |             |                                         |                 |                   |        |

| bit 15          |                                    | med SPIx Supp                         |             | _                                       |                 |                   |        |

|                 |                                    |                                       |             | cpin is used as                         | a Frame Sync    | : pulse input/out | out)   |

| h:+ 1 4         |                                    | SPIx support is o                     |             | ntual hit                               |                 |                   |        |

| bit 14          |                                    | me Sync Pulse<br>/nc pulse input (    |             | ntroi dit                               |                 |                   |        |

|                 | ,                                  | /nc pulse input (                     | · /         |                                         |                 |                   |        |

| bit 13          | -                                  | ame Sync Pulse                        | . ,         |                                         |                 |                   |        |

|                 |                                    | /nc pulse is acti                     | -           |                                         |                 |                   |        |

|                 | 0 = Frame Sync pulse is active-low |                                       |             |                                         |                 |                   |        |

| bit 12-2        | Unimplemen                         | ited: Read as 'd                      | )'          |                                         |                 |                   |        |

| bit 1           | FRMDLY: Fra                        | ame Sync Pulse                        | Edge Select | t bit                                   |                 |                   |        |

|                 | ,                                  | /nc pulse coinci                      |             |                                         |                 |                   |        |

| 1.11.0          | -                                  | /nc pulse prece                       |             | DIT CIOCK                               |                 |                   |        |

| bit 0           |                                    | nanced Buffer E                       |             |                                         |                 |                   |        |

|                 |                                    | d Buffer is enab<br>d Buffer is disab |             | d mode)                                 |                 |                   |        |

|                 |                                    |                                       |             |                                         |                 |                   |        |

#### REGISTER 18-3: SPIXCON2: SPIX CONTROL REGISTER 2

## 20.3 UARTx Registers

| R/W-0                 | U-0                                                                                                             | R/W-0                                                | R/W-0                          | R/W-0                                    | U-0                                                                                | R/W-0             | R/W-0            |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------|------------------------------------------|------------------------------------------------------------------------------------|-------------------|------------------|--|--|

| UARTEN <sup>(1)</sup> | —                                                                                                               | USIDL                                                | IREN <sup>(2)</sup>            | RTSMD                                    | —                                                                                  | UEN               | <1:0>            |  |  |

| bit 15                |                                                                                                                 |                                                      |                                |                                          |                                                                                    |                   | bit 8            |  |  |

| R/W-0, HC             | R/W-0                                                                                                           | R/W-0, HC                                            | R/W-0                          | R/W-0                                    | R/W-0                                                                              | R/W-0             | R/W-0            |  |  |

| WAKE                  | LPBACK                                                                                                          | ABAUD                                                | URXINV                         | BRGH                                     | PDSEI                                                                              | -                 | STSEL            |  |  |

| bit 7                 | LFDACK                                                                                                          | ABAUD                                                | URAINV                         | BRGH                                     | FDGEI                                                                              | _<1.0>            | bit (            |  |  |

|                       |                                                                                                                 |                                                      |                                |                                          |                                                                                    |                   |                  |  |  |

| Legend:               |                                                                                                                 | HC = Hardwa                                          | re Clearable b                 | bit                                      |                                                                                    |                   |                  |  |  |

| R = Readable          | bit                                                                                                             | W = Writable                                         | bit                            | U = Unimpler                             | mented bit, read                                                                   | l as '0'          |                  |  |  |

| -n = Value at F       | POR                                                                                                             | '1' = Bit is set                                     |                                | '0' = Bit is cle                         | ared                                                                               | x = Bit is unkr   | nown             |  |  |

| bit 15                | UARTEN: UA                                                                                                      | RTx Enable bi                                        | t(1)                           |                                          |                                                                                    |                   |                  |  |  |

|                       |                                                                                                                 |                                                      |                                |                                          | y UARTx as defin<br>y port latches; L                                              |                   |                  |  |  |

| bit 14                | Unimplemen                                                                                                      | ted: Read as '                                       | 0'                             |                                          |                                                                                    |                   |                  |  |  |

| bit 13                | USIDL: UART                                                                                                     | Tx Stop in Idle                                      | Mode bit                       |                                          |                                                                                    |                   |                  |  |  |

|                       |                                                                                                                 | ues module op<br>s module oper                       |                                |                                          | Idle mode                                                                          |                   |                  |  |  |

| bit 12                | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup>                                           |                                                      |                                |                                          |                                                                                    |                   |                  |  |  |

|                       | <ul> <li>1 = IrDA encoder and decoder are enabled</li> <li>0 = IrDA encoder and decoder are disabled</li> </ul> |                                                      |                                |                                          |                                                                                    |                   |                  |  |  |

| bit 11                | RTSMD: Mod                                                                                                      | le Selection for                                     | UxRTS Pin b                    | it                                       |                                                                                    |                   |                  |  |  |

|                       |                                                                                                                 | in in Simplex n<br>in in Flow Con                    |                                |                                          |                                                                                    |                   |                  |  |  |