Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc806-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

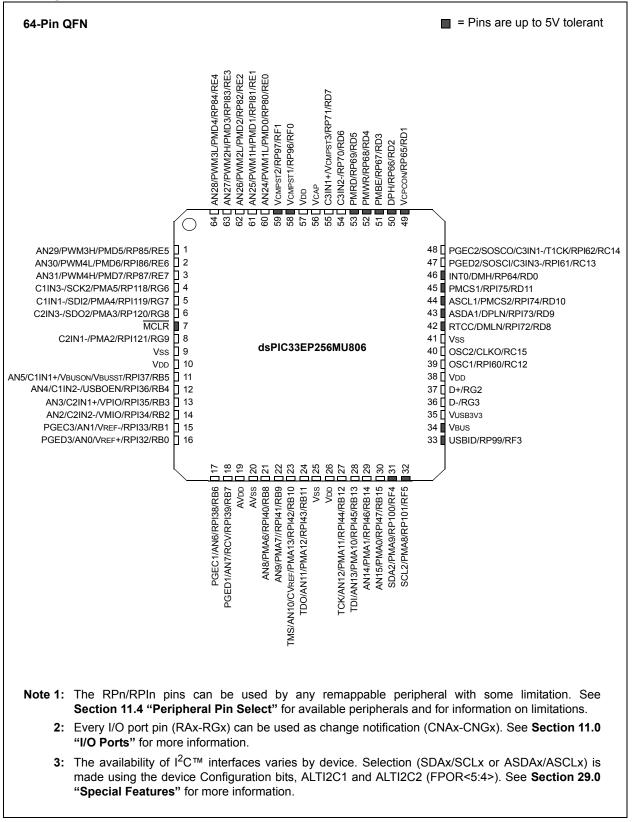

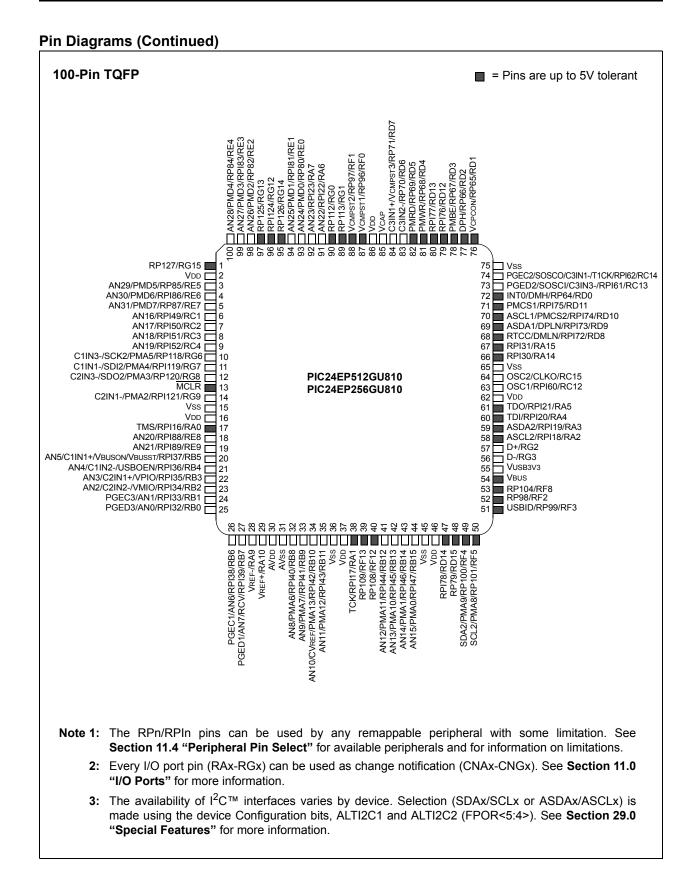

#### **Pin Diagrams**

# TABLE 3:PIN NAMES: PIC24EP256GU810 AND PIC24EP512GU810DEVICES<sup>(1,2)</sup> (CONTINUED)

| Pin<br>Number | Full Pin Name              |

|---------------|----------------------------|

| E1            | AN19/RPI52/RC4             |

| E2            | AN18/RPI51/RC3             |

| E3            | C1IN3-/SCK2/PMA5/RP118/RG6 |

| E4            | AN17/RPI50/RC2             |

| E5            | No Connect                 |

| E6            | RP113/RG1                  |

| E7            | No Connect                 |

| K4            | AN8/PMA6/RPI40/RB8         |

| K5            | No Connect                 |

| K6            | RP108/RF12                 |

| K7            | AN14/PMA1/RPI46/RB14       |

| K8            | VDD                        |

| K9            | RP79/RD15                  |

| K10           | USBID/RP99/RF3             |

| K11           | RP98/RF2                   |

| L1            | PGEC1/AN6/RPI38/RB6        |

| L2            | Vref-/RA9                  |

| Pin<br>Number | Full Pin Name                       |

|---------------|-------------------------------------|

| J8            | No Connect                          |

| J9            | No Connect                          |

| J10           | RP104/RF8                           |

| J11           | D-/RG3 <sup>(5)</sup>               |

| K1            | PGEC3/AN1/RPI33/RB1                 |

| K2            | PGED3/AN0/RPI32/RB0                 |

| K3            | VREF+/RA10                          |

| L3            | AVss                                |

| L4            | AN9/PMA7/RPI41/RB9                  |

| L5            | AN10/CVREF/PMA13/RPI42/RB10         |

| L6            | RP109/RF13                          |

| L7            | AN13/PMA10/RPI45/RB13               |

| L8            | AN15/PMA0/RPI47/RB15                |

| L9            | RPI78/RD14                          |

| L10           | SDA2 <sup>(3)</sup> /PMA9/RP100/RF4 |

| L11           | SCL2 <sup>(3)</sup> /PMA8/RP101/RF5 |

Note 1: The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See Section 11.4 "Peripheral Pin Select" for available peripherals and for information on limitations.

2: Every I/O port pin (RAx-RGx) can be used as change notification (CNAx-CNGx). See Section 11.0 "I/O Ports" for more information.

3: The availability of I<sup>2</sup>C™ interfaces varies by device. Selection (SDAx/SCLx or ASDAx/ASCLx) is made using the device Configuration bits, ALTI2C1 and ALTI2C2 (FPOR<5:4>). See Section 29.0 "Special Features" for more information.

4: The pin name is SCL1/RG2 for the dsPIC33EP512(GP/MC)806 and PIC24EP512GP806 devices.

5: The pin name is SDA1/RG3 for the dsPIC33EP512(GP/MC)806 and PIC24EP512GP806 devices.

| Pin Name                          | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                                       |  |  |  |

|-----------------------------------|-------------|----------------|-----|---------------------------------------------------------------------------------------------------|--|--|--|

| C2IN1+, C2IN2-,<br>C2IN1-, C2IN3- | I           | Analog         | No  | Comparator 2 inputs.                                                                              |  |  |  |

| C2OUT                             | 0           | —              | Yes | Comparator 2 output.                                                                              |  |  |  |

| C3IN1+, C3IN2-,<br>C2IN1-, C3IN3- | Ι           | Analog         | No  | Comparator 3 inputs.                                                                              |  |  |  |

| C3OUT                             | 0           | —              | Yes | Comparator 3 output.                                                                              |  |  |  |

| PMA0                              | I/O         | TTL/ST         | No  | Parallel Master Port Address Bit 0 input (Buffered Slave modes) and                               |  |  |  |

|                                   |             |                |     | output (Master modes).                                                                            |  |  |  |

| PMA1                              | I/O         | TTL/ST         | No  | Parallel Master Port Address Bit 1 input (Buffered Slave modes) and                               |  |  |  |

|                                   | _           |                |     | output (Master modes).                                                                            |  |  |  |

| PMA2 -PMA13                       | 0           | —              |     | Parallel Master Port Address Bits 2-13 (Demultiplexed Master modes).                              |  |  |  |

| PMBE                              | 0           |                |     | Parallel Master Port byte enable strobe.                                                          |  |  |  |

| PMCS1, PMCS2                      | 0           |                |     | Parallel Master Port Chip Select 1 and 2 strobe.                                                  |  |  |  |

| PMD0-PMD7                         | I/O         | TTL/ST         | No  | Parallel Master Port data (Demultiplexed Master mode) or address/data (Multiplexed Master modes). |  |  |  |

| PMRD                              | 0           |                | No  | Parallel Master Port read strobe.                                                                 |  |  |  |

| PMWR                              | 0           | —              | No  | Parallel Master Port write strobe.                                                                |  |  |  |

| FLT1-FLT7 <sup>(1)</sup>          | I           | ST             | Yes | PWM Fault Input 1 through 7.                                                                      |  |  |  |

| DTCMP1-DTCMP7 <sup>(1)</sup>      | 1           | ST             | Yes | PWM dead-time compensation input.                                                                 |  |  |  |

| PWM1L-PWM7L <sup>(1)</sup>        | 0           |                |     | PWM Low Output 1 through 7.                                                                       |  |  |  |

| PWM1H-PWM7H <sup>(1)</sup>        | 0           |                |     | PWM High Output 1 through 7.                                                                      |  |  |  |

| SYNCI1, SYNCI2 <sup>(1)</sup>     | I           | ST             |     | PWM Synchronization Inputs 1 and 2.                                                               |  |  |  |

| SYNCO1, SYNCO2 <sup>(1)</sup>     | 0           | _              |     | PWM Synchronization Outputs 1 and 2.                                                              |  |  |  |

| Legend: CMOS = CM                 |             | •              | •   | or output Analog = Analog input P = Power                                                         |  |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output

Analog = Analog input

P = Pow

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

PPS = Peripheral Pin Select

TTL = TTL input buffer

Note 1: This pin is available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

**2:** AVDD must be connected at all times.

3: These pins are input only on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

4: These pins are only available on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

5: The availability of I<sup>2</sup>C<sup>™</sup> interfaces varies by device. Refer to the "Pin Diagrams" section for availability. Selection (SDAx/SCLx or ASDAx/ASCLx) is made using the device Configuration bits, ALTI2C1 and ALTI2C2 (FPOR<5:4>). See Section 29.0 "Special Features" for more information.

6: Analog functionality is activated by enabling the USB module and is not controlled by the ANSEL register.

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

#### **REGISTER 8-3:** DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0    | U-0   | U-0   | U-0   | U-0    | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|--------|-------|-------|-------|

| _      | _     |       |       |        | _     |       | _     |

| bit 15 |       |       |       |        |       |       | bit 8 |

|        |       |       |       |        |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | STA<  | 23:16> |       |       |       |

| bit 7  |       |       |       |        |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

#### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0           | R/W-0                             | R/W-0            | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 |  |

|-----------------|-----------------------------------|------------------|-------|-----------------------------------------|------------------------------------|-------|-------|--|

|                 |                                   |                  | STA   | <15:8>                                  |                                    |       |       |  |

| bit 15          |                                   |                  |       |                                         |                                    |       | bit 8 |  |

|                 |                                   |                  |       |                                         |                                    |       |       |  |

| R/W-0           | R/W-0                             | R/W-0            | R/W-0 | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0 |  |

|                 |                                   |                  | STA   | <7:0>                                   |                                    |       |       |  |

| bit 7           |                                   |                  |       |                                         |                                    |       | bit 0 |  |

|                 |                                   |                  |       |                                         |                                    |       |       |  |

| Legend:         |                                   |                  |       |                                         |                                    |       |       |  |

| R = Readable    | R = Readable bit W = Writable bit |                  |       |                                         | U = Unimplemented bit, read as '0' |       |       |  |

| -n = Value at P | OR                                | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                                    | nown  |       |  |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

| U-0                                             | U-0                                                              | U-0   | U-0   | R/W-0           | U-0              | U-0      | U-0   |

|-------------------------------------------------|------------------------------------------------------------------|-------|-------|-----------------|------------------|----------|-------|

| —                                               | —                                                                | —     | —     |                 | —                | _        | —     |

| bit 15                                          |                                                                  |       |       |                 |                  |          | bit 8 |

|                                                 |                                                                  |       |       |                 |                  |          |       |

| R/W-0                                           | R/W-0                                                            | R/W-0 | R/W-0 | R/W-0           | R/W-0            | R/W-0    | R/W-0 |

|                                                 |                                                                  |       | STB<  | 23:16>          |                  |          |       |

| bit 7                                           |                                                                  |       |       |                 |                  |          | bit 0 |

|                                                 |                                                                  |       |       |                 |                  |          |       |

| Legend:                                         |                                                                  |       |       |                 |                  |          |       |

| R = Readable bit W = Writable bit U = Unimpleme |                                                                  |       |       |                 | mented bit, read | l as '0' |       |

| -n = Value at F                                 | /alue at POR '1' = Bit is set '0' = Bit is cleared x = Bit is ur |       |       | x = Bit is unkr | nown             |          |       |

|                                                 |                                                                  |       |       |                 |                  |          |       |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: Secondary Start Address bits (source or destination)

#### REGISTER 8-6: DMAXSTBL: DMA CHANNEL x START ADDRESS REGISTER B (LOW)

| R/W-0                             | R/W-0            | R/W-0       | R/W-0                                   | R/W-0                                                                                                                                | R/W-0                                                                                                                                                             | R/W-0                                                                                                                                                     |

|-----------------------------------|------------------|-------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |                  | STB         | <15:8>                                  |                                                                                                                                      |                                                                                                                                                                   |                                                                                                                                                           |

|                                   |                  |             |                                         |                                                                                                                                      |                                                                                                                                                                   | bit 8                                                                                                                                                     |

|                                   |                  |             |                                         |                                                                                                                                      |                                                                                                                                                                   |                                                                                                                                                           |

| R/W-0                             | R/W-0            | R/W-0       | R/W-0                                   | R/W-0                                                                                                                                | R/W-0                                                                                                                                                             | R/W-0                                                                                                                                                     |

|                                   |                  | STE         | 3<7:0>                                  |                                                                                                                                      |                                                                                                                                                                   |                                                                                                                                                           |

|                                   |                  |             |                                         |                                                                                                                                      |                                                                                                                                                                   | bit 0                                                                                                                                                     |

|                                   |                  |             |                                         |                                                                                                                                      |                                                                                                                                                                   |                                                                                                                                                           |

|                                   |                  |             |                                         |                                                                                                                                      |                                                                                                                                                                   |                                                                                                                                                           |

| R = Readable bit W = Writable bit |                  |             | U = Unimplemented bit, read as '0'      |                                                                                                                                      |                                                                                                                                                                   |                                                                                                                                                           |

| POR                               | '1' = Bit is set |             | '0' = Bit is cleared x = Bit is unknown |                                                                                                                                      |                                                                                                                                                                   | nown                                                                                                                                                      |

|                                   | R/W-0            | R/W-0 R/W-0 | R/W-0     R/W-0       STE       bit     | STB<15:8>           R/W-0         R/W-0         R/W-0           STB<7:0>           bit         W = Writable bit         U = Unimplem | STB<15:8>           R/W-0         R/W-0         R/W-0         R/W-0           STB<7:0>           bit         W = Writable bit         U = Unimplemented bit, read | STB<15:8>           R/W-0         R/W-0         R/W-0         R/W-0         R/W-0           STB<7:0>         U = Unimplemented bit, read as '0'         U |

bit 15-0 STB<15:0>: Secondary Start Address bits (source or destination)

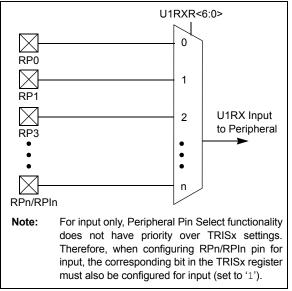

## 11.4 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral Pin Select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation "RPn" or "RPIn" in their full pin designation, where "RP" designates a remappable function for input or output and "RPI" designates a remappable functions for input only, and "n" is the remappable pin number.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral. When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-22). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals (see Table 11-1). Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn/RPIn pin with the corresponding value to that peripheral (see Table 11-2). For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

#### FIGURE 11-2: U1RX REMAPPABLE INPUT

Input/

Output

L

I

L

\_\_\_\_

I

I

Т

L

\_\_\_\_

\_\_\_\_

\_\_\_\_

\_

1

|

I/O I/O

I/O

I/O

I/O

I/O I/O

I/O

I

1

Т

I

|

I/O

I/O

Т

I/O

I

I/O I/O

| |/0 **Pin Assignment**

RPI45

RPI46

RPI47

Reserved

RPI49

RPI50

RPI51

RPI52

Reserved

Reserved

Reserved Reserved

Reserved Reserved

**RPI60**

RPI61 RPI62

Reserved RP64

RP65

RP66

RP67 RP68

RP69

**RP70**

RP71 RPI72

RPI73

RPI74

RPI75 RPI76

RPI77

RPI78

RP79

**RP80**

**RPI81**

RP82 RPI83

**RP84**

RP85 RPI86

**RP87**

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

| Peripheral Pin Select<br>Input Register Value | Input/<br>Output | Pin Assignment        | Peripheral Pin Select<br>Input Register Value |

|-----------------------------------------------|------------------|-----------------------|-----------------------------------------------|

| 000 0000                                      | I                | Vss                   | 010 1101                                      |

| 000 0001                                      | I                | C1OUT <sup>(1)</sup>  | 010 1110                                      |

| 000 0010                                      | I                | C2OUT <sup>(1)</sup>  | 010 1111                                      |

| 000 0011                                      | I                | C3OUT <sup>(1)</sup>  | 011 0000                                      |

| 000 0100                                      | _                | Reserved              | 011 0001                                      |

| 000 0101                                      | _                | Reserved              | 011 0010                                      |

| 000 0110                                      | _                | Reserved              | 011 0011                                      |

| 000 0111                                      | _                | Reserved              | 011 0100                                      |

| 000 1000                                      | I                | FINDX1 <sup>(1)</sup> | 011 0101                                      |

| 000 1001                                      | I                | FHOME1 <sup>(1)</sup> | 011 0110                                      |

| 000 1010                                      | I                | FINDX2 <sup>(1)</sup> | 011 0111                                      |

| 000 1011                                      | I                | FHOME2 <sup>(1)</sup> | 011 1000                                      |

| 000 1100                                      | _                | Reserved              | 011 1001                                      |

| 000 1101                                      | _                | Reserved              | 011 1010                                      |

| 000 1110                                      | —                | Reserved              | 011 1011                                      |

| 000 1111                                      | —                | Reserved              | 011 1100                                      |

| 001 0000                                      | I                | RPI16                 | 011 1101                                      |

| 001 0001                                      | I                | RPI17                 | 011 1110                                      |

| 001 0010                                      | I                | RPI18                 | 011 1111                                      |

| 001 0011                                      | I                | RPI19                 | 100 0000                                      |

| 001 0100                                      | I                | RPI20                 | 100 0001                                      |

| 001 0101                                      | I                | RPI21                 | 100 0010                                      |

| 001 0110                                      | I                | RPI22                 | 100 0011                                      |

| 001 0111                                      | I                | RPI23                 | 100 0100                                      |

| 001 1000                                      | _                | Reserved              | 100 0101                                      |

| 001 1001                                      | —                | Reserved              | 100 0110                                      |

| 001 1010                                      | _                | Reserved              | 100 0111                                      |

| 001 1011                                      | —                | Reserved              | 100 1000                                      |

| 001 1100                                      | —                | Reserved              | 100 1001                                      |

| 001 1101                                      | _                | Reserved              | 100 1010                                      |

| 001 1110                                      | I                | RPI30                 | 100 1011                                      |

| 001 1111                                      | I                | RPI31                 | 100 1100                                      |

| 010 0000                                      | I                | RPI32                 | 100 1101                                      |

| 010 0001                                      | I                | RPI33                 | 100 1110                                      |

| 010 0010                                      | I                | RPI34                 | 100 1111                                      |

| 010 0011                                      | I                | RPI35                 | 101 0000                                      |

| 010 0100                                      | I                | RPI36                 | 101 0001                                      |

| 010 0101                                      | I                | RPI37                 | 101 0010                                      |

| 010 0110                                      | I                | RPI38                 | 101 0011                                      |

| 010 0111                                      | I                | RPI39                 | 101 0100                                      |

| 010 1000                                      | I                | RPI40                 | 101 0101                                      |

| 010 1001                                      | I                | RPI41                 | 101 0110                                      |

| 010 1010                                      | 1                | RPI42                 | 101 0111                                      |

Note 1: See Section 11.4.4.2 "Virtual Connections" for more information on selecting this pin assignment.

© 2009-2012 Microchip Technology Inc.

#### REGISTER 11-18: RPINR17: PERIPHERAL PIN SELECT INPUT REGISTER 17 (dsPIC33EPXXXMU806/810/814 DEVICES ONLY)

| U-0             | R/W-0                         | R/W-0                                | R/W-0 | R/W-0       | R/W-0        | R/W-0            | R/W-0 |

|-----------------|-------------------------------|--------------------------------------|-------|-------------|--------------|------------------|-------|

| —               |                               |                                      | I     | HOME2R<6:0> | .(1)         |                  |       |

| bit 15          |                               |                                      |       |             |              |                  | bit 8 |

| U-0             | R/W-0                         | R/W-0                                | R/W-0 | R/W-0       | R/W-0        | R/W-0            | R/W-0 |

| _               |                               |                                      |       | INDX2R<6:0> | [1]          |                  |       |

| bit 7           |                               |                                      |       |             |              |                  | bit 0 |

|                 |                               |                                      |       |             |              |                  |       |

| Legend:         |                               | W = Writable I                       |       |             |              |                  |       |

| R = Readable    |                               | nented bit, rea                      |       |             |              |                  |       |

| -n = Value at F | Value at POR '1' = Bit is set |                                      |       |             | ared         | x = Bit is unkr  | nown  |

|                 |                               | -2 for input pin<br>nput tied to RP1 |       | ,           |              |                  |       |

|                 | •                             |                                      |       |             |              |                  |       |

|                 |                               | nput tied to CMI                     |       |             |              |                  |       |

| h:+ 7           |                               | nput tied to Vss                     |       |             |              |                  |       |

| bit 7           | -                             | ted: Read as '                       |       |             | i' D         |                  | (1)   |

| bit 6-0         |                               | -2 for input pin                     |       |             | responding R | Pn/RPIn Pin bits | (')   |

|                 | 1111111 = Ir                  | nput tied to RP1                     | 27    |             |              |                  |       |

|                 | ·                             |                                      |       |             |              |                  |       |

|                 |                               |                                      |       |             |              |                  |       |

|                 | 0000001 = lr<br>0000000 = lr  | nput tied to CMI                     |       |             |              |                  |       |

Note 1: These bits are available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

| U-0          | R/W-0        | R/W-0                                                  | R/W-0   | R/W-0                | R/W-0           | R/W-0           | R/W-0 |  |  |

|--------------|--------------|--------------------------------------------------------|---------|----------------------|-----------------|-----------------|-------|--|--|

|              | 10,00-0      | 10,00-0                                                | 10.00-0 | IC16R<6:0>           |                 |                 |       |  |  |

| bit 15       |              |                                                        |         |                      |                 |                 | bit 8 |  |  |

|              |              |                                                        |         |                      |                 |                 |       |  |  |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0   | R/W-0                | R/W-0           | R/W-0           | R/W-0 |  |  |

|              |              |                                                        |         | IC15R<6:0>           |                 |                 |       |  |  |

| bit 7        |              |                                                        |         |                      |                 |                 | bit C |  |  |

| Legend:      |              |                                                        |         |                      |                 |                 |       |  |  |

| R = Readat   | ole bit      | W = Writable                                           | bit     | U = Unimplem         | nented bit, rea | d as '0'        |       |  |  |

| -n = Value a | at POR       | '1' = Bit is set                                       |         | '0' = Bit is cleared |                 | x = Bit is unkr | nown  |  |  |

|              |              | nput tied to RP <sup>-</sup>                           | 127     |                      |                 |                 |       |  |  |

|              |              | nput tied to CM                                        |         |                      |                 |                 |       |  |  |

| bit 7        | 0000000 = Ir | nput tied to CM<br>nput tied to Vss<br>nted: Read as ' | ;       |                      |                 |                 |       |  |  |

#### REGISTER 11-36: RPINR36: PERIPHERAL PIN SELECT INPUT REGISTER 36

| U-0          | R/W-0        | R/W-0                                                               | R/W-0         | R/W-0                | R/W-0           | R/W-0              | R/W-0    |

|--------------|--------------|---------------------------------------------------------------------|---------------|----------------------|-----------------|--------------------|----------|

| _            |              |                                                                     |               |                      | )>              |                    |          |

| bit 15       |              |                                                                     |               |                      |                 |                    | bit 8    |

|              |              |                                                                     |               |                      |                 |                    |          |

| U-0          | R/W-0        | R/W-0                                                               | R/W-0         | R/W-0                | R/W-0           | R/W-0              | R/W-0    |

| —            |              |                                                                     |               | SYNCI2R<6:0          | >               |                    |          |

| bit 7        |              |                                                                     |               |                      |                 |                    | bit 0    |

|              |              |                                                                     |               |                      |                 |                    |          |

| Legend:      |              |                                                                     |               |                      |                 |                    |          |

| R = Readab   | le bit       | W = Writable                                                        | bit           | U = Unimpler         | nented bit, rea | ad as '0'          |          |

| -n = Value a | t POR        | '1' = Bit is set                                                    |               | '0' = Bit is cleared |                 | x = Bit is unknown |          |

|              |              | nput tied to RP1<br>nput tied to CMI<br>nput tied to Vss            | <b>P</b> 1    |                      |                 |                    |          |

| bit 7        | Unimpleme    | nted: Read as '                                                     | )'            |                      |                 |                    |          |

| bit 6-0      | (see Table 1 | : <b>0&gt;:</b> Assign PWI<br>I-2 for input pin<br>nput tied to RP1 | selection nun |                      | the Correspo    | nding RPn/RPIr     | Pin bits |

|              | 0000001 =    | ,<br>nput tied to CMI<br>nput tied to Vss                           | ⊃1            |                      |                 |                    |          |

#### REGISTER 11-38: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

| <b>REGISTER 16-14:</b> PHASEX: PWMX PRIMARY PHASE SHIFT REGISTER <sup>(1,2)</sup> |

|-----------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------|

| <b>Legend:</b><br>R = Readable bi |       | W = Writable bit |       | U = Unimpler |       |       |       |

|-----------------------------------|-------|------------------|-------|--------------|-------|-------|-------|

| bit 7                             |       |                  |       |              |       |       | bit 0 |

|                                   |       |                  | PHAS  | Ex<7:0>      |       |       |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 |

| bit 15                            |       |                  |       |              |       |       | bit 8 |

|                                   |       |                  | PHASE | Ex<15:8>     |       |       |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 |

bit 15-0 **PHASEx<15:0>:** PWM Phase Shift Value or Independent Time Base Period for the PWM Generator bits

**Note 1:** If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation:

'1' = Bit is set

• Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCON<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase shift value for PWMxH and PWMxL outputs.

'0' = Bit is cleared

- True Independent Output mode (PMOD<1:0> (IOCONx<11:10>) = 11), PHASEx<15:0> = Phase shift value for PWMxH only.

- **2:** If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation:

- Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL.

- True Independent Output mode (PMOD<1:0> (IOCONx<11:10>) = 11), PHASEx<15:0> = Independent time base period value for PWMxH only.

-n = Value at POR

x = Bit is unknown

| bit 7  |       |       |       |       |       |       | bit 0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| AMSK7  | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| bit 15 |       |       |       |       |       |       | bit 8 |

| —      | —     | —     | —     | _     |       | AMSK9 | AMSK8 |

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

bit 15-10 Unimplemented: Read as '0'

R = Readable bit

-n = Value at POR

bit 9-0 AMSKx: Mask for Address bit x Select bit

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

'0' = Bit is cleared

U = Unimplemented bit, read as '0'

x = Bit is unknown

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2CxMSK<6:0> only):

W = Writable bit

'1' = Bit is set

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disable masking for bit Ax + 1; bit match is required in this position

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| R/W-0        | R/W-0                            | R/W-0                                    | R/W-0                                          | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|----------------------------------|------------------------------------------|------------------------------------------------|-------------------|-----------------|-----------------|-------|

|              | F7BF                             | P<3:0>                                   |                                                |                   | F6BI            | D<3:0>          |       |

| bit 15       |                                  |                                          |                                                |                   |                 |                 | bit 8 |

| R/W-0        | R/W-0                            | R/W-0                                    | R/W-0                                          | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|              | F5BF                             | P<3:0>                                   |                                                |                   | F4BI            | ><3:0>          |       |

| bit 7        |                                  |                                          |                                                |                   |                 |                 | bit 0 |

| Legend:      | lo hit                           | M = Mritabla                             | <b>h</b> it                                    |                   | control hit roo | d aa (0)        |       |

| R = Readab   |                                  | W = Writable                             |                                                | U = Unimplen      |                 |                 |       |

| -n = Value a | t POR                            | '1' = Bit is set                         |                                                | '0' = Bit is clea | ared            | x = Bit is unkr | IOWN  |

| bit 15-12    | F7BP<3:0>:                       | RX Buffer Masl                           | k for Filter 7 k                               | oits              |                 |                 |       |

|              |                                  |                                          |                                                |                   |                 |                 |       |

|              |                                  | r hits received ir<br>r hits received ir | n RX FIFO bu                                   |                   |                 |                 |       |

|              |                                  |                                          | n RX FIFO bu                                   |                   |                 |                 |       |

|              | 1110 <b>= Filte</b>              |                                          | n RX FIFO bu                                   |                   |                 |                 |       |

|              | 1110 = Filte<br>•<br>•<br>•<br>• |                                          | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | 4                 |                 |                 |       |

- bit 7-4 F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bit 15-12)

- bit 3-0 F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bit 15-12)

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                         | R/W-0                                      | R/W-0           | R/W-0                              | R/W-0 | R/W-0           | R/W-0   |  |

|---------------|-----------------------------------------------|--------------------------------------------|-----------------|------------------------------------|-------|-----------------|---------|--|

|               | F11B                                          | P<3:0>                                     |                 |                                    | F10E  | 3P<3:0>         |         |  |

| bit 15        |                                               |                                            |                 |                                    |       |                 | bit 8   |  |

| R/W-0         | R/W-0                                         | R/W-0                                      | R/W-0           | R/W-0                              | R/W-0 | R/W-0           | R/W-0   |  |

| 10,00-0       | F9BP<3:0>                                     |                                            |                 |                                    | -     | P<3:0>          | 10.00-0 |  |

| bit 7         | 1 3 01                                        | 10.02                                      |                 |                                    | 100   | 1 3.02          | bit 0   |  |

|               |                                               |                                            |                 |                                    |       |                 | bit o   |  |

| Legend:       |                                               |                                            |                 |                                    |       |                 |         |  |

| R = Readabl   | e bit                                         | W = Writable                               | bit             | U = Unimplemented bit, read as '0' |       |                 |         |  |

| -n = Value at | POR                                           | '1' = Bit is set                           | :               | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown    |  |

|               |                                               |                                            |                 |                                    |       |                 |         |  |

| bit 15-12     | F11BP<3:0                                     | RX Buffer Ma                               | sk for Filter 1 | 1 bits                             |       |                 |         |  |

|               | 1111 = Filter hits received in RX FIFO buffer |                                            |                 |                                    |       |                 |         |  |

|               | 1111 = Filte                                  | er hits received in                        | h RX FIFO bu    | lmer                               |       |                 |         |  |

|               |                                               | er hits received in<br>er hits received in |                 | -                                  |       |                 |         |  |

|               |                                               |                                            |                 | -                                  |       |                 |         |  |

|          | •                                                                        |

|----------|--------------------------------------------------------------------------|

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F10BP<3:0>: RX Buffer Mask for Filter 10 bits (same values as bit 15-12) |

| bit 7-4  | F9BP<3:0>: RX Buffer Mask for Filter 9 bits (same values as bit 15-12)   |

| bit 3-0  | F8BP<3:0>: RX Buffer Mask for Filter 8 bits (same values as bit 15-12)   |

| REGISTER     | 21-15:                                        | CXBU       | FPN14: ECA                           |                 | 12-15 BUFFE      | RPOINTER        | REGISTER 4      |       |

|--------------|-----------------------------------------------|------------|--------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| R/W-0        | R/\                                           | W-0        | R/W-0                                | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|              |                                               | F15BP      | 2<3:0>                               |                 |                  | F14E            | 3P<3:0>         |       |

| bit 15       |                                               |            |                                      |                 |                  |                 |                 | bit 8 |

| R/W-0        | R/                                            | W-0        | R/W-0                                | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|              |                                               | F13BP<3:0> |                                      |                 |                  |                 |                 |       |

| bit 7        |                                               |            |                                      |                 |                  |                 |                 | bit 0 |

|              |                                               |            |                                      |                 |                  |                 |                 |       |

| Legend:      |                                               |            |                                      |                 |                  |                 |                 |       |

| R = Readab   | le bit                                        |            | W = Writable                         | bit             | U = Unimplen     | nented bit, rea | ad as '0'       |       |

| -n = Value a | t POR                                         |            | '1' = Bit is set                     |                 | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

| bit 15-12    | F15BI                                         | P<3:0>:    | : RX Buffer Ma                       | sk for Filter 1 | 5 bits           |                 |                 |       |

|              | 1111 = Filter hits received in RX FIFO buffer |            |                                      |                 |                  |                 |                 |       |

|              | 1110                                          | = Filter   | hits received in                     | n RX Buffer 14  | 4                |                 |                 |       |

|              | •                                             |            |                                      |                 |                  |                 |                 |       |

|              | •                                             |            |                                      |                 |                  |                 |                 |       |

|              | •                                             |            |                                      |                 |                  |                 |                 |       |

|              |                                               |            | hits received in<br>hits received in |                 |                  |                 |                 |       |

|              |                                               |            |                                      |                 |                  |                 |                 |       |

### REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

| bit 11-8 | <b>F14BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 14 bits (same values as bit 15-12) |

|----------|---------------------------------------------------------------------------------------|

| bit 7-4  | F13BP<3:0>: RX Buffer Mask for Filter 13 bits (same values as bit 15-12)              |

bit 3-0 **F12BP<3:0>:** RX Buffer Mask for Filter 12 bits (same values as bit 15-12)

| REGISTER 21-22: | CxRXFUL1: ECANx RECEIVE BUFFER FULL REGISTER 1 |

|-----------------|------------------------------------------------|

|                 |                                                |

| r       |         |         |         |         |         |        |        |

|---------|---------|---------|---------|---------|---------|--------|--------|

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

| RXFUL7  | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1 | RXFUL0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                             |                    |  |  |

|-------------------|----------------------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read | l as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0                                                                  | R/C-0   | R/C-0            | R/C-0                                    | R/C-0                                   | R/C-0   | R/C-0   | R/C-0   |

|------------------------------------------------------------------------|---------|------------------|------------------------------------------|-----------------------------------------|---------|---------|---------|

| RXFUL31                                                                | RXFUL30 | RXFUL29          | RXFUL28                                  | RXFUL27                                 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15                                                                 |         |                  |                                          |                                         |         |         | bit 8   |

|                                                                        |         |                  |                                          |                                         |         |         |         |

| R/C-0                                                                  | R/C-0   | R/C-0            | R/C-0                                    | R/C-0                                   | R/C-0   | R/C-0   | R/C-0   |

| RXFUL23                                                                | RXFUL22 | RXFUL21          | RXFUL20                                  | RXFUL19                                 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7                                                                  |         |                  |                                          |                                         | bit 0   |         |         |

|                                                                        |         |                  |                                          |                                         |         |         |         |

| Legend: C = Writable bit, but only '0' can be written to clear the bit |         |                  |                                          |                                         |         |         |         |

| R = Readable bit W                                                     |         | W = Writable     | e bit U = Unimplemented bit, read as '0' |                                         |         |         |         |

| -n = Value at POR                                                      |         | '1' = Bit is set |                                          | '0' = Bit is cleared x = Bit is unknown |         |         | nown    |

bit 15-0 **RXFUL<31:16>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

# 27.3 Programmable CRC Registers

| REGISTER 2      | 7-1: CRUU                                                                                                                                                                      | UN1: CRC C                                         |                | EGISTER          |                 |                 |                |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------|------------------|-----------------|-----------------|----------------|--|--|

| R/W-0           | U-0                                                                                                                                                                            | R/W-0                                              | R-0            | R-0              | R-0             | R-0             | R-0            |  |  |

| CRCEN           |                                                                                                                                                                                | – CSIDL VWORD<4:0>                                 |                |                  |                 |                 |                |  |  |

| bit 15          |                                                                                                                                                                                |                                                    | •              |                  |                 |                 | bit 8          |  |  |

|                 |                                                                                                                                                                                | <b>D</b> 444 0                                     | <b>D</b> 444 A | <b>D</b> 444 0   |                 |                 |                |  |  |

| R-0             | R-1                                                                                                                                                                            | R/W-0                                              | R/W-0          | R/W-0            | U-0             | U-0             | U-0            |  |  |

| CRCFUL          | JL CRCMPT CRCISEL CRCGO LENDIAN — —                                                                                                                                            |                                                    |                |                  |                 |                 |                |  |  |

| bit 7           |                                                                                                                                                                                |                                                    |                |                  |                 |                 | bit (          |  |  |

| Legend:         |                                                                                                                                                                                |                                                    |                |                  |                 |                 |                |  |  |

| R = Readable    | bit                                                                                                                                                                            | W = Writable                                       | bit            | U = Unimpler     | nented bit, rea | d as '0'        |                |  |  |

| -n = Value at F | POR                                                                                                                                                                            | '1' = Bit is set                                   |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown           |  |  |

|                 |                                                                                                                                                                                |                                                    |                |                  |                 |                 |                |  |  |

| bit 15          | 0 = CRC mo                                                                                                                                                                     | dule is enabled                                    |                | ichines, pointer | s and CRCWI     | DAT/CRCDAT a    | re reset; othe |  |  |

| bit 14          | Unimplemen                                                                                                                                                                     | ted: Read as '                                     | 0'             |                  |                 |                 |                |  |  |

| bit 13          | CSIDL: CRC                                                                                                                                                                     | Stop in Idle Mo                                    | ode bit        |                  |                 |                 |                |  |  |

|                 | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                        |                                                    |                |                  |                 |                 |                |  |  |

| bit 12-8        | VWORD<4:0                                                                                                                                                                      | >: Pointer Valu                                    | e bits         |                  |                 |                 |                |  |  |

|                 | Indicates the<br>16 when PLE                                                                                                                                                   |                                                    | d words in the | FIFO. Has a n    | naximum value   | e of 8 when PLE | N<4:0> > 7 oi  |  |  |

| bit 7           | CRCFUL: FIF                                                                                                                                                                    | CRCFUL: FIFO Full bit                              |                |                  |                 |                 |                |  |  |

|                 | 1 = FIFO is for<br>0 = FIFO is n                                                                                                                                               |                                                    |                |                  |                 |                 |                |  |  |

| bit 6           | CRCMPT: FIF                                                                                                                                                                    |                                                    |                |                  |                 |                 |                |  |  |

|                 | 1 = FIFO is empty                                                                                                                                                              |                                                    |                |                  |                 |                 |                |  |  |

|                 | 0 = FIFO is not empty                                                                                                                                                          |                                                    |                |                  |                 |                 |                |  |  |

| bit 5           | CRCISEL: CRC Interrupt Selection bit                                                                                                                                           |                                                    |                |                  |                 |                 |                |  |  |

|                 | <ul> <li>1 = Interrupt on FIFO is empty; final word of data is still shifting through CRC</li> <li>0 = Interrupt on shift is complete and CRCWDAT results are ready</li> </ul> |                                                    |                |                  |                 |                 |                |  |  |

| bit 4           | CRCGO: Start CRC bit                                                                                                                                                           |                                                    |                |                  |                 |                 |                |  |  |

|                 | 1 = Starts CRC serial shifter                                                                                                                                                  |                                                    |                |                  |                 |                 |                |  |  |

|                 | 0 = CRC seri                                                                                                                                                                   | ial shifter is turr                                | ned off        |                  |                 |                 |                |  |  |

| bit 3           |                                                                                                                                                                                | LENDIAN: Data Word Little-Endian Configuration bit |                |                  |                 |                 |                |  |  |

|                 | 1 = Data word is shifted into the CRC starting with the LSb (little endian)                                                                                                    |                                                    |                |                  |                 |                 |                |  |  |

| hit 2-0         | <ul> <li>Data word is shifted into the CRC starting with the MSb (big endian)</li> <li>Unimplemented: Read as '0'</li> </ul>                                                   |                                                    |                |                  |                 |                 |                |  |  |

| bit 2-0         | ommplemen                                                                                                                                                                      | ieu. Nedu as                                       | J              |                  |                 |                 |                |  |  |

### REGISTER 27-1: CRCCON1: CRC CONTROL REGISTER 1