Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 83                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mu810-e-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 PRODUCT FAMILIES

The device names, pin counts, memory sizes and peripheral availability of each device are listed in Table 1. Their pinout diagrams appear on the following pages.

# TABLE 1: dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 CONTROLLER FAMILIES

|                   |            |               |                                                |                            |                               |               |                           | Re                                             | map | pable                       | Peri | ipher | als                                |                           |     |                                                             |      |       |                      |                                  |            |                      |          |

|-------------------|------------|---------------|------------------------------------------------|----------------------------|-------------------------------|---------------|---------------------------|------------------------------------------------|-----|-----------------------------|------|-------|------------------------------------|---------------------------|-----|-------------------------------------------------------------|------|-------|----------------------|----------------------------------|------------|----------------------|----------|

| Device            | suid       | Packages      | Program Flash Memory<br>(Kbyte) <sup>(1)</sup> | RAM (Kbyte) <sup>(2)</sup> | 16-Bit Timer <sup>(3,4)</sup> | Input Capture | Output Compare (with PWM) | Motor Control PWM<br>(Channels) <sup>(5)</sup> | GEI | UART with IrDA $^{\otimes}$ | IdS  | ECAN™ | External Interrupts <sup>(6)</sup> | DMA Controller (Channels) | DCI | Analog Comparators/<br>Inputs Per Comparator <sup>(7)</sup> | RTCC | I²Стм | <b>CRC Generator</b> | 10-Bit/12-Bit ADC <sup>(8)</sup> | <b>BSU</b> | Parallel Master Port | I/O Pins |

| dsPIC33EP256MU806 | 64         | QFN,<br>TQFP  | 280                                            | 28                         | 9                             | 16            | 16                        | 8                                              | 2   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>24 ch                  | 1          | Y                    | 51       |

| dsPIC33EP256MU810 | 100<br>121 | TQFP<br>TFBGA | 280                                            | 28                         | 9                             | 16            | 16                        | 12                                             | 2   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>32 ch                  | 1          | Y                    | 83       |

| dsPIC33EP256MU814 | 144        | TQFP,<br>LQFP | 280                                            | 28                         | 9                             | 16            | 16                        | 14                                             | 2   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>32 ch                  | 1          | Y                    | 122      |

| dsPIC33EP512GP806 | 64         | QFN,<br>TQFP  | 536                                            | 52                         | 9                             | 16            | 16                        | _                                              | _   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>24 ch                  | _          | Y                    | 53       |

| dsPIC33EP512MC806 | 64         | QFN,<br>TQFP  | 536                                            | 52                         | 9                             | 16            | 16                        | 8                                              | 2   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>24 ch                  | _          | Y                    | 53       |

| dsPIC33EP512MU810 | 100<br>121 | TQFP<br>TFBGA | 536                                            | 52                         | 9                             | 16            | 16                        | 12                                             | 2   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>32 ch                  | 1          | Y                    | 83       |

| dsPIC33EP512MU814 | 144        | TQFP,<br>LQFP | 536                                            | 52                         | 9                             | 16            | 16                        | 14                                             | 2   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>32 ch                  | 1          | Y                    | 122      |

| PIC24EP256GU810   | 100<br>121 | TQFP<br>TFBGA | 280                                            | 28                         | 9                             | 16            | 16                        | 0                                              | 0   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>32 ch                  | 1          | Y                    | 83       |

| PIC24EP256GU814   | 144        | TQFP,<br>LQFP | 280                                            | 28                         | 9                             | 16            | 16                        | 0                                              | 0   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>32 ch                  | 1          | Y                    | 122      |

| PIC24EP512GP806   | 64         | QFN,<br>TQFP  | 586                                            | 52                         | 9                             | 16            | 16                        | _                                              | _   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>24 ch                  | _          | Y                    | 53       |

| PIC24EP512GU810   | 100<br>121 | TQFP<br>TFBGA | 536                                            | 52                         | 9                             | 16            | 16                        | 0                                              | 0   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>32 ch                  | 1          | Y                    | 83       |

| PIC24EP512GU814   | 144        | TQFP,L<br>QFP | 536                                            | 52                         | 9                             | 16            | 16                        | 0                                              | 0   | 4                           | 4    | 2     | 5                                  | 15                        | 1   | 3/4                                                         | 1    | 2     | 1                    | 2 ADC,<br>32 ch                  | 1          | Y                    | 122      |

Note 1: Flash size is inclusive of 24 Kbytes of auxiliary Flash. Auxiliary Flash supports simultaneous code execution and self-erase/programming. Refer to Section 5. "Flash Programming" (DS70609) in the "dsPIC33E/PIC24E Family Reference Manual".

2: RAM size is inclusive of 4 Kbytes of DMA RAM (DPSRAM) for all devices.

3: Up to eight of these timers can be combined into four 32-bit timers.

4: Eight out of nine timers are remappable.

5: PWM Faults and Sync signals are remappable.

**6**: Four out of five interrupts are remappable.

7: Comparator output is remappable.

8: The ADC2 module supports 10-bit mode only.

|                | • · . | ••••••   | .,     | -, 0/    |        |        |        |                         |                        |             |          |       |              | -        | _     |        | -     |               |

|----------------|-------|----------|--------|----------|--------|--------|--------|-------------------------|------------------------|-------------|----------|-------|--------------|----------|-------|--------|-------|---------------|

| File Name      | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9                   | Bit 8                  | Bit 7       | Bit 6    | Bit 5 | Bit 4        | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE         | 0220  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN<                    | <1:0>                  | WAKE        | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA          | 0222  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF                   | TRMT                   | URXIS       | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG        | 0224  | _        | _      | _        | _      | —      | _      | _                       |                        |             |          | UART  | k Transmit F | Register |       |        |       | XXXX          |

| U1RXREG        | 0226  | _        | _      | _        |        | —      | _      | —                       |                        |             |          | UART  | xReceive R   | egister  |       |        |       | 0000          |

| U1BRG          | 0228  |          |        |          |        |        |        | Baud                    | Rate Gen               | erator Pres | scaler   |       |              |          |       |        |       | 0000          |

| U2MODE         | 0230  | UARTEN   |        | USIDL    | IREN   | RTSMD  | —      | UEN<                    | <1:0>                  | WAKE        | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA          | 0232  | UTXISEL1 | UTXINV | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF                   | TRMT                   | URXIS       | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG        | 0234  | —        |        |          |        | —      | —      | UARTx Transmit Register |                        |             |          |       |              |          | XXXX  |        |       |               |

| U2RXREG        | 0236  | _        |        |          |        | —      | _      | _                       | UARTx Receive Register |             |          |       |              |          | 0000  |        |       |               |

| U2BRG          | 0238  |          |        |          |        |        |        | Baud                    | Rate Gen               | erator Pres | scaler   |       |              |          |       |        |       | 0000          |

| U3MODE         | 0250  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | —      | UEN<                    | <1:0>                  | WAKE        | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U3STA          | 0252  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF                   | TRMT                   | URXIS       | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |

| <b>U3TXREG</b> | 0254  | —        | _      | _        | _      | —      | _      | —                       |                        |             |          | UART  | x Transmit F | Register |       |        |       | xxxx          |

| <b>U3RXREG</b> | 0256  | —        | —      | —        | —      | —      | _      |                         |                        |             |          | UART  | x Receive R  | legister |       |        |       | 0000          |

| U3BRG          | 0258  |          |        |          |        |        |        | Baud                    | Rate Gen               | erator Pres | scaler   | -     | -            |          |       |        | -     | 0000          |

| U4MODE         | 02B0  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN<                    | <1:0>                  | WAKE        | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U4STA          | 02B2  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF                   | TRMT                   | URXIS       | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |

| U4TXREG        | 02B4  | _        | _      | _        | _      | _      | _      | _                       |                        |             |          | UART  | k Transmit F | Register |       |        |       | xxxx          |

| U4RXREG        | 02B6  | _        | _      | —        | _      | -      | _      | —                       |                        |             |          | UART  | x Receive R  | legister |       |        |       | 0000          |

| U4BRG          | 02B8  |          |        |          |        |        |        | Baud                    | Rate Gen               | erator Pres | scaler   |       |              |          |       |        |       | 0000          |

|                |       |          |        |          |        |        |        |                         |                        |             |          |       |              |          |       |        |       |               |

#### TABLE 4-23: UART1, UART2, UART3 and UART4 REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-25: ADC1 and ADC2 REGISTER MAP (CONTINUED)

| File Name | Addr. | Bit 15 | Bit 14                 | Bit 13                | Bit 12  | Bit 11 | Bit 10          | Bit 9   | Bit 8       | Bit 7    | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|--------|------------------------|-----------------------|---------|--------|-----------------|---------|-------------|----------|-----------|-------|-------|--------|-----------|---------|---------|---------------|

| ADC2BUF9  | 0352  |        |                        |                       |         |        |                 |         | ADCx Data E | Buffer 9 |           |       |       |        |           |         |         | XXXX          |

| ADC2BUFA  | 0354  |        | ADCx Data Buffer 10 xx |                       |         |        |                 |         |             | XXXX     |           |       |       |        |           |         |         |               |

| ADC2BUFB  | 0356  |        | ADCx Data Buffer 11 xx |                       |         |        |                 |         |             | XXXX     |           |       |       |        |           |         |         |               |

| ADC2BUFC  | 0358  |        | ADCx Data Buffer 12 xx |                       |         |        |                 |         |             | XXXX     |           |       |       |        |           |         |         |               |

| ADC2BUFD  | 035A  |        |                        | ADCx Data Buffer 13 x |         |        |                 |         |             |          | XXXX      |       |       |        |           |         |         |               |

| ADC2BUFE  | 035C  |        |                        |                       |         |        |                 |         | ADCx Data B | uffer 14 |           |       |       |        |           |         |         | XXXX          |

| ADC2BUFF  | 035E  |        |                        |                       |         |        |                 |         | ADCx Data B | uffer 15 |           |       |       |        |           |         |         | XXXX          |

| AD2CON1   | 0360  | ADON   | _                      | ADSIDL                | ADDMABM | —      |                 | FOR     | M<1:0>      | 5        | SSRC<2:0> | •     | SSRCG | SIMSAM | ASAM      | SAMP    | DONE    | 0000          |

| AD2CON2   | 0362  | Ň      | VCFG<2:0               | >                     | —       | —      | CSCNA           | CHP     | S<1:0>      | BUFS     |           |       | SMP   | l<3:0> |           | BUFM    | ALTS    | 0000          |

| AD2CON3   | 0364  | ADRC   |                        |                       |         |        | SAMC<4:0        | >       |             |          |           |       | ADCS  | S<7:0> |           |         |         | 0000          |

| AD2CHS123 | 0366  | —      |                        | _                     | _       | _      | CH123N          | NB<1:0> | CH123SB     |          | _         | _     | _     | _      | CH123N    | IA<1:0> | CH123SA | 0000          |

| AD2CHS0   | 0368  | CH0NB  |                        | _                     |         |        | CH0SB<4:0> CH0N |         |             |          | _         | _     |       | (      | CH0SA<4:0 | >       |         | 0000          |

| AD2CSSL   | 0270  | CSS15  | CSS14                  | CSS13                 | CSS12   | CSS11  | CSS10           | CSS9    | CSS8        | CSS7     | CSS6      | CSS5  | CSS4  | CSS3   | CSS2      | CSS1    | CSS0    | 0000          |

| AD2CON4   | 0272  | —      | _                      | ADDMAEN DMABL<2:0>    |         |        |                 |         |             |          | 0000      |       |       |        |           |         |         |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are not available on dsPIC33EP256MU806 devices.

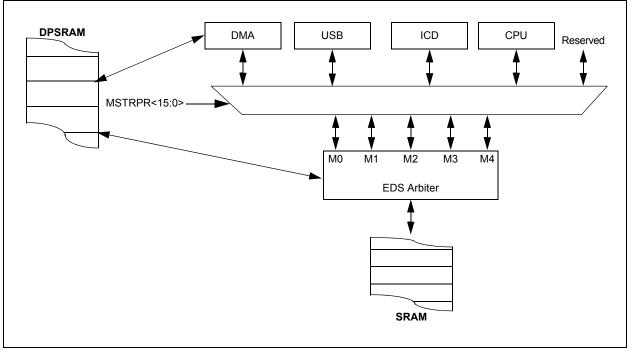

#### 4.4.3 EDS ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA, the USB module and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus masters (USB and DMA Controllers) are allocated to M2 and M3,

respectively (M1 is reserved and cannot be used). The user application may raise or lower the priority of the masters to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-74.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization, or dynamically in response to real-time events.

| Priority     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |          |          |  |  |  |  |  |  |

|--------------|-----------------------------------------|----------|----------|----------|--|--|--|--|--|--|

| Priority     | 0x0000                                  | 0x0008   | 0x0020   | 0x0028   |  |  |  |  |  |  |

| M0 (highest) | CPU                                     | USB      | DMA      | USB      |  |  |  |  |  |  |

| M1           | Reserved                                | CPU      | CPU      | DMA      |  |  |  |  |  |  |

| M2           | USB                                     | Reserved | Reserved | CPU      |  |  |  |  |  |  |

| М3           | DMA                                     | DMA      | USB      | Reserved |  |  |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      | ICD      | ICD      |  |  |  |  |  |  |

#### TABLE 4-74: EDS BUS ARBITER PRIORITY

Note 1: All other values of MSTRPR<15:0> are reserved.

## FIGURE 4-8: EDS ARBITER ARCHITECTURE

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/ 810/814 and PIC24EPXXX(GP/GU)810/ 814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70609) of the "dsPIC33E/ PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33EPXXX(GP/MC/MU)806/810/ 814 and PIC24EPXXX(GP/GU)810/814 device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user application can write program memory data either in blocks or 'rows' of 128 instructions (384 bytes) at a time or a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

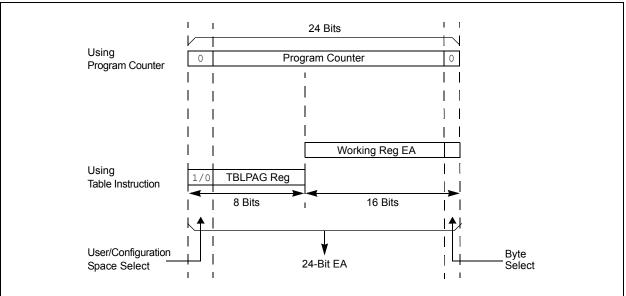

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| TABLE 7-1: | INTERRUPT VECTOR DETAILS ( | CONTINUED) |

|------------|----------------------------|------------|

|            |                            |            |

| Interrupt Source                        | Vector  |         | IVT               | Interrupt Bit Location |          |             |  |  |

|-----------------------------------------|---------|---------|-------------------|------------------------|----------|-------------|--|--|

| Interrupt Source                        | #       | IRQ #   | Address           | Flag                   | Enable   | Priority    |  |  |

| USB1 – USB OTG Interrupt <sup>(2)</sup> | 94      | 86      | 0x0000C0          | IFS5<6>                | IEC5<6>  | IPC21<10:8> |  |  |

| U4E – UART4 Error Interrupt             | 95      | 87      | 0x0000C2          | IFS5<7>                | IEC5<7>  | IPC21<14:12 |  |  |

| U4RX – UART4 Receiver                   | 96      | 88      | 0x0000C4          | IFS5<8>                | IEC5<8>  | IPC22<2:0>  |  |  |

| U4TX – UART4 Transmitter                | 97      | 89      | 0x0000C6          | IFS5<9>                | IEC5<9>  | IPC22<6:4>  |  |  |

| SPI3E – SPI3 Error                      | 98      | 90      | 0x0000C8          | IFS5<10>               | IEC5<10> | IPC22<10:8> |  |  |

| SPI3 – SPI3 Transfer Done               | 99      | 91      | 0x0000CA          | IFS5<11>               | IEC5<11> | IPC22<14:12 |  |  |

| OC9 – Output Compare 9                  | 100     | 92      | 0x0000CC          | IFS5<12>               | IEC5<12> | IPC23<2:0>  |  |  |

| IC9 – Input Capture 9                   | 101     | 93      | 0x0000CE          | IFS5<13>               | IEC5<13> | IPC23<6:4>  |  |  |

| PWM1 – PWM Generator 1 <sup>(1)</sup>   | 102     | 94      | 0x0000D0          | IFS5<14>               | IEC5<14> | IPC23<10:8> |  |  |

| PWM2 – PWM Generator 2 <sup>(1)</sup>   | 103     | 95      | 0x0000D2          | IFS5<15>               | IEC5<15> | IPC23<14:12 |  |  |

| PWM3 – PWM Generator 3 <sup>(1)</sup>   | 104     | 96      | 0x0000D4          | IFS6<0>                | IEC6<0>  | IPC24<2:0>  |  |  |

| PWM4 – PWM Generator 4 <sup>(1)</sup>   | 105     | 97      | 0x0000D6          | IFS6<1>                | IEC6<1>  | IPC24<6:4>  |  |  |

| PWM5 – PWM Generator 5 <sup>(1)</sup>   | 106     | 98      | 0x0000D8          | IFS6<2>                | IEC6<2>  | IPC24<10:8> |  |  |

| PWM6 – PWM Generator 6 <sup>(1)</sup>   | 107     | 99      | 0x0000DA          | IFS6<3>                | IEC6<3>  | IPC24<14:12 |  |  |

| PWM7 – PWM Generator 7 <sup>(1)</sup>   | 108     | 100     | 0x0000DC          | IFS6<4>                | IEC6<4>  | IPC25<2:0>  |  |  |

| Reserved                                | 109-125 | 101-117 | 0x0000DE-0x0000FC | _                      | _        | _           |  |  |

| DMA8 – DMA Channel 8                    | 126     | 118     | 0x000100          | IFS7<6>                | IEC7<6>  | IPC29<10:8> |  |  |

| DMA9 – DMA Channel 9                    | 127     | 119     | 0x000102          | IFS7<7>                | IEC7<7>  | IPC29<14:12 |  |  |

| DMA10 – DMA Channel 10                  | 128     | 120     | 0x000104          | IFS7<8>                | IEC7<8>  | IPC30<2:0>  |  |  |

| DMA11 – DMA Channel 11                  | 129     | 121     | 0x000106          | IFS7<9>                | IEC7<9>  | IPC30<6:4>  |  |  |

| SPI4E – SPI4 Error                      | 130     | 122     | 0x000108          | IFS7<10>               | IEC7<10> | IPC30<10:8> |  |  |

| SPI4 – SPI4 Transfer Done               | 131     | 123     | 0x00010A          | IFS7<11>               | IEC7<11> | IPC30<14:12 |  |  |

| OC10 – Output Compare 10                | 132     | 124     | 0x00010C          | IFS7<12>               | IEC7<12> | IPC31<2:0>  |  |  |

| IC10 – Input Capture 10                 | 133     | 125     | 0x00010E          | IFS7<13>               | IEC7<13> | IPC31<6:4>  |  |  |

| OC11 – Output Compare11                 | 134     | 126     | 0x000110          | IFS7<14>               | IEC7<14> | IPC31<10:8> |  |  |

| IC11 – Input Capture 11                 | 135     | 127     | 0x000112          | IFS7<15>               | IEC7<15> | IPC31<14:12 |  |  |

| OC12 – Output Compare 12                | 136     | 128     | 0x000114          | IFS8<0>                | IEC8<0>  | IPC32<2:0>  |  |  |

| IC12 – Input Capture 12                 | 137     | 129     | 0x000116          | IFS8<1>                | IEC8<1>  | IPC32<6:4>  |  |  |

| DMA12 – DMA Channel 12                  | 138     | 130     | 0x000118          | IFS8<2>                | IEC8<2>  | IPC32<10:8> |  |  |

| DMA13– DMA Channel 13                   | 139     | 131     | 0x00011A          | IFS8<3>                | IEC8<3>  | IPC32<14:12 |  |  |

| DMA14 – DMA Channel 14                  | 140     | 132     | 0x00011C          | IFS8<4>                | IEC8<4>  | IPC33<2:0>  |  |  |

| Reserved                                | 141     | 133     | 0x00011E          | —                      | _        | —           |  |  |

| OC13 – Output Compare 13                | 142     | 134     | 0x000120          | IFS8<6>                | IEC8<6>  | IPC33<10:8> |  |  |

| IC13 – Input Capture 13                 | 143     | 135     | 0x000122          | IFS8<7>                | IEC8<7>  | IPC33<14:12 |  |  |

| OC14 – Output Compare14                 | 144     | 136     | 0x000124          | IFS8<8>                | IEC8<8>  | IPC34<2:0>  |  |  |

| IC14 – Input Capture 14                 | 145     | 137     | 0x000126          | IFS8<9>                | IEC8<9>  | IPC34<6:4>  |  |  |

| OC15 – Output Compare 15                | 146     | 138     | 0x000128          | IFS8<10>               | IEC8<10> | IPC34<10:8> |  |  |

| IC15 – Input Capture 15                 | 147     | 139     | 0x00012A          | IFS8<11>               | IEC8<11> | IPC34<14:12 |  |  |

| OC16 – Output Compare 16                | 148     | 140     | 0x00012C          | IFS8<12>               | IEC8<12> | IPC35<2:0>  |  |  |

| IC16 – Input Capture 16                 | 149     | 141     | 0x00012E          | IFS8<13>               | IEC8<13> | IPC35<6:4>  |  |  |

| ICD – ICD Application                   | 150     | 142     | 0x000130          | IFS8<14>               | IEC8<14> | IPC35<10:8> |  |  |

| IOD - IOD Application                   |         |         |                   |                        |          |             |  |  |

Note 1: This interrupt source is available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

2: This interrupt source is available on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices only.

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| U-0             | U-0                                                                                                                            | U-0                                         | U-0   | U-0                                     | U-0              | U-0    | U-0   |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------|-----------------------------------------|------------------|--------|-------|--|--|--|--|

| —               | —                                                                                                                              | —                                           | —     | —                                       | —                | —      | —     |  |  |  |  |

| bit 15          |                                                                                                                                |                                             |       |                                         |                  |        | bit 8 |  |  |  |  |

|                 |                                                                                                                                |                                             |       |                                         |                  |        |       |  |  |  |  |

| U-0             | R/W-0                                                                                                                          | R/W-0                                       | R/W-0 | U-0                                     | U-0              | U-0    | U-0   |  |  |  |  |

| —               | UAE                                                                                                                            | DAE                                         | DOOVR | —                                       | —                | —      | —     |  |  |  |  |

| bit 7           |                                                                                                                                |                                             |       |                                         |                  |        | bit 0 |  |  |  |  |

|                 |                                                                                                                                |                                             |       |                                         |                  |        |       |  |  |  |  |

| Legend:         |                                                                                                                                |                                             |       |                                         |                  |        |       |  |  |  |  |

| R = Readable    | bit                                                                                                                            | W = Writable                                | bit   | U = Unimple                             | mented bit, read | as '0' |       |  |  |  |  |

| -n = Value at F | POR                                                                                                                            | '1' = Bit is set                            | :     | '0' = Bit is cleared x = Bit is unknown |                  |        |       |  |  |  |  |

|                 |                                                                                                                                |                                             |       |                                         |                  |        |       |  |  |  |  |

| bit 15-7        | Unimplemen                                                                                                                     | Unimplemented: Read as '0'                  |       |                                         |                  |        |       |  |  |  |  |

| bit 6           | UAE: USB Address Error Soft Trap Status bit                                                                                    |                                             |       |                                         |                  |        |       |  |  |  |  |

|                 | <ul> <li>1 = USB address error (soft) trap has occurred</li> <li>0 = USB address error (soft) trap has not occurred</li> </ul> |                                             |       |                                         |                  |        |       |  |  |  |  |

| bit E           |                                                                                                                                |                                             |       |                                         |                  |        |       |  |  |  |  |

| bit 5           |                                                                                                                                | DAE: DMA Address Error Soft Trap Status bit |       |                                         |                  |        |       |  |  |  |  |

|                 |                                                                                                                                |                                             |       |                                         |                  |        |       |  |  |  |  |

#### REGISTER 7-5: INTCON3: INTERRUPT CONTROL REGISTER 3

| bit 0    |                                                                                                                            |

|----------|----------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = DMA address error soft trap has occurred</li> <li>0 = DMA address error soft trap has not occurred</li> </ul> |

| bit 4    | DOOVR: Do Stack Overflow Soft Trap Status bit                                                                              |

|          | <ul> <li>1 = Do stack overflow soft trap has occurred</li> <li>0 = Do stack overflow soft trap has not occurred</li> </ul> |

| 1.11.0.0 |                                                                                                                            |

bit 3-0 Unimplemented: Read as '0'

#### REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     |     |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| —       | —   | —   | —   | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     |     |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| Logonan           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

bit 15-1 Unimplemented: Read as '0'

bit 0 SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

#### **REGISTER 8-7:** DMAXPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>            |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PAD   | )<7:0>            |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplem      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-8: DMAXCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|----------------------|-------|-------|

| —      | _   |       |       | CNT<  | 13:8> <sup>(2)</sup> |       |       |

| bit 15 |     |       |       |       |                      |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------------------|-------|-------|-------|

|       |       |       | CNT<  | 7:0> <sup>(2)</sup> |       |       |       |

| bit 7 |       |       |       |                     |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V on a 5V tolerant pin) by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification for that pin.

See the **"Pin Diagrams"** section for the available pins and their functionality.

### 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default. Refer to the Pinout I/O Descriptions (Table 1-1 in **Section 1.0 "Device Overview"**) for the complete list of analog pins.

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the pins defined as Analog in Table 1-1 in **Section 1.0 "Device Overview"**) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP, as shown in Example 11-1.

## 11.3 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

Note: Pull-ups and pull-downs on change notification pins should always be disabled when the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | OxFF00, WO | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | WO, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

| U-0          | R/W-0        | R/W-0                                                               | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0    |

|--------------|--------------|---------------------------------------------------------------------|---------------|------------------|-----------------|-----------------|----------|

| _            |              |                                                                     |               | DTCMP1R<6:0      | )>              |                 |          |

| bit 15       |              |                                                                     |               |                  |                 |                 | bit 8    |

|              |              |                                                                     |               |                  |                 |                 |          |

| U-0          | R/W-0        | R/W-0                                                               | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0    |

| —            |              |                                                                     |               | SYNCI2R<6:0      | >               |                 |          |

| bit 7        |              |                                                                     |               |                  |                 |                 | bit 0    |

|              |              |                                                                     |               |                  |                 |                 |          |

| Legend:      |              |                                                                     |               |                  |                 |                 |          |

| R = Readab   | le bit       | W = Writable                                                        | bit           | U = Unimpler     | nented bit, rea | ad as '0'       |          |

| -n = Value a | t POR        | '1' = Bit is set                                                    |               | '0' = Bit is cle | ared            | x = Bit is unkr | nown     |

|              |              | nput tied to RP1<br>nput tied to CMI<br>nput tied to Vss            | P1            |                  |                 |                 |          |

| bit 7        | Unimpleme    | nted: Read as '                                                     | )'            |                  |                 |                 |          |

| bit 6-0      | (see Table 1 | : <b>0&gt;:</b> Assign PWI<br>I-2 for input pin<br>nput tied to RP1 | selection nun |                  | the Correspo    | nding RPn/RPIr  | Pin bits |

|              | 0000001 =    | ,<br>nput tied to CMI<br>nput tied to Vss                           | ⊃1            |                  |                 |                 |          |

## REGISTER 11-38: RPINR38: PERIPHERAL PIN SELECT INPUT REGISTER 38

## 13.2 Timerx/y Control Registers

| R/W-0        | U-0                                                                         | R/W-0                      | U-0             | U-0               | U-0            | U-0                | U-0 |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------|----------------------------|-----------------|-------------------|----------------|--------------------|-----|--|--|--|--|--|

| TON          |                                                                             | TSIDL                      | _               |                   | —              | _                  | _   |  |  |  |  |  |

| pit 15       |                                                                             |                            |                 |                   |                |                    | bit |  |  |  |  |  |

| U-0          | R/W-0                                                                       | R/W-0                      | R/W-0           | R/W-0             | U-0            | R/W-0              | U-0 |  |  |  |  |  |

| 0-0          | TGATE                                                                       | I                          | S<1:0>          | T32               | 0-0            | TCS <sup>(1)</sup> | 0-0 |  |  |  |  |  |

| <br>bit 7    | IGAIE                                                                       | ICKE                       | 5~1.0~          | 132               | _              | 10307              |     |  |  |  |  |  |

|              |                                                                             |                            |                 |                   |                |                    | bit |  |  |  |  |  |

| Legend:      |                                                                             |                            |                 |                   |                |                    |     |  |  |  |  |  |

| R = Readable | e bit                                                                       | W = Writable               | bit             | U = Unimplem      | ented bit, rea | d as '0'           |     |  |  |  |  |  |

| n = Value at | POR                                                                         | '1' = Bit is set           |                 | '0' = Bit is clea | ared           | x = Bit is unkno   | own |  |  |  |  |  |

| bit 15       | TON: Timerx                                                                 | On hit                     |                 |                   |                |                    |     |  |  |  |  |  |

| 511 15       | When T32 = $2$                                                              |                            |                 |                   |                |                    |     |  |  |  |  |  |

|              | $\frac{\text{Vnen } 132 = 1:}{1 = \text{Starts } 32 - \text{bit Timerx/y}}$ |                            |                 |                   |                |                    |     |  |  |  |  |  |

|              |                                                                             | 0 = Stops 32-bit Timerx/y  |                 |                   |                |                    |     |  |  |  |  |  |

|              | $\frac{\text{When T32 = 0:}}{1 = \text{Starts 16-bit Timerx}}$              |                            |                 |                   |                |                    |     |  |  |  |  |  |

|              | 1 = Starts 16-<br>0 = Stops 16-                                             |                            |                 |                   |                |                    |     |  |  |  |  |  |

| oit 14       | -                                                                           | Unimplemented: Read as '0' |                 |                   |                |                    |     |  |  |  |  |  |

| bit 13       | TSIDL: Timer                                                                | x Stop in Idle I           | Node bit        |                   |                |                    |     |  |  |  |  |  |

|              | 1 = Discontinues module operation when device enters Idle mode              |                            |                 |                   |                |                    |     |  |  |  |  |  |

|              |                                                                             | s module opera             |                 | ode               |                |                    |     |  |  |  |  |  |

| bit 12-7     | -                                                                           | ted: Read as '             |                 |                   |                |                    |     |  |  |  |  |  |

| bit 6        |                                                                             | erx Gated Time             | Accumulatio     | n Enable bit      |                |                    |     |  |  |  |  |  |

|              | <u>When TCS = 1:</u><br>This bit is ignored.                                |                            |                 |                   |                |                    |     |  |  |  |  |  |

|              | When $TCS = 0$ :                                                            |                            |                 |                   |                |                    |     |  |  |  |  |  |

|              | 1 = Gated time accumulation is enabled                                      |                            |                 |                   |                |                    |     |  |  |  |  |  |

|              |                                                                             | e accumulatio              |                 |                   |                |                    |     |  |  |  |  |  |

| bit 5-4      |                                                                             | : Timerx Input             | Clock Presca    | le Select bits    |                |                    |     |  |  |  |  |  |

|              | 11 = 1:256                                                                  |                            |                 |                   |                |                    |     |  |  |  |  |  |

|              | 10 = 1:64<br>01 = 1:8                                                       |                            |                 |                   |                |                    |     |  |  |  |  |  |

|              | 00 = 1:1                                                                    |                            |                 |                   |                |                    |     |  |  |  |  |  |

| bit 3        | <b>T32:</b> 32-Bit Ti                                                       | mer Mode Sel               | ect bit         |                   |                |                    |     |  |  |  |  |  |

|              | 1 = Timerx and Timery form a single 32-bit timer                            |                            |                 |                   |                |                    |     |  |  |  |  |  |

|              | 0 = Timerx ar                                                               | id Timery act a            | is two 16-bit t | mers              |                |                    |     |  |  |  |  |  |

| bit 2        | •                                                                           | ted: Read as '             |                 |                   |                |                    |     |  |  |  |  |  |

| bit 1        |                                                                             | Clock Source S             |                 |                   |                |                    |     |  |  |  |  |  |

|              | 1 = External o<br>0 = Internal cl                                           | lock from TxC              | K pin (on the   | rising edge)      |                |                    |     |  |  |  |  |  |

|              |                                                                             |                            |                 |                   |                |                    |     |  |  |  |  |  |

## REGISTER 13-1: TxCON: (T2CON, T4CON, T6CON OR T8CON) CONTROL REGISTER

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

## 17.1 QEI Resources

Many useful resources related to QEI are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en554310

### 17.1.1 KEY RESOURCES

- Section 15. "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

| R/W-0         | R/W-0                                     | R/W-0                                | R/W-0         | R/W-0             | R/W-0             | R/W-0           | R/W-0         |  |  |  |

|---------------|-------------------------------------------|--------------------------------------|---------------|-------------------|-------------------|-----------------|---------------|--|--|--|

| ALRMEN        | CHIME                                     |                                      | AMA           | SK<3:0>           |                   | ALRMP           | FR<1:0>       |  |  |  |

| bit 15        | •                                         |                                      |               |                   |                   |                 | bit 8         |  |  |  |

|               |                                           | D/M/ 0                               |               |                   | D/M/ 0            |                 |               |  |  |  |

| R/W-0         | R/W-0                                     | R/W-0                                | R/W-0         | R/W-0<br>PT<7:0>  | R/W-0             | R/W-0           | R/W-0         |  |  |  |

| bit 7         |                                           |                                      |               | 1 \$1.05          |                   |                 | bit (         |  |  |  |

|               |                                           |                                      |               |                   |                   |                 |               |  |  |  |

| Legend:       |                                           |                                      |               |                   |                   |                 |               |  |  |  |

| R = Readable  | e bit                                     | W = Writable                         | bit           | U = Unimpler      | mented bit, read  | l as '0'        |               |  |  |  |

| -n = Value at | POR                                       | '1' = Bit is set                     |               | '0' = Bit is cle  | ared              | x = Bit is unkr | iown          |  |  |  |

|               |                                           |                                      |               |                   |                   |                 |               |  |  |  |

| bit 15        |                                           | larm Enable bit                      |               |                   |                   |                 |               |  |  |  |

|               | 1 = Alarm Is<br>CHIME                     | s enabled (clear                     | ed automatic  | ally after an ala | irm event when    | ever ARP1<7:(   | )> = 0x00 and |  |  |  |

|               | 0 = Alarm is                              | ,                                    |               |                   |                   |                 |               |  |  |  |

| bit 14        | CHIME: Chi                                | me Enable bit                        |               |                   |                   |                 |               |  |  |  |

|               | 1 = Chime i                               | s enabled; ARP                       | T<7:0> bits a | re allowed to ro  | ll over from 0x0  | 0 to 0xFF       |               |  |  |  |

|               | 0 = Chime i                               | s disabled; ARP                      | T<7:0> bits s | stop once they r  | each 0x00         |                 |               |  |  |  |

| bit 13-10     | AMASK<3:0>: Alarm Mask Configuration bits |                                      |               |                   |                   |                 |               |  |  |  |

|               | 0000 = Every half second                  |                                      |               |                   |                   |                 |               |  |  |  |

|               | 0001 = Eve                                | •                                    |               |                   |                   |                 |               |  |  |  |

|               | 0010 = Eve<br>0011 = Eve                  | ry 10 seconds                        |               |                   |                   |                 |               |  |  |  |

|               |                                           | ry 10 minutes                        |               |                   |                   |                 |               |  |  |  |

|               | 0101 <b>= Eve</b>                         |                                      |               |                   |                   |                 |               |  |  |  |

|               | 0110 <b>= Onc</b>                         | •                                    |               |                   |                   |                 |               |  |  |  |

|               | 0111 <b>= Onc</b>                         |                                      |               |                   |                   |                 |               |  |  |  |

|               | 1000 = Onc                                |                                      | when config   | urad for Eabrua   | ny 20th anao a    |                 |               |  |  |  |

|               |                                           | e a year (except<br>erved – do not u |               |                   | iry 29th, once e  | very 4 years)   |               |  |  |  |

|               |                                           | erved – do not u                     |               |                   |                   |                 |               |  |  |  |

| bit 9-8       | ALRMPTR<                                  | :1:0>: Alarm Val                     | ue Register \ | Vindow Pointer    | bits              |                 |               |  |  |  |

|               |                                           | e corresponding<br>1:0> value decre  |               |                   |                   |                 |               |  |  |  |

| bit 7-0       |                                           | : Alarm Repeat                       |               | -                 |                   |                 |               |  |  |  |

|               |                                           | -<br>Alarm will repe                 |               |                   |                   |                 |               |  |  |  |

|               | •                                         |                                      |               |                   |                   |                 |               |  |  |  |

|               | •                                         |                                      |               |                   |                   |                 |               |  |  |  |

|               | •                                         |                                      |               |                   |                   |                 |               |  |  |  |

|               | 00000000                                  | = Alarm will not r                   | epeat         |                   |                   |                 |               |  |  |  |

|               | The counter<br>0xFF unless                | decrements on                        | any alarm ev  | ent. The counte   | er is prevented f | rom rolling ove | r from 0x00 t |  |  |  |

#### REGISTER 26-3: ALCFGRPT: ALARM CONFIGURATION REGISTER

#### 32.1 DC Characteristics

#### TABLE 32-1: OPERATING MIPS VS. VOLTAGE

|                | Voo Bongo                 | Tomp Bongo            | Maximum MIPS                                                       |

|----------------|---------------------------|-----------------------|--------------------------------------------------------------------|

| Characteristic | VDD Range<br>(in Volts)   | Temp Range<br>(in °C) | dsPIC33EPXXX(GP/MC/MU)806/810/<br>814 and PIC24EPXXX(GP/GU)810/814 |

| _              | 2.95V-3.6V <sup>(1)</sup> | -40°C to +85°C        | 70                                                                 |

| —              | 2.95V-3.6V <sup>(1)</sup> | -40°C to +125°C       | 60                                                                 |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, Comparator and DAC will have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 32-11 for the minimum and maximum BOR values.

#### TABLE 32-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min. | Тур.        | Max. | Unit |

|---------------------------------------------------------------------------------------------|--------|------|-------------|------|------|

| Industrial Temperature Devices                                                              |        |      |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40  |             | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40  | —           | +85  | °C   |

| Extended Temperature Devices                                                                |        |      |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40  |             | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40  |             | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     |      | Pint + Pi/( | D    | W    |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$     |        |      |             |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (    | TJ – ΤΑ)/θ. | IA   | W    |

#### TABLE 32-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                       | Symbol | Тур. | Max. | Unit | Notes |

|------------------------------------------------------|--------|------|------|------|-------|

| Package Thermal Resistance, 64-pin QFN (9x9 mm)      | θJA    | 28   |      | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10 mm)   | θJA    | 47   | _    | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12 mm)  | θJA    | 43   | —    | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (14x14 mm)  | θJA    | 43   | _    | °C/W | 1     |

| Package Thermal Resistance, 121-pin TFBGA (10x10 mm) | θJA    | 40   | _    | °C/W | 1     |

| Package Thermal Resistance, 144-pin LQFP (20x20 mm)  | θJA    | 33   | —    | °C/W | 1     |

| Package Thermal Resistance, 144-pin TQFP (16x16 mm)  | θJA    | 33   | _    | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| <b>TABLE 32-17:</b> | PLL CI | OCK TIMING | SPECIFICATIONS |

|---------------------|--------|------------|----------------|

|---------------------|--------|------------|----------------|

| АС СНА | RACTERI | STICS                                                            |                   | erating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |     |     |     |                    |  |  |  |

|--------|---------|------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------------------|--|--|--|

| Param. | Symbol  | Characteris                                                      | tic               | Conditions                                                                                                                     |     |     |     |                    |  |  |  |

| OS50   | Fplli   | PLL Voltage Controll<br>Oscillator (VCO) Inpu<br>Frequency Range |                   | 0.8                                                                                                                            |     | 8.0 | MHz | ECPLL, XTPLL modes |  |  |  |

| OS51   | Fsys    | On-Chip VCO Syster<br>Frequency                                  |                   |                                                                                                                                | _   | 340 | MHz |                    |  |  |  |

| OS52   | TLOCK   | PLL Start-up Time (L                                             | Time (Lock Time)  |                                                                                                                                | 1.5 | 3.1 | mS  |                    |  |  |  |

| OS53   | DCLK    | CLKO Stability (Jitter                                           | ·) <sup>(2)</sup> | -5                                                                                                                             | 0.5 | 5   | %   |                    |  |  |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if FOSC = 120 MHz and the SPI bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

# TABLE 32-18: AUXILIARY PLL CLOCK TIMING SPECIFICATIONS (dsPIC33EPXXXMU8XX AND PIC24EPXXXGU8XX DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                                  | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |                     |      |       |                    |  |

|--------------------|--------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|--------------------|--|

| Param.             | Symbol | Characteristic                                                   |                                                                                                                                                                                                                                                                               | Min. | Typ. <sup>(1)</sup> | Max. | Units | Conditions         |  |