Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 83                                                                               |

| Program Memory Size        | 512КВ (170К х 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mu810-i-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Pin Diagrams (Continued)

| 121-     | 121-Pin TFBGA <sup>(1)</sup> |          |           |           |           |          |           |              |           |           |              |

|----------|------------------------------|----------|-----------|-----------|-----------|----------|-----------|--------------|-----------|-----------|--------------|

|          |                              |          |           |           |           | 33EP250  |           |              |           |           |              |

|          | 1                            | 2        | 3         | 4         | 5         | 6        | 7         | 8            | 9         | 10        | 11           |

| <b>A</b> | O<br>RE4                     | O<br>RE3 | RG13      | O<br>RE0  | RG0       | RF1      |           | NC           | RD12      | RD2       | RD1          |

| 3        | NC                           | RG15     | O<br>RE2  | O<br>RE1  | O<br>RA7  | RF0      | O<br>VCAP | RD5          | RD3       | ⊖<br>Vss  | O<br>RC14    |

| c        | O<br>RE6                     |          | RG12      | RG14      | O<br>RA6  | NC       | O<br>RD7  | RD4          | NC        | O<br>RC13 | <b>R</b> D11 |

| D        | O<br>RC1                     | O<br>RE7 | O<br>RE5  | NC        | NC        | NC       | O<br>RD6  | RD13         | RD0       | NC        | RD10         |

| E        | O<br>RC4                     | C<br>RC3 | O<br>RG6  | O<br>RC2  | NC        | RG1      | NC        | RA15         | RD8       | RD9       | RA14         |

| F        | MCLR                         | O<br>RG8 | O<br>RG9  | O<br>RG7  | ⊖<br>Vss  | NC       | NC        |              | O<br>RC12 | ⊖<br>Vss  | O<br>RC15    |

| 3        | C<br>RE8                     | O<br>RE9 | RA0       | NC        | O<br>Vdd  | ⊖<br>Vss | ⊖<br>Vss  | NC           | RA5       | RA3       | RA4          |

| н        | O<br>RB5                     | O<br>RB4 | NC        | NC        | NC        | O<br>Vdd | NC        | <b>V</b> BUS | UUSB3V3   | O<br>RG2  | RA2          |

| J        | O<br>RB3                     | O<br>RB2 | O<br>RB7  | O<br>AVDD | O<br>RB11 | RA1      | O<br>RB12 | NC           | NC        | RF8       | O<br>RG3     |

| ĸ        | O<br>RB1                     | O<br>RB0 | O<br>RA10 | C<br>RB8  | NC        | RF12     | O<br>RB14 | O<br>VDD     | RD15      | RF3       | RF2          |

| -        | C<br>RB6                     | O<br>RA9 | )<br>AVss | O<br>RB9  | O<br>RB10 | RF13     | O<br>RB13 | O<br>RB15    | RD14      | RF4       | RF5          |

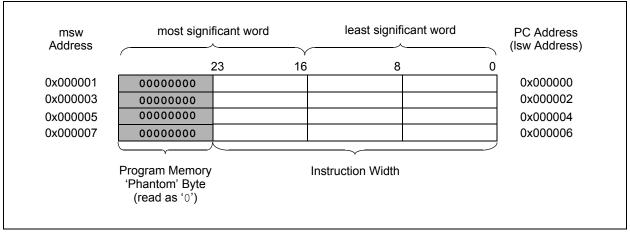

### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

## 4.1.2 INTERRUPT AND TRAP VECTORS

All devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address 0x000000 of the primary Flash memory or at address 0x7FFFFC of the auxiliary Flash memory, with the actual address for the start of code at address 0x000002 of the primary Flash memory or at address 0x7FFFFE of the auxiliary Flash memory. Reset Target Vector Select bit (RSTPRI) in the FPOR Configuration register controls whether primary or auxiliary Flash Reset location is used.

A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

## FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

NOTES:

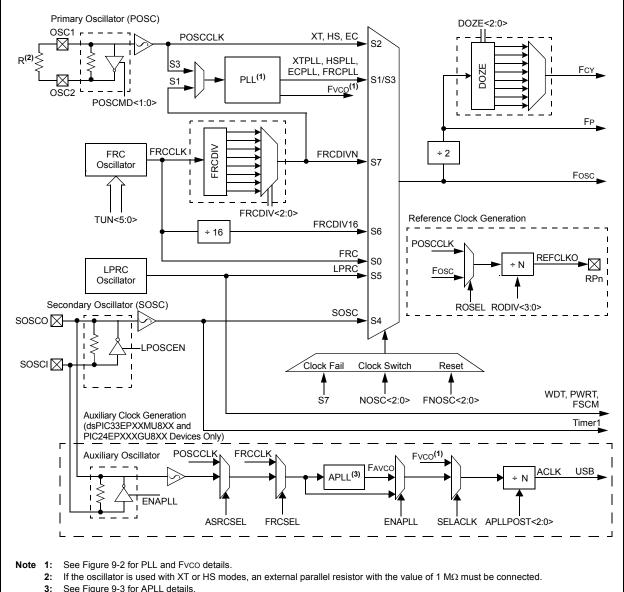

#### FIGURE 9-1: **OSCILLATOR SYSTEM DIAGRAM**

3: See Figure 9-3 for APLL details.

## REGISTER 11-30: RPINR30: PERIPHERAL PIN SELECT INPUT REGISTER 30

| U-0                                | U-0   | U-0              | U-0                                | U-0             | U-0   | U-0   | U-0   |

|------------------------------------|-------|------------------|------------------------------------|-----------------|-------|-------|-------|

| -                                  | —     | —                | _                                  | —               | —     | —     | —     |

| bit 15                             |       |                  |                                    |                 |       |       | bit 8 |

|                                    |       |                  |                                    |                 |       |       |       |

| U-0                                | R/W-0 | R/W-0            | R/W-0                              | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

| —                                  |       |                  |                                    | SS3R<6:0>       |       |       |       |

| bit 7                              | •     |                  |                                    |                 |       |       | bit 0 |

|                                    |       |                  |                                    |                 |       |       |       |

| Legend:                            |       |                  |                                    |                 |       |       |       |

| R = Readable bit W = Writable bit  |       |                  | U = Unimplemented bit, read as '0' |                 |       |       |       |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cle | ared                               | x = Bit is unkr | nown  |       |       |

| ·                                  |       |                  |                                    |                 |       |       |       |

## bit 15-7 Unimplemented: Read as '0'

bit 6-0

SS3R<6:0>: Assign SPI3 Slave Select Input (SS3) to the Corresponding RPn/RPIn Pin bits (see Table 11-2 for input pin selection numbers)

1111111 = Input tied to RP127

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

## REGISTER 11-49: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP84  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

|        |     |       |       |       |        |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| _      | _   |       |       | RP82  | R<5:0> |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

bit 7

| bit 13-8 | <b>RP84R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP84 Output Pin bits (see Table 11-3 for peripheral function numbers) |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7-6  | Unimplemented: Read as '0'                                                                                                               |

|          | RROOR (F.O. ) Design based Output Function is Assigned to RROO Output Dis hits                                                           |

bit 5-0 **RP82R<5:0>:** Peripheral Output Function is Assigned to RP82 Output Pin bits (see Table 11-3 for peripheral function numbers)

### REGISTER 11-50: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP87  | ′R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP85  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP87R<5:0>:** Peripheral Output Function is Assigned to RP87 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP85R<5:0>:** Peripheral Output Function is Assigned to RP85 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 0

## REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6 | STREN: SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Used in conjunction with the SCLREL bit.                                                                                                                                                                                                                                                                                                                       |

|       | 1 = Enables software or receives clock stretching                                                                                                                                                                                                                                                                                                              |

|       | 0 = Disables software or receives clock stretching                                                                                                                                                                                                                                                                                                             |

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                                                                                                                               |

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                                                                                                                                        |

|       |                                                                                                                                                                                                                                                                                                                                                                |

| bit 4 | <ul> <li>ACKEN: Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits the ACKDT data bit. Hardware is clear at the end of a master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                    |

|       | 1 = Enables Receive mode for $I^2C$ . Hardware is clear at the end of the eighth bit of a master receive data byte.<br>0 = Receive sequence is not in progress                                                                                                                                                                                                 |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                              |

|       | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of a master Stop sequence.</li> <li>0 = Stop condition is not in progress</li> </ul>                                                                                                                                                                                 |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                   |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of a master Repeated Start sequence.                                                                                                                                                                                                                                |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                                                                                                                                                                |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                    |

|       | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of a master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                                                                                                                                              |

Note 1: When performing master operations, ensure that the IPMIEN bit is '0'.

| r       |         |         |         |         |         |        |        |

|---------|---------|---------|---------|---------|---------|--------|--------|

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

| RXFUL7  | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1 | RXFUL0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                             |                    |  |  |

|-------------------|----------------------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read | l as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0                             | R/C-0   | R/C-0            | R/C-0             | R/C-0                               | R/C-0   | R/C-0           | R/C-0   |  |

|-----------------------------------|---------|------------------|-------------------|-------------------------------------|---------|-----------------|---------|--|

| RXFUL31                           | RXFUL30 | RXFUL29          | RXFUL28           | RXFUL27                             | RXFUL26 | RXFUL25         | RXFUL24 |  |

| bit 15                            |         |                  |                   |                                     |         |                 | bit 8   |  |

|                                   |         |                  |                   |                                     |         |                 |         |  |

| R/C-0                             | R/C-0   | R/C-0            | R/C-0             | R/C-0                               | R/C-0   | R/C-0           | R/C-0   |  |

| RXFUL23                           | RXFUL22 | RXFUL21          | RXFUL20           | RXFUL19                             | RXFUL18 | RXFUL17         | RXFUL16 |  |

| bit 7                             | •       |                  |                   | •                                   |         | •               | bit 0   |  |

|                                   |         |                  |                   |                                     |         |                 |         |  |

| Legend:                           |         | C = Writable b   | oit, but only '0' | '0' can be written to clear the bit |         |                 |         |  |

| R = Readable bit W = Writable bit |         |                  | bit               | U = Unimplemented bit, read as '0'  |         |                 |         |  |

| -n = Value at P                   | OR      | '1' = Bit is set |                   | '0' = Bit is cle                    | ared    | x = Bit is unkr | nown    |  |

bit 15-0 **RXFUL<31:16>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                      |                    |  |  |

|-------------------|----------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0'            |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 15-0

RXOVF<15:0>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

## REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only '0 | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|-------------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit              | U = Unimplemented bit, read as '0'                             |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

## 22.4 USB Control Registers

## REGISTER 22-1: UxOTGSTAT: USB OTG STATUS REGISTER

| U-0            | U-0                   | U-0                                   | U-0            | U-0               | U-0            | U-0             | U-0              |

|----------------|-----------------------|---------------------------------------|----------------|-------------------|----------------|-----------------|------------------|

|                | —                     | —                                     | _              | —                 | —              | _               | —                |

| bit 15         |                       |                                       |                | ·                 |                |                 | bit 8            |

|                |                       |                                       |                |                   |                |                 |                  |

| R-0, HSC       | U-0                   | R-0, HSC                              | U-0            | R-0, HSC          | R-0, HSC       | U-0             | R-0, HSC         |

| ID             |                       | LSTATE                                |                | SESVD             | SESEND         |                 | VBUSVD           |

| bit 7          |                       |                                       |                |                   |                |                 | bit (            |

| Legend:        |                       | U = Unimplem                          | ented bit, rea | d as 'O'          |                |                 |                  |

| R = Readal     | ble bit               | W = Writable b                        |                |                   | are Settable/C | learable bit    |                  |

| -n = Value a   | at POR                | '1' = Bit is set                      |                | '0' = Bit is clea | ared           | x = Bit is unk  | nown             |

|                |                       |                                       |                |                   |                |                 |                  |

| bit 15-8       | Unimplemen            | nted: Read as '0                      | ,              |                   |                |                 |                  |

| bit 7          | ID: ID Pin Sta        | ate Indicator bit                     |                |                   |                |                 |                  |

|                |                       | is attached or a                      |                |                   |                | 3 receptacle    |                  |

|                |                       | plug has been                         |                | he USB recepta    | cle            |                 |                  |

| bit 6          | Unimplemen            | ted: Read as '0                       | 3              |                   |                |                 |                  |

| bit 5          |                       | e State Stable Ir                     |                |                   |                |                 |                  |

|                |                       | line state (as de<br>line state has N |                | ,                 |                | for the previc  | ous 1 ms         |

| bit 4          | Unimplemen            | ted: Read as '0                       | ,              |                   |                |                 |                  |

| bit 3          | SESVD: Ses            | sion Valid Indica                     | tor bit        |                   |                |                 |                  |

|                | 1 = The VBU<br>device | s voltage is abo                      | ve VA_SESS_V   | LD (as defined i  | n the USB OT   | G Specificatior | n) on the A or E |

|                |                       | s voltage is belo                     | W VA_SESS_V    | LD on the A or E  | 3 device       |                 |                  |

| bit 2          | SESEND: B-            | Session End Inc                       | licator bit    |                   |                |                 |                  |

|                |                       | voltage is below<br>s voltage is abov |                |                   |                | Specification)  | on the B device  |

|                |                       | nted: Read as '0                      |                |                   |                |                 |                  |

| bit 1          | Chimpionion           |                                       |                |                   |                |                 |                  |

| bit 1<br>bit 0 | •                     | VBUS Valid Indic                      |                |                   |                |                 |                  |

|                | VBUSVD: A-            |                                       | ator bit       | D (as defined in  | the USB OTG    | Specification)  | on the A devic   |

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| U-0          | U-0             | U-0               | U-0             | U-0               | U-0              | U-0             | U-0   |

|--------------|-----------------|-------------------|-----------------|-------------------|------------------|-----------------|-------|

| _            | _               | —                 | _               |                   |                  | —               |       |

| bit 15       | ·               |                   |                 |                   |                  |                 | bit 8 |

|              |                 |                   |                 |                   |                  |                 |       |

| R/W-0        | R/W-0           | R/W-0             | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| BTSEE        | BUSACCEE        | DMAEE             | BTOEE           | DFN8EE            | CRC16EE          | CRC5EE          | PIDEE |

| bit 7        |                 |                   |                 |                   |                  |                 | bit ( |

| Legend:      |                 |                   |                 |                   |                  |                 |       |

| R = Readat   | ole bit         | W = Writable      | bit             | U = Unimplen      | nented bit, read | l as '0'        |       |

| -n = Value a | at POR          | '1' = Bit is set  |                 | '0' = Bit is clea | ared             | x = Bit is unkn | own   |

|              |                 |                   |                 |                   |                  |                 |       |

| bit 15-8     | Unimplement     | ted: Read as '    | )'              |                   |                  |                 |       |

| bit 7        | BTSEE: Bit S    | tuff Error Interr | upt Enable bit  |                   |                  |                 |       |

|              | 1 = Interrupt   |                   |                 |                   |                  |                 |       |

|              | 0 = Interrupt   |                   |                 |                   |                  |                 |       |

| bit 6        |                 | Bus Access Er     | ror Interrupt E | nable bit         |                  |                 |       |

|              | 1 = Interrupt   |                   |                 |                   |                  |                 |       |

| bit 5        |                 | A Error Interrup  | t Enable bit    |                   |                  |                 |       |

|              | 1 = Interrupt i | •                 |                 |                   |                  |                 |       |

|              | 0 = Interrupt   |                   |                 |                   |                  |                 |       |

| bit 4        | BTOEE: Bus      | Turnaround Tir    | ne-out Error Ir | nterrupt Enable   | bit              |                 |       |

|              | 1 = Interrupt   |                   |                 |                   |                  |                 |       |

|              | 0 = Interrupt   |                   | –               |                   |                  |                 |       |

| bit 3        |                 | a Field Size Er   | ror Interrupt E | nable bit         |                  |                 |       |

|              | 1 = Interrupt   |                   |                 |                   |                  |                 |       |

| bit 2        | -               | RC16 Failure Ir   | nterrupt Enabl  | e bit             |                  |                 |       |

| ~            | 1 = Interrupt i |                   |                 |                   |                  |                 |       |

|              | 0 = Interrupt   |                   |                 |                   |                  |                 |       |

| bit 1        | CRC5EE: CR      | C5 Host Error     | Interrupt Enab  | le bit            |                  |                 |       |

|              | 1 = Interrupt   |                   |                 |                   |                  |                 |       |

|              | 0 = Interrupt   |                   |                 |                   |                  |                 |       |

| bit 0        | 1 = Interrupt i | heck Failure Ir   | iterrupt Enable | e dit             |                  |                 |       |

|              |                 |                   |                 |                   |                  |                 |       |

NOTES:

## REGISTER 26-1: RCFGCAL: RTCC CALIBRATION AND CONFIGURATION REGISTER<sup>(1)</sup> (CONTINUED)

| bit 7-0 | CAL<7:0>: RTCC Drift Calibration bits                                                                            |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|         | 01111111 = Maximum positive adjustment; adds 508 RTCC clock pulses every one minute                              |  |  |  |  |  |  |

|         | •                                                                                                                |  |  |  |  |  |  |

|         | •                                                                                                                |  |  |  |  |  |  |

|         | •                                                                                                                |  |  |  |  |  |  |

|         | 00000001 = Minimum positive adjustment; adds four RTCC clock pulses every one minute<br>00000000 = No adjustment |  |  |  |  |  |  |

|         | 111111111 = Minimum negative adjustment; subtracts four RTCC clock pulses every one minute                       |  |  |  |  |  |  |

|         | •                                                                                                                |  |  |  |  |  |  |

|         | •                                                                                                                |  |  |  |  |  |  |

|         | •                                                                                                                |  |  |  |  |  |  |

|         | 10000000 = Maximum negative adjustment; subtracts 512 RTCC clock pulses every one minute                         |  |  |  |  |  |  |

- Note 1: The RCFGCAL register is only affected by a POR.

- 2: A write to the RTCEN bit is only allowed when RTCWREN = 1.

- 3: This bit is read-only. It is cleared when the lower half of the MINSEC register is written.

## 32.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings

## (See Note 1)

| Ambient temperature under bias                                                    | 40°C to +125°C          |

|-----------------------------------------------------------------------------------|-------------------------|

| Storage temperature                                                               | 65°C to +150°C          |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss <sup>(3)</sup>    | 0.3V to (VDD + 0.3V)    |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | -0.3V to +5.5V          |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to 3.6V            |

| Voltage on D+ OR D- pin with respect to VUSB3V3                                   | 0.3V to (VUSB3V3 +0.3V) |

| Voltage on VBUS with respect to VSS                                               | 0.3V to +5.5V           |

| Maximum current out of Vss pin                                                    | 320 mA                  |

| Maximum current into Vod pin <sup>(2)</sup>                                       |                         |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(4)</sup>                     |                         |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(4)</sup>                     | 25 mA                   |

| Maximum current sunk by all ports                                                 | 200 mA                  |

| Maximum current sourced by all ports <sup>(2)</sup>                               | 200 mA                  |

**Note 1:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 32-2).

- 3: See the "Pin Diagrams" section for the 5V tolerant pins.

- 4: Characterized but not tested.

| DC CHARACTERISTICS |        |                                                                                                 |                    | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |      |       |                                                       |  |  |

|--------------------|--------|-------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------|------|-------|-------------------------------------------------------|--|--|

| Param.             | Symbol | Characteristic                                                                                  | Min.               | Тур.                                                                      | Max. | Units | Conditions                                            |  |  |

| DO10               | Vol    | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins – All I/O Pins<br>except OSC2 and SOSCO  |                    | _                                                                         | 0.4  | V     | $IOL \le 10 \text{ mA}, \text{ VDD} = 3.3 \text{V}$   |  |  |

|                    |        | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins – OSC2 and<br>SOSCO                      | _                  | _                                                                         | 0.4  | V     | Iol $\leq$ 15 mA, Vdd = 3.3V                          |  |  |

| DO20               | Vон    | Output High Voltage<br>I/O Pins:<br>4x Sink Driver Pins – All I/O Pins<br>except OSC2 and SOSCO | 2.4                | _                                                                         | _    | V     | ІОН ≥ -10 mA, VDD = 3.3V                              |  |  |

|                    |        | Output High Voltage<br>I/O Pins:<br>8x Sink Driver Pins – OSC2 and<br>SOSCO                     | 2.4                | _                                                                         | _    | V     | ІОн ≥ -15 mA, VDD = 3.3V                              |  |  |

|                    | Vон1   | Output High Voltage                                                                             | 1.5 <sup>(1)</sup> | _                                                                         | —    |       | IOH $\ge$ -14 mA, VDD = 3.3V                          |  |  |

|                    |        | 4x Sink Driver Pins – All I/O Pins<br>except OSC2 and SOSCO                                     | 2.0 <sup>(1)</sup> | —                                                                         | —    | V     | ІОН ≥ -12 mA, VDD = 3.3V                              |  |  |

| DO20A              |        |                                                                                                 | 3.0 <sup>(1)</sup> | _                                                                         | _    |       | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$   |  |  |

|                    |        | Output High Voltage<br>I/O Pins:<br>8x Sink Driver Pins – OSC2 and<br>SOSCO                     | 1.5 <sup>(1)</sup> |                                                                           | _    | v     | $IOH \ge -22 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$ |  |  |

|                    |        |                                                                                                 | 2.0 <sup>(1)</sup> |                                                                           | _    |       | IOH ≥ -18 mA, VDD = 3.3V                              |  |  |

|                    |        |                                                                                                 | 3.0 <sup>(1)</sup> |                                                                           | _    |       | IOH ≥ -10 mA, VDD = 3.3V                              |  |  |

Note 1: Parameters are characterized, but not tested.

## TABLE 32-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V^{(2)}} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |      |       |            |

|--------------------|--------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|-------|------------|

| Param.             | Symbol | Characteristic                      |                                                                                                                                                                                                                                                                                             | Min. <sup>(1)</sup> | Тур. | Max. | Units | Conditions |

| BO10               | VBOR   | BOR Event on VDD Tra<br>High-to-Low | ansition                                                                                                                                                                                                                                                                                    | 2.7                 |      | 2.9  | V     | Vdd        |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, Comparator and DAC will have degraded performance. Device functionality is tested but not characterized.

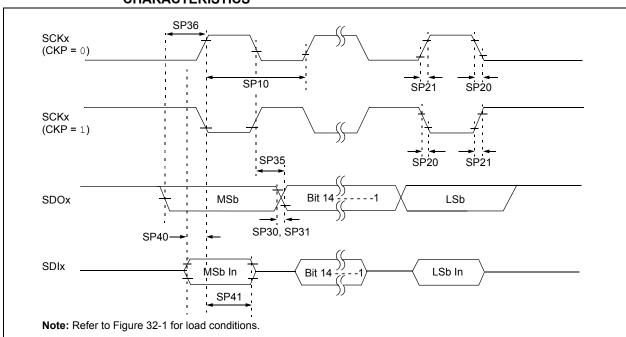

### FIGURE 32-25: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

## TABLE 32-43:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               |      | therwise            | <b>stated)</b><br>ture -40° | °C ≤ TA ≤ | <b>V to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------------|-----------------------|-----------------------------------------------|------|---------------------|-----------------------------|-----------|-----------------------------------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min. | Typ. <sup>(2)</sup> | Max.                        | Units     | Conditions                                                      |

| SP10               | TscP                  | Maximum SCKx Frequency                        |      | —                   | 10                          | MHz       | See Note 3                                                      |

| SP20               | TscF                  | SCKx Output Fall Time                         | _    | —                   | —                           | ns        | See Parameter DO32 and Note 4                                   |

| SP21               | TscR                  | SCKx Output Rise Time                         | _    | —                   | —                           | ns        | See Parameter DO31 and Note 4                                   |

| SP30               | TdoF                  | SDOx Data Output Fall Time                    | _    | —                   | —                           | ns        | See Parameter DO32 and <b>Note 4</b>                            |

| SP31               | TdoR                  | SDOx Data Output Rise Time                    | —    | —                   | —                           | ns        | See Parameter DO31 and Note 4                                   |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge     | _    | 6                   | 20                          | ns        |                                                                 |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to<br>First SCKx Edge  | 30   | —                   | —                           | ns        |                                                                 |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30   | —                   | —                           | ns        |                                                                 |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge     | 30   | —                   |                             | ns        |                                                                 |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 100 ns. The clock generated in Master mode must not violate this specification.

- **4**: Assumes 50 pF load on all SPIx pins.

|        |        |                                                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V (see Note 4) \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ \mbox{-}40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |         |       |      |                                      |  |

|--------|--------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|------|--------------------------------------|--|

| Param. | Symbol | Characteristic                                                          | Min. Typ. <sup>(1)</sup> Max. Units Conditions                                                                                                                                                                                                                                                       |         |       |      |                                      |  |

|        |        | Cloc                                                                    | k Parame                                                                                                                                                                                                                                                                                             | eters   |       |      |                                      |  |

| AD50   | Tad    | ADC Clock Period                                                        | 76                                                                                                                                                                                                                                                                                                   | _       |       | ns   |                                      |  |

| AD51   | tRC    | ADC Internal RC Oscillator Period                                       | _                                                                                                                                                                                                                                                                                                    | 250     | _     | ns   |                                      |  |

|        |        | Con                                                                     | version F                                                                                                                                                                                                                                                                                            | Rate    |       |      |                                      |  |

| AD55   | tCONV  | Conversion Time                                                         | —                                                                                                                                                                                                                                                                                                    | 12 TAD  | _     |      |                                      |  |

| AD56   | FCNV   | Throughput Rate                                                         | —                                                                                                                                                                                                                                                                                                    | —       | 1.1   | Msps | Using sequential sampling            |  |

| AD57   | TSAMP  | Sample Time                                                             | 2 Tad                                                                                                                                                                                                                                                                                                | —       | _     |      |                                      |  |

|        |        | Timin                                                                   | g Param                                                                                                                                                                                                                                                                                              | eters   |       |      | •                                    |  |

| AD60   | tPCS   | Conversion Start from Sample<br>Trigger <sup>(2)</sup>                  | 2 Tad                                                                                                                                                                                                                                                                                                | —       | 3 Tad | _    | Auto-Convert Trigger<br>not selected |  |

| AD61   | tpss   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2)</sup>           | 2 Tad                                                                                                                                                                                                                                                                                                | —       | 3 Tad | —    |                                      |  |

| AD62   | tcss   | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2)</sup>      | —                                                                                                                                                                                                                                                                                                    | 0.5 Tad | _     | —    |                                      |  |

| AD63   | tdpu   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                                    | —       | 20    | μs   | See Note 3                           |  |

## TABLE 32-58: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

**3:** The tDPU parameter is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (ADxCON1<15>) = 1). During this time, the ADC result is indeterminate.

4: Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, Comparator and DAC will have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 32-11 for the minimum and maximum BOR values.

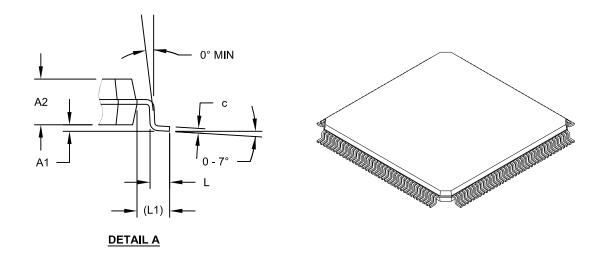

## 144-Lead Plastic Low Profile Quad Flatpack (PL) – 20x20x1.40 mm Body, with 2.00 mm Footprint [LQFP]

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                       | MILLIMETERS      |      |            |      |

|-----------------------|------------------|------|------------|------|

| Dimension             | Dimension Limits |      |            | MAX  |

| Number of Leads       | Ν                |      | 144        |      |

| Lead Pitch            | е                |      | 0.50 BSC   |      |

| Overall Height        | А                | -    | -          | 1.60 |

| Molded Package Height | A2               | 1.35 | 1.40       | 1.45 |

| Standoff              | A1               | 0.05 | -          | 0.15 |

| Foot Length           | L                | 0.45 | 0.60       | 0.75 |

| Footprint             | L1               |      | 1.00 (REF) |      |

| Overall Width         | Е                |      | 22.00 BSC  |      |

| Overall Length        | D                |      | 22.00 BSC  |      |

| Molded Body Width     | E1               |      | 20.00 BSC  |      |

| Molded Body Length    | D1               |      | 20.00 BSC  |      |

| Lead Thickness        | С                | 0.09 | -          | 0.20 |

| Lead Width            | b                | 0.17 | 0.22       | 0.27 |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-044B Sheet 2 of 2

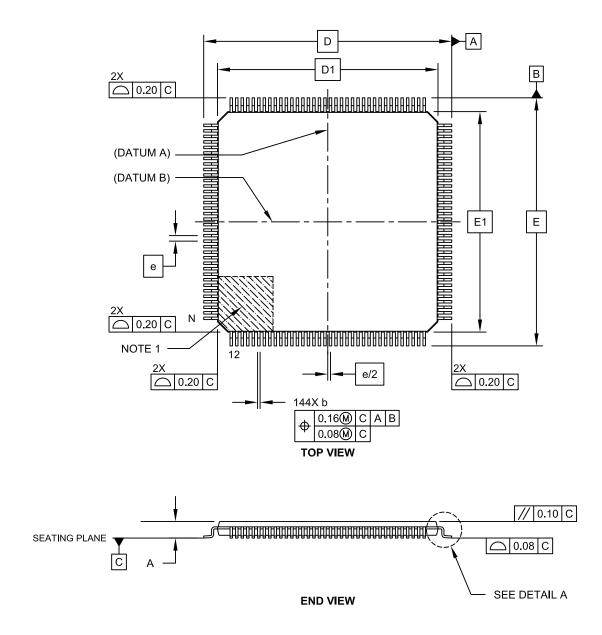

## 144-Lead Plastic Thin Quad Flatpack (PH)-16x16x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-155B Sheet 1 of 2

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response                     | Total Pages Sent                  |

|------------|-----------------------------------------------------------------------|-----------------------------------|

| From       |                                                                       |                                   |

| FIOIII     |                                                                       |                                   |

|            | Company<br>Address                                                    |                                   |

|            | City / State / ZIP / Country                                          |                                   |

|            | Telephone: ()                                                         | FAX: ()                           |

| Appli      | cation (optional):                                                    |                                   |

| Woul       | ld you like a reply?YN                                                |                                   |

| Devic      | ce: dsPIC33EPXXX(GP/MC/MU)806/810/814 and<br>PIC24EPXXX(GP/GU)810/814 | Literature Number: DS70616G       |

| Ques       | stions:                                                               |                                   |

| 1. V       | What are the best features of this document?                          |                                   |

| _          |                                                                       |                                   |

| <br>2. ⊢   | How does this document meet your hardware and softwar                 | e development needs?              |

|            |                                                                       |                                   |

| 3. C       | Do you find the organization of this document easy to follo           | w? If not, why?                   |

| —          |                                                                       |                                   |

| 4. V       | What additions to the document do you think would enhan               | ce the structure and subject?     |

| _          |                                                                       |                                   |

| 5. V       | What deletions from the document could be made without                | affecting the overall usefulness? |

| _          |                                                                       |                                   |

| _          |                                                                       |                                   |

| 6. ls      | s there any incorrect or misleading information (what and             | where)?                           |

| _          |                                                                       |                                   |

| 7. ⊢       | How would you improve this document?                                  |                                   |

|            |                                                                       |                                   |

| _          |                                                                       |                                   |