Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| Product Status            | Active                                                                           |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| peed                      | 70 MIPs                                                                          |

| connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG            |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| lumber of I/O             | 83                                                                               |

| rogram Memory Size        | 512KB (170K x 24)                                                                |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AM Size                   | 24K x 16                                                                         |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| ata Converters            | A/D 32x10b/12b                                                                   |

| scillator Type            | Internal                                                                         |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                |

| lounting Type             | Surface Mount                                                                    |

| ackage / Case             | 100-TQFP                                                                         |

| upplier Device Package    | 100-TQFP (14x14)                                                                 |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mu810-i-pf |

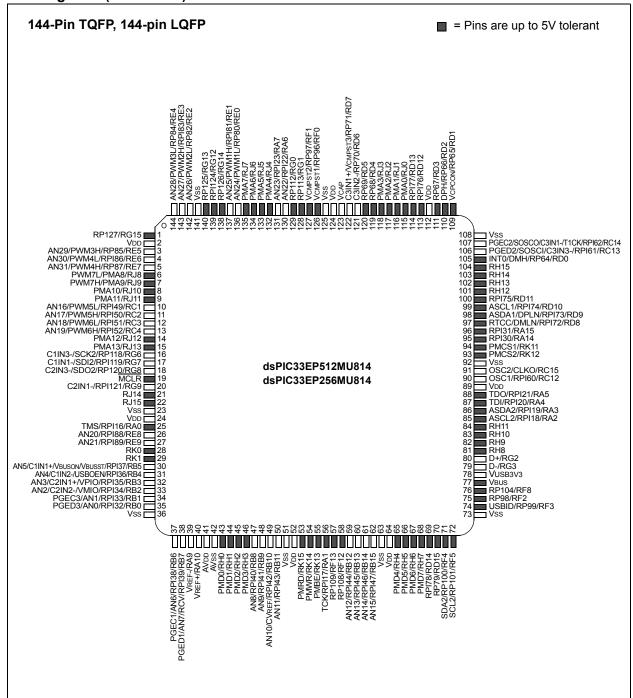

#### Pin Diagrams (Continued)

- **Note 1:** The RPn/RPIn pins can be used by any remappable peripheral with some limitation. See **Section 11.4 "Peripheral Pin Select"** for available peripherals and for information on limitations.

- 2: Every I/O port pin (RAx-RKx) can be used as change notification (CNAx-CNKx). See **Section 11.0** "I/O Ports" for more information.

- **3:** The availability of I<sup>2</sup>C interfaces varies by device. Selection (SDAx/SCLx or ASDAx/ASCLx) is made using the device Configuration bits, ALTI2C1 and ALTI2C2 (FPOR<5:4>). See **Section 29.0** "**Special Features**" for more information.

| sPIC33EPXXX(G | P/MC/MU)806/ | /810/814 and | PIC24EPXX | K(GP/GU)810/ | 814 |

|---------------|--------------|--------------|-----------|--------------|-----|

| OTES:         |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

|               |              |              |           |              |     |

### 3.5 Programmer's Model

The programmer's model is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, all devices in this family contain control registers for interrupts, while the dsPIC33EPXXX(GP/MC/MU)806/810/814 devices contain control registers for Modulo and Bit-reversed Addressing. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory mapped, as shown in Table 4-1.

TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

| Register(s) Name                                      | Description                                               |

|-------------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                        | Working Register Array                                    |

| ACCA, ACCB                                            | 40-Bit DSP Accumulators                                   |

| PC                                                    | 23-Bit Program Counter                                    |

| SR                                                    | ALU and DSP Engine Status register                        |

| SPLIM                                                 | Stack Pointer Limit Value register                        |

| TBLPAG                                                | Table Memory Page Address register                        |

| DSRPAG                                                | Extended Data Space (EDS) Read Page register              |

| DSWPAG                                                | Extended Data Space (EDS) Write Page register             |

| RCOUNT                                                | REPEAT Loop Count register                                |

| DCOUNT <sup>(1)</sup>                                 | DO Loop Count register                                    |

| DOSTARTH <sup>(1,2)</sup> , DOSTARTL <sup>(1,2)</sup> | DO Loop Start Address register (High and Low)             |

| DOENDH <sup>(1)</sup> , DOENDL <sup>(1)</sup>         | DO Loop End Address register (High and Low)               |

| CORCON                                                | Contains DSP Engine, DO Loop Control and Trap Status bits |

Note 1: This register is available on dsPIC33EPXXX(GP/MC/MU)806/810/814 devices only.

2: The DOSTARTH and DOSTARTL registers are read-only.

| TARI F 4-18. | PWM GENERATOR 6 REGISTER MAP FOR dsPIC33EPXXX(MC/MU)810/814 DEVICES ON  | IV |

|--------------|-------------------------------------------------------------------------|----|

| IADLL TIO.   | I WIN CENERALON O NECICIEN MAI I ON USI 1033EI AAA(MO/MO/MO/TDEVICES ON |    |

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13     | Bit 12        | Bit 11   | Bit 10  | Bit 9   | Bit 8      | Bit 7              | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|--------|------------|---------------|----------|---------|---------|------------|--------------------|--------|---------|---------|---------|-----------|---------|---------|---------------|

| PWMCON6   | 0CC0  | FLTSTAT | CLSTAT | TRGSTAT    | FLTIEN        | CLIEN    | TRGIEN  | ITB     | MDCS       | DTC<               | 1:0>   | DTCP    | 1       | MTBS    | CAM       | XPRES   | IUE     | 0000          |

| IOCON6    | 0CC2  | PENH    | PENL   | POLH       | POLL          | PMOD     | <1:0>   | OVRENH  | OVRENL     | OVRDA <sup>*</sup> | T<1:0> | FLTD    | \T<1:0> | CLDA    | AT<1:0>   | SWAP    | OSYNC   | 0000          |

| FCLCON6   | 0CC4  | IFLTMOD |        | (          | CLSRC<4:0     | )>       |         | CLPOL   | CLMOD      |                    | FLT    | SRC<4:0 | >       |         | FLTPOL    | FLTMO   | D<1:0>  | 0000          |

| PDC6      | 0CC6  |         |        | PDC6<15:0> |               |          |         |         |            |                    |        | 0000    |         |         |           |         |         |               |

| PHASE6    | 0CC8  |         |        |            | PHASE6<15:0>  |          |         |         |            |                    |        | 0000    |         |         |           |         |         |               |

| DTR6      | 0CCA  | _       | _      |            | DTR6<13:0>    |          |         |         |            |                    |        | 0000    |         |         |           |         |         |               |

| ALTDTR6   | 0CCC  | _       | _      |            | ALTDTR6<13:0> |          |         |         |            |                    |        |         | 0000    |         |           |         |         |               |

| SDC6      | 0CCE  |         |        |            |               |          |         |         | SDC6<15:0  | >                  |        |         |         |         |           |         |         | 0000          |

| SPHASE6   | 0CD0  |         |        |            |               |          |         | S       | SPHASE6<15 | :0>                |        |         |         |         |           |         |         | 0000          |

| TRIG6     | 0CD2  |         |        |            |               |          |         | ٦       | FRGCMP<15  | :0>                |        |         |         |         |           |         |         | 0000          |

| TRGCON6   | 0CD4  |         | TRGD   | IV<3:0>    |               | _        | _       | _       | _          | -                  | _      |         |         | TR      | GSTRT<5:0 | )>      |         | 0000          |

| PWMCAP6   | 0CD8  |         |        |            |               |          |         | Р       | WMCAP6<15  | 5:0>               |        |         |         |         |           |         |         | 0000          |

| LEBCON6   | 0CDA  | PHR     | PHF    | PLR        | PLF           | FLTLEBEN | CLLEBEN | _       | _          | -                  | _      | BCH     | BCL     | BPHH    | BPHL      | BPLH    | BPLL    | 0000          |

| LEBDLY6   | 0CDC  | _       | _      | LEB<11:0>  |               |          |         |         |            |                    | 0000   |         |         |         |           |         |         |               |

| AUXCON6   | 0CDE  | _       | _      | _          | _             |          | BLANKS  | EL<3:0> |            | -                  | _      |         | CHOPS   | EL<3:0> |           | CHOPHEN | CHOPLEN | 0000          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-19: PWM GENERATOR 7 REGISTER MAP FOR dsPIC33EPXXX(MC/MU)814 DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14       | Bit 13  | Bit 12        | Bit 11                                      | Bit 10 | Bit 9    | Bit 8      | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3    | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|--------------|---------|---------------|---------------------------------------------|--------|----------|------------|-------|--------|---------|---------|----------|-----------|---------|---------|---------------|

| PWMCON7   | 0CE0  | FLTSTAT | CLSTAT       | TRGSTAT | FLTIEN        | CLIEN                                       | TRGIEN | ITB      | MDCS       | DTC<  | 1:0>   | DTCP    | -       | MTBS     | CAM       | XPRES   | IUE     | 0000          |

| IOCON7    | 0CE2  | PENH    | PENL         | POLH    | POLL          | PMOD                                        | <1:0>  | OVRENH   | OVRENL     | OVRDA | T<1:0> | FLTDA   | \T<1:0> | CLDA     | AT<1:0>   | SWAP    | OSYNC   | 0000          |

| FCLCON7   | 0CE4  | IFLTMOD |              | (       | CLSRC<4:0     | )>                                          |        | CLPOL    | CLMOD      |       | FLT    | SRC<4:0 | >       |          | FLTPOL    | FLTMO   | D<1:0>  | 0000          |

| PDC7      | 0CE6  |         | PDC7<15:0>   |         |               |                                             |        |          |            |       |        | 0000    |         |          |           |         |         |               |

| PHASE7    | 0CE8  |         | PHASE7<15:0> |         |               |                                             |        |          |            |       | 0000   |         |         |          |           |         |         |               |

| DTR7      | 0CEA  | _       | _            |         | DTR7<13:0>    |                                             |        |          |            |       |        | 0000    |         |          |           |         |         |               |

| ALTDTR7   | 0CEC  | _       | _            |         | ALTDTR7<13:0> |                                             |        |          |            |       |        | 0000    |         |          |           |         |         |               |

| SDC7      | 0CEE  |         |              |         |               |                                             |        |          | SDC7<15:0  | >     |        |         |         |          |           |         |         | 0000          |

| SPHASE7   | 0CF0  |         |              |         |               |                                             |        | 5        | SPHASE7<15 | :0>   |        |         |         |          |           |         |         | 0000          |

| TRIG7     | 0CF2  |         |              |         |               |                                             |        | 7        | TRGCMP<15  | :0>   |        |         |         |          |           |         |         | 0000          |

| TRGCON7   | 0CF4  |         | TRGD         | IV<3:0> |               | _                                           | _      | _        | _          | _     | _      |         |         | TR       | GSTRT<5:( | )>      |         | 0000          |

| PWMCAP7   | 0CF8  |         |              |         |               |                                             |        | Р        | WMCAP7<15  | 5:0>  |        |         |         |          |           |         |         | 0000          |

| LEBCON7   | 0CFA  | PHR     | PHF          | PLR     | PLF           | FLTLEBEN CLLEBEN BCH BCL BPHH BPHL BPLH BPL |        |          |            |       |        |         | BPLL    | 0000     |           |         |         |               |

| LEBDLY7   | 0CFC  | _       | LEB<11:0>    |         |               |                                             |        |          |            |       | 0000   |         |         |          |           |         |         |               |

| AUXCON7   | 0CFE  | _       | _            | _       | _             |                                             | BLANKS | SEL<3:0> |            | _     | _      |         | CHOPS   | SEL<3:0> |           | CHOPHEN | CHOPLEN | 0000          |

dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.4.3 EDS ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA, the USB module and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus masters (USB and DMA Controllers) are allocated to M2 and M3,

respectively (M1 is reserved and cannot be used). The user application may raise or lower the priority of the masters to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-74.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization, or dynamically in response to real-time events.

TABLE 4-74: EDS BUS ARBITER PRIORITY

| Duiovity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |          |          |  |  |  |  |  |

|--------------|-----------------------------------------|----------|----------|----------|--|--|--|--|--|

| Priority     | 0x0000                                  | 0x0008   | 0x0020   | 0x0028   |  |  |  |  |  |

| M0 (highest) | CPU                                     | USB      | DMA      | USB      |  |  |  |  |  |

| M1           | Reserved                                | CPU      | CPU      | DMA      |  |  |  |  |  |

| M2           | USB                                     | Reserved | Reserved | CPU      |  |  |  |  |  |

| M3           | DMA                                     | DMA      | USB      | Reserved |  |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      | ICD      | ICD      |  |  |  |  |  |

Note 1: All other values of MSTRPR<15:0> are reserved.

FIGURE 4-8: **EDS ARBITER ARCHITECTURE DPSRAM** USB ICD CPU **DMA** Reserved MSTRPR<15:0 M0 M1 M2 М3 M4 **EDS Arbiter SRAM**

© 2009-2012 Microchip Technology Inc.

## REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0     |

|--------|-----|-----|-----|-----|-----|-----|-----------|

| _      | _   | _   | _   | _   | _   | _   | PLLDIV<8> |

| bit 15 |     |     |     |     |     |     | bit 8     |

| R/W-0 | R/W-0 | R/W-1 | R/W-1 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | PLLDI | V<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 **Unimplemented:** Read as '0'

bit 8-0 PLLDIV<8:0>: PLL Feedback Divisor bits (also denoted as 'M', PLL multiplier)

111111111 **= 513**

•

•

000110000 = **50** (default)

•

•

•

000000010 = 4

000000001 = 3

000000000 = 2

Note 1: This register is reset only on a Power-on Reset (POR).

## REGISTER 10-5: PMD5: PERIPHERAL MODULE DISABLE CONTROL REGISTER 5

| R/W-0  | R/W-0 |

|--------|--------|--------|--------|--------|--------|--------|-------|

| IC16MD | IC15MD | IC14MD | IC13MD | IC12MD | IC11MD | IC10MD | IC9MD |

| bit 15 |        |        |        |        |        |        | bit 8 |

| R/W-0  | R/W-0 |

|--------|--------|--------|--------|--------|--------|--------|-------|

| OC16MD | OC15MD | OC14MD | OC13MD | OC12MD | OC11MD | OC10MD | OC9MD |

| bit 7  |        |        |        |        |        |        | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15                  | IC16MD: IC16 Module Disable bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | 1 = IC16 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | 0 = IC16 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 14                  | IC15MD: IC15 Module Disable bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | 1 = IC15 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | 0 = IC15 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 13                  | IC14MD: IC14 Module Disable bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | 1 = IC14 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | 0 = IC14 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 12                  | IC13MD: IC13 Module Disable bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | 1 = IC13 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | 0 = IC13 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 11                  | IC12MD: IC12 Module Disable bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | 1 = IC12 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | 0 = IC12 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                     |

| bit 10                  | IC11MD: IC11 Module Disable bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | 1 = IC11 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | 0 = IC11 module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 9                   | IC10MD: IC10 Module Disable bit                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 9                   | IC10MD: IC10 Module Disable bit  1 = IC10 module is disabled                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 9                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 9                   | 1 = IC10 module is disabled                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                         | 1 = IC10 module is disabled<br>0 = IC10 module is enabled                                                                                                                                                                                                                                                                                                                                                                                      |

|                         | 1 = IC10 module is disabled<br>0 = IC10 module is enabled<br>IC9MD: IC9 Module Disable bit                                                                                                                                                                                                                                                                                                                                                     |

|                         | 1 = IC10 module is disabled<br>0 = IC10 module is enabled<br>IC9MD: IC9 Module Disable bit<br>1 = IC9 module is disabled                                                                                                                                                                                                                                                                                                                       |

| bit 8                   | 1 = IC10 module is disabled<br>0 = IC10 module is enabled<br>IC9MD: IC9 Module Disable bit<br>1 = IC9 module is disabled<br>0 = IC9 module is enabled                                                                                                                                                                                                                                                                                          |

| bit 8                   | 1 = IC10 module is disabled<br>0 = IC10 module is enabled<br>IC9MD: IC9 Module Disable bit<br>1 = IC9 module is disabled<br>0 = IC9 module is enabled<br>OC16MD: OC16 Module Disable bit                                                                                                                                                                                                                                                       |

| bit 8                   | 1 = IC10 module is disabled<br>0 = IC10 module is enabled<br>IC9MD: IC9 Module Disable bit<br>1 = IC9 module is disabled<br>0 = IC9 module is enabled<br>OC16MD: OC16 Module Disable bit<br>1 = OC16 module is disabled                                                                                                                                                                                                                        |

| bit 8                   | 1 = IC10 module is disabled<br>0 = IC10 module is enabled<br>IC9MD: IC9 Module Disable bit<br>1 = IC9 module is disabled<br>0 = IC9 module is enabled<br>OC16MD: OC16 Module Disable bit<br>1 = OC16 module is disabled<br>0 = OC16 module is enabled                                                                                                                                                                                          |

| bit 8                   | 1 = IC10 module is disabled 0 = IC10 module is enabled IC9MD: IC9 Module Disable bit 1 = IC9 module is disabled 0 = IC9 module is enabled OC16MD: OC16 Module Disable bit 1 = OC16 module is disabled 0 = OC16 module is enabled OC15MD: OC15 Module Disable bit                                                                                                                                                                               |

| bit 8                   | 1 = IC10 module is disabled 0 = IC10 module is enabled IC9MD: IC9 Module Disable bit 1 = IC9 module is disabled 0 = IC9 module is enabled OC16MD: OC16 Module Disable bit 1 = OC16 module is disabled 0 = OC16 module is enabled OC15MD: OC15 Module Disable bit 1 = OC15 module is disabled                                                                                                                                                   |

| bit 8 bit 7 bit 6       | 1 = IC10 module is disabled 0 = IC10 module is enabled IC9MD: IC9 Module Disable bit 1 = IC9 module is disabled 0 = IC9 module is enabled OC16MD: OC16 Module Disable bit 1 = OC16 module is disabled 0 = OC16 module is enabled OC15MD: OC15 Module Disable bit 1 = OC15 module is disabled 0 = OC15 module is enabled                                                                                                                        |

| bit 8 bit 7 bit 6       | 1 = IC10 module is disabled 0 = IC10 module is enabled IC9MD: IC9 Module Disable bit 1 = IC9 module is disabled 0 = IC9 module is enabled OC16MD: OC16 Module Disable bit 1 = OC16 module is disabled 0 = OC16 module is enabled OC15MD: OC15 Module Disable bit 1 = OC15 module is disabled 0 = OC15 module is enabled 0 = OC15 module is enabled OC14MD: OC14 Module Disable bit                                                             |

| bit 8 bit 7 bit 6       | 1 = IC10 module is disabled 0 = IC10 module is enabled IC9MD: IC9 Module Disable bit 1 = IC9 module is disabled 0 = IC9 module is enabled OC16MD: OC16 Module Disable bit 1 = OC16 module is disabled 0 = OC16 module is enabled OC15MD: OC15 Module Disable bit 1 = OC15 module is disabled 0 = OC15 module is enabled OC14MD: OC14 Module Disable bit 1 = OC14 module is disabled                                                            |

| bit 8 bit 7 bit 6 bit 5 | 1 = IC10 module is disabled 0 = IC10 module is enabled  IC9MD: IC9 Module Disable bit 1 = IC9 module is disabled 0 = IC9 module is enabled  OC16MD: OC16 Module Disable bit 1 = OC16 module is disabled 0 = OC16 module is enabled  OC15MD: OC15 Module Disable bit 1 = OC15 module is disabled 0 = OC15 module is enabled  OC14MD: OC14 Module Disable bit 1 = OC14 module is disabled 0 = OC14 module is enabled                             |

| bit 8 bit 7 bit 6 bit 5 | 1 = IC10 module is disabled 0 = IC10 module is enabled IC9MD: IC9 Module Disable bit 1 = IC9 module is disabled 0 = IC9 module is enabled OC16MD: OC16 Module Disable bit 1 = OC16 module is disabled 0 = OC16 module is enabled OC15MD: OC15 Module Disable bit 1 = OC15 module is disabled 0 = OC15 module is enabled OC14MD: OC14 Module Disable bit 1 = OC14 module is disabled 0 = OC14 module is enabled OC13MD: OC13 Module Disable bit |

# REGISTER 11-18: RPINR17: PERIPHERAL PIN SELECT INPUT REGISTER 17 (dsPIC33EPXXXMU806/810/814 DEVICES ONLY)

| U-0    | R/W-0                      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|----------------------------|-------|-------|-------|-------|-------|-------|--|

| _      | HOME2R<6:0> <sup>(1)</sup> |       |       |       |       |       |       |  |

| bit 15 |                            |       |       |       |       |       | bit 8 |  |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------------|-------|-------|-------|

| _     |       |       |       | INDX2R<6:0> | (1)   |       |       |

| bit 7 |       |       |       |             |       |       | bit 0 |

Legend:W = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-8 **HOME2R<6:0>:** Assign QEI2 HOME2 (HOME2) to the Corresponding RPn/RPIn Pin bits<sup>(1)</sup>

(see Table 11-2 for input pin selection numbers)

1111111 = Input tied to RP127

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 INDX2R<6:0>: Assign QEI2 INDEX2 (INDX2) to the Corresponding RPn/RPIn Pin bits<sup>(1)</sup>

(see Table 11-2 for input pin selection numbers)

1111111 = Input tied to RP127

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

Note 1: These bits are available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

#### REGISTER 11-24: RPINR24: PERIPHERAL PIN SELECT INPUT REGISTER 24

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      |       |       |       | CSCKR<6:0> | >     |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | CSDIR<6:0> | •     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

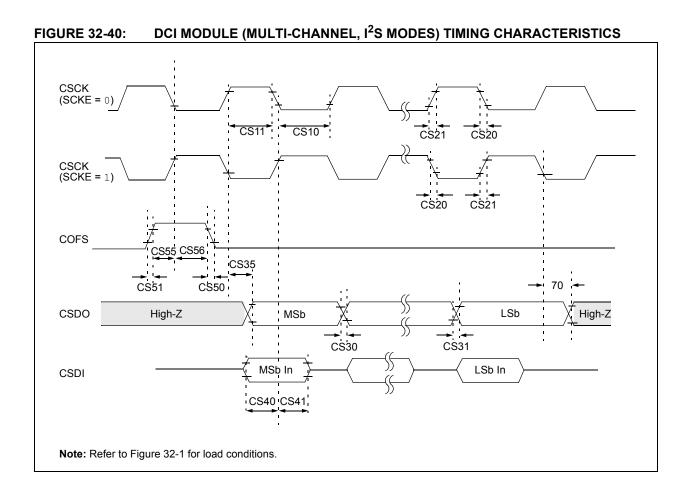

bit 14-8 CSCKR<6:0>: Assign DCI Clock Input (CSCK) to the Corresponding RPn/RPIn Pin bits

(see Table 11-2 for input pin selection numbers)

11111111 = Input tied to RP127

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 CSDIR<6:0>: Assign DCI Data Input (CSDI) to the Corresponding RPn/RPIn Pin bits

(see Table 11-2 for input pin selection numbers)

1111111 = Input tied to RP127

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

#### 15.2 Output Compare Control Registers

#### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0 | R/W-0       | R/W-0  | R/W-0  | R/W-0 |

|--------|-----|--------|-------|-------------|--------|--------|-------|

| _      | _   | OCSIDL |       | OCTSEL<2:0> | ENFLTC | ENFLTB |       |

| bit 15 |     |        |       |             |        |        | bit 8 |

| R/W-0  | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0    | R/W-0 | R/W-0    | R/W-0 |

|--------|------------|------------|------------|----------|-------|----------|-------|

| ENFLTA | OCFLTC     | OCFLTB     | OCFLTA     | TRIGMODE |       | OCM<2:0> |       |

| bit 7  |            |            |            |          |       |          | bit 0 |

| Legend:           | HCS = Hardware Settable/Clearable bit |                                         |  |  |  |  |

|-------------------|---------------------------------------|-----------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0'      |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

bit 15-14 **Unimplemented:** Read as '0'

bit 13 OCSIDL: Stop Output Compare x in Idle Mode Control bit

1 = Output Compare x Halts in CPU Idle mode

0 = Output Compare x continues to operate in CPU Idle mode

bit 12-10 OCTSEL<2:0>: Output Compare x Clock Select bits

111 = Peripheral clock (FP)

110 = Reserved

101 = Reserved

100 = Clock source of T1CLK is the clock source of OCx (only the synchronous clock is supported)

011 = Clock source of T5CLK is the clock source of OCx

010 = Clock source of T4CLK is the clock source of OCx

001 = Clock source of T3CLK is the clock source of OCx

000 = Clock source of T2CLK is the clock source of OCx

bit 9 ENFLTC: Fault C Input Enable bit

1 = Output Compare Fault C input (OCFC) is enabled

0 = Output Compare Fault C input (OCFC) is disabled

bit 8 ENFLTB: Fault B Input Enable bit

1 = Output Compare Fault B input (OCFB) is enabled

0 = Output Compare Fault B input (OCFB) is disabled

bit 7 ENFLTA: Fault A Input Enable bit

1 = Output Compare Fault A input (OCFA) is enabled

0 = Output Compare Fault A input (OCFA) is disabled

bit 6 OCFLTC: PWM Fault C Condition Status bit

1 = PWM Fault C condition on OCFC pin has occurred

0 = No PWM Fault C condition on OCFC pin has occurred

bit 5 OCFLTB: PWM Fault B Condition Status bit

1 = PWM Fault B condition on OCFB pin has occurred

0 = No PWM Fault B condition on OCFB pin has occurred

bit 4 OCFLTA: PWM Fault A Condition Status bit

1 = PWM Fault A condition on OCFA pin has occurred

0 = No PWM Fault A condition on OCFA pin has occurred

bit 3 TRIGMODE: Trigger Status Mode Select bit

1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

0 = TRIGSTAT is cleared only by software

**Note 1:** OCxR and OCxRS are double-buffered in PWM mode only.

#### REGISTER 16-10: MDC: PWM MASTER DUTY CYCLE REGISTER

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| MDC<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15    |       |       |       | bit 8 |       |       |       |  |  |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| MDC<7:0> |       |       |       |       |       |       |       |  |  |  |

| bit 7    |       |       |       |       |       |       |       |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 MDC<15:0>: Master PWM Duty Cycle Value bits

#### **REGISTER 16-16: DTRx: PWMx DEAD-TIME REGISTER**

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | DTRx  | <13:8> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|

| DTRx<7:0> |       |       |       |       |       |       |       |  |

| bit 7     |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-0 DTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-17: ALTDTRx: PWMx ALTERNATE DEAD-TIME REGISTER

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 |

|--------|-----|-------|-------|--------|----------|-------|-------|

| _      | _   |       |       | ALTDTI | Rx<13:8> |       |       |

| bit 15 |     |       |       |        |          |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------|-------|-------|-------|

|       |       |       | ALTDTF | Rx<7:0> |       |       |       |

| bit 7 |       |       |        |         |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-0 ALTDTRx<13:0>: Unsigned 14-Bit Dead-Time Value for PWMx Dead-Time Unit bits

#### REGISTER 16-19: IOCONx: PWMx I/O CONTROL REGISTER (CONTINUED)

bit 3-2 CLDAT<1:0>: Data for PWMxH and PWMxL Pins if CLMOD is Enabled bits

IFLTMOD (FCLCONx<15>) = 0: Normal Fault mode:

If current limit is active, PWMxH is driven to the state specified by CLDAT<1>. If current limit is active, PWMxL is driven to the state specified by CLDAT<0>.

IFLTMOD (FCLCONx<15>) = 1: Independent Fault mode:

The CLDAT<1:0> bits are ignored.

bit 1 **SWAP:** Swap PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0 **OSYNC:** Output Override Synchronization bit

1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWM time base

0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary

**Note 1:** These bits should not be changed after the PWM module is enabled (PTEN = 1).

#### REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

| U-0    | R/W-x  | U-0 | U-0 | U-0 | R/W-x | R/W-x       | R/W-x |

|--------|--------|-----|-----|-----|-------|-------------|-------|

| _      | WAKFIL | _   | _   | _   | :     | SEG2PH<2:0> |       |

| bit 15 |        |     |     |     |       |             | bit 8 |

| R/W-x    | R/W-x | R/W-x       | R/W-x | R/W-x | R/W-x      | R/W-x | R/W-x |

|----------|-------|-------------|-------|-------|------------|-------|-------|

| SEG2PHTS | SAM   | SEG1PH<2:0> |       |       | PRSEG<2:0> |       |       |

| bit 7    |       |             |       |       |            |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14 WAKFIL: Select CAN Bus Line Filter for Wake-up bit

1 = Uses CAN bus line filter for wake-up

0 = CAN bus line filter is not used for wake-up

bit 13-11 **Unimplemented:** Read as '0'

bit 10-8 **SEG2PH<2:0>:** Phase Segment 2 bits

111 = Length is 8 x TQ

•

•

000 = Length is  $1 \times TQ$

bit 7 SEG2PHTS: Phase Segment 2 Time Select bit

1 = Freely programmable

0 = Maximum of SEG1PH bits or Information Processing Time (IPT), whichever is greater

bit 6 SAM: Sample of the CAN Bus Line bit

1 = Bus line is sampled three times at the sample point

0 = Bus line is sampled once at the sample point

bit 5-3 **SEG1PH<2:0>:** Phase Segment 1 bits

111 = Length is 8 x TQ

•

•

•

$000 = \text{Length is } 1 \times \text{TQ}$

bit 2-0 **PRSEG<2:0>:** Propagation Time Segment bits

111 = Length is 8 x TQ

•

•

•

000 = Length is 1 x TQ

Note:

# 22.0 USB ON-THE-GO (OTG) MODULE (dsPIC33EPXXXMU8XX AND PIC24EPGU8XX DEVICES ONLY)

Note 1: This data sheet is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 25. "USB On-The-Go (OTG)" (DS70571) of the "dsPIC33E/PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 22.1 Overview

The Universal Serial Bus (USB) On-The-Go (OTG) module includes the following features:

- · USB Full-Speed Support for Host and Device

- Low-Speed Host Support

- USB On-The-Go Support

- · Integrated Signaling Resistors

- Integrated Analog Comparators for VBUS Monitoring

- · Integrated USB Transceiver

- · Hardware Performs Transaction Handshaking

- · Endpoint Buffering Anywhere in System RAM

- Integrated DMA Controller to Access System RAM

- Support for all four transfer types:

- Control

- Interrupt

- Bulk Data

- Isochronous

- Queueing of up to Four Endpoint Transfers without Servicing

- · USB 5V Charge Pump Controller

The USB module contains the analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), pull-up and pull-down resistors, and the register interface. Figure 22-1 illustrates the block diagram of the USB OTG module.

The device auxiliary clock generator provides the 48 MHz clock required for USB communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the protocol for data transfers. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The implementation and use of the USB specifications and other third party specifications or technology may require a license from various entities, including, but not limited to USB Implementers Forum, Inc. (also referred to as USB-IF). It is your responsibility to obtain more information regarding any applicable licensing obligations.

#### 22.2 Clearing USB OTG Interrupts

Unlike device level interrupts, the USB OTG interrupt status flags are not freely writable in software. All USB OTG flag bits are implemented as hardware set-only bits. Additionally, these bits can only be cleared in software by writing a '1' to their locations (i.e., performing a BSET instruction). Writing a '0' to a flag bit (i.e., a BCLR instruction) has no effect.

**Note:** Throughout this section, a bit that can only be cleared by writing a '1' to its location is referred to as "Write '1' to clear bit". In register descriptions, this function is indicated by the descriptor, "K".

**TABLE 30-2: INSTRUCTION SET OVERVIEW (CONTINUED)**

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax                             | Description                                    | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|---------|---------------------------------------------|------------------------------------------------|---------------|-------------------------------|--------------------------|

| 46                 | MOV                  | MOV     | f,Wn                                        | Move f to Wn                                   | 1             | 1                             | None                     |

|                    |                      | MOV     | f                                           | Move f to f                                    | 1             | 1                             | None                     |

|                    |                      | MOV     | f,WREG                                      | Move f to WREG                                 | 1             | 1                             | None                     |

|                    |                      | MOV     | #lit16,Wn                                   | Move 16-bit literal to Wn                      | 1             | 1                             | None                     |

|                    |                      | MOV.b   | #lit8,Wn                                    | Move 8-bit literal to Wn                       | 1             | 1                             | None                     |

|                    |                      | MOV     | Wn,f                                        | Move Wn to f                                   | 1             | 1                             | None                     |

|                    |                      | MOV     | Wso, Wdo                                    | Move Ws to Wd                                  | 1             | 1                             | None                     |

|                    |                      | MOV     | WREG, f                                     | Move WREG to f                                 | 1             | 1                             | None                     |

|                    |                      | MOV.D   | Wns,Wd                                      | Move Double from W(ns):W(ns + 1) to Wd         | 1             | 2                             | None                     |

|                    |                      | MOV.D   | Ws, Wnd                                     | Move Double from Ws to W(nd + 1):W(nd)         | 1             | 2                             | None                     |

| 47                 | MOVPAG               | MOVPAG  | #lit10,DSRPAG                               | Move 10-bit literal to DSRPAG                  | 1             | 1                             | None                     |

|                    |                      | MOVPAG  | #lit9,DSWPAG                                | Move 9-bit literal to DSWPAG                   | 1             | 1                             | None                     |

|                    |                      | MOVPAG  | #lit8,TBLPAG                                | Move 8-bit literal to TBLPAG                   | 1             | 1                             | None                     |

|                    |                      | MOVPAGW | Ws, DSRPAG                                  | Move Ws<9:0> to DSRPAG                         | 1             | 1                             | None                     |

|                    |                      | MOVPAGW | Ws, DSWPAG                                  | Move Ws<8:0> to DSWPAG                         | 1             | 1                             | None                     |

|                    |                      | MOVPAGW | Ws, TBLPAG                                  | Move Ws<7:0> to TBLPAG                         | 1             | 1                             | None                     |

| 48                 | MOVSAC               | MOVSAC  | Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup>   | Prefetch and store accumulator                 | 1             | 1                             | None                     |

| 49 MI              | MPY                  | MPY     | Wm*Wn, Acc, Wx, Wxd, Wy, Wyd <sup>(1)</sup> | Multiply Wm by Wn to Accumulator               | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY     | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd <sup>(1)</sup> | Square Wm to Accumulator                       | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 50                 | MPY.N                | MPY.N   | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd(1)                  | -(Multiply Wm by Wn) to Accumulator            | 1             | 1                             | None                     |

| 51                 | MSC                  | MSC     | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd, AWB(1)        | Multiply and Subtract from Accumulator         | 1             | 1                             | OA,OB,OAB,<br>SA,SB,SAB  |

| 52                 | MUL                  | MUL.SS  | Wb, Ws, Wnd                                 | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)       | 1             | 1                             | None                     |

|                    |                      | MUL.SS  | Wb, Ws, Acc(1)                              | Accumulator = signed(Wb) * signed(Ws)          | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb, Ws, Wnd                                 | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)     | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb, Ws, Acc <sup>(1)</sup>                  | Accumulator = signed(Wb) * unsigned(Ws)        | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb, #lit5, Acc <sup>(1)</sup>               | Accumulator = signed(Wb) * unsigned(lit5)      | 1             | 1                             | None                     |

|                    |                      | MUL.US  | Wb, Ws, Wnd                                 | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)     | 1             | 1                             | None                     |

|                    |                      | MUL.US  | Wb, Ws, Acc <sup>(1)</sup>                  | Accumulator = unsigned(Wb) * signed(Ws)        | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb, Ws, Wnd                                 | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(Ws)   | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Acc <sup>(1)</sup>                 | Accumulator = unsigned(Wb) * unsigned(lit5)    | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb, Ws, Acc <sup>(1)</sup>                  | Accumulator = unsigned(Wb) * unsigned(Ws)      | 1             | 1                             | None                     |

|                    |                      | MULW.SS | Wb, Ws, Wnd                                 | Wnd = signed(Wb) * signed(Ws)                  | 1             | 1                             | None                     |

|                    |                      | MULW.SU | Wb, Ws, Wnd                                 | Wnd = signed(Wb) * unsigned(Ws)                | 1             | 1                             | None                     |

|                    |                      | MULW.US | Wb, Ws, Wnd                                 | Wnd = unsigned(Wb) * signed(Ws)                | 1             | 1                             | None                     |

|                    |                      | MULW.UU | Wb, Ws, Wnd                                 | Wnd = unsigned(Wb) * unsigned(Ws)              | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                                | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)   | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                                | Wnd = signed(Wb) * unsigned(lit5)              | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                                | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(lit5) | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                                | Wnd = unsigned(Wb) * unsigned(lit5)            | 1             | 1                             | None                     |

|                    |                      | MUL     | f                                           | W3:W2 = f * WREG                               | 1             | 1                             | None                     |

Note 1:

This instruction is available in dsPIC33EPXXX(GP/MC/MU)806/810/814 devices only.

Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

© 2009-2012 Microchip Technology Inc.

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Field Application Engineer (FAE)

- · Technical Support

- · Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

#### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager Reader Response                    | Total Pages Sent                     |

|------------|-------------------------------------------------------------------|--------------------------------------|

| From:      | ·                                                                 |                                      |

| FIOIII.    | -                                                                 |                                      |

|            | Company                                                           |                                      |

|            | Address City / State / ZIP / Country                              |                                      |

|            |                                                                   |                                      |

| مانده ۸    |                                                                   | FAX: (                               |

|            | cation (optional):                                                |                                      |

|            | d you like a reply?YN                                             |                                      |

| Devic      | e: dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 | Literature Number: DS70616G          |

| Quest      | tions:                                                            |                                      |

| 1. W       | /hat are the best features of this document?                      |                                      |

| _          |                                                                   |                                      |

| 2. H       | ow does this document meet your hardware and softwa               | are development needs?               |

| _          |                                                                   |                                      |

| 2 -        |                                                                   | lave of make who o                   |

| 3. D       | o you find the organization of this document easy to fol          | low? II not, wny?                    |

| _          |                                                                   |                                      |

| 4. W       | /hat additions to the document do you think would enha            | nce the structure and subject?       |

|            | <b>,</b>                                                          | <b>,</b>                             |

| _          |                                                                   |                                      |

| 5. W       | /hat deletions from the document could be made withou             | at affecting the overall usefulness? |

| _          |                                                                   |                                      |

| _          |                                                                   |                                      |

| 6. Is      | there any incorrect or misleading information (what an            | d where)?                            |

| _          |                                                                   |                                      |

|            |                                                                   |                                      |

| 7. H       | ow would you improve this document?                               |                                      |

| _          |                                                                   |                                      |

|            |                                                                   |                                      |