Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 83                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

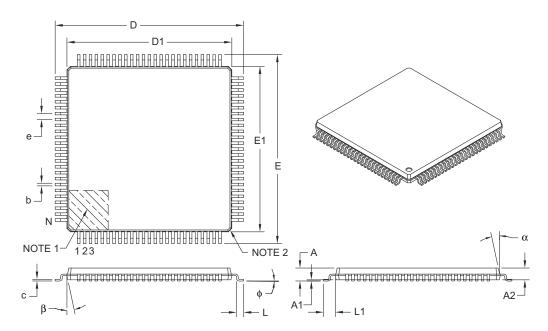

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mu810-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|     |          |          |           |           |           | 4EP2560<br>4EP5120 |           |           |           |           |              |

|-----|----------|----------|-----------|-----------|-----------|--------------------|-----------|-----------|-----------|-----------|--------------|

|     | 1        | 2        | 3         | 4         | 5         | 6                  | 7         | 8         | 9         | 10        | 11           |

| ۹ ( | O<br>RE4 | O<br>RE3 | RG13      | O<br>RE0  | RG0       | RF1                | O<br>Vdd  | NC        | RD12      | RD2       | RD1          |

| 3   | NC       | RG15     | O<br>RE2  | O<br>RE1  | O<br>RA7  | RF0                | O<br>VCAP | RD5       | RD3       | ⊖<br>Vss  | O<br>RC14    |

| c   | O<br>RE6 | O<br>VDD | RG12      | RG14      | O<br>RA6  | NC                 | O<br>RD7  | RD4       | NC        | O<br>RC13 | <b>R</b> D11 |

| D   | O<br>RC1 | O<br>RE7 | O<br>RE5  | NC        | NC        | NC                 | O<br>RD6  | RD13      | RD0       | NC        | RD10         |

| E   | O<br>RC4 | C<br>RC3 | O<br>RG6  | O<br>RC2  | NC        | RG1                | NC        | RA15      | RD8       | RD9       | RA14         |

| F   | MCLR     | O<br>RG8 | O<br>RG9  | O<br>RG7  | ⊖<br>Vss  | NC                 | NC        |           | O<br>RC12 | ⊖<br>Vss  | O<br>RC15    |

| G   | O<br>RE8 | O<br>RE9 | RA0       | NC        | O<br>Vdd  | ⊖<br>Vss           | ⊖<br>Vss  | NC        | RA5       | RA3       | RA4          |

| н   | O<br>RB5 | O<br>RB4 | NC        | NC        | NC        | O<br>Vdd           | NC        | VBUS      | UUSB3V3   | O<br>RG2  | RA2          |

| J   | O<br>RB3 | O<br>RB2 | O<br>RB7  | O<br>AVDD | O<br>RB11 | RA1                | O<br>RB12 | NC        | NC        | RF8       | O<br>RG3     |

| к   | O<br>RB1 | O<br>RB0 | O<br>RA10 | O<br>RB8  | NC        | RF12               | O<br>RB14 |           | RD15      | RF3       | RF2          |

| L   | O<br>RB6 | O<br>RA9 | )<br>AVss | O<br>RB9  | O<br>RB10 | RF13               | O<br>RB13 | O<br>RB15 | RD14      | RF4       | RF5          |

# Pin Diagrams (Continued)

| Pin Name                          | Pin<br>Type | Buffer<br>Type | PPS | Description                                                    |

|-----------------------------------|-------------|----------------|-----|----------------------------------------------------------------|

| SCL1 <sup>(5)</sup>               | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                |

| SDA1 <sup>(5)</sup>               | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                 |

| ASCL1 <sup>(5)</sup>              | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.      |

| ASDA1 <sup>(5)</sup>              | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.       |

| SCL2 <sup>(5)</sup>               | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                |

| SDA2 <sup>(5)</sup>               | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                 |

| ASCL2 <sup>(5)</sup>              | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.      |

| ASDA2 <sup>(5)</sup>              | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.       |

| TMS                               | Ι           | ST             | No  | JTAG Test mode select pin.                                     |

| ТСК                               | I           | ST             | No  | JTAG test clock input pin.                                     |

| TDI                               | I.          | ST             | No  | JTAG test data input pin.                                      |

| TDO                               | 0           | —              | No  | JTAG test data output pin.                                     |

| INDX1 <sup>(1)</sup>              | I           | ST             | Yes | Quadrature Encoder Index1 pulse input.                         |

| HOME1 <sup>(1)</sup>              | 1           | ST             | Yes | Quadrature Encoder Home1 pulse input.                          |

| QEA1 <sup>(1)</sup>               | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer |

|                                   |             |                |     | external clock input in Timer mode.                            |

| QEB1 <sup>(1)</sup>               | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer |

| (4)                               |             |                |     | external gate input in Timer mode.                             |

| CNTCMP1 <sup>(1)</sup>            | 0           |                | Yes | Quadrature Encoder Compare Output 1.                           |

| INDX2 <sup>(1)</sup>              | I           | ST             | Yes | Quadrature Encoder Index2 pulse input.                         |

| HOME2 <sup>(1)</sup>              | I           | ST             | Yes | Quadrature Encoder Home2 pulse input.                          |

| QEA2 <sup>(1)</sup>               | I           | ST             | Yes | Quadrature Encoder Phase A input in QEI2 mode. Auxiliary timer |

| (1)                               |             |                |     | external clock input in Timer mode.                            |

| QEB2 <sup>(1)</sup>               | I           | ST             | Yes | Quadrature Encoder Phase B input in QEI2 mode. Auxiliary timer |

|                                   | 0           |                | M   | external gate input in Timer mode.                             |

| CNTCMP2 <sup>(1)</sup>            | 0           | —              | Yes | Quadrature Encoder Compare Output 2.                           |

| COFS                              | I/O         | ST             | Yes | Data Converter Interface frame synchronization pin.            |

| CSCK                              | I/O         | ST             | Yes | Data Converter Interface serial clock input/output pin.        |

| CSDI                              |             | ST             | Yes | Data Converter Interface serial data input pin.                |

| CSDO                              | 0           |                | Yes | Data Converter Interface serial data output pin.               |

| C1RX                              | I           | ST             | Yes | ECAN1 bus receive pin.                                         |

| C1TX                              | 0           | —              | Yes | ECAN1 bus transmit pin.                                        |

| C2RX                              | Ι           | ST             | Yes | ECAN2 bus receive pin.                                         |

| C2TX                              | 0           | —              | Yes | ECAN2 bus transmit pin.                                        |

| RTCC                              | 0           |                | No  | Real-Time Clock alarm output.                                  |

| CVREF                             | 0           | Analog         | No  | Comparator voltage reference output.                           |

| C1IN1+, C1IN2-,<br>C1IN1-, C1IN3- | I           | Analog         | No  | Comparator 1 inputs                                            |

| C1OUT                             | 0           |                | Yes | Comparator 1 output.                                           |

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select

Analog = Analog input O = Output TTL = TTL input buffer

P = Powe I = Input

Note 1: This pin is available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

- **2:** AVDD must be connected at all times.

- 3: These pins are input only on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

- 4: These pins are only available on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

- 5: The availability of I<sup>2</sup>C<sup>™</sup> interfaces varies by device. Refer to the "**Pin Diagrams**" section for availability. Selection (SDAx/SCLx or ASDAx/ASCLx) is made using the device Configuration bits, ALTI2C1 and ALTI2C2 (FPOR<5:4>). See Section 29.0 "Special Features" for more information.

- 6: Analog functionality is activated by enabling the USB module and is not controlled by the ANSEL register.

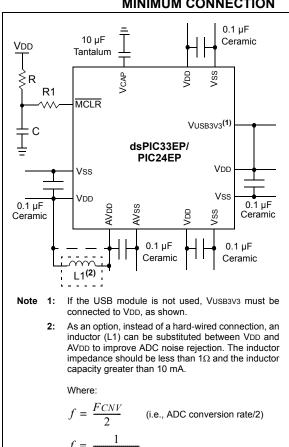

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7 µF to 47 µF.

#### 2.3 **CPU Logic Filter Capacitor** Connection (VCAP)

A low-ESR (< 1 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7 µF (10 µF is recommended), 16V connected to ground. The type can be ceramic or tantalum. See Section 32.0 "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See Section 29.2 "On-Chip Voltage Regulator" for details.

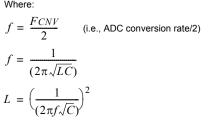

#### Master Clear (MCLR) Pin 2.4

The MCLR pin provides two specific device functions:

- · Device Reset

- · Device Programming and Debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### EXAMPLE OF MCLR PIN FIGURE 2-2: CONNECTIONS

- **Note 1:**  $R \leq 10 \text{ k}\Omega$  is recommended. A suggested starting value is 10 k $\Omega$ . Ensure that the MCLR pin VIH and VIL specifications are met.

- $R1 \leq 470\Omega$  will limit any current flowing into 2: MCLR from the external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

#### TABLE 4-38: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXMU806 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6       | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|-------------|--------|--------|-------|-------|-------|-------------|------------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        |             | RP65   | R<5:0> |       |       | _     |             | RP64R<5:0> |       |       |        |       |       | 0000          |

| RPOR1        | 0682  |        | _      |        |             | RP67   | २<5:0> |       |       | _     | —           |            |       | RP66  | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        | RP69R<5:0>  |        |        |       | —     | _     |             | RP68R<5:0> |       |       |        |       | 0000  |               |

| RPOR3        | 0686  | _      | _      |        | RP71R<5:0>  |        |        |       | —     | _     | RP70R<5:0>  |            |       |       |        | 0000  |       |               |

| RPOR4        | 0688  | _      | _      |        | RP80R<5:0>  |        |        |       | —     | —     | _           | _          | _     | —     | _      | —     | 0000  |               |

| RPOR5        | 068A  |        | _      |        |             | RP84   | २<5:0> |       |       | _     | —           |            |       | RP82  | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  |        | -      |        |             | RP87   | २<5:0> |       |       | _     | —           | RP85R<5:0> |       |       |        |       | 0000  |               |

| RPOR7        | 068E  |        | -      |        |             | RP97   | २<5:0> |       |       | _     | —           |            |       | RP96  | R<5:0> |       |       | 0000          |

| RPOR8        | 0690  |        | -      |        | RP99R<5:0>  |        |        |       | _     | —     |             |            |       |       | _      | 0000  |       |               |

| RPOR9        | 0692  | _      | _      |        | RP101R<5:0> |        |        |       | —     | _     | RP100R<5:0> |            |       |       | 0000   |       |       |               |

| RPOR13       | 069A  | _      | _      |        | RP118R<5:0> |        |        |       | —     | —     | _           | _          | _     | —     | _      | —     | 0000  |               |

| RPOR14       | 069C  | —      | —      | _      |             |        |        |       | _     | _     | RP120R<5:0> |            |       |       |        | 0000  |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-39: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXX(GP/MC/MU)806 AND PIC24EPXXXGP806 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|-------|-------|--------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | —      |        |            | RP65F  | R<5:0> |       |       | —     | —     |       |       | RP64   | R<5:0> |       |       | 0000          |

| RPOR1        | 0682  | —      | _      |        |            | RP67F  | R<5:0> |       |       | _     | _     |       |       | RP66   | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |            | RP69F  | R<5:0> |       |       | _     | _     |       |       | RP68   | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        | RP71R<5:0> |        |        |       | _     | _     |       |       | RP70  | R<5:0> |        |       | 0000  |               |

| RPOR4        | 0688  | _      | _      |        |            | RP80F  | R<5:0> |       |       | _     | _     | _     | _     | _      | _      | _     | _     | 0000          |

| RPOR5        | 068A  | _      | _      |        |            | RP84F  | R<5:0> |       |       | _     | _     |       |       | RP82   | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  | _      | _      |        |            | RP87F  | R<5:0> |       |       | _     | _     |       |       | RP85   | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |        |            | RP97F  | R<5:0> |       |       | _     | _     |       |       | RP96   | R<5:0> |       |       | 0000          |

| RPOR8        | 0690  | _      | _      |        |            | RP99F  | R<5:0> |       |       | _     | _     |       |       | RP98   | R<5:0> |       |       | 0000          |

| RPOR9        | 0692  | —      | _      |        |            | RP101  | R<5:0> |       |       | _     | _     |       |       | RP100  | R<5:0> |       |       | 0000          |

| RPOR10       | 0694  | —      | _      | _      | _          | _      | _      | _     | _     | _     | _     |       |       | RP102  | R<5:0> |       |       | 0000          |

| RPOR13       | 069A  | —      | _      |        |            | RP118  | R<5:0> |       |       | _     | _     | _     | _     | —      | _      | —     | _     | 0000          |

| RPOR14       | 069C  | _      | —      | —      | _          | —      | —      | _     | —     | _     | —     |       |       | RP120  | R<5:0> |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receive a request to transfer data, a simple fixed priority scheme, based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA controller provides these functional capabilities:

- Up to 15 DMA Channels

- Register Indirect With Post-Increment Addressing mode

- Register Indirect Without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU Interrupt after Half or Full Block Transfer Complete

- Byte or Word Transfers

- · Fixed Priority Channel Arbitration

- Manual (software) or Automatic (peripheral DMA requests) Transfer Initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two DPSRAM start addresses after each block transfer complete)

- DMA Request for Each Channel can be Selected from Any Supported Interrupt Source

- Debug Support Features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 0000000                              | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | —                                                       | —                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | —                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | —                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| SPI3 Transfer Done            | 01011011                             | 0x02A8 (SPI3BUF)                                        | 0x02A8 (SPI3BUF)                                       |

| SPI4 Transfer Done            | 01111011                             | 0x02C8 (SPI4BUF)                                        | 0x02C8 (SPI4BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             |                                                         | 0x0234 (U2TXREG)                                       |

| UART3RX – UART3 Receiver      | 01010010                             | 0x0256 (U3RXREG)                                        | —                                                      |

| UART3TX – UART3 Transmitter   | 01010011                             | —                                                       | 0x0254 (U3TXREG)                                       |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

## REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit |

|-------|---------------------------------------------------|

|       | 1 = Output Compare 4 module is disabled           |

|       | 0 = Output Compare 4 module is enabled            |

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit |

|       | 1 = Output Compare 3 module is disabled           |

|       | 0 = Output Compare 3 module is enabled            |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit |

|       | 1 = Output Compare 2 module is disabled           |

|       | 0 = Output Compare 2 module is enabled            |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit |

|       | 1 = Output Compare 1 module is disabled           |

|       |                                                   |

#### 11.7 Peripheral Pin Select Control Registers

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | —     | —     | —     |

| bit 7  |       |       |       |            |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn/RPIn Pin bits (see Table 11-2 for input pin selection numbers) 11111111 = Input tied to RP127 .

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-47: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP71  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP70  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 13-8 | <b>RP71R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP71 Output Pin bits |

|----------|-----------------------------------------------------------------------------------------|

|          | (see Table 11-3 for peripheral function numbers)                                        |

| bit 7-6  | Unimplemented: Read as '0'                                                              |

bit 5-0 **RP70R<5:0>:** Peripheral Output Function is Assigned to RP70 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### REGISTER 11-48: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP80  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP79  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

| bit 13-8 | RP80R<5:0>: Peripheral Output Function is Assigned to RP80 Output Pin bits |

|----------|----------------------------------------------------------------------------|

|          | (see Table 11-3 for peripheral function numbers)                           |

| bit 7-6  | Unimplemented: Read as '0'                                                 |

bit 5-0 **RP79R<5:0>:** Peripheral Output Function is Assigned to RP79 Output Pin bits (see Table 11-3 for peripheral function numbers)

## REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6 | STREN: SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Used in conjunction with the SCLREL bit.                                                                                                                                                                                                                                                                                                                       |

|       | 1 = Enables software or receives clock stretching                                                                                                                                                                                                                                                                                                              |

|       | 0 = Disables software or receives clock stretching                                                                                                                                                                                                                                                                                                             |

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                                                                                                                               |

|       | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                                                                                                                                        |

|       |                                                                                                                                                                                                                                                                                                                                                                |

| bit 4 | <ul> <li>ACKEN: Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits the ACKDT data bit. Hardware is clear at the end of a master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                    |

|       | 1 = Enables Receive mode for $I^2C$ . Hardware is clear at the end of the eighth bit of a master receive data byte.<br>0 = Receive sequence is not in progress                                                                                                                                                                                                 |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                              |

|       | <ul> <li>1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of a master Stop sequence.</li> <li>0 = Stop condition is not in progress</li> </ul>                                                                                                                                                                                 |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                   |

|       | 1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of a master Repeated Start sequence.                                                                                                                                                                                                                                |

|       | 0 = Repeated Start condition is not in progress                                                                                                                                                                                                                                                                                                                |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                                                                                                                                    |

|       | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of a master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                                                                                                                                              |

Note 1: When performing master operations, ensure that the IPMIEN bit is '0'.

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                               |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                        |

|       | <ul> <li>1 = Receiver is Idle</li> <li>0 = Receiver is active</li> </ul>                                                                                                                                                    |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                   |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                 |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                  |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                    |

|       | 0 = Framing error has not been detected                                                                                                                                                                                     |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                                                                             |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets<br/>the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                        |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                               |

|       |                                                                                                                                                                                                                             |

**Note 1:** Refer to **Section 17. "UART**" (DS70582) in the *"dsPIC33E/PIC24E Family Reference Manual"* for information on enabling the UARTx module for transmit operation.

| R-0                                                            | R-0<br>TERRO     | R-0<br>CNT<7:0>                         | R-0          | R-0          | R-0                           |

|----------------------------------------------------------------|------------------|-----------------------------------------|--------------|--------------|-------------------------------|

|                                                                | TERRO            | CNT<7:0>                                |              |              |                               |

|                                                                |                  |                                         |              |              |                               |

|                                                                |                  |                                         |              |              | bit 8                         |

|                                                                |                  |                                         |              |              |                               |

| R-0                                                            | R-0              | R-0                                     | R-0          | R-0          | R-0                           |

|                                                                | RERRO            | CNT<7:0>                                |              |              |                               |

|                                                                |                  |                                         |              |              | bit 0                         |

|                                                                |                  |                                         |              |              |                               |

|                                                                |                  |                                         |              |              |                               |

| adable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                                         |              |              |                               |

| -n = Value at POR (1' = Bit is set                             |                  | '0' = Bit is cleared x = Bit is unknown |              |              |                               |

|                                                                | / = Writable bit | RERRO                                   | RERRCNT<7:0> | RERRCNT<7:0> | <pre>RERRCNT&lt;7:0&gt;</pre> |

| REGISTER 21-8: | CXEC: ECANX TRANSMIT/RECEIVE ERROR COUNT REGISTER |

|----------------|---------------------------------------------------|

|                |                                                   |

| bit 15-8 | TERRCNT<7:0>: Transmit Error Count bits |

|----------|-----------------------------------------|

| bit 7-0  | RERRCNT<7:0>: Receive Error Count bits  |

#### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|--------|-------|-------|

| SJW   | <1:0> |       |       | BRP   | °<5:0> |       |       |

| bit 7 |       |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                       |

|----------|--------------------------------------------------------------------------------------------------|

| bit 7-6  | SJW<1:0>: Synchronization Jump Width bits                                                        |

|          | 11 = Length is 4 x TQ<br>10 = Length is 3 x TQ<br>01 = Length is 2 x TQ<br>00 = Length is 1 x TQ |

| bit 5-0  | BRP<5:0>: Baud Rate Prescaler bits                                                               |

|          | 11 1111 = TQ = 2 x 64 x 1/FCAN                                                                   |

|          | •                                                                                                |

|          | •                                                                                                |

|          | •                                                                                                |

|          | 00 0010 = TQ = 2 x 3 x 1/FCAN<br>00 0001 = TQ = 2 x 2 x 1/FCAN<br>00 0000 = TQ = 2 x 1 x 1/FCAN  |

| REGISTER     | 21-15: | CXBU     | FPN14: ECA                           |                 | 12-15 BUFFE      | RPOINTER        | REGISTER 4      |       |

|--------------|--------|----------|--------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| R/W-0        | R/\    | W-0      | R/W-0                                | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|              |        | F15BP    | 2<3:0>                               |                 |                  | F14E            | 3P<3:0>         |       |

| bit 15       |        |          |                                      |                 |                  |                 |                 | bit 8 |

| R/W-0        | R/     | W-0      | R/W-0                                | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|              |        | F13BP    | 2<3:0>                               |                 |                  | F12E            | 3P<3:0>         |       |

| bit 7        |        |          |                                      |                 |                  |                 |                 | bit 0 |

|              |        |          |                                      |                 |                  |                 |                 |       |

| Legend:      |        |          |                                      |                 |                  |                 |                 |       |

| R = Readab   | le bit |          | W = Writable                         | bit             | U = Unimplen     | nented bit, rea | ad as '0'       |       |

| -n = Value a | t POR  |          | '1' = Bit is set                     |                 | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

| bit 15-12    | F15BI  | P<3:0>:  | : RX Buffer Ma                       | sk for Filter 1 | 5 bits           |                 |                 |       |

|              | 1111   | = Filter | hits received in                     | n RX FIFO bu    | ffer             |                 |                 |       |

|              | 1110   | = Filter | hits received in                     | n RX Buffer 14  | 4                |                 |                 |       |

|              | •      |          |                                      |                 |                  |                 |                 |       |

|              | •      |          |                                      |                 |                  |                 |                 |       |

|              | •      |          |                                      |                 |                  |                 |                 |       |

|              |        |          | hits received in<br>hits received in |                 |                  |                 |                 |       |

|              |        |          |                                      |                 |                  |                 |                 |       |

### REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

| bit 11-8 | <b>F14BP&lt;3:0&gt;:</b> RX Buffer Mask for Filter 14 bits (same values as bit 15-12) |

|----------|---------------------------------------------------------------------------------------|

| bit 7-4  | F13BP<3:0>: RX Buffer Mask for Filter 13 bits (same values as bit 15-12)              |

bit 3-0 **F12BP<3:0>:** RX Buffer Mask for Filter 12 bits (same values as bit 15-12)

| <b>REGISTER</b> 2 | 22-6: UxCC            | N: USB CON                         | TROL REGI        | STER (HOST         | MODE)             |                    |               |

|-------------------|-----------------------|------------------------------------|------------------|--------------------|-------------------|--------------------|---------------|

| U-0               | U-0                   | U-0                                | U-0              | U-0                | U-0               | U-0                | U-0           |

| —                 | —                     | —                                  | —                | —                  | —                 | —                  | —             |

| bit 15            |                       |                                    |                  |                    |                   |                    | bit 8         |

|                   |                       |                                    |                  |                    |                   |                    |               |

| R-x, HSC          | R-x, HSC              | R/W-0                              | R/W-0            | R/W-0              | R/W-0             | R/W-0              | R/W-0         |

| JSTATE            | SE0                   | TOKBUSY                            | USBRST           | HOSTEN             | RESUME            | PPBRST             | SOFEN         |

| bit 7             |                       |                                    |                  |                    |                   |                    | bit 0         |

|                   |                       |                                    |                  |                    |                   |                    |               |

| Legend:           |                       | U = Unimplem                       | ented bit, read  | d as '0'           |                   |                    |               |

| R = Readable      | e bit                 | W = Writable b                     | bit              | HSC = Hardw        | are Settable/C    | learable bit       |               |

| -n = Value at     | POR                   | '1' = Bit is set                   |                  | '0' = Bit is clea  | ared              | x = Bit is unkn    | own           |

|                   |                       |                                    |                  |                    |                   |                    |               |

| bit 15-8          | Unimplemen            | ted: Read as '0                    | ,                |                    |                   |                    |               |

| bit 7             | JSTATE: Live          | Differential Re                    | ceiver J State   | Flag bit           |                   |                    |               |

|                   |                       | ifferential '0' in l               | ow-speed, diff   | erential '1' in fu | Ill-speed) is def | tected on the U    | SB            |

| h # 0             | 0 = No J state        |                                    | Elevelait        |                    |                   |                    |               |

| bit 6             |                       | gle-Ended Zero<br>ded zero is acti | -                | huo                |                   |                    |               |

|                   | 0                     | -ended zero is acti                |                  | bus                |                   |                    |               |

| bit 5             | -                     | oken Busy Stati                    |                  |                    |                   |                    |               |

|                   |                       | peing executed                     |                  | odule in On-Th     | e-Go state        |                    |               |

|                   |                       | is being execut                    |                  |                    |                   |                    |               |

| bit 4             | USBRST: US            | B Reset bit                        |                  |                    |                   |                    |               |

|                   |                       | set has been ge                    | enerated; for S  | Software Reset,    | application m     | ust set this bit f | for 50 ms and |

|                   | then clea             | et is terminated                   | I                |                    |                   |                    |               |

| bit 3             |                       | B Host Mode E                      |                  |                    |                   |                    |               |

| Sit O             |                       | capability is en                   |                  | wns on D+ and      | D- are activate   | d in hardware      |               |

|                   |                       | capability is dis                  |                  |                    |                   |                    |               |

| bit 2             | RESUME: US            | B Resume Sig                       | naling Enable    | bit                |                   |                    |               |

|                   | 1 = Resume<br>wake-up | signaling is activ                 | vated; software  | e must set the b   | oit for 10 ms and | d then clear to e  | enable remote |

|                   |                       | signaling is disa                  | abled            |                    |                   |                    |               |

| bit 1             |                       | g-Pong Buffers                     |                  |                    |                   |                    |               |

|                   | 1 = Resets a          | Il Ping-Pong Bu                    | ffer Pointers to |                    | fer descriptor b  | oanks              |               |

|                   | -                     | g Buffer Pointe                    |                  |                    |                   |                    |               |

| bit 0             |                       | Start-of-Frame                     |                  |                    |                   |                    |               |

|                   |                       | rame token is s<br>rame token is c |                  | 1 ms               |                   |                    |               |

|                   |                       |                                    | ISADIEU          |                    |                   |                    |               |

| <b>REGISTER</b>       | 22-7: UxAC  | DR: USB AD                         | DRESS REG       | SISTER                |                  |                 |       |

|-----------------------|-------------|------------------------------------|-----------------|-----------------------|------------------|-----------------|-------|

| U-0                   | U-0         | U-0                                | U-0             | U-0                   | U-0              | U-0             | U-0   |

| _                     | —           | _                                  | _               | —                     | —                | —               | _     |

| bit 15                |             |                                    |                 |                       |                  |                 | bit 8 |

| R/W-0                 | R/W-0       | R/W-0                              | R/W-0           | R/W-0                 | R/W-0            | R/W-0           | R/W-0 |

| LSPDEN <sup>(1)</sup> |             |                                    |                 | DEVADDR<6:0           | >                |                 |       |

| bit 7                 |             |                                    |                 |                       |                  |                 | bit C |

|                       |             |                                    |                 |                       |                  |                 |       |

| Legend:               |             |                                    |                 |                       |                  |                 |       |

| R = Readable          | e bit       | W = Writable I                     | oit             | U = Unimplem          | nented bit, read | l as '0'        |       |

| -n = Value at I       | POR         | '1' = Bit is set                   |                 | '0' = Bit is clea     | ared             | x = Bit is unkr | nown  |

| hit 15 0              | Unimploment | ted. Dood oo '                     | .,              |                       |                  |                 |       |

| bit 15-8              | •           | ited: Read as '0                   |                 | (4)                   |                  |                 |       |

| bit 7                 | LSPDEN: US  | B Low-Speed E                      | Enable Indicate | or bit <sup>(1)</sup> |                  |                 |       |

|                       |             | dule operates a<br>dule operates a |                 |                       |                  |                 |       |

| Note 1: | Host mode only. In Device mode, this bit is unimplemented. |

|---------|------------------------------------------------------------|

DEVADDR<6:0>: USB Device Address bits

#### REGISTER 22-8: UxTOK: USB TOKEN REGISTER (HOST MODE ONLY)

| U-0          | U-0                 | U-0                 | U-0                       | U-0               | U-0              | U-0             | U-0   |

|--------------|---------------------|---------------------|---------------------------|-------------------|------------------|-----------------|-------|

| _            | —                   | _                   | _                         | —                 | —                | _               | —     |

| bit 15       |                     |                     |                           |                   |                  |                 | bit 8 |

|              |                     |                     |                           |                   |                  |                 |       |

| R/W-0        | R/W-0               | R/W-0               | R/W-0                     | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|              | PID<                | 3:0> <sup>(1)</sup> |                           |                   | EP<              | 3:0>            |       |

| bit 7        |                     |                     |                           | ·                 |                  |                 | bit 0 |

|              |                     |                     |                           |                   |                  |                 |       |

| Legend:      |                     |                     |                           |                   |                  |                 |       |

| R = Readab   | le bit              | W = Writable I      | bit                       | U = Unimplem      | nented bit, read | as '0'          |       |

| -n = Value a | t POR               | '1' = Bit is set    |                           | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|              |                     |                     |                           |                   |                  |                 |       |

| bit 15-8     | Unimplemen          | ted: Read as '0     | )'                        |                   |                  |                 |       |

| bit 7-4      | PID<3:0>: To        | ken Type Identi     | ifier bits <sup>(1)</sup> |                   |                  |                 |       |

|              | 1101 = SETU         | JP (TX) token ty    | /pe transactior           | า                 |                  |                 |       |

|              | 1001 <b>= IN (R</b> | X) token type tr    | ansaction                 |                   |                  |                 |       |

|              | 0001 = OUT          | (TX) token type     | e transaction             |                   |                  |                 |       |

| bit 3-0      | EP<3:0>: Tok        | ken Command E       | Endpoint Addre            | ess bits          |                  |                 |       |

|              | This value mu       | ust specify a val   | lid endpoint or           | n the attached d  | evice.           |                 |       |

|              |                     |                     |                           |                   |                  |                 |       |

|              |                     |                     |                           |                   |                  |                 |       |

Note 1: All other combinations are reserved and are not to be used.

bit 6-0

# REGISTER 22-13: UxOTGIE: USB OTG INTERRUPT ENABLE REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0    | U-0 | R/W-0    |

|-------|----------|----------|--------|---------|----------|-----|----------|

| IDIE  | T1MSECIE | LSTATEIE | ACTVIE | SESVDIE | SESENDIE | —   | VBUSVDIE |

| bit 7 |          |          |        |         |          |     | bit 0    |

| Legend:    |           |                                                 |                       |                    |

|------------|-----------|-------------------------------------------------|-----------------------|--------------------|

| R = Reada  | ble bit   | W = Writable bit                                | U = Unimplemented bit | , read as '0'      |

| -n = Value | at POR    | '1' = Bit is set                                | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-8   | Unimple   | mented: Read as '0'                             |                       |                    |

| bit 7      | •         | Interrupt Enable bit                            |                       |                    |

|            |           | rupt is enabled                                 |                       |                    |

|            |           | rupt is disabled                                |                       |                    |

| bit 6      | T1MSEC    | IE: 1 Millisecond Timer Interr                  | rupt Enable bit       |                    |

|            | 1 = Inter | rupt is enabled                                 |                       |                    |

|            | 0 = Inter | rupt is disabled                                |                       |                    |

| bit 5      | LSTATE    | E: Line State Stable Interrupt                  | t Enable bit          |                    |

|            |           | rupt is enabled                                 |                       |                    |

|            | 0 = Inter | rupt is disabled                                |                       |                    |

| bit 4      |           | Bus Activity Interrupt Enable                   | e bit                 |                    |

|            |           | rupt is enabled                                 |                       |                    |

|            |           | rupt is disabled                                |                       |                    |

| bit 3      |           | E: Session Valid Interrupt Ena                  | able bit              |                    |

|            |           | rupt is enabled                                 |                       |                    |

| bit 2      |           | rupt is disabled                                | torrupt Epoblo bit    |                    |

| DIL Z      |           | IE: B-Device Session End In                     | iterrupt Enable bit   |                    |

|            |           | rupt is enabled<br>rupt is disabled             |                       |                    |

| bit 1      |           | mented: Read as '0'                             |                       |                    |

| bit 0      | •         |                                                 | provent Enable bit    |                    |

|            |           | IE: A-Device VBUS Valid Inte<br>rupt is enabled |                       |                    |

|            |           | rupt is disabled                                |                       |                    |

| TABLE 29-2:<br>Bit Field | Register           | RTSP Effect | S DESCRIPTION (CONTINUED) Description                                                                                                                                                                      |

|--------------------------|--------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | -                  |             | Watchdog Timer Window Enable bit                                                                                                                                                                           |

| WINDIS                   | FWDT               | Immediate   | 1 = Watchdog Timer is in Non-Window mode                                                                                                                                                                   |

|                          |                    |             | 0 = Watchdog Timer is in Window mode                                                                                                                                                                       |

| PLLKEN                   | FWDT               | Immediate   | PLL Lock Wait Enable bit                                                                                                                                                                                   |

|                          |                    |             | <ul> <li>1 = Clock switches to the PLL source will wait until the PLL lock signal is valid</li> <li>0 = Clock switch will not wait for PLL lock</li> </ul>                                                 |

| WDTPRE                   | FWDT               | Immediate   | Watchdog Timer Prescaler bit                                                                                                                                                                               |

|                          |                    |             | 1 = 1:128<br>0 = 1:32                                                                                                                                                                                      |

| APLK<1:0>                | FAS <sup>(2)</sup> | Immediate   | Auxiliary Segment Key bits                                                                                                                                                                                 |

|                          |                    |             | These bits must be set to '00' if AWRP = 1 and APL = 1. These bits must be set to '11' for any other value of the AWRP and APL bits.<br>Any mismatch between either the AWRP or APL bits and the APLK bits |

|                          |                    |             | (as described above), will result in code protection becoming enabled for<br>the Auxiliary Segment. A Flash bulk erase will be required to unlock the<br>device.                                           |

| APL                      | FAS <sup>(2)</sup> | Immediate   | Auxiliary Segment Code-Protect bit                                                                                                                                                                         |

|                          |                    |             | 1 = Auxiliary program memory is not code-protected                                                                                                                                                         |

|                          |                    |             | 0 = Auxiliary program memory is code-protected                                                                                                                                                             |

| AWRP                     | FAS <sup>(2)</sup> | Immediate   | Auxiliary Segment Write-Protect bit                                                                                                                                                                        |

|                          |                    |             | <ul><li>1 = Auxiliary program memory is not write-protected</li><li>0 = Auxiliary program memory is write-protected</li></ul>                                                                              |

| WDTPOST<3:0>             | FWDT               | Immediate   | Watchdog Timer Postscaler bits                                                                                                                                                                             |

|                          |                    |             | 1111 = 1:32,768                                                                                                                                                                                            |

|                          |                    |             | 1110 <b>= 1:16,384</b>                                                                                                                                                                                     |

|                          |                    |             | •                                                                                                                                                                                                          |

|                          |                    |             | •                                                                                                                                                                                                          |

|                          |                    |             | •                                                                                                                                                                                                          |

|                          |                    |             | 0001 = 1:2<br>0000 = 1:1                                                                                                                                                                                   |

| FPWRT<2:0>               | FPOR               | Immediate   | Power-on Reset Timer Value Select bits                                                                                                                                                                     |

| 11 10111 2.0             | 11 OIX             | ininediate  | 111 = PWRT = 128 ms                                                                                                                                                                                        |

|                          |                    |             | 110 = PWRT = 64 ms                                                                                                                                                                                         |

|                          |                    |             | 101 = PWRT = 32 ms                                                                                                                                                                                         |

|                          |                    |             | 100 = PWRT = 16 ms                                                                                                                                                                                         |

|                          |                    |             | 011 = PWRT = 8 ms                                                                                                                                                                                          |

|                          |                    |             | 010 = PWRT = 4 ms<br>001 = PWRT = 2 ms                                                                                                                                                                     |

|                          |                    |             | 000 = PWRT = Disabled                                                                                                                                                                                      |

| BOREN <sup>(1)</sup>     | FPOR               | Immediate   | Brown-out Reset (BOR) Detection Enable bit                                                                                                                                                                 |