Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 83                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 121-TFBGA                                                                         |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mu810t-i-bg |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11     | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|------------|------------|--------|-------|---------|-------|-------|-------|--------|-------|-------|-------|-------|---------------|

| N0        | 0000  |        |        |        |            | •          | •      |       | W0 (WR  | EG)   |       |       |        | •     |       |       | •     | 0000          |

| W1        | 0002  |        |        |        |            |            |        |       | W1      |       |       |       |        |       |       |       |       | 0000          |

| W2        | 0004  |        |        |        |            |            |        |       | W2      |       |       |       |        |       |       |       |       | 0000          |

| W3        | 0006  |        |        |        |            |            |        |       | W3      |       |       |       |        |       |       |       |       | 0000          |

| W4        | 8000  |        |        |        |            |            |        |       | W4      |       |       |       |        |       |       |       |       | 0000          |

| W5        | 000A  |        |        |        |            |            |        |       | W5      |       |       |       |        |       |       |       |       | 0000          |

| W6        | 000C  |        |        |        |            |            |        |       | W6      |       |       |       |        |       |       |       |       | 0000          |

| W7        | 000E  |        |        |        |            |            |        |       | W7      |       |       |       |        |       |       |       |       | 0000          |

| W8        | 0010  |        |        |        |            |            |        |       | W8      |       |       |       |        |       |       |       |       | 0000          |

| W9        | 0012  |        |        |        |            |            |        |       | W9      |       |       |       |        |       |       |       |       | 0000          |

| W10       | 0014  |        |        |        |            |            |        |       | W10     |       |       |       |        |       |       |       |       | 0000          |

| W11       | 0016  |        |        |        |            |            |        |       | W11     |       |       |       |        |       |       |       |       | 0000          |

| W12       | 0018  |        |        |        |            |            |        |       | W12     |       |       |       |        |       |       |       |       | 0000          |

| W13       | 001A  |        |        |        |            |            |        |       | W13     |       |       |       |        |       |       |       |       | 0000          |

| W14       | 001C  |        |        |        |            |            |        |       | W14     |       |       |       |        |       |       |       |       | 0000          |

| W15       | 001E  |        |        |        |            |            |        |       | W15     |       |       |       |        |       |       |       |       | 1000          |

| SPLIM     | 0020  |        |        |        |            |            |        |       | SPLIN   | Λ     |       |       |        |       |       |       |       | 0000          |

| ACCAL     | 0022  |        |        |        |            |            |        |       | ACCA    | L     |       |       |        |       |       |       |       | 0000          |

| ACCAH     | 0024  |        |        |        |            |            |        |       | ACCA    | Н     |       |       |        |       |       |       |       | 0000          |

| ACCAU     | 0026  |        |        | Sig    | n-Extensio | n of ACCA< | 39>    |       |         |       |       |       | AC     | CAU   |       |       |       | 0000          |

| ACCBL     | 0028  |        |        |        |            |            |        |       | ACCB    | L     |       |       |        |       |       |       |       | 0000          |

| ACCBH     | 002A  |        |        |        |            |            |        |       | ACCB    | Н     |       |       |        |       |       |       |       | 0000          |

| ACCBU     | 002C  |        |        | Sig    | n-Extensio | n of ACCB< | 39>    |       |         |       |       |       | AC     | CBU   |       |       |       | 0000          |

| PCL       | 002E  |        |        |        |            |            |        |       | PCL     |       |       |       |        |       |       |       | —     | 0000          |

| PCH       | 0030  | _      | _      | _      | _          | _          | _      | _     | —       | _     |       |       |        | PCH   |       |       |       | 0000          |

| DSRPAG    | 0032  | _      | _      | _      | _          | —          | _      |       |         |       |       | DSRP  | AG     |       |       |       |       | 0001          |

| DSWPAG    | 0034  | _      | _      | _      | _          | —          | _      | —     |         |       |       | [     | DSWPAG |       |       |       |       | 0001          |

| RCOUNT    | 0036  |        |        |        |            |            |        |       | RCOUN   | ΝT    |       |       |        |       |       |       |       | 0000          |

| DCOUNT    | 0038  |        |        |        |            |            |        |       | DCOUN   | NT    |       |       |        |       |       |       |       | 0000          |

| DOSTARTL  | 003A  |        |        |        |            |            |        | D     | OSTARTL |       |       |       |        |       |       |       | —     | 0000          |

| DOSTARTH  | 003C  | —      | _      | —      | —          | —          | —      | —     | —       | —     | —     |       |        | DOST  | ARTH  |       |       | 0000          |

| DOENDL    | 003E  |        |        |        |            |            |        |       | DOENDL  |       |       | •     |        |       |       |       | —     | 0000          |

| DOENDH    | 0040  | _      | _      | _      | _          | _          | _      | _     | _       | _     | _     |       |        | DOE   | NDH   |       |       | 0000          |

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXX(GP/MC/MU)806/810/814 DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12   | Bit 11 | Bit 10       | Bit 9       | Bit 8    | Bit 7       | Bit 6       | Bit 5       | Bit 4      | Bit 3         | Bit 2         | Bit 1           | Bit 0         | All<br>Resets |

|--------------|-------|--------|--------|------------|----------|--------|--------------|-------------|----------|-------------|-------------|-------------|------------|---------------|---------------|-----------------|---------------|---------------|

| IFS0         | 0800  | NVMIF  | DMA1IF | AD1IF      | U1TXIF   | U1RXIF | SPI1IF       | SPI1EIF     | T3IF     | T2IF        | OC2IF       | IC2IF       | DMA0IF     | T1IF          | OC1IF         | IC1IF           | <b>INT0IF</b> | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF     | T4IF   | OC4IF        | OC3IF       | DMA2IF   | IC8IF       | IC7IF       | AD2IF       | INT1IF     | CNIF          | CMIF          | MI2C1IF         | SI2C1IF       | 0000          |

| IFS2         | 0804  | T6IF   | DMA4IF | PMPIF      | OC8IF    | OC7IF  | OC6IF        | OC5IF       | IC6IF    | IC5IF       | IC4IF       | IC3IF       | DMA3IF     | C1IF          | C1RXIF        | SPI2IF          | SPI2EIF       | 0000          |

| IFS3         | 0806  | -      | RTCIF  | DMA5IF     | DCIIF    | DCIEIF | QEI1IF       | PSEMIF      | C2IF     | C2RXIF      | INT4IF      | INT3IF      | T9IF       | T8IF          | MI2C2IF       | SI2C2IF         | T7IF          | 0000          |

| IFS4         | 0808  |        | _      | _          | _        | QEI2IF | —            | PSESMIF     | _        | C2TXIF      | C1TXIF      | DMA7IF      | DMA6IF     | CRCIF         | U2EIF         | U1EIF           | _             | 0000          |

| IFS5         | 080A  | PWM2IF | PWM1IF | IC9IF      | OC9IF    | SPI3IF | SPI3EIF      | U4TXIF      | U4RXIF   | U4EIF       | _           | _           | _          | <b>U3TXIF</b> | <b>U3RXIF</b> | <b>U3EIF</b>    | _             | 0000          |

| IFS6         | 080C  | -      | _      | _          | _        | _      | —            | _           | _        |             | _           | _           | -          | _             | _             | PWM4IF          | PWM3IF        | 0000          |

| IFS7         | 080E  | IC11IF | OC11IF | IC10IF     | OC10IF   | SPI4IF | SPI4EIF      | DMA11IF     | DMA10IF  | DMA9IF      | DMA8IF      | _           | _          | _             | —             | _               | _             | 0000          |

| IFS8         | 0810  | _      | ICDIF  | IC16IF     | OC16IF   | IC15IF | OC15IF       | IC14IF      | OC14IF   | IC13IF      | OC13IF      | —           | DMA14IF    | DMA13IF       | DMA12IF       | IC12IF          | OC12IF        | 0000          |

| IEC0         | 0820  | NVMIE  | DMA1IE | AD1IE      | U1TXIE   | U1RXIE | SPI1IE       | SPI1EIE     | T3IE     | T2IE        | OC2IE       | IC2IE       | DMA0IE     | T1IE          | OC1IE         | IC1IE           | INT0IE        | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE     | T4IE   | OC4IE        | OC3IE       | DMA2IE   | IC8IE       | IC7IE       | AD2IE       | INT1IE     | CNIE          | CMIE          | MI2C1IE         | SI2C1IE       | 0000          |

| IEC2         | 0824  | T6IE   | DMA4IE | PMPIE      | OC8IE    | OC7IE  | OC6IE        | OC5IE       | IC6IE    | IC5IE       | IC4IE       | IC3IE       | DMA3IE     | C1IE          | C1RXIE        | SPI2IE          | SPI2EIE       | 0000          |

| IEC3         | 0826  | _      | RTCIE  | DMA5IE     | DCIIE    | DCIEIE | QEI1IE       | PSEMIE      | C2IE     | C2RXIE      | INT4IE      | INT3IE      | T9IE       | T8IE          | MI2C2IE       | SI2C2IE         | T7IE          | 0000          |

| IEC4         | 0828  |        | _      | _          | _        | QEI2IE | —            | PSESMIE     | _        | C2TXIE      | C1TXIE      | DMA7IE      | DMA6IE     | CRCIE         | U2EIE         | U1EIE           | —             | 0000          |

| IEC5         | 082A  | PWM2IE | PWM1IE | IC9IE      | OC9IE    | SPI3IE | SPI3EIE      | U4TXIE      | U4RXIE   | U4EIE       | _           | _           | _          | <b>U3TXIE</b> | <b>U3RXIE</b> | <b>U3EIE</b>    | _             | 0000          |

| IEC6         | 082C  | _      | _      | _          | _        | _      | —            | _           | _        |             | _           | _           | -          | _             | _             | PWM4IE          | PWM3IE        | 0000          |

| IEC7         | 082E  | IC11IE | OC11IE | IC10IE     | OC10IE   | SPI4IE | SPI4EIE      | DMA11IE     | DMA10IE  | DMA9IE      | DMA8IE      | _           | -          | _             | _             | _               | _             | 0000          |

| IEC8         | 0830  | _      | ICDIE  | IC16IE     | OC16IE   | IC15IE | OC15IE       | IC14IE      | OC14IE   | IC13IE      | OC13IE      | —           | DMA14IE    | DMA13IE       | DMA12IE       | IC12IE          | OC12IE        | 0000          |

| IPC0         | 0840  |        |        | T1IP<2:0>  |          | _      |              | OC1IP<2:0>  | >        |             |             | IC1IP<2:0>  |            | _             |               | INT0IP<2:0>     | •             | 4444          |

| IPC1         | 0842  |        |        | T2IP<2:0>  |          | _      |              | OC2IP<2:0>  | >        |             |             | IC2IP<2:0>  |            | _             | [             | DMA0IP<2:0>     | >             | 4444          |

| IPC2         | 0844  |        |        | U1RXIP<2:0 | )>       | _      |              | SPI1IP<2:0  | >        |             |             | SPI1EIP<2:0 | >          | _             |               | T3IP<2:0>       |               | 4444          |

| IPC3         | 0846  | _      |        | NVMIP<2:0  | >        | —      |              | DMA1IP<2:0  | >        |             |             | AD1IP<2:0>  |            | -             |               | J1TXIP<2:0>     | •             | 4444          |

| IPC4         | 0848  | _      |        | CNIP<2:0>  | •        | _      |              | CMIP<2:0>   |          | -           |             | MI2C1IP<2:0 | >          | -             | 5             | SI2C1IP<2:0>    | >             | 4444          |

| IPC5         | 084A  | _      |        | IC8IP<2:0> | <b>`</b> | _      |              | IC7IP<2:0>  |          | -           |             | AD2IP<2:0>  |            | -             |               | INT1IP<2:0>     |               | 4444          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |          | _      |              | OC4IP<2:0>  | <b>`</b> | -           |             | OC3IP<2:0>  |            | -             | [             | )<br>MA2IP<2:0> | >             | 4444          |

| IPC7         | 084E  | _      |        | U2TXIP<2:0 | )>       | _      |              | U2RXIP<2:0  | >        | -           |             | INT2IP<2:0> |            | -             |               | T5IP<2:0>       |               | 4444          |

| IPC8         | 0850  | _      |        | C1IP<2:0>  |          | _      |              | C1RXIP<2:0  | >        | -           |             | SPI2IP<2:0> |            | -             | 5             | SPI2EIP<2:0>    | >             | 4444          |

| IPC9         | 0852  | _      |        | IC5IP<2:0> | <b>`</b> | _      |              | IC4IP<2:0>  |          | -           |             | IC3IP<2:0>  |            | -             | [             | DMA3IP<2:0>     | >             | 4444          |

| IPC10        | 0854  | _      |        | OC7IP<2:0  | >        | —      |              | OC6IP<2:0>  | <b>`</b> | _           |             | OC5IP<2:0>  |            | _             |               | IC6IP<2:0>      |               | 4444          |

| IPC11        | 0856  | _      |        | T6IP<2:0>  |          | _      |              | DMA4IP<2:0  | >        | -           |             | PMPIP<2:0>  |            | -             |               | OC8IP<2:0>      |               | 4444          |

| IPC12        | 0858  | _      |        | T8IP<2:0>  |          | _      | MI2C2IP<2:0> |             | _        |             | SI2C2IP<2:0 | >           | _          |               | T7IP<2:0>     |                 | 4444          |               |

| IPC13        | 085A  |        |        | C2RXIP<2:0 | )>       | _      |              | INT4IP<2:0> | >        | _           |             | INT3IP<2:0> |            | _             | T9IP<2:0>     |                 |               | 4444          |

| IPC14        | 085C  | _      |        | DCIEIP<2:0 | >        | _      | QEI1IP<2:0>  |             | _        |             | PSEMIP<2:0  | >           | _          | C2IP<2:0>     |               |                 | 4444          |               |

| IPC15        | 085E  | _      |        | _          | _        | _      | RTCIP<2:0>   |             |          | DMA5IP<2:0> |             |             | DCIIP<2:0> |               |               | 0444            |               |               |

DECISTED MAD FOD IL DIGGEDWWWWGGGG DEVICES ONLY

\_ -

. .

INTERDURT

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-22: I2C1 and I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5    | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|----------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | _       | _      | —       | -      | —      | —      | —      | —     |       |       |          | I2Cx Rece    | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202  | _       | _      | —       | _      | _      | —      | —      | —     |       |       |          | I2Cx Trans   | mit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204  | _       | _      | _       | _      | _      | _      | _      |       |       |       | Bai      | ud Rate Gen  | erator       |       |       |       | 0000          |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT    | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D_A      | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      |        |       |       |       | I2Cx Add | ess Register |              |       |       |       | 0000          |

| I2C1MSK      | 020C  | _       | _      | _       | _      | _      | _      |        |       |       |       | I2Cx Ad  | dress Mask   |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | _       | _      | _       | _      | _      | _      | _      | _     |       |       |          | I2Cx Rece    | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | _       | _      | _       | _      | _      | _      | _      | _     |       |       |          | I2Cx Trans   | mit Register |       |       |       | OOFF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | _      | _      |       |       |       | Bai      | ud Rate Gen  | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | —      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT    | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | —       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D_A      | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | —       | _      | _      | —      |        |       |       |       | I2Cx Add | ess Register |              |       |       |       | 0000          |

| I2C2MSK      | 021C  | _       |        | —       | _      | _      |        |        |       |       |       | I2Cx Ad  | dress Mask   |              |       |       |       | 0000          |

|              |       |         |        |         |        |        |        |        |       |       |       |          |              |              |       |       |       |               |

Legend:

- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------|---------|--------|--------|--------|--------|--------|--------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | DCIMD  | I2C1MD  | U2MD    | U1MD   | SPI2MD | SPI1MD | C2MD   | C1MD   | AD1MD  | 0000          |

| PMD2         | 0762  | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD  | OC8MD   | OC7MD   | OC6MD  | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3         | 0764  | T9MD   | T8MD   | T7MD   | T6MD   | —      | CMPMD  | RTCCMD | PMPMD  | CRCMD   | —       | QEI2MD |        | U3MD   |        | I2C2MD | AD2MD  | 0000          |

| PMD4         | 0766  | —      |        | _      | —      | _      | —      | —      |        |         | _       | U4MD   |        | REFOMD |        |        | USB1MD | 0000          |

| PMD5         | 0768  | IC16MD | IC15MD | IC14MD | IC13MD | IC12MD | IC11MD | IC10MD | IC9MD  | OC16MD  | OC15MD  | OC14MD | OC13MD | OC12MD | OC11MD | OC10MD | OC9MD  | 0000          |

| PMD6         | 076A  | —      | PWM7MD | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD |         | _       | -      |        | —      |        | SPI4MD | SPI3MD | 0000          |

|              |       | —      |        | _      | —      | _      | —      | —      |        | DMA12MD | DMA8MD  | DMA4MD | DMA0MD | —      |        |        |        | 0000          |

| PMD7         | 076C  | —      |        | _      | _      | _      | —      | _      |        | DMA13MD | DMA9MD  | DMA5MD | DMA1MD | —      |        |        |        | 0000          |

| FINDT        | 0700  | —      |        | _      | _      | _      | —      | _      |        | DMA14MD | DMA10MD | DMA6MD | DMA2MD | —      |        |        |        | 0000          |

|              |       | _      | _      | _      | _      | _      | —      | _      | _      | -       | DMA11MD | DMA7MD | DMA3MD | —      | _      | _      |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-48: PMD REGISTER MAP FOR dsPIC33EPXXXMU810 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------|---------|--------|--------|--------|--------|--------|--------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | DCIMD  | I2C1MD  | U2MD    | U1MD   | SPI2MD | SPI1MD | C2MD   | C1MD   | AD1MD  | 0000          |

| PMD2         | 0762  | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD  | OC8MD   | OC7MD   | OC6MD  | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3         | 0764  | T9MD   | T8MD   | T7MD   | T6MD   | _      | CMPMD  | RTCCMD | PMPMD  | CRCMD   | _       | QEI2MD | _      | U3MD   | _      | I2C2MD | AD2MD  | 0000          |

| PMD4         | 0766  | _      | —      | —      | —      | —      | _      | —      |        | —       | —       | U4MD   |        | REFOMD | _      | _      | USB1MD | 0000          |

| PMD5         | 0768  | IC16MD | IC15MD | IC14MD | IC13MD | IC12MD | IC11MD | IC10MD | IC9MD  | OC16MD  | OC15MD  | OC14MD | OC13MD | OC12MD | OC11MD | OC10MD | OC9MD  | 0000          |

| PMD6         | 076A  | _      | —      | PWM6MD | PWM5MD | PWM4MD | PWM3MD | PWM2MD | PWM1MD | —       | —       |        |        | _      |        | SPI4MD | SPI3MD | 0000          |

|              |       | -      | _      | _      | _      | _      | _      | _      | _      | DMA12MD | DMA8MD  | DMA4MD | DMA0MD | _      | _      | _      | _      | 0000          |

| PMD7         | 076C  | _      | —      | —      | —      | —      | _      | —      |        | DMA13MD | DMA9MD  | DMA5MD | DMA1MD | _      | _      | _      |        | 0000          |

|              | 0/00  | _      | —      | —      | —      | —      | _      | —      |        | DMA14MD | DMA10MD | DMA6MD | DMA2MD | _      | _      | _      |        | 0000          |

|              |       | _      | —      | _      | —      | _      | _      | _      | _      | _       | DMA11MD | DMA7MD | DMA3MD | _      | _      | _      | _      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

TABLE 4-75: FUNDAMENTAL ADDRESSING MODES SUPPORTED

### 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions (dsPIC33EPXXXMU806/810/814 and PIC24EPXXXGU810/814) and the DSP accumulator class of instructions (dsPIC33EPXXXMU806/810/ 814 only) provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

**Note:** Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMU806/810/814 DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

# 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

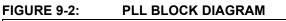

# 9.1 CPU Clocking System

The dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 family of devices provides seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase-Locked Loop (PLL)

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- Low-Power RC (LPRC) Oscillator

- FRC Oscillator with postscaler

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

### EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = FOSC/2

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relation between input frequency (FIN) and output frequency (FOSC).

Equation 9-3 provides the relation between input frequency (FIN) and VCO frequency (FVCO).

# EQUATION 9-2: Fosc CALCULATION

$$FOSC = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where,

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$ M = PLLDIV + 2

# EQUATION 9-3: Fvco CALCULATION

$$FVCO = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

| U-0          | R/W-0                      | R/W-0                                                                       | R/W-0                | R/W-0            | R/W-0           | R/W-0           | R/W-0    |

|--------------|----------------------------|-----------------------------------------------------------------------------|----------------------|------------------|-----------------|-----------------|----------|

| —            |                            |                                                                             |                      | T5CKR<6:0>       | •               |                 |          |

| bit 15       |                            |                                                                             |                      |                  |                 |                 | bit 8    |

|              |                            |                                                                             |                      |                  |                 |                 |          |

| U-0          | R/W-0                      | R/W-0                                                                       | R/W-0                | R/W-0            | R/W-0           | R/W-0           | R/W-0    |

| —            |                            |                                                                             |                      | T4CKR<6:0>       | •               |                 |          |

| bit 7        |                            |                                                                             |                      |                  |                 |                 | bit 0    |

|              |                            |                                                                             |                      |                  |                 |                 |          |

| Legend:      |                            |                                                                             |                      |                  |                 |                 |          |

| R = Readat   | ole bit                    | W = Writable                                                                | bit                  | U = Unimpler     | mented bit, rea | ad as '0'       |          |

| -n = Value a | at POR                     | '1' = Bit is set                                                            |                      | '0' = Bit is cle | ared            | x = Bit is unkr | nown     |

|              | 0000001 =                  | Input tied to RP<br>Input tied to CM<br>Input tied to Vss                   | P1                   |                  |                 |                 |          |

| bit 7        | Unimpleme                  | nted: Read as '                                                             | 0'                   |                  |                 |                 |          |

| bit 6-0      | (see Table 1<br>11111111 = | : Assign Timer<br>1-2 for input pin<br>Input tied to RP<br>Input tied to CM | selection nun<br>127 |                  | he Correspond   | ding RPn/RPIn F | Pin bits |

### REGISTER 11-5: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| U-0          | R/W-0        | R/W-0                                                                      | R/W-0     | R/W-0             | R/W-0           | R/W-0            | R/W-0  |

|--------------|--------------|----------------------------------------------------------------------------|-----------|-------------------|-----------------|------------------|--------|

|              |              |                                                                            |           | U1CTSR<6:02       | >               |                  |        |

| bit 15       |              |                                                                            |           |                   |                 |                  | bit 8  |

| U-0          | R/W-0        | R/W-0                                                                      | R/W-0     | R/W-0             | R/W-0           | R/W-0            | R/W-0  |

|              | 10.00-0      | 10.00-0                                                                    | 10.00-0   | U1RXR<6:0>        |                 | 1000-0           | 1000-0 |

| bit 7        |              |                                                                            |           | 01101110.0        |                 |                  | bit 0  |

|              |              |                                                                            |           |                   |                 |                  |        |

| Legend:      |              |                                                                            |           |                   |                 |                  |        |

| R = Readab   | ole bit      | W = Writable                                                               | bit       | U = Unimplen      | nented bit, rea | d as '0'         |        |

| -n = Value a | it POR       | '1' = Bit is set                                                           |           | '0' = Bit is clea | ared            | x = Bit is unkr  | nown   |

|              | 1111111 = lr | -2 for input pin<br>nput tied to RP<br>nput tied to CM<br>nput tied to Vss | 127<br>P1 |                   |                 |                  |        |

| bit 7        | Unimplemen   | nted: Read as '                                                            | 0'        |                   |                 |                  |        |

| bit 6-0      |              | <ul> <li>Assign UART</li> <li>2 for input pin</li> </ul>                   |           |                   | rresponding R   | Pn/RPIn Pin bits | 3      |

## REGISTER 11-19: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| R-0              | R-0<br>TERRO     | R-0<br>CNT<7:0>     | R-0          | R-0                | R-0                           |

|------------------|------------------|---------------------|--------------|--------------------|-------------------------------|

|                  | TERRO            | CNT<7:0>            |              |                    |                               |

|                  |                  |                     |              |                    |                               |

|                  |                  |                     |              |                    | bit 8                         |

|                  |                  |                     |              |                    |                               |

| R-0              | R-0              | R-0                 | R-0          | R-0                | R-0                           |

|                  | RERRO            | CNT<7:0>            |              |                    |                               |

|                  |                  |                     |              |                    | bit 0                         |

|                  |                  |                     |              |                    |                               |

|                  |                  |                     |              |                    |                               |

| ' = Writable bit |                  | U = Unimpleme       | nted bit, re | ad as '0'          |                               |

| ' = Bit is set   |                  | '0' = Bit is cleare | ed           | x = Bit is unknown |                               |

|                  | / = Writable bit | RERRO               | RERRCNT<7:0> | RERRCNT<7:0>       | <pre>RERRCNT&lt;7:0&gt;</pre> |

| REGISTER 21-8: | CXEC: ECANX TRANSMIT/RECEIVE ERROR COUNT REGISTER |

|----------------|---------------------------------------------------|

|                |                                                   |

| bit 15-8 | TERRCNT<7:0>: Transmit Error Count bits |

|----------|-----------------------------------------|

| bit 7-0  | RERRCNT<7:0>: Receive Error Count bits  |

### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|

| —            | —   | —   | _   | —   | —   | —   | —   |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |

| R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|----------|-------|-------|-------|-------|-------|

| SJW   | <1:0> | BRP<5:0> |       |       |       |       |       |

| bit 7 |       |          |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                                |  |  |

|-------------------|------------------|-----------------------------|--------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown             |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                       |  |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 7-6  | SJW<1:0>: Synchronization Jump Width bits                                                        |  |  |  |  |  |  |  |

|          | 11 = Length is 4 x TQ<br>10 = Length is 3 x TQ<br>01 = Length is 2 x TQ<br>00 = Length is 1 x TQ |  |  |  |  |  |  |  |

| bit 5-0  | BRP<5:0>: Baud Rate Prescaler bits                                                               |  |  |  |  |  |  |  |

|          | 11 1111 = TQ = 2 x 64 x 1/FCAN                                                                   |  |  |  |  |  |  |  |

|          | •                                                                                                |  |  |  |  |  |  |  |

|          | •                                                                                                |  |  |  |  |  |  |  |

|          | •                                                                                                |  |  |  |  |  |  |  |

|          | 00 0010 = TQ = 2 x 3 x 1/FCAN<br>00 0001 = TQ = 2 x 2 x 1/FCAN<br>00 0000 = TQ = 2 x 1 x 1/FCAN  |  |  |  |  |  |  |  |

| REGISTER 22-3: | UxPWRC: USB POWER CONTROL REGISTER |

|----------------|------------------------------------|

|----------------|------------------------------------|

| <u> </u>     | U-0 |

|--------------|-----|-----|-----|-----|-----|-----|-----|-----|

| bit 15 bit 8 |     | —   | —   | —   | —   | _   | —   | —   |

|              |     |     |     |     |     |     |     |     |

| HS, HC      | U-0 | U-0 | R/W     | U-0 | U-0 | R/W-0, HC | R/W-0                 |  |

|-------------|-----|-----|---------|-----|-----|-----------|-----------------------|--|

| UACTPND     | —   | —   | USLPGRD | _   | -   | USUSPND   | USBPWR <sup>(1)</sup> |  |

| bit 7 bit 0 |     |     |         |     |     |           |                       |  |

| Legend:           | egend: HS = Hardware Settable bit |                                    | it                 |  |

|-------------------|-----------------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set                  | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | UACTPND: USB Activity Pending bit                                                                                                                              |

|          | <ul> <li>1 = Module should not be suspended at the moment (requires the USLPGRD bit to be set)</li> <li>0 = Module may be suspended or powered down</li> </ul> |

| bit 6-5  | Unimplemented: Read as '0'                                                                                                                                     |

| bit 4    | USLPGRD: USB Sleep Guard bit                                                                                                                                   |

|          | <ul> <li>1 = Indicates to the USB module that it is about to be suspended or powered down</li> <li>0 = No suspend</li> </ul>                                   |

| bit 3-2  | Unimplemented: Read as '0'                                                                                                                                     |

| bit 1    | USUSPND: USB Suspend Mode Enable bit                                                                                                                           |

|          | <ul> <li>1 = USB OTG module is in Suspend mode</li> <li>0 = Normal USB OTG operation</li> </ul>                                                                |

| bit 0    | USBPWR: USB Operation Enable bit <sup>(1)</sup>                                                                                                                |

|          | 1 = USB OTG module is enabled                                                                                                                                  |

|          | 0 = USB OTG module is disabled                                                                                                                                 |

**Note 1:** Do not clear this bit unless the HOSTEN, USBEN and OTGEN bits (UxCON<3,0> and UxOTGCON<2>) are also cleared.

# REGISTER 22-13: UxOTGIE: USB OTG INTERRUPT ENABLE REGISTER (HOST MODE ONLY)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0    | U-0 | R/W-0    |

|-------|----------|----------|--------|---------|----------|-----|----------|

| IDIE  | T1MSECIE | LSTATEIE | ACTVIE | SESVDIE | SESENDIE | —   | VBUSVDIE |

| bit 7 |          |          |        |         |          |     | bit 0    |

| Legend:           |           |                                     |                       |                    |

|-------------------|-----------|-------------------------------------|-----------------------|--------------------|

| R = Reada         | ble bit   | W = Writable bit                    | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR |           | '1' = Bit is set                    | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-8          | Unimple   | mented: Read as '0'                 |                       |                    |

| bit 7             | •         | Interrupt Enable bit                |                       |                    |

|                   |           | rupt is enabled                     |                       |                    |

|                   |           | rupt is disabled                    |                       |                    |

| bit 6             | T1MSEC    | IE: 1 Millisecond Timer Interr      | rupt Enable bit       |                    |

|                   | 1 = Inter | rupt is enabled                     |                       |                    |

|                   | 0 = Inter | rupt is disabled                    |                       |                    |

| bit 5             | LSTATE    | E: Line State Stable Interrupt      | t Enable bit          |                    |

|                   |           | rupt is enabled                     |                       |                    |

|                   | 0 = Inter | rupt is disabled                    |                       |                    |

| bit 4             |           | Bus Activity Interrupt Enable       | e bit                 |                    |

|                   |           | rupt is enabled                     |                       |                    |

|                   |           | rupt is disabled                    |                       |                    |

| bit 3             |           | E: Session Valid Interrupt Ena      | adie dit              |                    |

|                   |           | rupt is enabled<br>rupt is disabled |                       |                    |

| bit 2             |           | IE: B-Device Session End In         | terrupt Enable bit    |                    |

|                   |           | rupt is enabled                     |                       |                    |

|                   |           | rupt is disabled                    |                       |                    |

| bit 1             | Unimple   | mented: Read as '0'                 |                       |                    |

| bit 0             | •         | IE: A-Device VBUS Valid Inte        | rrupt Enable bit      |                    |

|                   |           | rupt is enabled                     |                       |                    |

|                   |           | rupt is disabled                    |                       |                    |

### REGISTER 23-1: ADxCON1: ADCx CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | <ul> <li>111 = Reserved</li> <li>110 = PWM Generator 7 primary trigger compare ends sampling and starts conversion<sup>(2)</sup></li> <li>101 = PWM Generator 6 primary trigger compare ends sampling and starts conversion<sup>(2)</sup></li> <li>100 = PWM Generator 5 primary trigger compare ends sampling and starts conversion<sup>(2)</sup></li> <li>011 = PWM Generator 4 primary trigger compare ends sampling and starts conversion<sup>(2)</sup></li> <li>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion<sup>(2)</sup></li> <li>010 = PWM Generator 2 primary trigger compare ends sampling and starts conversion<sup>(2)</sup></li> <li>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion<sup>(2)</sup></li> <li>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion<sup>(2)</sup></li> <li>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion<sup>(2)</sup></li> <li>011 = Internal counter ends sampling and starts conversion (auto-convert)</li> <li>110 = Reserved</li> <li>101 = PWM secondary Special Event Trigger ends sampling and starts conversion<sup>(2)</sup></li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion<sup>(2)</sup></li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion<sup>(2)</sup></li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion<sup>(2)</sup></li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion<sup>(2)</sup></li> <li>010 = Timer3 compare ends sampling and starts conversion</li> </ul> |

|         | 000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4   | SSRCG: Sample Clock Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | (See bits<7-5> for details.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or 1x)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>When AD12B = 1, SIMSAM is: U-0, Unimplemented, Read as '0'</li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bit 2   | ASAM: ADC Sample Auto-Start bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| bit 1   | SAMP: ADC Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | <ul> <li>1 = ADC S&amp;H amplifiers are sampling</li> <li>0 = ADC S&amp;H amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1.</li> <li>If SSRC = 000, software can write '0' to end sampling and start conversion. If SSRC ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 0   | DONE: ADC Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |