Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART, USB OTG            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 122                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mu814-i-pl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

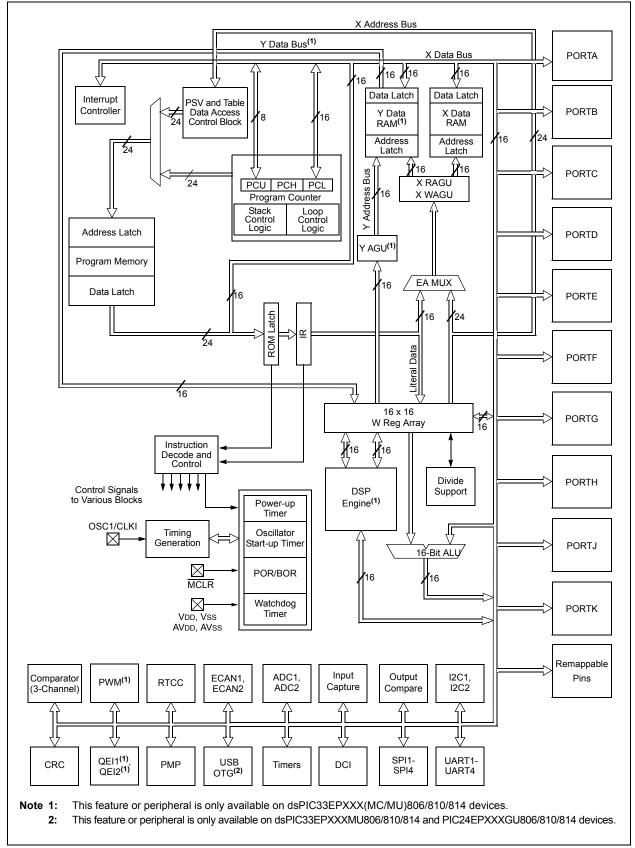

# FIGURE 3-1: dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 CPU BLOCK DIAGRAM

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11     | Bit 10 | Bit 9 | Bit 8   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|------------|------------|--------|-------|---------|-------|-------|-------|--------|-------|-------|-------|-------|---------------|

| N0        | 0000  |        |        |        |            | •          | •      |       | W0 (WR  | EG)   |       |       |        | •     |       |       | •     | 0000          |

| W1        | 0002  |        |        |        |            |            |        |       | W1      |       |       |       |        |       |       |       |       | 0000          |

| W2        | 0004  |        |        |        |            |            |        |       | W2      |       |       |       |        |       |       |       |       | 0000          |

| W3        | 0006  |        |        |        |            |            |        |       | W3      |       |       |       |        |       |       |       |       | 0000          |

| W4        | 8000  |        |        |        |            |            |        |       | W4      |       |       |       |        |       |       |       |       | 0000          |

| W5        | 000A  |        |        |        |            |            |        |       | W5      |       |       |       |        |       |       |       |       | 0000          |

| W6        | 000C  |        |        |        |            |            |        |       | W6      |       |       |       |        |       |       |       |       | 0000          |

| W7        | 000E  |        |        |        |            |            |        |       | W7      |       |       |       |        |       |       |       |       | 0000          |

| W8        | 0010  |        |        |        |            |            |        |       | W8      |       |       |       |        |       |       |       |       | 0000          |

| W9        | 0012  |        |        |        |            |            |        |       | W9      |       |       |       |        |       |       |       |       | 0000          |

| W10       | 0014  |        |        |        |            |            |        |       | W10     |       |       |       |        |       |       |       |       | 0000          |

| W11       | 0016  |        |        |        |            |            |        |       | W11     |       |       |       |        |       |       |       |       | 0000          |

| W12       | 0018  |        |        |        |            |            |        |       | W12     |       |       |       |        |       |       |       |       | 0000          |

| W13       | 001A  |        |        |        |            |            |        |       | W13     |       |       |       |        |       |       |       |       | 0000          |

| W14       | 001C  |        |        |        |            |            |        |       | W14     |       |       |       |        |       |       |       |       | 0000          |

| W15       | 001E  |        |        |        |            |            |        |       | W15     |       |       |       |        |       |       |       |       | 1000          |

| SPLIM     | 0020  |        |        |        |            |            |        |       | SPLIN   | Λ     |       |       |        |       |       |       |       | 0000          |

| ACCAL     | 0022  |        |        |        |            |            |        |       | ACCA    | L     |       |       |        |       |       |       |       | 0000          |

| ACCAH     | 0024  |        |        |        |            |            |        |       | ACCA    | Н     |       |       |        |       |       |       |       | 0000          |

| ACCAU     | 0026  |        |        | Sig    | n-Extensio | n of ACCA< | 39>    |       |         |       |       |       | AC     | CAU   |       |       |       | 0000          |

| ACCBL     | 0028  |        |        |        |            |            |        |       | ACCB    | L     |       |       |        |       |       |       |       | 0000          |

| ACCBH     | 002A  |        |        |        |            |            |        |       | ACCB    | Н     |       |       |        |       |       |       |       | 0000          |

| ACCBU     | 002C  |        |        | Sig    | n-Extensio | n of ACCB< | 39>    |       |         |       |       |       | AC     | CBU   |       |       |       | 0000          |

| PCL       | 002E  |        |        |        |            |            |        |       | PCL     |       |       |       |        |       |       |       | —     | 0000          |

| PCH       | 0030  | _      | _      | _      | _          | _          | _      | _     | —       | _     |       |       |        | PCH   |       |       |       | 0000          |

| DSRPAG    | 0032  | _      | _      | _      | _          | —          | _      |       |         |       |       | DSRP  | AG     |       |       |       |       | 0001          |

| DSWPAG    | 0034  | _      | _      | _      | _          | —          | _      | —     |         |       |       | [     | DSWPAG |       |       |       |       | 0001          |

| RCOUNT    | 0036  |        |        |        |            |            |        |       | RCOUN   | ΝT    |       |       |        |       |       |       |       | 0000          |

| DCOUNT    | 0038  |        |        |        |            |            |        |       | DCOUN   | NT    |       |       |        |       |       |       |       | 0000          |

| DOSTARTL  | 003A  |        |        |        |            |            |        | D     | OSTARTL |       |       |       |        |       |       |       | —     | 0000          |

| DOSTARTH  | 003C  | —      | _      | —      | —          | —          | —      | —     | —       | —     | —     |       |        | DOST  | ARTH  |       |       | 0000          |

| DOENDL    | 003E  |        |        |        |            |            |        |       | DOENDL  |       |       | •     |        |       |       |       | —     | 0000          |

| DOENDH    | 0040  | _      | _      | _      | _          | _          | _      | _     | _       | _     | _     |       |        | DOE   | NDH   |       |       | 0000          |

#### TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXX(GP/MC/MU)806/810/814 DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4   | 4-9:  | TIME   | R1 THR | ROUGH  | TIMER9 | REGIS  | TER MA | Р           |              |               |               |       |        |       |       |       |       |               |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------------|--------------|---------------|---------------|-------|--------|-------|-------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8        | Bit 7         | Bit 6         | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1      | 0100  |        |        |        |        |        |        |             | Timer1       | Register      |               |       |        |       |       |       |       | XXXX          |

| PR1       | 0102  |        |        |        |        |        |        |             | Period F     | Register 1    |               |       |        |       |       |       |       | FFFF          |

| T1CON     | 0104  | TON    | _      | TSIDL  | _      | _      | _      | —           | —            |               | TGATE         | TCKP  | S<1:0> | —     | TSYNC | TCS   |       | 0000          |

| TMR2      | 0106  |        |        |        |        |        |        |             | Timer2       | Register      |               |       |        |       |       |       | •     | XXXX          |

| TMR3HLD   | 0108  |        |        |        |        |        | Time   | r3 Holding  | Register (fo | r 32-bit time | er operations | only) |        |       |       |       |       | XXXX          |

| TMR3      | 010A  |        |        |        |        |        |        |             | Timer3       | Register      |               |       |        |       |       |       |       | XXXX          |

| PR2       | 010C  |        |        |        |        |        |        |             | Period F     | Register 2    |               |       |        |       |       |       |       | FFFF          |

| PR3       | 010E  |        |        |        |        |        |        |             | Period F     | Register 3    |               |       |        |       |       |       |       | FFFF          |

| T2CON     | 0110  | TON    | _      | TSIDL  | _      | _      | _      | _           | —            |               | TGATE         | TCKP  | S<1:0> | T32   | —     | TCS   |       | 0000          |

| T3CON     | 0112  | TON    | _      | TSIDL  | _      | _      | _      | _           |              |               | TGATE         | TCKP  | S<1:0> | _     | —     | TCS   |       | 0000          |

| TMR4      | 0114  |        | •      | •      | •      | •      | •      |             | Timer4       | Register      |               |       |        |       | •     | •     |       | XXXX          |

| TMR5HLD   | 0116  |        |        |        |        |        | Ti     | mer5 Holdir | ng Register  | (for 32-bit o | perations or  | ıly)  |        |       |       |       |       | XXXX          |

| TMR5      | 0118  |        |        |        |        |        |        |             | Timer5       | Register      |               |       |        |       |       |       |       | XXXX          |

| PR4       | 011A  |        |        |        |        |        |        |             | Period F     | Register 4    |               |       |        |       |       |       |       | FFFF          |

| PR5       | 011C  |        |        |        |        |        |        |             | Period F     | Register 5    |               |       |        |       |       |       |       | FFFF          |

| T4CON     | 011E  | TON    | —      | TSIDL  | —      | _      | _      | _           | _            |               | TGATE         | TCKP  | S<1:0> | T32   | —     | TCS   |       | 0000          |

| T5CON     | 0120  | TON    | _      | TSIDL  | _      | _      | _      | _           | _            | _             | TGATE         | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR6      | 0122  |        |        |        |        |        |        |             | Timer6       | Register      |               |       |        |       |       |       |       | XXXX          |

| TMR7HLD   | 0124  |        |        |        |        |        | Ti     | mer7 Holdir | ng Register  | (for 32-bit o | perations or  | ıly)  |        |       |       |       |       | XXXX          |

| TMR7      | 0126  |        |        |        |        |        |        |             | Timer7       | Register      |               |       |        |       |       |       |       | XXXX          |

| PR6       | 0128  |        |        |        |        |        |        |             | Period F     | Register 6    |               |       |        |       |       |       |       | FFFF          |

| PR7       | 012A  |        |        |        |        |        |        |             | Period F     | Register 7    |               |       |        |       |       |       |       | FFFF          |

| T6CON     | 012C  | TON    | —      | TSIDL  | _      | _      | _      | _           | _            |               | TGATE         | TCKP  | S<1:0> | T32   | —     | TCS   |       | 0000          |

| T7CON     | 012E  | TON    | —      | TSIDL  | _      | _      | _      | _           | _            |               | TGATE         | TCKP  | S<1:0> | —     | —     | TCS   | —     | 0000          |

| TMR8      | 0130  |        |        |        |        |        |        |             | Timer8       | Register      | •             |       |        |       |       |       |       | XXXX          |

| TMR9HLD   | 0132  |        |        |        |        |        | Ti     | mer9 Holdir | ng Register  | (for 32-bit o | perations or  | nly)  |        |       |       |       |       | XXXX          |

| TMR9      | 0134  |        |        |        |        |        |        |             | Timer9       | Register      |               |       |        |       |       |       |       | XXXX          |

| PR8       | 0136  |        |        |        |        |        |        |             | Period F     | Register 8    |               |       |        |       |       |       |       | FFFF          |

| PR9       | 0138  |        | -      |        |        | -      |        |             | Period F     | Register 9    |               |       |        |       |       |       |       | FFFF          |

| T8CON     | 013A  | TON    | _      | TSIDL  | —      |        |        | —           | —            |               | TGATE         | TCKP  | S<1:0> | T32   | —     | TCS   |       | 0000          |

| T9CON     | 013C  | TON    | _      | TSIDL  | _      | _      | _      | _           | _            |               | TGATE         | TCKP  | S<1:0> | —     | _     | TCS   | _     | 0000          |

dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>TABLE 4-21</b> : | QEI2 REGISTER MAP FOR dsPIC33EPXXX(MC/MU)806/810/814 DEVICES ONLY |

|---------------------|-------------------------------------------------------------------|

|---------------------|-------------------------------------------------------------------|

| File Name     | Addr. | Bit 15 | Bit 14          | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8      | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------|-------|--------|-----------------|----------|------------|------------|----------|----------|------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| QEI2CON       | 05C0  | QEIEN  | —               | QEISIDL  |            | PIMOD<2:0> |          | IMV<     | <1:0>      | —      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI2IOC       | 05C2  | QCAPEN | FLTREN          |          | QFDIV<2:0> |            | OUTFN    | VC<1:0>  | SWPAB      | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| QEI2STAT      | 05C4  | _      | —               | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN   | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS2CNTL      | 05C6  |        | POSCNT<15:0>    |          |            |            |          |          |            | 0000   |        |            |          |        |        |        |        |               |

| POS2CNTH      | 05C8  |        |                 |          |            |            |          |          | POSCNT<31: | 16>    |        |            |          |        |        |        |        | 0000          |

| POS2HLD       | 05CA  |        | POSHLD<15:0> 00 |          |            |            |          |          |            |        | 0000   |            |          |        |        |        |        |               |

| VEL2CNT       | 05CC  |        | VELCNT<15:0> 00 |          |            |            |          |          |            |        |        | 0000       |          |        |        |        |        |               |

| INT2TMRL      | 05CE  |        | INTTMR<15:0> 00 |          |            |            |          |          |            |        |        | 0000       |          |        |        |        |        |               |

| INT2TMRH      | 05D0  |        | INTTMR<31:16> 0 |          |            |            |          |          |            |        |        |            |          | 0000   |        |        |        |               |

| INT2HLDL      | 05D2  |        |                 |          |            |            |          |          | INTHLD<15  | 0>     |        |            |          |        |        |        |        | 0000          |

| INT2HLDH      | 05D4  |        |                 |          |            |            |          |          | INTHLD<31: | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX2CNTL     | 05D6  |        |                 |          |            |            |          |          | INDXCNT<15 | 5:0>   |        |            |          |        |        |        |        | 0000          |

| INDX2CNTH     | 05D8  |        |                 |          |            |            |          | I        | NDXCNT<31  | :16>   |        |            |          |        |        |        |        | 0000          |

| INDX2HLD      | 05DA  |        |                 |          |            |            |          |          | INDXHLD<15 | 5:0>   |        |            |          |        |        |        |        | 0000          |

| QEI2GECL      | 05DC  |        |                 |          |            |            |          |          | QEIGEC<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI2ICL       | 05DC  |        |                 |          |            |            |          |          | QEIIC<15:0 | )>     |        |            |          |        |        |        |        | 0000          |

| QEI2GECH      | 05DE  |        |                 |          |            |            |          |          | QEIGEC<31: | 16>    |        |            |          |        |        |        |        | 0000          |

| QEI2ICH       | 05DE  |        |                 |          |            |            |          |          | QEIIC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| QEI2LECL      | 05E0  |        |                 |          |            |            |          |          | QEILEC<15  | 0>     |        |            |          |        |        |        |        | 0000          |

| QEI2LECH      | 05E2  |        |                 |          |            |            |          |          | QEILEC<31: | 16>    |        |            |          |        |        |        |        | 0000          |

| a successful. |       |        |                 |          |            |            |          |          |            |        |        |            |          |        |        |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-41: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMU810 DEVICES ONLY (CONTINUED)

| File<br>Name | Addr.                | Bit 15 | Bit 14     | Bit 13       | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|----------------------|--------|------------|--------------|--------|-----------|--------|-------|--------------|--------------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR35      | 35 06E6 — IC14R<6:0> |        |            |              |        |           |        | —     | IC13R<6:0> 0 |              |              |       |       |            |       |       |       |               |

| RPINR36      | 06E8                 |        | IC16R<6:0> |              |        |           |        |       |              | _            | IC15R<6:0>   |       |       |            |       |       |       |               |

| RPINR37      | 06EA                 | _      |            | SYNCI1R<6:0> |        |           |        |       |              | _            |              |       | (     | OCFCR<6:0  | >     |       |       | 0000          |

| RPINR38      | 06EC                 |        |            |              | D      | TCMP1R<6: | 0>     |       |              | _            | SYNCI2R<6:0> |       |       |            |       |       |       | 0000          |

| RPINR39      | 06EE                 |        |            |              | D      | TCMP3R<6: | 0>     |       |              | _            | DTCMP2R<6:0> |       |       |            |       |       |       | 0000          |

| RPINR40      | 06F0                 |        |            |              | D      | TCMP5R<6: | 0>     |       |              | _            |              |       | D     | TCMP4R<6:  | 0>    |       |       | 0000          |

| RPINR41      | 06F2                 |        |            |              |        |           |        | _     | _            | DTCMP6R<6:0> |              |       |       |            | 0000  |       |       |               |

| RPINR42      | 06F4                 | _      | FLT6R<6:0> |              |        |           |        |       |              | _            | FLT5R<6:0>   |       |       |            |       | 0000  |       |               |

| RPINR43      | 06F6                 | _      |            | _            | —      | _         |        | _     | _            | _            |              |       |       | FLT7R<6:0> | •     |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0          | R/W-0                      | R/W-0                                                                       | R/W-0                | R/W-0            | R/W-0           | R/W-0           | R/W-0    |

|--------------|----------------------------|-----------------------------------------------------------------------------|----------------------|------------------|-----------------|-----------------|----------|

| —            |                            |                                                                             |                      | T5CKR<6:0>       | •               |                 |          |

| bit 15       |                            |                                                                             |                      |                  |                 |                 | bit 8    |

|              |                            |                                                                             |                      |                  |                 |                 |          |

| U-0          | R/W-0                      | R/W-0                                                                       | R/W-0                | R/W-0            | R/W-0           | R/W-0           | R/W-0    |

| —            |                            |                                                                             |                      | T4CKR<6:0>       | •               |                 |          |

| bit 7        |                            |                                                                             |                      |                  |                 |                 | bit 0    |

|              |                            |                                                                             |                      |                  |                 |                 |          |

| Legend:      |                            |                                                                             |                      |                  |                 |                 |          |

| R = Readat   | ole bit                    | W = Writable                                                                | bit                  | U = Unimpler     | mented bit, rea | ad as '0'       |          |

| -n = Value a | at POR                     | '1' = Bit is set                                                            |                      | '0' = Bit is cle | ared            | x = Bit is unkr | nown     |

|              | 0000001 =                  | Input tied to RP<br>Input tied to CM<br>Input tied to Vss                   | P1                   |                  |                 |                 |          |

| bit 7        | Unimpleme                  | nted: Read as '                                                             | 0'                   |                  |                 |                 |          |

| bit 6-0      | (see Table 1<br>11111111 = | : Assign Timer<br>1-2 for input pin<br>Input tied to RP<br>Input tied to CM | selection nun<br>127 |                  | he Correspond   | ding RPn/RPIn F | Pin bits |

#### REGISTER 11-5: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4

| U-0                          | R/W-0        | R/W-0                                                                | R/W-0         | R/W-0            | R/W-0           | R/W-0            | R/W-0  |

|------------------------------|--------------|----------------------------------------------------------------------|---------------|------------------|-----------------|------------------|--------|

| —                            |              |                                                                      |               | C2RXR<6:0>       | •               |                  |        |

| bit 15                       |              |                                                                      |               |                  |                 |                  | bit 8  |

| U-0                          | R/W-0        | R/W-0                                                                | R/W-0         | R/W-0            | R/W-0           | R/W-0            | R/W-0  |

|                              |              | 1000 0                                                               | 1000 0        | C1RXR<6:0>       |                 | 10000            | 1010 0 |

| bit 7                        |              |                                                                      |               |                  |                 |                  | bit C  |

| Logondi                      |              |                                                                      |               |                  |                 |                  |        |

| <b>Legend:</b><br>R = Readab | le bit       | W = Writable                                                         | bit           | U = Unimpler     | nented bit, rea | ad as '0'        |        |

| -n = Value a                 | t POR        | '1' = Bit is set                                                     |               | '0' = Bit is cle | ared            | x = Bit is unkr  | nown   |

|                              |              | Input tied to RP                                                     |               |                  |                 |                  |        |

|                              |              | Input tied to CM<br>Input tied to Vss                                |               |                  |                 |                  |        |

| bit 7                        | Unimpleme    | nted: Read as '                                                      | 0'            |                  |                 |                  |        |

| bit 6-0                      | (see Table 1 | >: Assign CAN1<br>1-2 for input pin<br>Input tied to RP <sup>-</sup> | selection nur |                  | responding R    | Pn/RPIn Pin bits | i      |

|                              |              | Input tied to CM<br>Input tied to Vss                                |               |                  |                 |                  |        |

#### REGISTER 11-26: RPINR26: PERIPHERAL PIN SELECT INPUT REGISTER 26

NOTES:

#### REGISTER 16-1: PTCON: PWM TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup>                                                                                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 111 = Reserved                                                                                                                                                                  |

|         | •                                                                                                                                                                               |

|         | •                                                                                                                                                                               |

|         | •                                                                                                                                                                               |

|         | 010 = Reserved<br>001 = SYNCI2<br>000 = SYNCI1                                                                                                                                  |

| bit 3-0 | SEVTPS<3:0>: PWM Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                             |

|         | 1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event                                                                                   |

|         | •                                                                                                                                                                               |

|         | •                                                                                                                                                                               |

|         | •                                                                                                                                                                               |

|         | 0001 = 1:2 Postscaler generates Special Event Trigger on every second compare match event<br>0000 = 1:1 Postscaler generates Special Event Trigger on every compare match event |

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

#### REGISTER 17-3: QEIxSTAT: QEIx STATUS REGISTER (CONTINUED)

| bit 2 | HOMIEN: Home Input Event Interrupt Enable bit                                                                  |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                   |

| bit 1 | IDXIRQ: Status Flag for Index Event Status bit                                                                 |

|       | <ul><li>1 = Index event has occurred</li><li>0 = No Index event has occurred</li></ul>                         |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled |

Note 1: This status bit is only applicable to PIMOD<2:0> modes '011' and '100'.

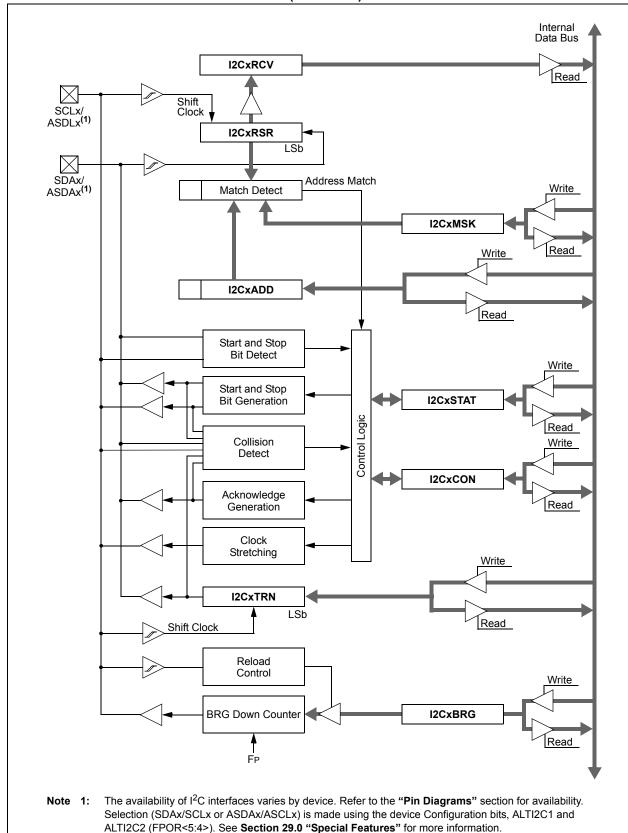

FIGURE 19-1:  $I^2 C^{TM}$  BLOCK DIAGRAM (x = 1 OR 2)

| R-0, HSC       | R-0, HSC                                                                                                                                                                  | U-0                                                                                                                                                | U-0                                                                                                                                                        | U-0                                                                                                                                     | R/C-0, HS                                                                                      | R-0, HSC                                                                                         | R-0, HSC            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------|

| ACKSTAT        | TRSTAT                                                                                                                                                                    |                                                                                                                                                    | _                                                                                                                                                          | —                                                                                                                                       | BCL                                                                                            | GCSTAT                                                                                           | ADD10               |

| oit 15         |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                            |                                                                                                                                         |                                                                                                |                                                                                                  | bit                 |

|                |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                            |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

| R/C-0, HS      | R/C-0, HS                                                                                                                                                                 | R-0, HSC                                                                                                                                           |                                                                                                                                                            | R/C-0, HSC                                                                                                                              | R-0, HSC                                                                                       | R-0, HSC                                                                                         | R-0, HSC<br>TBF     |

| IWCOL          | I2COV                                                                                                                                                                     | D_A                                                                                                                                                | Р                                                                                                                                                          | S                                                                                                                                       | R_W                                                                                            | RBF                                                                                              | bit                 |

|                |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                            |                                                                                                                                         |                                                                                                |                                                                                                  | <u> </u>            |

| Legend:        |                                                                                                                                                                           | C = Clearab                                                                                                                                        | le bit                                                                                                                                                     | U = Unimplen                                                                                                                            | nented bit, read                                                                               | as '0'                                                                                           |                     |

| R = Readable   | e bit                                                                                                                                                                     | W = Writabl                                                                                                                                        | e bit                                                                                                                                                      | HS = Hardwa                                                                                                                             | re Settable bit                                                                                | HSC = Hardware Se                                                                                | ettable/Clearable   |

| -n = Value at  | POR                                                                                                                                                                       | '1' = Bit is s                                                                                                                                     | et                                                                                                                                                         | '0' = Bit is clea                                                                                                                       | ared                                                                                           | x = Bit is unknown                                                                               |                     |

|                |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                            |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

| bit 15         |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                            | P 1.1. 1                                                                                                                                |                                                                                                |                                                                                                  |                     |

|                | (wnen opera<br>1 = NACK re                                                                                                                                                | -                                                                                                                                                  |                                                                                                                                                            | blicable to ma                                                                                                                          | ster transmit op                                                                               | eration)                                                                                         |                     |

|                | $\perp$ = NACK rec                                                                                                                                                        |                                                                                                                                                    |                                                                                                                                                            |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

|                |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                            | a slave Ackno                                                                                                                           | owledge.                                                                                       |                                                                                                  |                     |

| oit 14         |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                            |                                                                                                                                         | -                                                                                              | cable to master trar                                                                             | smit operation)     |

|                |                                                                                                                                                                           |                                                                                                                                                    | progress (8 l                                                                                                                                              |                                                                                                                                         |                                                                                                |                                                                                                  | . ,                 |

|                |                                                                                                                                                                           |                                                                                                                                                    | ot in progress                                                                                                                                             |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

|                | Hardware is<br>Acknowledg                                                                                                                                                 |                                                                                                                                                    | beginning of                                                                                                                                               | a master tra                                                                                                                            | nsmission. Har                                                                                 | dware is clear at t                                                                              | he end of a sla     |

| oit 13-11      | Unimpleme                                                                                                                                                                 | nted: Read                                                                                                                                         | <b>as</b> '0'                                                                                                                                              |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

| pit 10         | BCL: Maste                                                                                                                                                                | r Bus Collisi                                                                                                                                      | on Detect bit                                                                                                                                              |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

|                |                                                                                                                                                                           |                                                                                                                                                    | een detecteo                                                                                                                                               | during a mas                                                                                                                            | ter operation                                                                                  |                                                                                                  |                     |

|                | 0 = No collis                                                                                                                                                             |                                                                                                                                                    | the states in the second                                                                                                                                   |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

| -: · ·         |                                                                                                                                                                           |                                                                                                                                                    | tion of a bus                                                                                                                                              | collision.                                                                                                                              |                                                                                                |                                                                                                  |                     |

| oit 9          | GCSTAT: Ge                                                                                                                                                                |                                                                                                                                                    | was receive                                                                                                                                                | d                                                                                                                                       |                                                                                                |                                                                                                  |                     |

|                |                                                                                                                                                                           |                                                                                                                                                    | was receive                                                                                                                                                |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

|                |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                            |                                                                                                                                         | ral call address                                                                               | . Hardware is clear                                                                              | at a Stop detectio  |

| oit 8          | ADD10: 10-                                                                                                                                                                | Bit Address                                                                                                                                        | Status bit                                                                                                                                                 | -                                                                                                                                       |                                                                                                |                                                                                                  |                     |

|                | 1 = 10-bit ac                                                                                                                                                             | ldress was r                                                                                                                                       | natched                                                                                                                                                    |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

|                | 0 = 10-bit ac                                                                                                                                                             |                                                                                                                                                    |                                                                                                                                                            |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

|                |                                                                                                                                                                           |                                                                                                                                                    |                                                                                                                                                            | yte of a matche                                                                                                                         | ed 10-bit addres                                                                               | s. Hardware is clear                                                                             | at a Stop detection |

| oit 7          | IWCOL: Wri                                                                                                                                                                | te Collision I                                                                                                                                     | Detect bit                                                                                                                                                 |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

|                | $1 - \Lambda n$ off on                                                                                                                                                    |                                                                                                                                                    |                                                                                                                                                            |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

|                |                                                                                                                                                                           |                                                                                                                                                    | o the I2CxTR                                                                                                                                               | N register fail                                                                                                                         | ed because the                                                                                 | I <sup>2</sup> C module is bus                                                                   | y                   |

|                | 0 = No collis                                                                                                                                                             | ion                                                                                                                                                |                                                                                                                                                            |                                                                                                                                         |                                                                                                |                                                                                                  |                     |

| bit 6          | 0 = No collis<br>Hardware is                                                                                                                                              | ion<br>set at an oc                                                                                                                                | currence of a                                                                                                                                              | a write to I2Cx                                                                                                                         |                                                                                                | I <sup>2</sup> C module is busy                                                                  |                     |

| bit 6          | 0 = No collis<br>Hardware is<br>I2COV: I2C>                                                                                                                               | ion<br>set at an oc<br>Receive Ov                                                                                                                  | currence of a<br>verflow Flag I                                                                                                                            | a write to I2Cx<br>pit                                                                                                                  | TRN while busy                                                                                 | / (cleared by softwa                                                                             |                     |

| pit 6          | 0 = No collis<br>Hardware is<br>I2COV: I2C>                                                                                                                               | ion<br>set at an oc<br>Receive Ov<br>vas received                                                                                                  | currence of a<br>verflow Flag I                                                                                                                            | a write to I2Cx<br>pit                                                                                                                  | TRN while busy                                                                                 |                                                                                                  |                     |

| bit 6          | <ul> <li>0 = No collis</li> <li>Hardware is</li> <li>I2COV: I2C&gt;</li> <li>1 = A byte w</li> <li>0 = No overfl</li> </ul>                                               | ion<br>set at an oc<br>Receive Ov<br>vas received<br>flow                                                                                          | currence of a<br>verflow Flag I<br>while the I20                                                                                                           | a write to I2Cx<br>bit<br>CxRCV registe                                                                                                 | TRN while busy                                                                                 | / (cleared by softwa                                                                             | are).               |

|                | 0 = No collis<br>Hardware is<br>I2COV: I2C><br>1 = A byte w<br>0 = No overf<br>Hardware is                                                                                | ion<br>set at an oc<br>Receive Ov<br>vas received<br>flow<br>set at an att                                                                         | currence of a<br>verflow Flag I<br>while the I2C<br>empt to trans                                                                                          | a write to I2Cx<br>bit<br>CxRCV registe                                                                                                 | TRN while busy<br>r is still holding<br>to I2CxRCV (cl                                         | (cleared by softwatter<br>the previous byte                                                      | are).               |

| bit 6<br>bit 5 | 0 = No collis<br>Hardware is<br>I2COV: I2C><br>1 = A byte w<br>0 = No overf<br>Hardware is<br>D_A: Data/A                                                                 | ion<br>set at an oc<br>Receive Ov<br>vas received<br>flow<br>set at an att<br>vddress bit (v                                                       | currence of a<br>verflow Flag I<br>while the I2C<br>empt to trans                                                                                          | a write to I2Cx<br>bit<br>CxRCV registe<br>sfer I2CxRSR<br>ng as I <sup>2</sup> C slav                                                  | TRN while busy<br>r is still holding<br>to I2CxRCV (cl                                         | (cleared by softwatter<br>the previous byte                                                      | are).               |

|                | 0 = No collis<br>Hardware is<br>I2COV: I2C><br>1 = A byte w<br>0 = No overt<br>Hardware is<br>D_A: Data/A<br>1 = Indicates<br>0 = Indicates                               | ion<br>set at an oc<br>(Receive Ov<br>/as received<br>flow<br>set at an att<br>oddress bit (v<br>s that the lass<br>s that the lass                | currence of a<br>verflow Flag I<br>while the I2C<br>empt to trans<br>when operation<br>t byte received<br>t byte received                                  | a write to I2Cx<br>bit<br>CxRCV registe<br>sfer I2CxRSR<br>ng as I <sup>2</sup> C slav<br>ed was data<br>ed was a devi                  | TRN while busy<br>r is still holding<br>to I2CxRCV (cl<br>e)<br>ce address                     | <ul> <li>(cleared by software)</li> <li>the previous byte</li> <li>eared by software)</li> </ul> | are).               |

| bit 5          | 0 = No collis<br>Hardware is<br>I2COV: I2C><br>1 = A byte w<br>0 = No over<br>Hardware is<br>D_A: Data/A<br>1 = Indicates<br>0 = Indicates<br>Hardware is                 | ion<br>set at an oc<br>(Receive Ov<br>/as received<br>flow<br>set at an att<br>oddress bit (v<br>s that the lass<br>s that the lass                | currence of a<br>verflow Flag I<br>while the I2C<br>empt to trans<br>when operation<br>t byte received<br>t byte received                                  | a write to I2Cx<br>bit<br>CxRCV registe<br>sfer I2CxRSR<br>ng as I <sup>2</sup> C slav<br>ed was data<br>ed was a devi                  | TRN while busy<br>r is still holding<br>to I2CxRCV (cl<br>e)<br>ce address                     | (cleared by softwatter<br>the previous byte                                                      | are).               |

| bit 5          | 0 = No collis<br>Hardware is<br>I2COV: I2C><br>1 = A byte w<br>0 = No overf<br>Hardware is<br>D_A: Data/A<br>1 = Indicates<br>0 = Indicates<br>Hardware is<br>P: Stop bit | ion<br>set at an oc<br>(Receive Ov<br>vas received<br>flow<br>set at an att<br>oddress bit (v<br>s that the las<br>s that the las<br>clear at a de | currence of a<br>verflow Flag I<br>while the I2C<br>empt to trans<br>when operation<br>to byte receive<br>to byte receive<br>evice address                 | a write to I2Cx<br>bit<br>CxRCV registe<br>sfer I2CxRSR<br>ng as I <sup>2</sup> C slav<br>ed was data<br>ed was a devi<br>s match. Hard | TRN while busy<br>r is still holding<br>to I2CxRCV (cl<br>e)<br>ce address<br>ware is set by r | <ul> <li>(cleared by software)</li> <li>the previous byte</li> <li>eared by software)</li> </ul> | are).               |

|                | 0 = No collis<br>Hardware is<br>I2COV: I2C><br>1 = A byte w<br>0 = No overf<br>Hardware is<br>D_A: Data/A<br>1 = Indicates<br>0 = Indicates<br>Hardware is<br>P: Stop bit | ion<br>set at an oc<br>(Receive Ov<br>vas received<br>flow<br>set at an att<br>oddress bit (v<br>s that the las<br>clear at a de<br>s that a Stop  | currence of a<br>verflow Flag I<br>while the I2C<br>empt to trans<br>when operation<br>to byte receive<br>to byte receive<br>evice address<br>bit has been | a write to I2Cx<br>bit<br>CxRCV registe<br>sfer I2CxRSR<br>ng as I <sup>2</sup> C slav<br>ed was data<br>ed was a devi                  | TRN while busy<br>r is still holding<br>to I2CxRCV (cl<br>e)<br>ce address<br>ware is set by r | <ul> <li>(cleared by software)</li> <li>the previous byte</li> <li>eared by software)</li> </ul> | are).               |

#### REGISTER 22-14: UxIR: USB INTERRUPT STATUS REGISTER (DEVICE MODE ONLY)

| U-0       | U-0 | U-0       | U-0       | U-0       | U-0       | U-0    | U-0       |

|-----------|-----|-----------|-----------|-----------|-----------|--------|-----------|

| _         | _   | —         | —         | —         | —         | —      | —         |

| bit 15    |     |           |           |           |           |        | bit 8     |

|           |     |           |           |           |           |        |           |

| R/K-0, HS | U-0 | R/K-0, HS | R/K-0, HS | R/K-0, HS | R/K-0, HS | R-0    | R/K-0, HS |

| STALLIF   | _   | RESUMEIF  | IDLEIF    | TRNIF     | SOFIF     | UERRIF | URSTIF    |

| bit 7     |     |           |           |           |           |        | bit 0     |

| Legend:           | U = Unimplemented bit, read as '0'                    |                      |                    |  |  |  |

|-------------------|-------------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | K = Write '1' to clear bit HS = Hardware Settable bit |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                      | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                              |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | STALLIF: STALL Handshake Interrupt bit                                                                                                                                                                                                                                                  |

|          | 1 = A STALL handshake was sent by the peripheral during the handshake phase of the transaction in Device mode                                                                                                                                                                           |

|          | 0 = A STALL handshake has not been sent                                                                                                                                                                                                                                                 |

| bit 6    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                              |

| bit 5    | RESUMEIF: Resume Interrupt bit                                                                                                                                                                                                                                                          |

|          | <ul> <li>1 = A K-State is observed on the D+ or D- pin for 2.5 μs (differential '1' for low speed, differential '0' for full speed)</li> <li>0 = No K-State is observed</li> </ul>                                                                                                      |

| L:1 4    |                                                                                                                                                                                                                                                                                         |