Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 83                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 12K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gu810-e-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

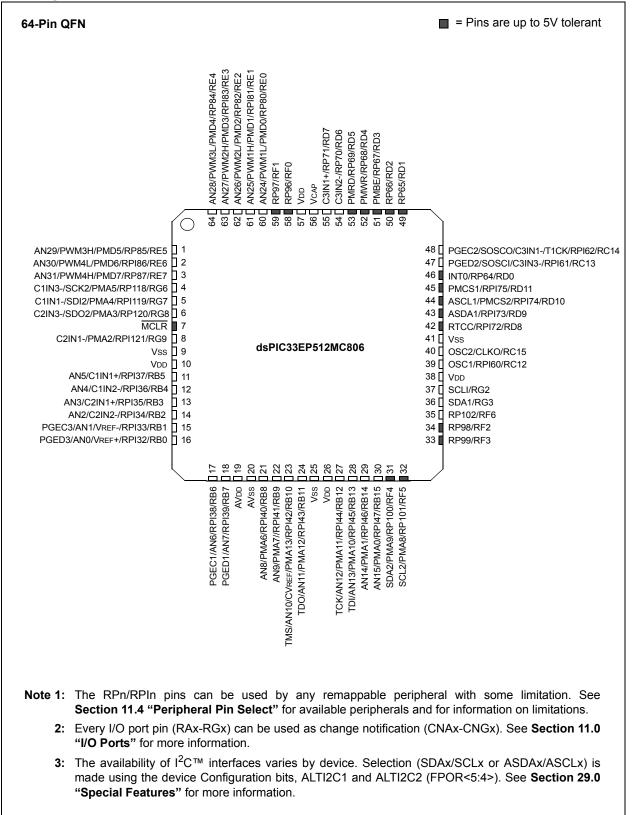

#### **Pin Diagrams**

DS70616G-page 4

# Pin Diagrams (Continued)

| 121-     | Pin TFBG | 6A <sup>(1)</sup> |           |           | do DIC(   | 33EP256  | MI 1940   |              | ) = Pins a | are up to | 5V tolera    |

|----------|----------|-------------------|-----------|-----------|-----------|----------|-----------|--------------|------------|-----------|--------------|

|          |          |                   |           |           |           | 33EP250  |           |              |            |           |              |

|          | 1        | 2                 | 3         | 4         | 5         | 6        | 7         | 8            | 9          | 10        | 11           |

| <b>A</b> | O<br>RE4 | O<br>RE3          | RG13      | O<br>RE0  | RG0       | RF1      |           | NC           | RD12       | RD2       | RD1          |

| 3        | NC       | RG15              | O<br>RE2  | O<br>RE1  | O<br>RA7  | RF0      | O<br>VCAP | RD5          | RD3        | ⊖<br>Vss  | O<br>RC14    |

| c        | O<br>RE6 |                   | RG12      | RG14      | O<br>RA6  | NC       | O<br>RD7  | RD4          | NC         | O<br>RC13 | <b>R</b> D11 |

| D        | O<br>RC1 | O<br>RE7          | O<br>RE5  | NC        | NC        | NC       | O<br>RD6  | RD13         | RD0        | NC        | RD10         |

| E        | O<br>RC4 | C<br>RC3          | O<br>RG6  | O<br>RC2  | NC        | RG1      | NC        | RA15         | RD8        | RD9       | RA14         |

| F        | MCLR     | O<br>RG8          | O<br>RG9  | O<br>RG7  | ⊖<br>Vss  | NC       | NC        |              | O<br>RC12  | ⊖<br>Vss  | O<br>RC15    |

| 3        | C<br>RE8 | O<br>RE9          | RA0       | NC        | O<br>Vdd  | ⊖<br>Vss | ⊖<br>Vss  | NC           | RA5        | RA3       | RA4          |

| н        | O<br>RB5 | O<br>RB4          | NC        | NC        | NC        | O<br>Vdd | NC        | <b>V</b> BUS | UUSB3V3    | O<br>RG2  | RA2          |

| J        | O<br>RB3 | O<br>RB2          | O<br>RB7  | O<br>AVDD | O<br>RB11 | RA1      | O<br>RB12 | NC           | NC         | RF8       | O<br>RG3     |

| ĸ        | O<br>RB1 | O<br>RB0          | O<br>RA10 | C<br>RB8  | NC        | RF12     | O<br>RB14 | O<br>VDD     | RD15       | RF3       | RF2          |

| -        | C<br>RB6 | O<br>RA9          | )<br>AVss | O<br>RB9  | O<br>RB10 | RF13     | O<br>RB13 | O<br>RB15    | RD14       | RF4       | RF5          |

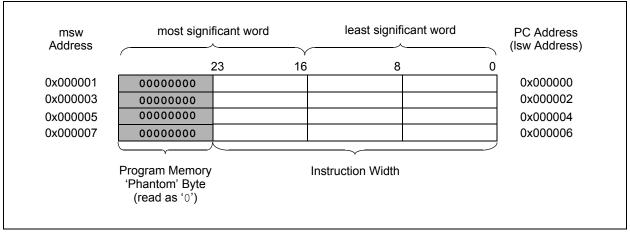

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address 0x000000 of the primary Flash memory or at address 0x7FFFFC of the auxiliary Flash memory, with the actual address for the start of code at address 0x000002 of the primary Flash memory or at address 0x7FFFFE of the auxiliary Flash memory. Reset Target Vector Select bit (RSTPRI) in the FPOR Configuration register controls whether primary or auxiliary Flash Reset location is used.

A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11     | Bit 10 | Bit 9  | Bit 8       | Bit 7        | Bit 6       | Bit 5  | Bit 4  | Bit 3    | Bit 2     | Bit 1    | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|----------|--------|------------|--------|--------|-------------|--------------|-------------|--------|--------|----------|-----------|----------|-------|---------------|

| DC1CON1   | 0900  | _      | —      | OCSIDL   | C      | OCTSEL<2:0 | )>     | ENFLTC | ENFLTB      | ENFLTA       | OCFLTC      | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC1CON2   | 0902  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  |            | _      | —      | OC32        | OCTRIG       | TRIGSTAT    | OCTRIS |        | SY       | NCSEL<4:( | )>       |       | 0000          |

| OC1RS     | 0904  |        |        |          |        |            |        | Outp   | out Compare | e 1 Seconda  | ry Register |        |        |          |           |          |       | XXXX          |

| OC1R      | 0906  |        |        |          |        |            |        |        | Output Co   | mpare 1 Reg  | gister      |        |        |          |           |          |       | XXXX          |

| OC1TMR    | 0908  |        |        |          |        |            |        |        | Timer Va    | alue 1 Regis | ter         |        |        |          |           |          |       | XXXX          |

| OC2CON1   | 090A  | _      | —      | OCSIDL   | C      | CTSEL<2:0  | )>     | ENFLTC | ENFLTB      | ENFLTA       | OCFLTC      | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC2CON2   | 090C  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _          | —      | —      | OC32        | OCTRIG       | TRIGSTAT    | OCTRIS |        | SY       | NCSEL<4:0 | )>       |       | 0000          |

| OC2RS     | 090E  |        |        |          |        |            |        | Out    | out Compare | e 2 Seconda  | ry Register |        |        |          |           |          |       | XXXX          |

| OC2R      | 0910  |        |        |          |        |            |        |        | Output Co   | mpare 2 Reg  | gister      |        |        |          |           |          |       | XXXX          |

| OC2TMR    | 0912  |        |        |          |        |            |        |        | Timer Va    | alue 2 Regis | ter         |        |        |          |           |          |       | XXXX          |

| OC3CON1   | 0914  | _      | —      | OCSIDL   | C      | CTSEL<2:0  | )>     | ENFLTC | ENFLTB      | ENFLTA       | OCFLTC      | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC3CON2   | 0916  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _          | —      | —      | OC32        | OCTRIG       | TRIGSTAT    | OCTRIS |        | SY       | NCSEL<4:0 | )>       |       | 0000          |

| OC3RS     | 0918  |        |        |          |        |            |        | Out    | out Compare | e 3 Seconda  | ry Register |        |        |          |           |          |       | XXXX          |

| OC3R      | 091A  |        |        |          |        |            |        |        | Output Co   | mpare 3 Reg  | gister      |        |        |          |           |          |       | XXXX          |

| OC3TMR    | 091C  |        |        |          |        |            |        |        | Timer Va    | alue 3 Regis | ter         |        |        |          |           |          |       | XXXX          |

| OC4CON1   | 091E  | —      | _      | OCSIDL   | C      | CTSEL<2:0  | )>     | ENFLTC | ENFLTB      | ENFLTA       | OCFLTC      | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC4CON2   | 0920  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  |            | —      | —      | OC32        | OCTRIG       | TRIGSTAT    | OCTRIS |        | SY       | NCSEL<4:0 | )>       |       | 0000          |

| OC4RS     | 0922  |        |        |          |        |            |        | Outp   | out Compare | e 4 Seconda  | ry Register |        |        |          |           |          |       | XXXX          |

| OC4R      | 0924  |        |        |          |        |            |        |        | Output Co   | mpare 4 Reg  | gister      |        |        |          |           |          |       | XXXX          |

| OC4TMR    | 0926  |        |        |          |        |            |        |        | Timer Va    | alue 4 Regis | ter         |        |        |          |           |          |       | XXXX          |

| OC5CON1   | 0928  | —      | _      | OCSIDL   | C      | CTSEL<2:0  | )>     | ENFLTC | ENFLTB      | ENFLTA       | OCFLTC      | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC5CON2   | 092A  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _          | _      | _      | OC32        | OCTRIG       | TRIGSTAT    | OCTRIS |        | SY       | NCSEL<4:0 | )>       |       | 0000          |

| OC5RS     | 092C  |        |        |          |        |            |        | Outp   | out Compare | e 5 Seconda  | ry Register |        |        |          |           |          |       | XXXX          |

| OC5R      | 092D  |        |        |          |        |            |        |        | Output Co   | mpare 5 Re   | gister      |        |        |          |           |          |       | XXXX          |

| OC5TMR    | 0930  |        |        |          |        |            |        |        | Timer Va    | alue 5 Regis | ter         |        |        |          |           |          |       | XXXX          |

| OC6CON1   | 0932  | _      | _      | OCSIDL   | C      | OCTSEL<2:0 | )>     | ENFLTC | ENFLTB      | ENFLTA       | OCFLTC      | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC6CON2   | 0934  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | _          | _      | _      | OC32        | OCTRIG       | TRIGSTAT    | OCTRIS |        | SY       | NCSEL<4:0 | )>       |       | 0000          |

| OC6RS     | 0936  |        |        |          |        |            |        | Out    | out Compare | e 6 Seconda  | ry Register |        |        |          |           |          |       | XXXX          |

| OC6R      | 0938  |        |        |          |        |            |        |        | Output Co   | mpare 6 Re   | gister      |        |        |          |           |          |       | XXXX          |

| OC6TMR    | 093A  |        |        |          |        |            |        |        | Timer Va    | alue 6 Regis | ter         |        |        |          |           |          |       | XXXX          |

| OC7CON1   | 093C  | _      |        | OCSIDL   | C      | CTSEL<2:0  | )>     | ENFLTC | ENFLTB      | ENFLTA       | OCFLTC      | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC7CON2   | 093E  | FLTMD  | FLTOUT | FLTTRIEN | OCINV  | —          |        | —      | OC32        | OCTRIG       | TRIGSTAT    | OCTRIS |        | SY       | NCSEL<4:0 | )>       |       | 0000          |

| OC7RS     | 0940  |        |        |          |        |            |        | Out    | out Compare | e 7 Seconda  | ry Register |        |        |          |           |          |       | XXXX          |

| OC7R      | 0942  |        |        |          |        |            |        |        |             | mpare 7 Reg  |             |        |        |          |           |          |       | XXXX          |

| OC7TMR    | 0944  |        |        |          |        |            |        |        | Timer Va    | alue 7 Regis | ter         |        |        |          |           |          |       | xxxx          |

dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

#### TABLE 4-11: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 16 REGISTER MAP

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-41: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMU810 DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------------|--------|------------|--------|-------|-------|-------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR35      | 06E6  | _      |        |              |        | IC14R<6:0> | •      |       |       | —     |              |       |       | IC13R<6:0> |       |       |       | 0000          |

| RPINR36      | 06E8  |        |        |              |        | IC16R<6:0> | •      |       |       | _     | IC15R<6:0>   |       |       |            |       |       |       | 0000          |

| RPINR37      | 06EA  | _      |        | SYNCI1R<6:0> |        |            |        |       |       | _     |              |       | (     | OCFCR<6:0  | >     |       |       | 0000          |

| RPINR38      | 06EC  |        |        | DTCMP1R<6:0> |        |            |        |       |       | _     |              |       | S     | YNCI2R<6:( | )>    |       |       | 0000          |

| RPINR39      | 06EE  |        |        |              | D      | TCMP3R<6:  | 0>     |       |       | _     |              |       | D     | TCMP2R<6:  | 0>    |       |       | 0000          |

| RPINR40      | 06F0  |        |        |              | D      | TCMP5R<6:  | 0>     |       |       | _     | DTCMP4R<6:0> |       |       |            |       |       | 0000  |               |

| RPINR41      | 06F2  |        | _      |              |        |            |        |       |       | _     |              |       | D     | TCMP6R<6:  | 0>    |       |       | 0000          |

| RPINR42      | 06F4  | _      |        |              |        | FLT6R<6:0> | >      |       |       | _     |              |       |       | FLT5R<6:0> | •     |       |       | 0000          |

| RPINR43      | 06F6  | _      |        | _            | _      | _          |        | _     | _     | _     |              |       |       | FLT7R<6:0> | •     |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|------------|----------|-------|-------|---------------|

| RPINR0       | 06A0  | _      |        |        |        | INT1R<6:03 | >      |       |       | —     | _     | —     | —     | —          |          | —     | —     | 0000          |

| RPINR1       | 06A2  | —      |        |        |        | INT3R<6:0  | >      | _     | _     | —     |       |       |       | INT2R<6:0> | <b>`</b> |       |       | 0000          |

| RPINR2       | 06A4  | —      | —      | —      | —      | _          | _      | _     | _     | —     |       |       |       | INT4R<6:0> | <b>`</b> |       |       | 0000          |

| RPINR3       | 06A6  | —      |        |        |        | T3CKR<6:0  | >      |       |       | —     |       |       |       | T2CKR<6:0  | >        |       |       | 0000          |

| RPINR4       | 06A8  | —      |        |        |        | T5CKR<6:0  | >      |       |       |       |       |       |       | T4CKR<6:0  | >        |       |       | 0000          |

| RPINR5       | 06AA  | _      |        |        |        | T7CKR<6:0  | >      |       |       | —     |       |       |       | T6CKR<6:0  | >        |       |       | 0000          |

| RPINR6       | 06AC  | —      |        |        |        | T9CKR<6:0  | >      |       |       | —     |       |       |       | T8CKR<6:0  | >        |       |       | 0000          |

| RPINR7       | 06AE  | —      |        |        |        | IC2R<6:0>  |        |       |       | —     |       |       |       | IC1R<6:0>  |          |       |       | 0000          |

| RPINR8       | 06B0  | —      |        |        |        | IC4R<6:0>  |        |       |       | —     |       |       |       | IC3R<6:0>  |          |       |       | 0000          |

| RPINR9       | 06B2  | —      |        |        |        | IC6R<6:0>  |        |       |       | —     |       |       |       | IC5R<6:0>  |          |       |       | 0000          |

| RPINR10      | 06B4  | —      |        |        |        | IC8R<6:0>  |        |       |       | —     |       |       |       | IC7R<6:0>  |          |       |       | 0000          |

| RPINR11      | 06B6  | —      |        |        |        | OCFBR<6:0  | >      |       |       | —     |       |       |       | OCFAR<6:0  | >        |       |       | 0000          |

| RPINR12      | 06B8  | —      |        |        |        | FLT2R<6:0  | >      |       |       | —     |       |       |       | FLT1R<6:0> | >        |       |       | 0000          |

| RPINR13      | 06BA  | _      |        |        |        | FLT4R<6:0  | >      |       |       | —     |       |       |       | FLT3R<6:0> | >        |       |       | 0000          |

| RPINR14      | 06BC  | _      |        |        |        | QEB1R<6:0  | >      |       |       | —     |       |       |       | QEA1R<6:0  | >        |       |       | 0000          |

| RPINR15      | 06BE  | _      |        |        | F      | IOME1R<6:  | 0>     |       |       | —     |       |       |       | NDX1R<6:0  | >        |       |       | 0000          |

| RPINR16      | 06C0  | —      |        |        |        | QEB2R<6:0  | >      |       |       | —     |       |       |       | QEA2R<6:0  | >        |       |       | 0000          |

| RPINR17      | 06C2  | —      |        |        | F      | IOME2R<6:  | 0>     |       |       | —     |       |       |       | NDX2R<6:0  | >        |       |       | 0000          |

| RPINR18      | 06C4  | —      |        |        | ι      | J1CTSR<6:( | )>     |       |       | —     |       |       |       | U1RXR<6:0  | >        |       |       | 0000          |

| RPINR19      | 06C6  | —      |        |        | ι      | J2CTSR<6:( | )>     |       |       | —     |       |       |       | U2RXR<6:0  | >        |       |       | 0000          |

| RPINR20      | 06C8  | —      |        | -      |        | SCK1R<6:0  | >      | -     |       | —     |       |       |       | SDI1R<6:0> | >        |       |       | 0000          |

| RPINR21      | 06CA  | —      | —      | —      | _      | —          | —      | —     | _     | —     |       |       |       | SS1R<6:0>  |          |       |       | 0000          |

| RPINR23      | 06CE  | —      | —      | _      | —      | —          | _      | —     | _     | —     |       |       |       | SS2R<6:0>  |          |       |       | 0000          |

| RPINR24      | 06D0  | —      |        |        |        | CSCKR<6:0  | >      |       |       |       |       |       |       | CSDIR<6:0> | >        |       |       | 0000          |

| RPINR25      | 06D2  | —      |        | —      | _      | —          | —      | —     | -     |       |       |       | C     | OFSINR<6:  | 0>       |       |       | 0000          |

| RPINR26      | 06D4  | —      |        |        |        | C2RXR<6:0  | >      |       |       | —     |       |       |       | C1RXR<6:0  | >        |       |       | 0000          |

| RPINR27      | 06D6  | —      |        |        | ι      | J3CTSR<6:( | )>     |       |       | —     |       |       |       | U3RXR<6:0  | >        |       |       | 0000          |

| RPINR28      | 06D8  | —      |        |        | ι      | J4CTSR<6:( | )>     |       |       | —     |       |       |       | U4RXR<6:0  | >        |       |       | 0000          |

| RPINR29      | 06DA  | —      |        |        |        | SCK3R<6:0  | >      |       |       | —     |       |       |       | SDI3R<6:0> | >        |       |       | 0000          |

| RPINR30      | 06DC  | —      | —      | —      | —      | —          | —      | —     | —     | —     |       |       |       | SS3R<6:0>  |          |       |       | 0000          |

| RPINR31      | 06DE  | _      |        |        |        | SCK4R<6:0  | >      |       |       | _     |       |       |       | SDI4R<6:0> | >        |       |       | 0000          |

| RPINR32      | 06E0  | _      | _      | -      | —      | _          | _      | —     | _     | _     |       |       |       | SS4R<6:0>  |          |       |       | 0000          |

| RPINR33      | 06E2  | _      |        |        |        | IC10R<6:03 | >      |       |       | _     |       |       |       | IC9R<6:0>  |          |       |       | 0000          |

| RPINR34      | 06E4  | _      |        |        |        | IC12R<6:03 | >      |       |       | _     |       |       |       | IC11R<6:0> | •        |       |       | 0000          |

#### TABLE 4-42: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXX(MC/MU)806 DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

| U-0           | U-0        | U-0              | U-0             | U-0              | U-0              | U-0            | R/W-0     |

|---------------|------------|------------------|-----------------|------------------|------------------|----------------|-----------|

| _             | —          | —                | _               | —                | —                | -              | PLLDIV<8> |

| bit 15        |            |                  |                 |                  |                  |                | bit 8     |

|               |            |                  |                 |                  |                  |                |           |

| R/W-0         | R/W-0      | R/W-1            | R/W-1           | R/W-0            | R/W-0            | R/W-0          | R/W-0     |

|               |            |                  | PLLD            | IV<7:0>          |                  |                |           |

| bit 7         |            |                  |                 |                  |                  |                | bit 0     |

|               |            |                  |                 |                  |                  |                |           |

| Legend:       |            |                  |                 |                  |                  |                |           |

| R = Readab    | le bit     | W = Writable     | bit             | U = Unimpler     | mented bit, read | d as '0'       |           |

| -n = Value at | t POR      | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unl | nown      |

|               |            |                  |                 |                  |                  |                |           |

| bit 15-9      | Unimpleme  | nted: Read as '  | 0'              |                  |                  |                |           |

| bit 8-0       | PLLDIV<8:0 | >: PLL Feedbad   | ck Divisor bits | (also denoted    | as 'M', PLL mu   | ltiplier)      |           |

|               | 111111111  | = 513            |                 |                  |                  |                |           |

|               | •          |                  |                 |                  |                  |                |           |

|               | •          |                  |                 |                  |                  |                |           |

|               | •          |                  |                 |                  |                  |                |           |

|               | 000110000  | = 50 (default)   |                 |                  |                  |                |           |

|               | •          |                  |                 |                  |                  |                |           |

|               | •          |                  |                 |                  |                  |                |           |

|               | 000000010  | = 3              |                 |                  |                  |                |           |

|               | 000000000  | - 2              |                 |                  |                  |                |           |

# REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

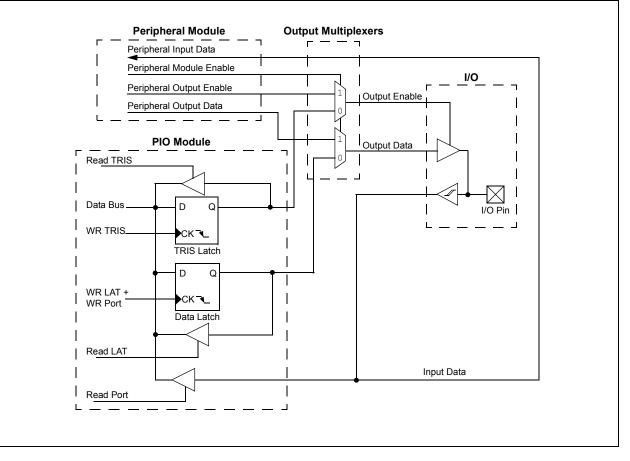

## 11.5 I/O Helpful Tips

- In some cases, certain pins, as defined in 1. Table 32-9 in Section 32.0 "Electrical Characteristics" under "Injection Current", have internal protection diodes to VDD and VSS; the term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin, (i.e., ANx, see Table 1-1 in Section 1.0 "Device Overview"), are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin, automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared analog pin (see Table 1-1 in Section 1.0 "Device Overview"), the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left to right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1; this indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin. Dedicated peripheral functions are always higher priority than remappable functions. I/O pins are always the lowest priority.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD-0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 32.0 "Electrical Characteristics"** for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input, provided there is no external analog input, such as for a built-in self test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including any pin with a single output from either a dedicated or remappable "output".

#### REGISTER 11-22: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0             | U-0             | U-0   |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| —               | —     | —                | —     | —                | —               | —               | —     |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| U-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| —               |       |                  |       | SS1R<6:0>        |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared           | x = Bit is unki | nown  |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 SS1R<6:0>: Assign SPI1 Slave Select Input (SS1) to the Corresponding RPn/RPIn Pin bits (see Table 11-2 for input pin selection numbers) 1111111 = Input tied to RP127

> . 0000001 = Input tied to CMP1 0000000 = Input tied to Vss

#### REGISTER 11-23: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|

| _               | _     | —                |       | _                | _                | _               | —     |

| bit 15          |       |                  |       |                  |                  |                 | bit 8 |

|                 |       |                  |       |                  |                  |                 |       |

| U-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| —               |       |                  |       | SS2R<6:0>        |                  |                 |       |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |

|                 |       |                  |       |                  |                  |                 |       |

| Legend:         |       |                  |       |                  |                  |                 |       |

| R = Readable    | bit   | W = Writable I   | oit   | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

bit 15-7 Unimplemented: Read as '0'

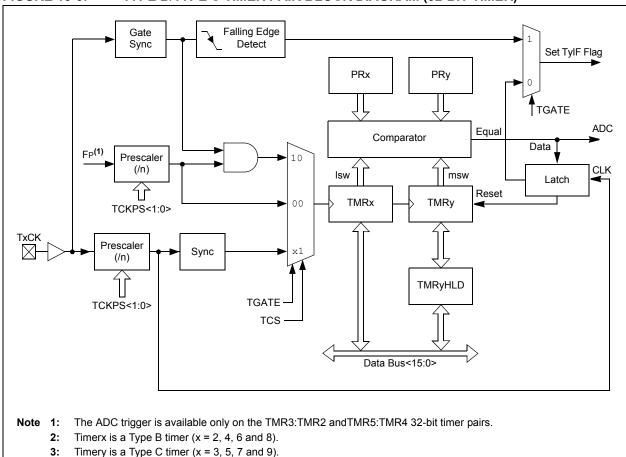

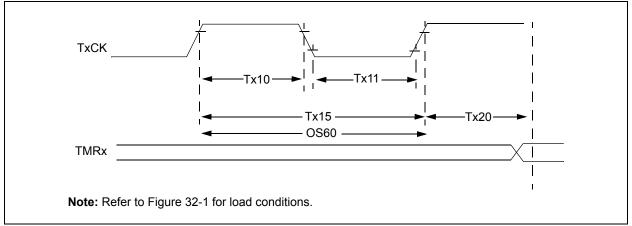

#### FIGURE 13-3: TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

#### 13.1 Timer Resources

Many useful resources related to timers are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en554310              |

#### 13.1.1 KEY RESOURCES

- Section 11. "Timers" (DS70362) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- · Development Tools

## 13.2 Timerx/y Control Registers

| R/W-0        | U-0                               | R/W-0            | U-0             | U-0               | U-0            | U-0                | U-0 |

|--------------|-----------------------------------|------------------|-----------------|-------------------|----------------|--------------------|-----|

| TON          |                                   | TSIDL            | _               |                   | —              | _                  | _   |

| pit 15       |                                   |                  |                 |                   |                |                    | bit |

| U-0          | R/W-0                             | R/W-0            | R/W-0           | R/W-0             | U-0            | R/W-0              | U-0 |

| 0-0          | TGATE                             | I                | S<1:0>          | T32               | 0-0            | TCS <sup>(1)</sup> | 0-0 |

| <br>bit 7    | IGAIE                             | ICKE             | 5~1.0~          | 132               | _              | 10307              |     |

|              |                                   |                  |                 |                   |                |                    | bit |

| Legend:      |                                   |                  |                 |                   |                |                    |     |

| R = Readable | e bit                             | W = Writable     | bit             | U = Unimplem      | ented bit, rea | d as '0'           |     |

| n = Value at | POR                               | '1' = Bit is set |                 | '0' = Bit is clea | ared           | x = Bit is unkno   | own |

| bit 15       | TON: Timerx                       | On hit           |                 |                   |                |                    |     |

| 511 15       | When T32 = $2$                    |                  |                 |                   |                |                    |     |

|              | 1 = Starts 32-                    |                  |                 |                   |                |                    |     |

|              | 0 = Stops 32-                     |                  |                 |                   |                |                    |     |

|              | <u>When T32 = 0</u>               |                  |                 |                   |                |                    |     |

|              | 1 = Starts 16-<br>0 = Stops 16-   |                  |                 |                   |                |                    |     |

| oit 14       | -                                 | ted: Read as '   | 0'              |                   |                |                    |     |

| bit 13       | TSIDL: Timer                      | x Stop in Idle I | Node bit        |                   |                |                    |     |

|              |                                   |                  |                 | device enters lo  | lle mode       |                    |     |

|              |                                   | s module opera   |                 | ode               |                |                    |     |

| bit 12-7     | -                                 | ted: Read as '   |                 |                   |                |                    |     |

| bit 6        |                                   | erx Gated Time   | Accumulatio     | n Enable bit      |                |                    |     |

|              | When TCS =<br>This bit is igno    |                  |                 |                   |                |                    |     |

|              | When TCS =                        |                  |                 |                   |                |                    |     |

|              | 1 = Gated tim                     | e accumulatio    |                 |                   |                |                    |     |

|              |                                   | e accumulatio    |                 |                   |                |                    |     |

| bit 5-4      |                                   | : Timerx Input   | Clock Presca    | le Select bits    |                |                    |     |

|              | 11 = 1:256<br>10 = 1:64           |                  |                 |                   |                |                    |     |

|              | 10 = 1:64<br>01 = 1:8             |                  |                 |                   |                |                    |     |

|              | 00 = 1:1                          |                  |                 |                   |                |                    |     |

| bit 3        | <b>T32:</b> 32-Bit Ti             | mer Mode Sel     | ect bit         |                   |                |                    |     |

|              | 1 = Timerx an                     | d Timery form    | a single 32-b   | it timer          |                |                    |     |

|              | 0 = Timerx ar                     | id Timery act a  | is two 16-bit t | mers              |                |                    |     |

| bit 2        | •                                 | ted: Read as '   |                 |                   |                |                    |     |

| bit 1        |                                   | Clock Source S   |                 |                   |                |                    |     |

|              | 1 = External o<br>0 = Internal cl | lock from TxC    | K pin (on the   | rising edge)      |                |                    |     |

|              |                                   |                  |                 |                   |                |                    |     |

# REGISTER 13-1: TxCON: (T2CON, T4CON, T6CON OR T8CON) CONTROL REGISTER

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

| R/W-0           | R/W-0                                                                                            | R/W-0                                                  | R/W-0                                                 | R/W-0             | R/W-0                               | R/W-0          | R/W-0 |

|-----------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|-------------------|-------------------------------------|----------------|-------|

| QCAPEN          | FLTREN                                                                                           |                                                        | QFDIV<2:0>                                            |                   | OUTFN                               | C<1:0>         | SWPAB |

| bit 15          |                                                                                                  |                                                        |                                                       |                   |                                     |                | bit 8 |

| R/W-0           | R/W-0                                                                                            | R/W-0                                                  | R/W-0                                                 | R-x               | R-x                                 | R-x            | R-x   |

| HOMPOL          | IDXPOL                                                                                           | QEBPOL                                                 | QEAPOL                                                | HOME              | INDEX                               | QEB            | QEA   |

| bit 7           |                                                                                                  |                                                        |                                                       | 1                 |                                     |                | bit ( |

| Legend:         |                                                                                                  |                                                        |                                                       |                   |                                     |                |       |

| R = Readable    |                                                                                                  | W = Writable                                           | e bit                                                 | U = Unimpler      | nented bit, read                    | l as '0'       |       |

| -n = Value at I | POR                                                                                              | '1' = Bit is se                                        | et                                                    | '0' = Bit is cle  | ared                                | x = Bit is unk | nown  |

| bit 15          |                                                                                                  |                                                        | er Input Capture                                      |                   |                                     |                |       |

|                 |                                                                                                  | •                                                      |                                                       |                   | capture functior<br>a capture event |                |       |

| bit 14          | FLTREN: QE                                                                                       | EAx/QEBx/IND                                           | Xx/HOMEx Dig                                          | jital Filter Enab | ole bit                             |                |       |

|                 |                                                                                                  | digital filter is digital filter is                    | enabled<br>disabled (bypa                             | ssed)             |                                     |                |       |

| bit 13-11       | QFDIV<2:0>                                                                                       | ·: QEAx/QEBx                                           | /INDXx/HOME>                                          | Digital Input F   | Filter Clock Divi                   | de Select bits |       |

|                 | 101 = 1:32 c<br>100 = 1:16 c<br>011 = 1:8 clc<br>010 = 1:4 clc<br>001 = 1:2 clc<br>000 = 1:1 clc | clock divide<br>ock divide<br>ock divide<br>ock divide |                                                       |                   |                                     |                |       |

| bit 10-9        | OUTFNC<1:                                                                                        | 0>: QEI Modu                                           | le Output Func                                        | tion Mode Sele    | ect bits                            |                |       |

|                 | 10 = The CT                                                                                      | NCMPx pin go<br>NCMPx pin go                           | bes high when (<br>bes high when l<br>bes high when l | $POSxCNT \le QI$  |                                     | GEC            |       |

| bit 8           | 1 = QEAx an                                                                                      | ap QEA and C<br>d QEBx are s<br>d QEBx are n           | wapped prior to                                       | quadrature de     | ecoder logic                        |                |       |

| bit 7           |                                                                                                  |                                                        | olarity Select b                                      | it                |                                     |                |       |

|                 | 1 = Input is in<br>0 = Input is r                                                                | nverted                                                | ,                                                     |                   |                                     |                |       |

| bit 6           | -                                                                                                |                                                        | larity Select bit                                     |                   |                                     |                |       |

|                 | 1 = Input is in<br>0 = Input is r                                                                |                                                        |                                                       |                   |                                     |                |       |

|                 |                                                                                                  |                                                        |                                                       |                   |                                     |                |       |

| bit 5           |                                                                                                  | EBx Input Pol                                          | arity Select bit                                      |                   |                                     |                |       |

| bit 5           | 1 = Input is<br>0 = Input is                                                                     | inverted                                               | arity Select bit                                      |                   |                                     |                |       |

| bit 5<br>bit 4  | 1 = Input is<br>0 = Input is                                                                     | inverted<br>not inverted                               | arity Select bit                                      |                   |                                     |                |       |

|                 | 1 = Input is<br>0 = Input is                                                                     | inverted<br>not inverted<br>EAx Input Pol<br>inverted  | -                                                     |                   |                                     |                |       |

# REGISTER 17-2: QEIxIOC: QEIx I/O CONTROL REGISTER

# 20.3 UARTx Registers

| R/W-0                 | U-0                          | R/W-0                                               | R/W-0                          | R/W-0                                    | U-0                                                                                | R/W-0             | R/W-0            |

|-----------------------|------------------------------|-----------------------------------------------------|--------------------------------|------------------------------------------|------------------------------------------------------------------------------------|-------------------|------------------|

| UARTEN <sup>(1)</sup> | —                            | USIDL                                               | IREN <sup>(2)</sup>            | RTSMD                                    | —                                                                                  | UEN               | <1:0>            |

| bit 15                |                              |                                                     |                                |                                          |                                                                                    |                   | bit 8            |

| R/W-0, HC             | R/W-0                        | R/W-0, HC                                           | R/W-0                          | R/W-0                                    | R/W-0                                                                              | R/W-0             | R/W-0            |

| WAKE                  | LPBACK                       | ABAUD                                               | URXINV                         | BRGH                                     | PDSEI                                                                              | -                 | STSEL            |

| bit 7                 | LFDACK                       | ABAUD                                               | URAINV                         | BRGH                                     | FDGEI                                                                              | _<1.0>            | bit (            |

|                       |                              |                                                     |                                |                                          |                                                                                    |                   |                  |

| Legend:               |                              | HC = Hardwa                                         | re Clearable b                 | bit                                      |                                                                                    |                   |                  |

| R = Readable          | bit                          | W = Writable                                        | bit                            | U = Unimpler                             | mented bit, read                                                                   | l as '0'          |                  |

| -n = Value at F       | POR                          | '1' = Bit is set                                    |                                | '0' = Bit is cle                         | ared                                                                               | x = Bit is unkr   | nown             |

| bit 15                | UARTEN: UA                   | RTx Enable bi                                       | t(1)                           |                                          |                                                                                    |                   |                  |

|                       |                              |                                                     |                                |                                          | y UARTx as defin<br>y port latches; L                                              |                   |                  |

| bit 14                | Unimplemen                   | ted: Read as '                                      | 0'                             |                                          |                                                                                    |                   |                  |

| bit 13                | USIDL: UART                  | Tx Stop in Idle                                     | Mode bit                       |                                          |                                                                                    |                   |                  |

|                       |                              | ues module op<br>s module oper                      |                                |                                          | Idle mode                                                                          |                   |                  |

| bit 12                | IREN: IrDA <sup>®</sup> I    | Encoder and D                                       | ecoder Enable                  | e bit <sup>(2)</sup>                     |                                                                                    |                   |                  |

|                       |                              | oder and deco                                       |                                |                                          |                                                                                    |                   |                  |

| bit 11                | RTSMD: Mod                   | le Selection for                                    | UxRTS Pin b                    | it                                       |                                                                                    |                   |                  |

|                       |                              | in in Simplex n<br>in in Flow Con                   |                                |                                          |                                                                                    |                   |                  |

| bit 10                | Unimplemen                   | ted: Read as '                                      | 0'                             |                                          |                                                                                    |                   |                  |

| bit 9-8               | <b>UEN&lt;1:0&gt;:</b> ∪     | ARTx Pin Enal                                       | ole bits                       |                                          |                                                                                    |                   |                  |

|                       | 10 = UxTX, U<br>01 = UxTX, U | JxRX, UxCTS a<br>JxRX and UxR<br>nd UxRX pins a     | and UxRTS pi<br>TS pins are er | ns are enableo<br>nabled an <u>d use</u> | d; UxCTS pin is<br>d an <u>d used</u><br>ed; UxC <u>TS pin is</u><br>S and UxRTS/F | s controlled by   | port latches     |

| bit 7                 | WAKE: Wake                   | -up on Start Bi                                     | t Detect Durin                 | g Sleep Mode                             | Enable bit                                                                         |                   |                  |

|                       | hardware                     | ontinues to sar<br>on following r<br>-up is enabled | •                              | K pin; interrupt                         | is generated or                                                                    | n falling edge; b | it is cleared in |

| bit 6                 |                              | RTx Loopback                                        | Mode Select                    | bit                                      |                                                                                    |                   |                  |

|                       | 1 = Enables I                | Loopback mod                                        | e                              |                                          |                                                                                    |                   |                  |

| DIL O                 | 0 = Loopback                 | k mode is disal                                     |                                |                                          |                                                                                    |                   |                  |

|                       | -                            | k mode is disal<br>p-Baud Enable                    |                                |                                          |                                                                                    |                   |                  |

| bit 5                 | ABAUD: Auto                  | o-Baud Enable                                       | bit<br>surement on t           |                                          | eter – requires re                                                                 | eception of a S   | ync field (55h   |

REGISTER 20-1: UxMODE: UARTx MODE REGISTER

© 2009-2012 Microchip Technology Inc.

2: This feature is only available for the 16x BRG mode (BRGH = 0).

|                  | R/W-x                                                                                       | U-0                                                                                                                                                                     | U-0                                                                                      | U-0                                      | R/W-x           | R/W-x               | R/W-x |

|------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------|-----------------|---------------------|-------|

|                  | WAKFIL                                                                                      |                                                                                                                                                                         | _                                                                                        | —                                        |                 | SEG2PH<2:0>         |       |

| bit 15           |                                                                                             |                                                                                                                                                                         |                                                                                          |                                          |                 |                     | bit   |

| R/W-x            | R/W-x                                                                                       | R/W-x                                                                                                                                                                   | R/W-x                                                                                    | R/W-x                                    | R/W-x           | R/W-x               | R/W-x |

| SEG2PHTS         |                                                                                             |                                                                                                                                                                         | SEG1PH<2:0>                                                                              |                                          |                 | PRSEG<2:0>          |       |

| bit 7            |                                                                                             |                                                                                                                                                                         |                                                                                          |                                          |                 |                     | bit   |

| Legend:          |                                                                                             |                                                                                                                                                                         |                                                                                          |                                          |                 |                     |       |

| R = Readabl      | le bit                                                                                      | W = Writable                                                                                                                                                            | e bit                                                                                    | U = Unimpler                             | nented bit, rea | ad as '0'           |       |

| -n = Value at    | t POR                                                                                       | '1' = Bit is se                                                                                                                                                         | t                                                                                        | '0' = Bit is cle                         | ared            | x = Bit is unkno    | own   |

|                  |                                                                                             |                                                                                                                                                                         |                                                                                          |                                          |                 |                     |       |

| bit 15           | Unimplemen                                                                                  | nted: Read as                                                                                                                                                           | <b>'</b> 0 <b>'</b>                                                                      |                                          |                 |                     |       |

| bit 14           | WAKFIL: Sel                                                                                 | lect CAN Bus                                                                                                                                                            | Line Filter for W                                                                        | /ake-up bit                              |                 |                     |       |

|                  |                                                                                             | N bus line filte                                                                                                                                                        |                                                                                          |                                          |                 |                     |       |

|                  |                                                                                             |                                                                                                                                                                         | t used for wake                                                                          | e-up                                     |                 |                     |       |

| bit 13-11        | -                                                                                           | ted: Read as                                                                                                                                                            |                                                                                          |                                          |                 |                     |       |

| bit 10-8         | 111 = Length                                                                                | <b>)&gt;:</b> Phase Seg                                                                                                                                                 | iment 2 bits                                                                             |                                          |                 |                     |       |

|                  | III - Lengu                                                                                 |                                                                                                                                                                         |                                                                                          |                                          |                 |                     |       |

|                  | •                                                                                           |                                                                                                                                                                         |                                                                                          |                                          |                 |                     |       |

|                  | •                                                                                           |                                                                                                                                                                         |                                                                                          |                                          |                 |                     |       |

|                  | •                                                                                           |                                                                                                                                                                         |                                                                                          |                                          |                 |                     |       |

|                  | •<br>•<br>000 = Length                                                                      |                                                                                                                                                                         |                                                                                          |                                          |                 |                     |       |

| bit 7            | •<br>•<br>000 = Length                                                                      | n is 1 x Tq                                                                                                                                                             | ent 2 Time Sele                                                                          | ct bit                                   |                 |                     |       |

| bit 7            | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | n is 1 x TQ<br>Phase Segme<br>ogrammable                                                                                                                                |                                                                                          |                                          | Time (IPT), w   | /hichever is greate | er    |

| bit 7<br>bit 6   | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | n is 1 x TQ<br>Phase Segme<br>ogrammable                                                                                                                                | oits or Informati                                                                        |                                          | Time (IPT), w   | /hichever is greate | er    |

|                  | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | n is 1 x TQ<br>Phase Segme<br>ogrammable<br>n of SEG1PH I<br>e of the CAN E<br>s sampled thre                                                                           | oits or Informati                                                                        | on Processing sample point               | Time (IPT), w   | /hichever is great  | er    |

|                  | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | n is 1 x TQ<br>Phase Segme<br>ogrammable<br>n of SEG1PH I<br>e of the CAN E<br>s sampled thre                                                                           | bits or Informati<br>Bus Line bit<br>be times at the<br>be at the sample                 | on Processing sample point               | Time (IPT), w   | /hichever is great  | er    |

| bit 6            | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | n is 1 x TQ<br>Phase Segme<br>ogrammable<br>n of SEG1PH I<br>e of the CAN E<br>s sampled thre<br>s sampled onc<br><b>D&gt;:</b> Phase Seg                               | bits or Informati<br>Bus Line bit<br>be times at the<br>be at the sample                 | on Processing sample point               | Time (IPT), w   | /hichever is great  | er    |

| bit 6            | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | n is 1 x TQ<br>Phase Segme<br>ogrammable<br>n of SEG1PH I<br>e of the CAN E<br>s sampled thre<br>s sampled onc<br><b>D&gt;:</b> Phase Seg                               | bits or Informati<br>Bus Line bit<br>be times at the<br>be at the sample                 | on Processing sample point               | Time (IPT), w   | vhichever is great  | er    |

| bit 6            | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | n is 1 x TQ<br>Phase Segme<br>ogrammable<br>n of SEG1PH I<br>e of the CAN E<br>s sampled thre<br>s sampled onc<br><b>D&gt;:</b> Phase Seg                               | bits or Informati<br>Bus Line bit<br>be times at the<br>be at the sample                 | on Processing sample point               | Time (IPT), w   | /hichever is great  | er    |

| bit 6            | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | n is 1 x TQ<br>Phase Segme<br>ogrammable<br>n of SEG1PH I<br>e of the CAN E<br>s sampled thre<br>s sampled onc<br><b>D</b> : Phase Seg<br>n is 8 x TQ                   | bits or Informati<br>Bus Line bit<br>be times at the<br>be at the sample                 | on Processing sample point               | Time (IPT), w   | /hichever is great  | er    |

| bit 6<br>bit 5-3 | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | n is 1 x TQ<br>Phase Segme<br>ogrammable<br>n of SEG1PH I<br>e of the CAN E<br>s sampled thre<br>s sampled onc<br><b>D&gt;:</b> Phase Seg<br>n is 8 x TQ                | bits or Informati<br>Bus Line bit<br>ee times at the<br>ce at the sample<br>gment 1 bits | on Processing<br>sample point<br>e point | Time (IPT), w   | /hichever is great  | er    |

| bit 6            | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | n is 1 x TQ<br>Phase Segme<br>ogrammable<br>n of SEG1PH I<br>e of the CAN E<br>s sampled thre<br>s sampled onc<br><b>D&gt;:</b> Phase Seg<br>n is 8 x TQ<br>n is 1 x TQ | bits or Informati<br>Bus Line bit<br>be times at the<br>be at the sample                 | on Processing<br>sample point<br>e point | Time (IPT), w   | /hichever is great  | er    |