Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 122                                                                            |

| Program Memory Size        | 256KB (85.5K x 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 12K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

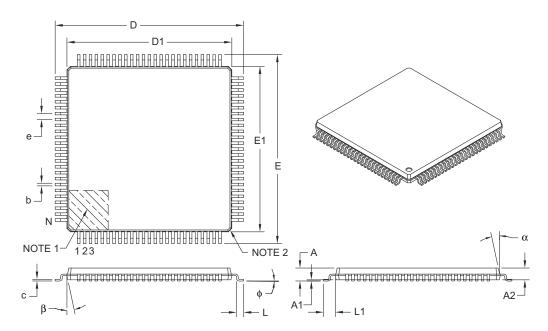

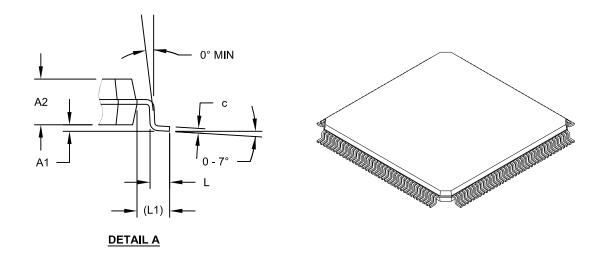

| Package / Case             | 144-LQFP                                                                       |

| Supplier Device Package    | 144-LQFP (20x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gu814-e-pl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.6 CPU Resources

Many useful resources related to the CPU are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | 2                                                                                    |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en554310                                                       |

## 3.6.1 KEY RESOURCES

- See Section 16. "CPU" (DS70359) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/ 810/814 and PIC24EPXXX(GP/GU)810/ 814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 4. "Program Memory" (DS70613) of the "dsPIC33E/ PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The device architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

## 4.1 Program Address Space

The device program address memory space is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or data space remapping as described in **Section 4.8 "Interfacing Program and Data Memory Spaces"**.

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The device program memory map is shown in Figure 4-1.

## FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 DEVICES<sup>(1)</sup>

| Ť                          | GOTO Instruction <sup>(2)</sup>                                                                                                       | GOTO Instruction <sup>(2)</sup><br>Reset Address <sup>(2)</sup> | 0x000000<br>0x000002                        |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------|

| -                          | Interrupt Vector Table                                                                                                                | Interrupt Vector Table                                          | 0x000004<br>0x0001FE<br>0x000200            |

| / Space                    | User Program<br>Flash Memory<br>(87552 instructions)                                                                                  | User Program<br>Flash Memory<br>(175104 instructions)           | 0x02ABFE<br>0x02AC00                        |

| User Memory Space          | ט<br>Unimplemented<br>(Read '0's)                                                                                                     | Unimplemented                                                   | 0x0557FE<br>0x055800                        |

| Use                        | Auxiliary Program                                                                                                                     | (Read '0's)<br>Auxiliary Program<br>Flash Memory                | 0x7FBFFE<br>0x7FC000<br>0x7FFFF8            |

| 0                          | Auxiliary Program<br>Flash Memory<br>Auxiliary Interrupt<br>Vector<br>GOTO Instruction <sup>(2)</sup><br>Reset Address <sup>(2)</sup> | Auxiliary Interrupt<br>Vector                                   | 0x7FFFFA                                    |

|                            | GOTO Instruction <sup>(2)</sup>                                                                                                       | GOTO Instruction <sup>(2)</sup>                                 | 0x7FFFFC                                    |

|                            | Reset Address <sup>(2)</sup>                                                                                                          | Reset Address <sup>(2)</sup>                                    | 0x7FFFE                                     |

| Î                          | Reserved                                                                                                                              | Reserved                                                        | 0x800000                                    |

| ' Space                    | Device Configuration<br>Registers                                                                                                     | Device Configuration<br>Registers                               | 0xF7FFE<br>0xF80000<br>0xF80012<br>0xF80014 |

| lemory                     | Reserved                                                                                                                              | Reserved                                                        | 0xF9FFFE                                    |

| Configuration Memory Space | Write Latch                                                                                                                           | Write Latch                                                     | 0xFA0000<br>0xFA00FE                        |

| nfigu                      | Reserved                                                                                                                              | Reserved                                                        | 0xFA0100<br>0xFEFFFE                        |

| ပိ                         | DEVID (2 Words)                                                                                                                       | DEVID (2 Words)                                                 | 0xFF0000<br>0xFF0002                        |

|                            | Reserved                                                                                                                              | Reserved                                                        |                                             |

|                            |                                                                                                                                       |                                                                 |                                             |

**Note 1:** Memory areas are not shown to scale.

2: The Reset location is controlled by the Reset Target Vector Select bit, RSTPRI (FICD<2>). See Section 29.0 "Special Features" for more information.

| File Name            | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7                  | Bit 6             | Bit 5                 | Bit 4        | Bit 3       | Bit 2    | Bit 1     | Bit 0    | All<br>Resets |

|----------------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|------------------------|-------------------|-----------------------|--------------|-------------|----------|-----------|----------|---------------|

| U10TGIR              | 0488  | —      | —      | —      |        |        | —      | —     | —     | IDIF                   | T1MSECIF          | LSTATEIF              | ACTVIF       | SESVDIF     | SESENDIF | _         | VBUSVDIF | 0000          |

| U10TGIE              | 048A  | _      | _      | _      | _      | _      | _      | _     | _     | IDIE                   | T1MSECIE          | LSTATEIE              | ACTVIE       | SESVDIE     | SESENDIE | _         | VBUSVDIE | 0000          |

| U10TGSTAT            | 048C  | _      | _      | _      | _      | _      | _      | _     | _     | ID                     | —                 | LSTATE                | —            | SESVD       | SESEND   | _         | VBUSVD   | 0000          |

| U10TGCON             | 048E  | _      | _      | _      | _      | _      | _      | —     | _     | DPPULUP                | DMPULUP           | DPPULDWN              | DMPULDWN     | VBUSON      | OTGEN    | VBUSCHG   | VBUSDIS  | 0000          |

| U1PWRC               | 0490  |        | _      | _      | -      | _      | _      | _     | _     | UACTPND <sup>(4)</sup> | _                 | —                     | USLPGRD      | _           | _        | USUSPND   | USBPWR   | 0000          |

| U1IR <sup>(1)</sup>  | 04C0  | _      |        |        |        |        | _      |       |       | STALLIF                | —                 | RESUMEIF              | IDLEIF       | TRNIF       | SOFIF    | UERRIF    | URSTIF   | 0000          |

| U1IR <sup>(2)</sup>  | 04C0  |        | _      | _      | -      | _      | _      | _     | _     | STALLIF                | ATTACHIF          | RESUMEIF              | IDLEIF       | TRNIF       | SOFIF    | UERRIF    | DETACHIF | 0000          |

| U1IE <sup>(1)</sup>  | 04C2  | _      |        |        |        |        | _      |       |       | STALLIE                | —                 | RESUMEIE              | IDLEIE       | TRNIE       | SOFIE    | UERRIE    | URSTIE   | 0000          |

| U1IE <sup>(2)</sup>  | 04C2  | _      |        | I      |        | -      |        |       | _     | STALLIE                | ATTACHIE          | RESUMEIE              | IDLEIE       | TRNIE       | SOFIE    | UERRIE    | DETACHIE | 0000          |

| U1EIR <sup>(1)</sup> | 04C4  | _      |        | I      |        | _      |        |       | _     | BTSEF                  | BUSACCEF          | DMAEF                 | BTOEF        | DFN8EF      | CRC16EF  | CRC5EF    | PIDEF    | 0000          |

| U1EIR <sup>(2)</sup> | 04C4  | _      |        | I      |        | _      |        |       | _     | BTSEF                  | BUSACCEF          | DMAEF                 | BTOEF        | DFN8EF      | CRC16EF  | EOFEF     | PIDEF    | 0000          |

| U1EIE <sup>(1)</sup> | 04C6  | _      |        | I      |        | _      |        |       | _     | BTSEE                  | BUSACCEE          | DMAEE                 | BTOEE        | DFN8EE      | CRC16EE  | CRC5EE    | PIDEE    | 0000          |

| U1EIE <sup>(2)</sup> | 04C6  | _      |        |        | -      | _      |        |       | -     | BTSEE                  | BUSACCEE          | DMAEE                 | BTOEE        | DFN8EE      | CRC16EE  | EOFEE     | PIDEE    | 0000          |

| U1STAT               | 04C8  | _      |        | I      |        | _      |        |       | _     |                        | ENDP <sup>-</sup> | T<3:0> <sup>(3)</sup> |              | DIR         | PPBI     | _         |          | 0000          |

| U1CON <sup>(1)</sup> | 04CA  | _      |        |        | -      | _      |        |       | -     | -                      | SE0               | PKTDIS                | —            | HOSTEN      | RESUME   | PPBRST    | USBEN    | 0000          |

| U1CON <sup>(2)</sup> | 04CA  | —      | -      | _      | —      | —      | —      | —     | —     | JSTATE                 | SE0               | TOKBUSY               | USBRST       | HOSTEN      | RESUME   | PPBRST    | SOFEN    | 0000          |

| U1ADDR               | 04CC  | —      | -      | _      | —      | —      | —      | —     | —     | LSPDEN <sup>(1)</sup>  |                   |                       | USB Device A | ddress (DEV | ADDR)    |           |          | 0000          |

| U1BDTP1              | 04CE  | —      | _      | _      | _      | _      | —      | _     | —     |                        |                   | BDT                   | PTRL<15:9>   |             |          |           | _        | 0000          |

| U1FRML               | 04D0  | —      | _      | _      | _      | _      | —      | _     | —     |                        | -                 |                       | FRML<7:0     | >           |          |           |          | 0000          |

| U1FRMH               | 04D2  | _      | _      | _      | _      | _      | _      | _     | _     | _                      | —                 | —                     | —            | _           |          | FRMH<2:0> |          | 0000          |

| U1TOK <sup>(3)</sup> | 04D4  | —      | _      | _      | _      | _      | —      | _     | —     |                        | PID               | <3:0>                 |              |             | EP       | <3:0>     |          | 0000          |

| U1SOF <sup>(3)</sup> | 04D6  | _      | _      | _      | _      | _      | _      | _     | _     |                        |                   |                       | CNT<7:0>     | <b>`</b>    |          |           |          | 0000          |

| U1BDTP2              | 04D8  | —      | _      | _      | _      | _      | —      | _     | —     |                        |                   |                       | BDTPTRH<23   | 3:16>       |          |           |          | 0000          |

| U1BDTP3              | 04DA  | —      | -      | _      | —      | —      | —      | —     | —     |                        |                   |                       | BDTPTRU<31   | :24>        |          |           |          | 0000          |

| U1CNFG1              | 04DC  | —      | -      | _      | —      | —      | —      | —     | —     | UTEYE                  | UOEMON            | —                     | USBSIDL      | —           | —        | —         | _        | 0000          |

| U1CNFG2              | O4DE  | —      | -      | _      | —      | —      | —      | —     | —     | —                      | —                 | UVCMPSEL              | PUVBUS       | EXTI2CEN    | UVBUSDIS | UVCMPDIS  | UTRDIS   | 0000          |

| U1EP0                | 04E0  | _      | _      | _      | —      | —      | —      | _     | —     | LSPD                   | RETRYDIS          | _                     | EPCONDIS     | EPRXEN      | EPTXEN   | EPSTALL   | EPHSHK   | 0000          |

| U1EP1                | 04E2  | _      |        | -      | _      | _      | -      | _     | -     | —                      | —                 | —                     | EPCONDIS     | EPRXEN      | EPTXEN   | EPSTALL   | EPHSHK   | 0000          |

| U1EP2                | 04E4  | _      | _      | _      | —      | _      | —      | _     | -     | —                      | —                 | —                     | EPCONDIS     | EPRXEN      | EPTXEN   | EPSTALL   | EPHSHK   | 0000          |

| U1EP3                | 04E6  | _      | —      | —      | —      |        | —      | —     | -     | _                      | _                 | _                     | EPCONDIS     | EPRXEN      | EPTXEN   | EPSTALL   | EPHSHK   | 0000          |

| U1EP4                | 04E8  | _      | _      |        |        |        | _      | _     | _     | _                      | _                 | _                     | EPCONDIS     | EPRXEN      | EPTXEN   | EPSTALL   | EPHSHK   | 0000          |

TABLE 4-27: USB OTG REGISTER MAP FOR dsPIC33EPMU806/810/814 AND PIC24EPGU806/10/814) DEVICES ONLY

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** This bit is available when the module is operating in Device mode.

2: This bit is available when the module is operating in Host mode

3: Device mode only. These bits are always read as '0' in Host mode.

4: The Reset value for this bit is undefined.

#### TABLE 4-34: PARALLEL MASTER/SLAVE PORT REGISTER MAP

| File Name              | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12                                                                                   | Bit 11  | Bit 10 | Bit 9         | Bit 8       | Bit 7        | Bit 6          | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------------------|-------|--------|--------|--------|------------------------------------------------------------------------------------------|---------|--------|---------------|-------------|--------------|----------------|---------|-------|-------|-------|-------|-------|---------------|

| PMCON                  | 0600  | PMPEN  | —      | PSIDL  | ADRMU                                                                                    | JX<1:0> | PTBEEN | PTWREN        | PTRDEN      | CSF          | <1:0>          | ALP     | CS2P  | CS1P  | BEP   | WRSP  | RDSP  | 0000          |

| PMMODE                 | 0602  | BUSY   | IRQM   | <1:0>  | INCM                                                                                     | <1:0>   | MODE16 | MODE          | <1:0>       | WAIT         | B<1:0>         |         | WAITN | <3:0> |       | WAITE | <1:0> | 0000          |

| PMADDR <sup>(1)</sup>  | 0604  | CS2    | CS1    |        |                                                                                          |         |        |               | Para        | llel Port Ad | dress (ADDR    | <13:0>) |       |       |       |       |       | 0000          |

| PMDOUT1 <sup>(1)</sup> | 0604  |        |        |        |                                                                                          |         |        |               |             |              |                |         |       |       |       |       | 0000  |               |

| PMDOUT2                | 0606  |        |        |        |                                                                                          |         |        |               |             |              |                |         |       |       |       |       | 0000  |               |

| PMDIN1                 | 0608  |        |        |        |                                                                                          |         |        | Parallel Port | Data In Reg | ister 1 (Buf | fers Level 0 a | and 1)  |       |       |       |       |       | 0000          |

| PMDIN2                 | 060A  |        |        |        |                                                                                          |         |        | Parallel Port | Data In Reg | ister 2 (Buf | fers Level 2 a | and 3)  |       |       |       |       |       | 0000          |

| PMAEN                  | 060C  | PTEN15 | PTEN14 | PTEN13 | IEN13 PTEN12 PTEN11 PTEN10 PTEN9 PTEN8 PTEN7 PTEN6 PTEN5 PTEN4 PTEN3 PTEN2 PTEN1 PTEN0 0 |         |        |               |             |              |                |         |       |       | 0000  |       |       |               |

| PMSTAT                 | 060E  | IBF    | IBOV   |        |                                                                                          | IB3F    | IB2F   | IB1F          | IB0F        | OBE          | OBUF           | _       | _     | OB3E  | OB2E  | OB1E  | OB0E  | 008F          |

| Lonondi                |       | 1      |        | 0      |                                                                                          |         |        | ha DMD mad    |             |              |                |         |       |       |       |       |       |               |

Legend: — = unimplemented, read as '0'. Shaded bits are not used in the operation of the PMP module.

Note 1: PMADDR and PMDOUT1 are the same physical register, but are defined differently depending on the module's operating mode.

#### TABLE 4-35: CRC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                        | Bit 13        | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8    | Bit 7        | Bit 6  | Bit 5   | Bit 4 | Bit 3   | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|-------------------------------|---------------|--------|--------|-----------|-------|----------|--------------|--------|---------|-------|---------|----------|-------|-------|---------------|

| CRCCON1   | 0640  | CRCEN  | _                             | CSIDL         |        | V      | WORD<4:0  | >     |          | CRCFUL       | CRCMPT | CRCISEL | CRCGO | LENDIAN | _        | —     | —     | 0000          |

| CRCCON2   | 0642  | -      |                               | _             |        | D      | WIDTH<4:0 | )>    |          | _            | _      | _       |       | Р       | LEN<4:0> |       |       | 0000          |

| CRCXORL   | 0644  |        |                               |               |        |        |           |       | X<15:    | 1>           |        |         |       |         |          |       | _     | 0000          |

| CRCXORH   | 0646  |        |                               | X<31:16> 0000 |        |        |           |       |          |              |        |         |       |         | 0000     |       |       |               |

| CRCDATL   | 0648  |        |                               |               |        |        |           |       | CRC Data | Input Low V  | Vord   |         |       |         |          |       |       | 0000          |

| CRCDATH   | 064A  |        | CRC Data Input High Word 0000 |               |        |        |           |       |          |              |        |         |       | 0000    |          |       |       |               |

| CRCWDATL  | 064C  |        |                               |               |        |        |           |       | CRC Re   | sult Low Wo  | ord    |         |       |         |          |       |       | 0000          |

| CRCWDATH  | 064E  |        |                               |               |        |        |           |       | CRC Re   | sult High Wo | ord    |         |       |         |          |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

## TABLE 4-36: REAL-TIME CLOCK AND CALENDAR REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                                            | Bit 13                          | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8  | Bit 7    | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|---------------------------------------------------|---------------------------------|---------|---------|--------|-------|--------|----------|-------|-------|---------|-------|-------|-------|-------|---------------|

| ALRMVAL   | 0620  |        | Alarm Value Register Window based on ALRMPTR<1:0> |                                 |         |         |        |       |        |          |       |       |         | XXXX  |       |       |       |               |

| ALCFGRPT  | 0622  | ALRMEN | CHIME                                             | AMASK<3:0> ALRMPTR<1:0> ARPT<7: |         |         |        |       |        |          |       |       | PT<7:0> |       |       | 0000  |       |               |

| RTCVAL    | 0624  |        | RTCC Value Register Window based on RTCPTR<1:0>   |                                 |         |         |        |       |        |          |       |       | XXXX    |       |       |       |       |               |

| RCFGCAL   | 0626  | RTCEN  | —                                                 | RTCWREN                         | RTCSYNC | HALFSEC | RTCOE  | RTCPT | R<1:0> | CAL<7:0> |       |       |         |       |       |       | 0000  |               |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

#### TABLE 4-49: PMD REGISTER MAP FOR dsPIC33EPXXXMU806 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------|---------|--------|--------|--------|--------|--------|--------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | DCIMD  | I2C1MD  | U2MD    | U1MD   | SPI2MD | SPI1MD | C2MD   | C1MD   | AD1MD  | 0000          |

| PMD2         | 0762  | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD  | OC8MD   | OC7MD   | OC6MD  | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3         | 0764  | T9MD   | T8MD   | T7MD   | T6MD   | —      | CMPMD  | RTCCMD | PMPMD  | CRCMD   |         | QEI2MD |        | U3MD   | _      | I2C2MD | AD2MD  | 0000          |

| PMD4         | 0766  | —      | _      | _      |        | _      | —      | —      | —      |         |         | U4MD   |        | REFOMD | _      | _      | USB1MD | 0000          |

| PMD5         | 0768  | IC16MD | IC15MD | IC14MD | IC13MD | IC12MD | IC11MD | IC10MD | IC9MD  | OC16MD  | OC15MD  | OC14MD | OC13MD | OC12MD | OC11MD | OC10MD | OC9MD  | 0000          |

| PMD6         | 076A  | —      | _      | _      |        | PWM4MD | PWM3MD | PWM2MD | PWM1MD |         |         | _      |        | _      | _      | SPI4MD | SPI3MD | 0000          |

|              |       | —      | _      | _      |        | _      | —      | —      | —      | DMA12MD | DMA8MD  | DMA4MD | DMA0MD | _      | _      | _      |        | 0000          |

| PMD7         | 076C  | —      | _      | _      |        | _      | —      | —      | —      | DMA13MD | DMA9MD  | DMA5MD | DMA1MD | _      | _      | _      |        | 0000          |

| FINDT        | 0700  | —      | _      | _      |        | _      | —      | —      | —      | DMA14MD | DMA10MD | DMA6MD | DMA2MD | _      | _      | _      |        | 0000          |

|              |       | _      | _      | _      | _      | _      | _      | _      | _      | -       | DMA11MD | DMA7MD | DMA3MD | _      | _      | _      | _      | 0000          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-50: PMD REGISTER MAP FOR dsPIC33EPXXXMC806 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------|---------|--------|--------|--------|--------|--------|--------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | DCIMD  | I2C1MD  | U2MD    | U1MD   | SPI2MD | SPI1MD | C2MD   | C1MD   | AD1MD  | 0000          |

| PMD2         | 0762  | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD  | IC1MD  | OC8MD   | OC7MD   | OC6MD  | OC5MD  | OC4MD  | OC3MD  | OC2MD  | OC1MD  | 0000          |

| PMD3         | 0764  | T9MD   | T8MD   | T7MD   | T6MD   | —      | CMPMD  | RTCCMD | PMPMD  | CRCMD   | —       | QEI2MD |        | U3MD   | _      | I2C2MD | AD2MD  | 0000          |

| PMD4         | 0766  |        | _      | _      | _      | _      | _      | _      | _      | _       | _       | U4MD   | _      | REFOMD | _      | _      | _      | 0000          |

| PMD5         | 0768  | IC16MD | IC15MD | IC14MD | IC13MD | IC12MD | IC11MD | IC10MD | IC9MD  | OC16MD  | OC15MD  | OC14MD | OC13MD | OC12MD | OC11MD | OC10MD | OC9MD  | 0000          |

| PMD6         | 076A  |        | _      | _      | _      | PWM4MD | PWM3MD | PWM2MD | PWM1MD | _       | _       | _      | _      | _      | _      | SPI4MD | SPI3MD | 0000          |

|              |       |        | _      | _      | _      | _      | _      | _      | _      | DMA12MD | DMA8MD  | DMA4MD | DMA0MD | _      | _      | _      | _      | 0000          |

|              | 0760  |        | _      | _      | _      | _      | _      | _      | _      | DMA13MD | DMA9MD  | DMA5MD | DMA1MD | _      | _      | _      | _      | 0000          |

| PMD7         | 076C  | _      | —      | —      | —      | _      | _      | —      | —      | DMA14MD | DMA10MD | DMA6MD | DMA2MD | —      | —      | —      | _      | 0000          |

|              |       | _      | _      | _      | _      | _      | _      | _      | _      | _       | DMA11MD | DMA7MD | DMA3MD | _      | _      | _      | _      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0             | R-0          | R-0                                                   | R-0           | R-0              | R-0              | R-0             | R-0    |

|-----------------|--------------|-------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|

| _               | RQCOL14      | RQCOL13                                               | RQCOL12       | RQCOL11          | RQCOL10          | RQCOL9          | RQCOL8 |

| bit 15          |              |                                                       |               |                  |                  |                 | bit 8  |

| R-0             | R-0          | R-0                                                   | R-0           | R-0              | R-0              | R-0             | R-0    |

| RQCOL7          | RQCOL6       | RQCOL5                                                | RQCOL4        | RQCOL3           | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7           |              |                                                       |               |                  |                  |                 | bit (  |

| Legend:         |              |                                                       |               |                  |                  |                 |        |

| R = Readable    | bit          | W = Writable                                          | bit           | U = Unimpler     | mented bit, read | l as '0'        |        |

| -n = Value at I | POR          | '1' = Bit is set                                      |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15          | Unimplemen   | ted: Read as '                                        | 0'            |                  |                  |                 |        |

| bit 14          | -            | hannel 14 Trar                                        |               | Collision Flag   | bit              |                 |        |

|                 | 1 = User FO  | RCE and interrest collision det                       | upt-based req | 0                |                  |                 |        |

| bit 13          | •            | hannel 13 Trar                                        |               | Collision Flag   | bit              |                 |        |

|                 | 1 = User FO  | RCE and interrest collision det                       | upt-based req |                  |                  |                 |        |

| bit 12          | RQCOL12: C   | hannel 12 Trar<br>RCE and interr                      | nsfer Request | •                |                  |                 |        |

|                 | 0 = No reque | est collision det                                     | ected         |                  |                  |                 |        |

| bit 11          |              | hannel 11 Trar                                        | •             | •                |                  |                 |        |

|                 |              | RCE and interrest collision det                       |               | uest collision o | detected         |                 |        |

| bit 10          |              | hannel 10 Trar                                        | =             | -                |                  |                 |        |

|                 |              | RCE and interrest collision det                       |               | uest collision o | detected         |                 |        |

| bit 9           | 1 = User FO  | annel 9 Transf<br>RCE and interr<br>est collision det | upt-based req | •                |                  |                 |        |

| bit 8           | 1 = User FO  | annel 8 Transf<br>RCE and interr                      | upt-based req | •                |                  |                 |        |

|                 |              | est collision det                                     |               |                  |                  |                 |        |

| bit 7           |              | annel 7 Transf                                        | -             | -                |                  |                 |        |

|                 |              | RCE and interrest collision def                       | •             | uest collision ( | Delected         |                 |        |

| bit 6           |              | annel 6 Transf                                        | -             | -                |                  |                 |        |

|                 |              | RCE and interrest collision det                       | •             | uest collision o | detected         |                 |        |

| bit 5           | -            | annel 5 Transf                                        |               | llision Flag bit |                  |                 |        |

|                 |              | RCE and interrest collision det                       |               | uest collision o | detected         |                 |        |

| bit 4           | RQCOL4: Ch   | annel 4 Transf                                        | er Request Co | llision Flag bit |                  |                 |        |

|                 |              | RCE and interrest collision det                       |               | uest collision o | detected         |                 |        |

| bit 3           | RQCOL3: Ch   | annel 3 Transf                                        | er Request Co | llision Flag bit |                  |                 |        |

|                 |              | RCE and interrest collision det                       |               | uest collision o | detected         |                 |        |

## REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

## REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER (CONTINUED)

| bit 2 | RQCOL2: Channel 2 Transfer Request Collision Flag bit                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = User FORCE and interrupt-based request collision detected</li><li>0 = No request collision detected</li></ul> |

| bit 1 | RQCOL1: Channel 1 Transfer Request Collision Flag bit                                                                     |

|       | 1 = User FORCE and interrupt-based request collision detected                                                             |

|       | 0 = No request collision detected                                                                                         |

| bit 0 | RQCOL0: Channel 0 Transfer Request Collision Flag bit                                                                     |

|       | 1 = User FORCE and interrupt-based request collision detected                                                             |

|       | 0 = No request collision detected                                                                                         |

| U-0                | R/W-0              | R/W-0                                                          | R/W-0          | R/W-0                 | R/W-0           | R/W-0           | R/W-0 |

|--------------------|--------------------|----------------------------------------------------------------|----------------|-----------------------|-----------------|-----------------|-------|

|                    |                    |                                                                |                | IC2R<6:0>             |                 |                 |       |

| it 15              |                    |                                                                |                |                       |                 |                 | bit 8 |

| U-0                | R/W-0              | R/W-0                                                          | R/W-0          | R/W-0                 | R/W-0           | R/W-0           | R/W-0 |

| _                  |                    |                                                                |                | IC1R<6:0>             |                 |                 |       |

| oit 7              |                    |                                                                |                |                       |                 |                 | bit ( |

|                    |                    |                                                                |                |                       |                 |                 |       |

| _egend:            |                    |                                                                |                |                       |                 |                 |       |

| R = Readat         | ole bit            | W = Writable                                                   | bit            | U = Unimplen          | nented bit, rea | id as '0'       |       |

| -n = Value a       | at POR             | '1' = Bit is set                                               | :              | '0' = Bit is clea     | ared            | x = Bit is unkr | nown  |

| bit 15<br>bit 14-8 | IC2R<6:0>: /       | <b>1ted:</b> Read as '<br>Assign Input Ca<br>1-2 for input pin | apture 2 (IC2) | to the Correspondent  | onding RPn/R    | PIn Pin bits    |       |

|                    |                    | nput tied to RP                                                |                | ,                     |                 |                 |       |

|                    |                    |                                                                |                |                       |                 |                 |       |

|                    |                    | nput tied to CM<br>nput tied to Vss                            |                |                       |                 |                 |       |

| bit 7              | Unimplemer         | nted: Read as '                                                | 0'             |                       |                 |                 |       |

| bit 6-0            |                    | Assign Input Ca<br>1-2 for input pin                           |                | to the Corresponders) | onding RPn/R    | PIn Pin bits    |       |

|                    | 1111111 <b>=  </b> | nput tied to RP                                                | 127            |                       |                 |                 |       |

|                    |                    |                                                                |                |                       |                 |                 |       |

|                    | •                  |                                                                |                |                       |                 |                 |       |

## REGISTER 11-8: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

### REGISTER 11-12: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0          | R/W-0                              | R/W-0                                                                        | R/W-0                      | R/W-0                              | R/W-0           | R/W-0     | R/W-0       |  |

|--------------|------------------------------------|------------------------------------------------------------------------------|----------------------------|------------------------------------|-----------------|-----------|-------------|--|

| _            |                                    |                                                                              |                            | OCFBR<6:0>                         |                 |           |             |  |

| bit 15       |                                    |                                                                              |                            |                                    |                 |           | bit 8       |  |

| U-0          | R/W-0                              | R/W-0                                                                        | R/W-0                      | R/W-0                              | R/W-0           | R/W-0     | R/W-0       |  |

|              |                                    | 10110                                                                        |                            | OCFAR<6:0>                         |                 | 10110     | 1010 0      |  |

| bit 7        |                                    |                                                                              |                            |                                    |                 |           | bit 0       |  |

| Legend:      |                                    |                                                                              |                            |                                    |                 |           |             |  |

| R = Readab   | le bit                             | W = Writable                                                                 | bit                        | U = Unimplem                       | nented bit, rea | ad as '0' |             |  |

| -n = Value a | -n = Value at POR '1' = Bit is set |                                                                              |                            | '0' = Bit is cleared x = Bit is ur |                 |           | nknown      |  |

|              | (see Table 11-                     | -2 for input pin                                                             |                            |                                    | oo oonoop       | <u>g</u>  | In Pin bits |  |

|              | 1111111 = In<br>0000001 = In       | -2 for input pin<br>aput tied to RP1<br>aput tied to CMI<br>aput tied to Vss | selection nun<br>I27<br>P1 |                                    |                 |           |             |  |

| bit 7        | 1111111 = In                       | put tied to RP1                                                              | selection nun<br>127<br>P1 |                                    |                 |           |             |  |

#### REGISTER 11-25: RPINR25: PERIPHERAL PIN SELECT INPUT REGISTER 25

| U-0                                | U-0   | U-0                                     | U-0   | U-0          | U-0             | U-0      | U-0   |

|------------------------------------|-------|-----------------------------------------|-------|--------------|-----------------|----------|-------|

| _                                  |       | —                                       | _     | —            |                 | —        | —     |

| bit 15                             |       |                                         |       |              |                 |          | bit 8 |

| U-0                                | R/W-0 | R/W-0                                   | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

| _                                  |       | 10110                                   |       | COFSR<6:0>   | -               | 10110    |       |

| bit 7                              |       |                                         |       |              |                 |          | bit 0 |

| Legend:                            |       |                                         |       |              |                 |          |       |

| R = Readable                       | bit   | W = Writable I                          | oit   | U = Unimpler | nented bit, rea | d as '0' |       |

| -n = Value at POR (1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |              | nown            |          |       |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 **COFSR<6:0>:** Assign DCI FSYNC Input (COFS) to the Corresponding RPn/RPIn Pin bits (see Table 11-2 for input pin selection numbers) 1111111 = Input tied to RP127

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

## REGISTER 11-47: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —      | —   |       | RP71R<5:0> |       |       |       |       |  |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |  |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP70  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 13-8 | <b>RP71R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP71 Output Pin bits |

|----------|-----------------------------------------------------------------------------------------|

|          | (see Table 11-3 for peripheral function numbers)                                        |

| bit 7-6  | Unimplemented: Read as '0'                                                              |

bit 5-0 **RP70R<5:0>:** Peripheral Output Function is Assigned to RP70 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### REGISTER 11-48: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP80  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|------------|-------|-------|-------|-------|-------|--|

| —     | —   | RP79R<5:0> |       |       |       |       |       |  |

| bit 7 |     |            |       |       |       |       | bit 0 |  |

| Legend:           |                                                                  |                      |                    |  |

|-------------------|------------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                                 | '0' = Bit is cleared | x = Bit is unknown |  |

bit 15-14 Unimplemented: Read as '0'

| bit 13-8 | RP80R<5:0>: Peripheral Output Function is Assigned to RP80 Output Pin bits |

|----------|----------------------------------------------------------------------------|

|          | (see Table 11-3 for peripheral function numbers)                           |

| bit 7-6  | Unimplemented: Read as '0'                                                 |

bit 5-0 **RP79R<5:0>:** Peripheral Output Function is Assigned to RP79 Output Pin bits (see Table 11-3 for peripheral function numbers)

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| R-0              | R-0<br>TERRO     | R-0<br>CNT<7:0>     | R-0          | R-0                | R-0                           |

|------------------|------------------|---------------------|--------------|--------------------|-------------------------------|

|                  | TERRO            | CNT<7:0>            |              |                    |                               |

|                  |                  |                     |              |                    |                               |

|                  |                  |                     |              |                    | bit 8                         |

|                  |                  |                     |              |                    |                               |

| R-0              | R-0              | R-0                 | R-0          | R-0                | R-0                           |

|                  | RERRO            | CNT<7:0>            |              |                    |                               |

|                  |                  |                     |              |                    | bit 0                         |

|                  |                  |                     |              |                    |                               |

|                  |                  |                     |              |                    |                               |

| ' = Writable bit |                  | U = Unimpleme       | nted bit, re | ad as '0'          |                               |

| ' = Bit is set   |                  | '0' = Bit is cleare | ed           | x = Bit is unknown |                               |

|                  | / = Writable bit | RERRO               | RERRCNT<7:0> | RERRCNT<7:0>       | <pre>RERRCNT&lt;7:0&gt;</pre> |

| REGISTER 21-8: | CXEC: ECANX TRANSMIT/RECEIVE ERROR COUNT REGISTER |

|----------------|---------------------------------------------------|

|                |                                                   |

| bit 15-8 | TERRCNT<7:0>: Transmit Error Count bits |

|----------|-----------------------------------------|

| bit 7-0  | RERRCNT<7:0>: Receive Error Count bits  |

#### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | _   |     | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|----------|-------|-------|-------|-------|--------|-------|-------|

| SJW<1:0> |       |       |       | BRP   | °<5:0> |       |       |

| bit 7    |       |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0'                                                                       |

|----------|--------------------------------------------------------------------------------------------------|

| bit 7-6  | SJW<1:0>: Synchronization Jump Width bits                                                        |

|          | 11 = Length is 4 x TQ<br>10 = Length is 3 x TQ<br>01 = Length is 2 x TQ<br>00 = Length is 1 x TQ |

| bit 5-0  | BRP<5:0>: Baud Rate Prescaler bits                                                               |

|          | 11 1111 = TQ = 2 x 64 x 1/FCAN                                                                   |

|          | •                                                                                                |

|          | •                                                                                                |

|          | •                                                                                                |

|          | 00 0010 = TQ = 2 x 3 x 1/FCAN<br>00 0001 = TQ = 2 x 2 x 1/FCAN<br>00 0000 = TQ = 2 x 1 x 1/FCAN  |

## REGISTER 22-17: UxIE: USB INTERRUPT ENABLE REGISTER (HOST MODE)

| U-0          | U-0                                                                             | U-0                                                                             | U-0             | U-0               | U-0             | U-0            | U-0      |  |  |  |

|--------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------|-------------------|-----------------|----------------|----------|--|--|--|

| _            | —                                                                               | —                                                                               |                 | —                 | _               | _              | _        |  |  |  |

| bit 15       |                                                                                 |                                                                                 |                 |                   |                 |                | bit 8    |  |  |  |

|              |                                                                                 |                                                                                 |                 |                   |                 |                |          |  |  |  |

| R/W-0        | R/W-0                                                                           | R/W-0                                                                           | R/W-0           | R/W-0             | R/W-0           | R/W-0          | R/W-0    |  |  |  |

| STALLIE      | ATTACHIE <sup>(1)</sup>                                                         | RESUMEIE                                                                        | IDLEIE          | TRNIE             | SOFIE           | UERRIE         | DETACHIE |  |  |  |

| bit 7        |                                                                                 |                                                                                 |                 |                   |                 |                | bit      |  |  |  |

| Legend:      |                                                                                 |                                                                                 |                 |                   |                 |                |          |  |  |  |

| R = Readab   | le bit                                                                          | W = Writable b                                                                  | it              | U = Unimplem      | ented bit, read | 1 as '0'       |          |  |  |  |

| -n = Value a |                                                                                 | '1' = Bit is set                                                                |                 | '0' = Bit is clea |                 | x = Bit is unk | nown     |  |  |  |

|              |                                                                                 |                                                                                 |                 |                   |                 |                |          |  |  |  |

| bit 15-8     | Unimplement                                                                     | ted: Read as '0'                                                                |                 |                   |                 |                |          |  |  |  |

| oit 7        | STALLIE: ST                                                                     | ALL Handshake                                                                   | Interrupt Ena   | able bit          |                 |                |          |  |  |  |

|              | 1 = Interrupt                                                                   | is enabled                                                                      |                 |                   |                 |                |          |  |  |  |

|              | 0 = Interrupt                                                                   | is disabled                                                                     |                 |                   |                 |                |          |  |  |  |

| pit 6        | ATTACHIE: P                                                                     | eripheral Attach                                                                | Interrupt bit(  | 1)                |                 |                |          |  |  |  |

|              |                                                                                 | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul> |                 |                   |                 |                |          |  |  |  |

| bit 5        |                                                                                 | Resume Interrup                                                                 | t hit           |                   |                 |                |          |  |  |  |

|              | 1 = Interrupt i                                                                 |                                                                                 |                 |                   |                 |                |          |  |  |  |

|              | 0 = Interrupt                                                                   |                                                                                 |                 |                   |                 |                |          |  |  |  |

| bit 4        | IDLEIE: Idle [                                                                  | Detect Interrupt I                                                              | oit             |                   |                 |                |          |  |  |  |

|              | 1 = Interrupt                                                                   |                                                                                 |                 |                   |                 |                |          |  |  |  |

|              | 0 = Interrupt                                                                   |                                                                                 |                 |                   |                 |                |          |  |  |  |

| bit 3        |                                                                                 | Processing Co                                                                   | mplete Interro  | upt bit           |                 |                |          |  |  |  |

|              | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul> |                                                                                 |                 |                   |                 |                |          |  |  |  |

| oit 2        | •                                                                               | of-Frame Token                                                                  | Intorrunt hit   |                   |                 |                |          |  |  |  |

|              |                                                                                 |                                                                                 | interrupt bit   |                   |                 |                |          |  |  |  |

|              | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul> |                                                                                 |                 |                   |                 |                |          |  |  |  |

| oit 1        |                                                                                 | 3 Error Conditior                                                               | n Interrupt bit |                   |                 |                |          |  |  |  |

|              | 1 = Interrupt                                                                   |                                                                                 | •               |                   |                 |                |          |  |  |  |

|              | 0 = Interrupt                                                                   | is disabled                                                                     |                 |                   |                 |                |          |  |  |  |

| bit 0        |                                                                                 | JSB Detach Inte                                                                 | rrupt Enable    | bit               |                 |                |          |  |  |  |

|              | 1 = Interrupt                                                                   | is enabled                                                                      |                 |                   |                 |                |          |  |  |  |

|              | 0 = Interrupt                                                                   |                                                                                 |                 |                   |                 |                |          |  |  |  |

Note 1: Unimplemented in OTG mode, read as '0'.

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| R/W-0         | U-0                                                                                      | R/W-0                                             | R/W-0           | R/W-0            | R/W-0              | R/W-0            | R/W-0         |  |  |  |

|---------------|------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------|------------------|--------------------|------------------|---------------|--|--|--|

| HLMS          | —                                                                                        | OCEN                                              | OCNEN           | OBEN             | OBNEN              | OAEN             | OANEN         |  |  |  |

| bit 15        |                                                                                          |                                                   |                 |                  | 1                  | 1                | bit 8         |  |  |  |

| R/W-0         | R/W-0                                                                                    | R/W-0                                             | R/W-0           | R/W-0            | R/W-0              | R/W-0            | R/W-0         |  |  |  |

| NAGS          | PAGS                                                                                     | ACEN                                              | ACNEN           | ABEN             | ABNEN              | AAEN             | AANEN         |  |  |  |

| bit 7         |                                                                                          |                                                   |                 |                  |                    | L                | bit 0         |  |  |  |

| Legend:       |                                                                                          |                                                   |                 |                  |                    |                  |               |  |  |  |

| R = Readable  | e bit                                                                                    | W = Writable                                      | bit             | U = Unimple      | mented bit, read   | as '0'           |               |  |  |  |

| -n = Value at | POR                                                                                      | '1' = Bit is se                                   | t               | '0' = Bit is cle | eared              | x = Bit is unk   | nown          |  |  |  |

| bit 15        |                                                                                          |                                                   | Jacking Soloot  | hito             |                    |                  |               |  |  |  |

| DIL 15        | •                                                                                        | or Low-Level N<br>king (blanking)                 | •               |                  | erted ('0') compa  | rator signal fro | m propagating |  |  |  |

|               |                                                                                          |                                                   |                 |                  | erted ('1') compar |                  |               |  |  |  |

| bit 14        | Unimpleme                                                                                | nted: Read as                                     | '0'             |                  |                    |                  |               |  |  |  |

| bit 13        | OCEN: OR                                                                                 | Gate C Input Ei                                   | nable bit       |                  |                    |                  |               |  |  |  |

|               |                                                                                          | onnected to OF<br>ot connected to                 | <b>Q</b>        |                  |                    |                  |               |  |  |  |

| bit 12        | OCNEN: OF                                                                                | R Gate C Input                                    | Inverted Enable | e bit            |                    |                  |               |  |  |  |

|               |                                                                                          | MCI is connect<br>MCI is not con                  |                 |                  |                    |                  |               |  |  |  |

| bit 11        | OBEN: OR                                                                                 | DBEN: OR Gate B Input Enable bit                  |                 |                  |                    |                  |               |  |  |  |

|               |                                                                                          | onnected to OF of connected to                    | •               |                  |                    |                  |               |  |  |  |

| bit 10        | OBNEN: OF                                                                                | R Gate B Input I                                  | nverted Enable  | e bit            |                    |                  |               |  |  |  |

|               |                                                                                          | MBI is connect<br>MBI is not con                  | •               | jate             |                    |                  |               |  |  |  |

| bit 9         | OAEN: OR                                                                                 | Gate A Input Er                                   | nable bit       |                  |                    |                  |               |  |  |  |

|               |                                                                                          | onnected to OF of connected to                    |                 |                  |                    |                  |               |  |  |  |

| bit 8         | OANEN: OF                                                                                | R Gate A Input I                                  | nverted Enable  | e bit            |                    |                  |               |  |  |  |

|               |                                                                                          | MAI is connect<br>MAI is not con                  | -               | jate             |                    |                  |               |  |  |  |

| bit 7         | 1 = Inverted                                                                             | Gate Output II<br>ANDI is conne<br>ANDI is not co | cted to OR gate | е                |                    |                  |               |  |  |  |

| bit 6         | 1 = ANDI is                                                                              | Gate Output E<br>connected to O<br>not connected  | R gate          |                  |                    |                  |               |  |  |  |

| bit 5         | ACEN: AND                                                                                | Gate C Input E                                    | Enable bit      |                  |                    |                  |               |  |  |  |

|               |                                                                                          | onnected to AN ot connected to                    |                 |                  |                    |                  |               |  |  |  |

| bit 4         | ACNEN: AN                                                                                | ID Gate C Input                                   | Inverted Enab   | ole bit          |                    |                  |               |  |  |  |

|               | ACNEN: AND Gate C Input Inverted Enable bit<br>1 = Inverted MCI is connected to AND gate |                                                   |                 |                  |                    |                  |               |  |  |  |

|               |                                                                                          | MCI IS CONNEC                                     | leu lo AND yai  | e                |                    |                  |               |  |  |  |

## 26.1 Writing to the RTCC Timer

Note: To allow the RTCC module to be clocked by the secondary crystal oscillator, the Secondary Oscillator Enable (LPOSCEN) bit in the Oscillator Control (OSCCON<1>) register must be set. For further details, refer to Section 7. "Oscillator" (DS70580) in the "dsPIC33E/PIC24E Family Reference Manual".

The user application can configure the time and calendar by writing the desired seconds, minutes, hours, weekday, date, month and year to the RTCC registers. Under normal operation, writes to the RTCC Timer registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To write to the RTCC register, the RTCWREN bit (RCFGCAL<13>) must be set. Setting the RTCWREN bit allows writes to the RTCC registers. Conversely, clearing the RTCWREN bit prevents writes.

To set the RTCWREN bit, the following procedure must be executed. The RTCWREN bit can be cleared at any time:

- 1. Write 0x55 to NVMKEY.

- 2. Write 0xAA to NVMKEY.

- 3. Set the RTCWREN bit using a single-cycle instruction.

The RTCC module is enabled by setting the RTCEN bit (RCFGCAL<15>). To set or clear the RTCEN bit, the RTCWREN bit (RCFGCAL<13>) must be set.

If the entire clock (hours, minutes and seconds) needs to be corrected, it is recommended that the RTCC module should be disabled to avoid coincidental write operation when the timer increments. Therefore, it stops the clock from counting while writing to the RTCC Timer register.

## 26.2 RTCC Resources

Many useful resources related to RTCC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter |

|-------|-----------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                               |

|       | http://www.microchip.com/wwwproducts/                                                   |

|       | Devices.aspx?dDocName=en554310                                                          |

### 26.2.1 KEY RESOURCES

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS70584) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related "dsPIC33E/PIC24E Family Reference Manual" Sections

- Development Tools