Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 122                                                                             |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 12K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 144-LQFP                                                                        |

| Supplier Device Package    | 144-LQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep256gu814t-i-pl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>TABLE 4-21</b> : | QEI2 REGISTER MAP FOR dsPIC33EPXXX(MC/MU)806/810/814 DEVICES ONLY |

|---------------------|-------------------------------------------------------------------|

|---------------------|-------------------------------------------------------------------|

| File Name     | Addr. | Bit 15 | Bit 14            | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8      | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------|-------|--------|-------------------|----------|------------|------------|----------|----------|------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| QEI2CON       | 05C0  | QEIEN  | —                 | QEISIDL  |            | PIMOD<2:0> |          | IMV<     | <1:0>      | —      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI2IOC       | 05C2  | QCAPEN | FLTREN            |          | QFDIV<2:0> |            | OUTFN    | VC<1:0>  | SWPAB      | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| QEI2STAT      | 05C4  | _      | —                 | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN   | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS2CNTL      | 05C6  |        |                   |          |            |            |          |          | POSCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| POS2CNTH      | 05C8  |        |                   |          |            |            |          |          | POSCNT<31: | 16>    |        |            |          |        |        |        |        | 0000          |

| POS2HLD       | 05CA  |        |                   |          |            |            |          |          | POSHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| VEL2CNT       | 05CC  |        |                   |          |            |            |          |          | VELCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INT2TMRL      | 05CE  |        |                   |          |            |            |          |          | INTTMR<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INT2TMRH      | 05D0  |        | INTTMR<31:16> 000 |          |            |            |          |          |            | 0000   |        |            |          |        |        |        |        |               |

| INT2HLDL      | 05D2  |        |                   |          |            |            |          |          | INTHLD<15  | 0>     |        |            |          |        |        |        |        | 0000          |

| INT2HLDH      | 05D4  |        |                   |          |            |            |          |          | INTHLD<31: | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX2CNTL     | 05D6  |        |                   |          |            |            |          |          | INDXCNT<15 | 5:0>   |        |            |          |        |        |        |        | 0000          |

| INDX2CNTH     | 05D8  |        |                   |          |            |            |          | I        | NDXCNT<31  | :16>   |        |            |          |        |        |        |        | 0000          |

| INDX2HLD      | 05DA  |        |                   |          |            |            |          |          | INDXHLD<15 | 5:0>   |        |            |          |        |        |        |        | 0000          |

| QEI2GECL      | 05DC  |        |                   |          |            |            |          |          | QEIGEC<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI2ICL       | 05DC  |        |                   |          |            |            |          |          | QEIIC<15:0 | )>     |        |            |          |        |        |        |        | 0000          |

| QEI2GECH      | 05DE  |        | QEIGEC<31:16> 000 |          |            |            |          |          |            | 0000   |        |            |          |        |        |        |        |               |

| QEI2ICH       | 05DE  |        | QEIIC<31:16> 000  |          |            |            |          |          | 0000       |        |        |            |          |        |        |        |        |               |

| QEI2LECL      | 05E0  |        | QEILEC<15:0> 0001 |          |            |            |          |          | 0000       |        |        |            |          |        |        |        |        |               |

| QEI2LECH      | 05E2  |        |                   |          |            |            |          |          | QEILEC<31: | 16>    |        |            |          |        |        |        |        | 0000          |

| a successful. |       |        |                   |          |            |            |          |          |            |        |        |            |          |        |        |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-24: SPI1, SPI2, SPI3 and SPI4 REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                                         | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7      | Bit 6       | Bit 5  | Bit 4               | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|------------------------------------------------|---------|--------|--------|--------|------------|-------------|------------|-------------|--------|---------------------|------------|-------|--------|--------|---------------|

| SPI1STAT  | 0240  | SPIEN  | —                                              | SPISIDL | —      | —      | Ś      | SPIBEC<2:0 | >           | SRMPT      | SPIROV      | SRXMPT |                     | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1  | 0242  |        | —                                              | —       | DISSCK | DISSDO | MODE16 | SMP        | CKE         | SSEN       | CKP         | MSTEN  | SPRE<2:0> PPRE<1:0> |            |       | 0000   |        |               |

| SPI1CON2  | 0244  | FRMEN  | SPIFSD                                         | FRMPOL  | _      | —      | _      | —          | —           | —          | —           | —      | —                   | —          | —     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF   | 0248  |        | SPIx Transmit and Receive Buffer Register 000  |         |        |        |        |            |             |            | 0000        |        |                     |            |       |        |        |               |

| SPI2STAT  | 0260  | SPIEN  | -                                              | SPISIDL | —      | —      | 5      | SPIBEC<2:0 | >           | SRMPT      | SPIROV      | SRXMPT |                     | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1  | 0262  |        | —                                              | —       | DISSCK | DISSDO | MODE16 | SMP        | CKE         | SSEN       | CKP         | MSTEN  |                     | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2  | 0264  | FRMEN  | SPIFSD                                         | FRMPOL  | —      | _      | —      | —          | —           | —          | —           | —      | —                   | —          | —     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF   | 0268  |        |                                                |         |        |        |        | SPIx Tra   | nsmit and R | eceive Buf | fer Registe | r      |                     |            |       |        |        | 0000          |

| SPI3STAT  | 02A0  | SPIEN  | -                                              | SPISIDL | —      | —      | 5      | SPIBEC<2:0 | >           | SRMPT      | SPIROV      | SRXMPT |                     | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI3CON1  | 02A2  |        | —                                              | —       | DISSCK | DISSDO | MODE16 | SMP        | CKE         | SSEN       | CKP         | MSTEN  |                     | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI3CON2  | 02A4  | FRMEN  | SPIFSD                                         | FRMPOL  | —      | _      | —      | —          | —           | —          | —           | —      | —                   | —          | —     | FRMDLY | SPIBEN | 0000          |

| SPI3BUF   | 02A8  |        |                                                |         |        |        |        | SPIx Tra   | nsmit and R | eceive Buf | fer Registe | r      |                     |            |       |        |        | 0000          |

| SPI4STAT  | 02C0  | SPIEN  | -                                              | SPISIDL | —      | —      | 5      | SPIBEC<2:0 | >           | SRMPT      | SPIROV      | SRXMPT |                     | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI4CON1  | 02C2  |        | —                                              | —       | DISSCK | DISSDO | MODE16 | SMP        | CKE         | SSEN       | CKP         | MSTEN  |                     | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI4CON2  | 02C4  | FRMEN  | SPIFSD                                         | FRMPOL  | _      | —      | _      | _          | _           | —          | —           | —      | _                   | —          | _     | FRMDLY | SPIBEN | 0000          |

| SPI4BUF   | 02C8  |        | SPIx Transmit and Receive Buffer Register 0000 |         |        |        |        |            |             |            |             |        |                     |            |       |        |        |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE        | 4-41. | FER    |              |            |        | INFUT      | REGIST |       |       | 5610331   |            |            |            |            | 1     | 1     | 1     |               |

|--------------|-------|--------|--------------|------------|--------|------------|--------|-------|-------|-----------|------------|------------|------------|------------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13     | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7     | Bit 6      | Bit 5      | Bit 4      | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0       | 06A0  | _      |              |            |        | INT1R<6:0  | >      |       |       | _         | —          | -          | —          | —          | —     | —     | —     | 0000          |

| RPINR1       | 06A2  | —      |              | INT3R<6:0> |        |            |        |       |       | —         | INT2R<6:0> |            |            |            |       | 0000  |       |               |

| RPINR2       | 06A4  | —      | —            |            |        |            |        |       | —     | —         |            |            |            | INT4R<6:0> | >     |       |       | 0000          |

| RPINR3       | 06A6  | —      |              |            |        | T3CKR<6:0  | >      |       |       | —         |            |            |            | T2CKR<6:0  | >     |       |       | 0000          |

| RPINR4       | 06A8  | —      |              |            |        | T5CKR<6:0  | >      |       |       | —         |            |            |            | T4CKR<6:0  | >     |       |       | 0000          |

| RPINR5       | 06AA  | —      |              |            |        | T7CKR<6:0  | >      |       |       | —         |            |            |            | T6CKR<6:0  | >     |       |       | 0000          |

| RPINR6       | 06AC  | —      |              |            |        | T9CKR<6:0  | >      |       |       | —         |            |            |            | T8CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  | —      |              |            |        | IC2R<6:0>  |        |       |       | —         |            |            |            | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  | —      |              |            |        | IC4R<6:0>  |        |       |       | —         |            |            |            | IC3R<6:0>  |       |       |       | 0000          |

| RPINR9       | 06B2  | —      |              |            |        | IC6R<6:0>  |        |       |       | —         |            |            |            | IC5R<6:0>  |       |       |       | 0000          |

| RPINR10      | 06B4  | —      |              |            |        | IC8R<6:0>  |        |       |       | —         |            |            |            | IC7R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  | —      |              |            |        | OCFBR<6:0  | )>     |       |       | —         |            |            |            | OCFAR<6:0  | >     |       |       | 0000          |

| RPINR12      | 06B8  | —      |              |            |        | FLT2R<6:0  | >      |       |       | —         |            |            |            | FLT1R<6:0> | >     |       |       | 0000          |

| RPINR13      | 06BA  | _      |              |            |        | FLT4R<6:0  | >      |       |       | —         |            |            |            | FLT3R<6:0> | >     |       |       | 0000          |

| RPINR14      | 06BC  | _      | QEB1R<6:0> — |            |        |            |        |       | (     | QEA1R<6:0 | >          |            |            | 0000       |       |       |       |               |

| RPINR15      | 06BE  | —      |              |            | F      | IOME1R<6:  | 0>     |       |       | —         |            |            | I          | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR16      | 06C0  | —      |              |            |        | QEB2R<6:0  | >      |       |       | —         |            |            |            | QEA2R<6:0  | >     |       |       | 0000          |

| RPINR17      | 06C2  | —      |              |            | F      | IOME2R<6:  | 0>     |       |       | —         |            |            | I          | NDX2R<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  | —      |              |            | ι      | J1CTSR<6:  | 0>     |       |       | —         | U1RXR<6:0> |            |            |            |       | 0000  |       |               |

| RPINR19      | 06C6  | —      |              |            | ι      | J2CTSR<6:  | 0>     |       |       | —         | U2RXR<6:0> |            |            |            |       |       | 0000  |               |

| RPINR20      | 06C8  | —      |              |            |        | SCK1R<6:0  | >      |       |       | —         |            |            |            | SDI1R<6:0> | >     |       |       | 0000          |

| RPINR21      | 06CA  | —      | —            | —          | —      |            | —      | _     | —     | —         |            |            |            | SS1R<6:0>  |       |       |       | 0000          |

| RPINR23      | 06CE  | —      | —            | —          | —      |            | —      | _     | —     | —         |            |            |            | SS2R<6:0>  |       |       |       | 0000          |

| RPINR24      | 06D0  | —      |              |            | 1      | CSCKR<6:0  | )>     |       | _     | —         |            |            |            | CSDIR<6:0  | >     |       |       | 0000          |

| RPINR25      | 06D2  | —      | —            | _          | _      |            | —      | —     | —     | —         |            |            | С          | OFSINR<6:  | 0>    |       |       | 0000          |

| RPINR26      | 06D4  | —      |              |            |        | C2RXR<6:0  | >      |       |       | —         |            |            |            | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR27      | 06D6  | —      |              |            | ι      | J3CTSR<6:  | 0>     |       |       | —         |            |            |            | U3RXR<6:0  | >     |       |       | 0000          |

| RPINR28      | 06D8  | _      | U4CTSR<6:0>  |            |        |            |        | —     |       |           |            | U4RXR<6:0  | >          |            |       | 0000  |       |               |

| RPINR29      | 06DA  | _      | SCK3R<6:0>   |            |        |            |        | —     |       |           |            | SDI3R<6:0> | >          |            |       | 0000  |       |               |

| RPINR30      | 06DC  | _      |              |            |        |            |        | _     |       |           |            | SS3R<6:0>  |            |            |       | 0000  |       |               |

| RPINR31      | 06DE  | _      |              | SCK4R<6:0> |        |            |        |       | _     |           |            |            | SDI4R<6:0> | >          |       |       | 0000  |               |

| RPINR32      | 06E0  | _      | _            | —          |        | _          | —      | —     | —     | _         | SS4R<6:0>  |            |            |            |       | 0000  |       |               |

| RPINR33      | 06E2  | _      |              |            |        | IC10R<6:03 | >      |       |       | _         | IC9R<6:0>  |            |            |            | 0000  |       |       |               |

| RPINR34      | 06E4  | _      |              |            |        | IC12R<6:0  | >      |       |       | _         |            |            |            | IC11R<6:0> | ·     |       |       | 0000          |

## TABLE 4-41: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMU810 DEVICES ONLY

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0     | R-0   |

|--------|-------|-------|--------|---------------------|-----|---------|-------|

| VAR    | —     | US<   | 1:0>   | EDT                 |     | DL<2:0> |       |

| bit 15 |       |       |        |                     |     |         | bit 8 |

|        |       |       |        |                     |     |         |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0   | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND     | IF    |

| bit 7  |       |       |        |                     |     |         | bit 0 |

|        |       |       |        |                     |     |         |       |

## REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15 | VAR: Variable Exception Processing Latency Control bit |

|--------|--------------------------------------------------------|

|        | 1 = Variable exception processing is enabled           |

|        | 0 = Fixed exception processing is enabled              |

|        | (2)                                                    |

#### bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

## Note 1: For complete register details, see Register 3-2: "CORCON: Core Control Register".

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

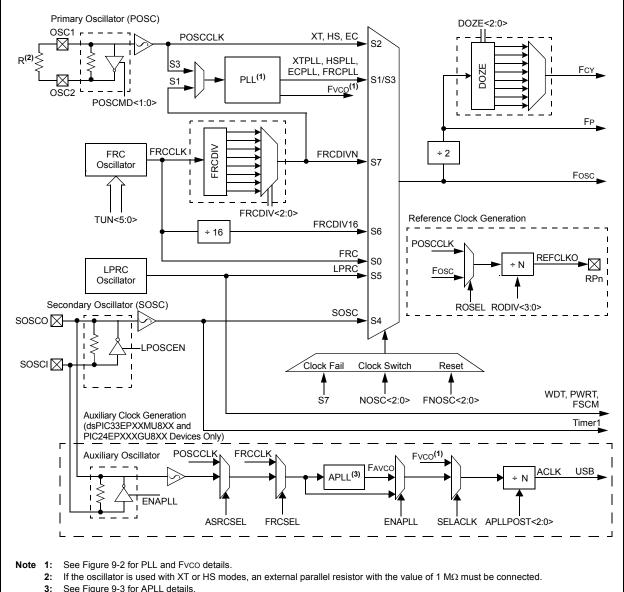

#### FIGURE 9-1: **OSCILLATOR SYSTEM DIAGRAM**

3: See Figure 9-3 for APLL details.

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| <b>REGISTER 9-4</b> : | 0301              | UN. FRC 030                                           | JILLATOR      | IUNING REG       | ISIER /          |                 |        |

|-----------------------|-------------------|-------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|

| U-0                   | U-0               | U-0                                                   | U-0           | U-0              | U-0              | U-0             | U-0    |

| _                     |                   | —                                                     | —             | —                | _                | —               |        |

| bit 15                |                   |                                                       |               |                  |                  |                 | bit 8  |

| U-0                   | U-0               | R/W-0                                                 | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|                       | _                 |                                                       |               |                  | 1<5:0>           | 1011 0          | 1000 0 |

| bit 7                 |                   |                                                       |               |                  |                  |                 | bit 0  |

|                       |                   |                                                       |               |                  |                  |                 |        |

| Legend:               |                   |                                                       |               |                  |                  |                 |        |

| R = Readable bit      |                   | W = Writable I                                        | oit           | U = Unimpler     | nented bit, read | as '0'          |        |

| -n = Value at POF     | २                 | '1' = Bit is set                                      |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15-6 <b>U</b>     | nimplomon         | ted: Read as '0                                       | `,            |                  |                  |                 |        |

|                       | -                 |                                                       |               |                  |                  |                 |        |

| 0                     | 11111 <b>= Ce</b> | RC Oscillator T<br>enter frequency<br>enter frequency | + 11.625% (8  |                  |                  |                 |        |

| •                     |                   |                                                       |               |                  |                  |                 |        |

| •                     |                   |                                                       |               |                  |                  |                 |        |

| •                     |                   |                                                       |               |                  |                  |                 |        |

| 0                     | 00000 <b>= Ce</b> | enter frequency<br>enter frequency                    | (7.37 MHz nd  | ominal)          |                  |                 |        |

| 1                     | 11111 <b>= Ce</b> | enter frequency                                       | – 0.375% (7.3 | 345 MHz)         |                  |                 |        |

| •                     |                   |                                                       |               |                  |                  |                 |        |

| •                     |                   |                                                       |               |                  |                  |                 |        |

|                       |                   | enter frequency<br>enter frequency                    |               |                  |                  |                 |        |

## REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER<sup>(1)</sup>

| REGISTER 9-6: | ACLKDIV3: AUXILIARY CLOCK DIVISOR REGISTER 3 <sup>(1,2)</sup> |

|---------------|---------------------------------------------------------------|

|---------------|---------------------------------------------------------------|

| U-0             | U-0 | U-0              | U-0 | U-0              | U-0                           | U-0          | U-0   |  |

|-----------------|-----|------------------|-----|------------------|-------------------------------|--------------|-------|--|

| —               | —   | —                | _   | —                | —                             | —            | —     |  |

| bit 15          |     |                  |     |                  |                               |              | bit 8 |  |

|                 |     |                  |     |                  |                               |              |       |  |

| U-0             | U-0 | U-0              | U-0 | U-0              | R/W-0                         | R/W-0        | R/W-0 |  |

|                 | —   | —                | _   | _                | /                             | APLLDIV<2:0> |       |  |

| bit 7           | •   |                  |     |                  |                               |              | bit 0 |  |

|                 |     |                  |     |                  |                               |              |       |  |

| Legend:         |     |                  |     |                  |                               |              |       |  |

| R = Readable I  | bit | W = Writable     | bit | U = Unimpler     | nented bit, read              | as '0'       |       |  |

| -n = Value at P | OR  | '1' = Bit is set |     | '0' = Bit is cle | is cleared x = Bit is unknown |              |       |  |

bit 15-3 Unimplemented: Read as '0'

| bit 2-0 | APLLDIV<2:0>: PLL Feedback Divisor bits (PLL Multiplier Ratio) |

|---------|----------------------------------------------------------------|

|         | 111 <b>= 24</b>                                                |

|         | 110 <b>= 21</b>                                                |

|         | 101 <b>= 20</b>                                                |

|         | 100 = 19                                                       |

|         | 011 <b>= 18</b>                                                |

|         | 010 = 17                                                       |

|         | 001 = 16                                                       |

|         | 000 = 15 (default)                                             |

Note 1: This register resets only on a Power-on Reset (POR).

2: This register is only available on dsPIC33EPXXXMU8XX and PIC24EPXXXGU8XX devices.

| U-0                | R/W-0                                      | R/W-0                                                                                    | R/W-0                                          | R/W-0             | R/W-0         | R/W-0            | R/W-0 |

|--------------------|--------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|---------------|------------------|-------|

| _                  |                                            |                                                                                          |                                                | INT3R<6:0>        |               |                  |       |

| bit 15             | ŀ                                          |                                                                                          |                                                |                   |               |                  | bit 8 |

|                    |                                            |                                                                                          |                                                |                   |               |                  |       |

| U-0                | R/W-0                                      | R/W-0                                                                                    | R/W-0                                          | R/W-0             | R/W-0         | R/W-0            | R/W-0 |

| _                  |                                            |                                                                                          |                                                | INT2R<6:0>        |               |                  |       |

| bit 7              |                                            |                                                                                          |                                                |                   |               |                  | bit C |

|                    |                                            |                                                                                          |                                                |                   |               |                  |       |

| Legend:            |                                            |                                                                                          |                                                |                   |               |                  |       |

| R = Readab         |                                            | W = Writable                                                                             |                                                | U = Unimplem      |               |                  |       |

| -n = Value a       | at POR                                     | '1' = Bit is set                                                                         |                                                | '0' = Bit is clea | ared          | x = Bit is unkr  | nown  |

|                    | INT3R<6:0>:<br>(see Table 11               | I-2 for input pin                                                                        | al Interrupt 3 (<br>selection num              | ,                 | rresponding I | RPn/RPIn Pin bit | ts    |

| bit 15<br>bit 14-8 | INT3R<6:0><br>(see Table 11<br>1111111 = I | : Assign Externa<br>I-2 for input pin<br>nput tied to RP <sup>-</sup><br>nput tied to CM | al Interrupt 3 (<br>selection num<br>127<br>P1 | ,                 | rresponding I | RPn/RPIn Pin bil | ts    |

|                    | INT3R<6:0><br>(see Table 11<br>1111111 = I | : Assign Externa<br>I-2 for input pin<br>nput tied to RP1                                | al Interrupt 3 (<br>selection num<br>127<br>P1 | ,                 | rresponding I | RPn/RPIn Pin bil | is    |

### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0                | R/W-0                                        | R/W-0                                                                                 | R/W-0                                       | R/W-0                     | R/W-0           | R/W-0           | R/W-0 |

|--------------------|----------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------|---------------------------|-----------------|-----------------|-------|

| —                  |                                              |                                                                                       |                                             | IC14R<6:0>                |                 |                 |       |

| bit 15             |                                              |                                                                                       |                                             |                           |                 |                 | bit 8 |

|                    |                                              |                                                                                       |                                             |                           |                 |                 |       |

| U-0                | R/W-0                                        | R/W-0                                                                                 | R/W-0                                       | R/W-0                     | R/W-0           | R/W-0           | R/W-0 |

| _                  |                                              |                                                                                       |                                             | IC13R<6:0>                |                 |                 |       |

| bit 7              |                                              |                                                                                       |                                             |                           |                 |                 | bit ( |

|                    |                                              |                                                                                       |                                             |                           |                 |                 |       |

| Legend:            |                                              |                                                                                       |                                             |                           |                 |                 |       |

| R = Readab         | ole bit                                      | W = Writable                                                                          | bit                                         | U = Unimplem              | nented bit, rea | id as '0'       |       |

| -n = Value a       | at POR                                       | '1' = Bit is set                                                                      |                                             | '0' = Bit is clea         | ared            | x = Bit is unkr | iown  |

|                    | IC14R<6:0>:<br>(see Table 11                 | -2 for input pin                                                                      | apture 14 (IC<br>selection num              | 14) to the Corre<br>bers) | esponding RP    | n/RPIn Pin bits |       |

| bit 15<br>bit 14-8 | IC14R<6:0>:<br>(see Table 11<br>1111111 = Ir | Assign Input C                                                                        | apture 14 (IC<br>selection num<br>127<br>P1 |                           | esponding RP    | n/RPIn Pin bits |       |

|                    | IC14R<6:0>:<br>(see Table 11<br>1111111 = Ir | Assign Input C<br>-2 for input pin<br>nput tied to RP <sup>2</sup><br>nput tied to CM | apture 14 (IC<br>selection num<br>127<br>P1 |                           | esponding RP    | n/RPIn Pin bits |       |

## REGISTER 11-35: RPINR35: PERIPHERAL PIN SELECT INPUT REGISTER 35

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

## REGISTER 11-53: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP101 | IR<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| —     | —   |       |       | RP100 | 0R<5:0> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 13-8 | RP101R<5:0>: Peripheral Output Function is Assigned to RP101Output Pin bits |

|----------|-----------------------------------------------------------------------------|

|          | (see Table 11-3 for peripheral function numbers)                            |

| bit 7-6  | Unimplemented: Read as '0'                                                  |

bit 5-0 **RP100R<5:0>:** Peripheral Output Function is Assigned to RP100 Output Pin bits (see Table 11-3 for peripheral function numbers)

## REGISTER 11-54: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | -   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| —     | —   |       |       | RP102 | 2R<5:0> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP102R<5:0>:** Peripheral Output Function is Assigned to RP102 Output Pin bits (see Table 11-3 for peripheral function numbers)

## 13.2 Timerx/y Control Registers

| R/W-0        | U-0                                      | R/W-0            | U-0             | U-0               | U-0            | U-0                | U-0 |

|--------------|------------------------------------------|------------------|-----------------|-------------------|----------------|--------------------|-----|

| TON          |                                          | TSIDL            | _               |                   | —              | _                  | _   |

| pit 15       |                                          |                  |                 |                   |                |                    | bit |

| U-0          | R/W-0                                    | R/W-0            | R/W-0           | R/W-0             | U-0            | R/W-0              | U-0 |

| 0-0          | TGATE                                    | I                | S<1:0>          | T32               | 0-0            | TCS <sup>(1)</sup> | 0-0 |

| <br>bit 7    | IGAIE                                    | ICKE             | 5~1.0~          | 132               | _              | 10307              |     |

|              |                                          |                  |                 |                   |                |                    | bit |

| Legend:      |                                          |                  |                 |                   |                |                    |     |

| R = Readable | e bit                                    | W = Writable     | bit             | U = Unimplem      | ented bit, rea | d as '0'           |     |

| n = Value at | POR                                      | '1' = Bit is set |                 | '0' = Bit is clea | ared           | x = Bit is unkno   | own |

| bit 15       | TON: Timerx                              | On hit           |                 |                   |                |                    |     |

| 511 15       | When T32 = $2$                           |                  |                 |                   |                |                    |     |

|              | 1 = Starts 32-                           |                  |                 |                   |                |                    |     |

|              | 0 = Stops 32-                            |                  |                 |                   |                |                    |     |

|              | <u>When T32 = 0</u>                      |                  |                 |                   |                |                    |     |

|              | 1 = Starts 16-<br>0 = Stops 16-          |                  |                 |                   |                |                    |     |

| oit 14       | -                                        | ted: Read as '   | 0'              |                   |                |                    |     |

| bit 13       | TSIDL: Timer                             | x Stop in Idle I | Node bit        |                   |                |                    |     |

|              |                                          |                  |                 | device enters lo  | lle mode       |                    |     |

|              |                                          | s module opera   |                 | ode               |                |                    |     |

| bit 12-7     | -                                        | ted: Read as '   |                 |                   |                |                    |     |

| bit 6        |                                          | erx Gated Time   | Accumulatio     | n Enable bit      |                |                    |     |

|              | When TCS =<br>This bit is igno           |                  |                 |                   |                |                    |     |

|              | When TCS =                               |                  |                 |                   |                |                    |     |

|              | 1 = Gated tim                            | e accumulatio    |                 |                   |                |                    |     |

|              |                                          | e accumulatio    |                 |                   |                |                    |     |

| bit 5-4      |                                          | : Timerx Input   | Clock Presca    | le Select bits    |                |                    |     |

|              | 11 = 1:256<br>10 = 1:64                  |                  |                 |                   |                |                    |     |

|              | 10 = 1:64<br>01 = 1:8                    |                  |                 |                   |                |                    |     |

|              | 00 = 1:1                                 |                  |                 |                   |                |                    |     |

| bit 3        | <b>T32:</b> 32-Bit Timer Mode Select bit |                  |                 |                   |                |                    |     |

|              | 1 = Timerx an                            | d Timery form    | a single 32-b   | it timer          |                |                    |     |

|              | 0 = Timerx ar                            | id Timery act a  | is two 16-bit t | mers              |                |                    |     |

| bit 2        | •                                        | ted: Read as '   |                 |                   |                |                    |     |

| bit 1        |                                          | Clock Source S   |                 |                   |                |                    |     |

|              | 1 = External o<br>0 = Internal cl        | lock from TxC    | K pin (on the   | rising edge)      |                |                    |     |

|              |                                          |                  |                 |                   |                |                    |     |

## REGISTER 13-1: TxCON: (T2CON, T4CON, T6CON OR T8CON) CONTROL REGISTER

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

## 16.1 PWM Resources

Many useful resources related to the high-speed PWM are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en554310              |

#### 16.1.1 KEY RESOURCES

- Section 11. "High-Speed PWM" (DS70645) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

| U-0          | U-0                                                                                                                          | U-0                                                                                                                              | U-0                                                                                                          | R/W-0                                                              | R/W-0           | R/W-0           | R/W-0   |

|--------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------|-----------------|---------|

| _            | _                                                                                                                            | _                                                                                                                                | _                                                                                                            | BLANKSEL<3:0>                                                      |                 |                 |         |

| bit 15       |                                                                                                                              | ·                                                                                                                                |                                                                                                              |                                                                    |                 |                 | bit 8   |

| U-0          | U-0                                                                                                                          | R/W-0                                                                                                                            | R/W-0                                                                                                        | R/W-0                                                              | R/W-0           | R/W-0           | R/W-0   |

| —            | —                                                                                                                            |                                                                                                                                  | CHOPS                                                                                                        | SEL<3:0>                                                           |                 | CHOPHEN         | CHOPLEN |

| bit 7        |                                                                                                                              |                                                                                                                                  |                                                                                                              |                                                                    |                 |                 | bit     |

| Legend:      |                                                                                                                              |                                                                                                                                  |                                                                                                              |                                                                    |                 |                 |         |

| R = Readab   | le bit                                                                                                                       | W = Writable                                                                                                                     | bit                                                                                                          | U = Unimplen                                                       | nented bit, rea | ad as '0'       |         |

| -n = Value a | t POR                                                                                                                        | '1' = Bit is set                                                                                                                 |                                                                                                              | '0' = Bit is clea                                                  | ared            | x = Bit is unki | nown    |

| bit 15-12    | Unimpleme                                                                                                                    | nted: Read as '                                                                                                                  | ∩'                                                                                                           |                                                                    |                 |                 |         |

| bit 11-8     | •                                                                                                                            | .<3:0>: PWM St                                                                                                                   |                                                                                                              | rce Select bits                                                    |                 |                 |         |

|              | 0101 = PWM<br>0100 = PWM<br>0011 = PWM<br>0010 = PWM<br>0001 = PWM                                                           | M6H selected as<br>M5H selected as<br>M4H selected as<br>M3H selected as<br>M2H selected as<br>M1H selected as<br>state blanking | s state blank s<br>s state blank s<br>s state blank s<br>s state blank s                                     | ource<br>ource<br>ource<br>ource                                   |                 |                 |         |

| bit 7-6      | Unimpleme                                                                                                                    | nted: Read as '                                                                                                                  | 0'                                                                                                           |                                                                    |                 |                 |         |

| bit 5-2      |                                                                                                                              | 3:0>: PWM Cho                                                                                                                    | -                                                                                                            |                                                                    |                 |                 |         |

|              | 1001 = Rese<br>1000 = Rese<br>0111 = PWM<br>0110 = PWM<br>0101 = PWM<br>0100 = PWM<br>0011 = PWM<br>0010 = PWM<br>0010 = PWM |                                                                                                                                  | CHOP clock<br>CHOP clock<br>CHOP clock<br>CHOP clock<br>CHOP clock<br>CHOP clock<br>CHOP clock<br>CHOP clock | source<br>source<br>source<br>source<br>source<br>source<br>source |                 | outputs.        |         |

| bit 1        | 1 = PWMxH                                                                                                                    | PWMxH Output<br>chopping functi<br>chopping functi                                                                               | on is enabled                                                                                                |                                                                    |                 |                 |         |

| bit 0        |                                                                                                                              | PWMxL Output                                                                                                                     |                                                                                                              |                                                                    |                 |                 |         |

#### .....

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| U-0           | U-0           | R-0                                   | R-0              | R-0              | R-0                | R-0             | R-0   |

|---------------|---------------|---------------------------------------|------------------|------------------|--------------------|-----------------|-------|

| —             |               | TXBO                                  | TXBP             | RXBP             | TXWAR              | RXWAR           | EWARN |

| bit 15        |               |                                       |                  |                  |                    |                 | bit   |

| R/C-0         | R/C-0         | R/C-0                                 | U-0              | R/C-0            | R/C-0              | R/C-0           | R/C-0 |

| IVRIF         | WAKIF         | ERRIF                                 | _                | FIFOIF           | RBOVIF             | RBIF            | TBIF  |

| bit 7         |               |                                       |                  |                  |                    |                 | bit ( |

| Legend:       |               | C = Writable                          | hit but only '0' | can be writte    | n to clear the bit | ŀ               |       |

| R = Readabl   | e bit         | W = Writable                          |                  |                  | mented bit, read   |                 |       |

| -n = Value at | POR           | '1' = Bit is set                      |                  | '0' = Bit is cle |                    | x = Bit is unkr | nown  |

|               |               |                                       | o.1              |                  |                    |                 |       |

| bit 15-14     | -             | nted: Read as '                       |                  | - :4             |                    |                 |       |

| bit 13        |               | smitter in Error<br>ter is in Bus Off |                  | JIL              |                    |                 |       |

|               |               | ter is not in Bus                     |                  |                  |                    |                 |       |

| bit 12        | TXBP: Trans   | smitter in Error                      | State Bus Pas    | sive bit         |                    |                 |       |

|               | 1 = Transmit  | ter is in Bus Pa                      | ssive state      |                  |                    |                 |       |

|               |               | ter is not in Bus                     |                  |                  |                    |                 |       |

| bit 11        |               | eiver in Error Sta                    |                  | e bit            |                    |                 |       |

|               |               | r is in Bus Pass<br>r is not in Bus P |                  |                  |                    |                 |       |

| bit 10        |               | Insmitter in Erro                     |                  | na hit           |                    |                 |       |

|               |               | ter is in Error W                     |                  | ig sit           |                    |                 |       |

|               |               | ter is not in Erro                    | •                | te               |                    |                 |       |

| bit 9         | RXWAR: Re     | ceiver in Error                       | State Warning    | bit              |                    |                 |       |

|               |               | is in Error War<br>is not in Error '  |                  |                  |                    |                 |       |

| bit 8         | EWARN: Tra    | ansmitter or Red                      | eiver in Error   | State Warning    | bit                |                 |       |

|               |               | ter or Receiver<br>ter or Receiver    |                  | Ų                |                    |                 |       |

| bit 7         |               | d Message Inte                        |                  |                  | ,                  |                 |       |

|               | 1 = Interrupt | Request has of<br>Request has no      | ccurred          |                  |                    |                 |       |

| bit 6         |               | Wake-up Activ                         |                  | aq bit           |                    |                 |       |

|               |               | Request has o                         |                  |                  |                    |                 |       |

|               | 0 = Interrupt | Request has n                         | ot occurred      |                  |                    |                 |       |

| bit 5         |               |                                       |                  | ources in CxIN   | TF<13:8> regis     | ter)            |       |

|               |               | Request has o                         |                  |                  |                    |                 |       |

| bit 4         | -             | Request has ne<br>nted: Read as '     |                  |                  |                    |                 |       |

| bit 3         | -             | D Almost Full In                      |                  | t                |                    |                 |       |

|               | 1 = Interrupt | Request has o                         | ccurred          |                  |                    |                 |       |

| <b>h</b> # 0  | •             | Request has no                        |                  | l- 14            |                    |                 |       |

| bit 2         |               | Buffer Overflor                       |                  | g dit            |                    |                 |       |

|               |               | Request has of<br>Request has no      |                  |                  |                    |                 |       |

| bit 1         | -             | uffer Interrupt Fl                    |                  |                  |                    |                 |       |

|               |               | Request has o                         | -                |                  |                    |                 |       |

|               | -             | Request has no                        |                  |                  |                    |                 |       |

| bit 0         |               | ffer Interrupt Fla                    | -                |                  |                    |                 |       |

|               |               | Request has o                         |                  |                  |                    |                 |       |

| REGISTER 21-22: | CxRXFUL1: ECANx RECEIVE BUFFER FULL REGISTER 1 |

|-----------------|------------------------------------------------|

|                 |                                                |

| r       |         |         |         |         |         |        |        |

|---------|---------|---------|---------|---------|---------|--------|--------|

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

| RXFUL7  | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1 | RXFUL0 |

| bit 7   |         |         |         |         |         |        | bit 0  |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                      |                    |  |  |  |

|-------------------|----------------------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0'            |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0                                                                 | R/C-0                             | R/C-0   | R/C-0             | R/C-0                              | R/C-0   | R/C-0   | R/C-0   |

|-----------------------------------------------------------------------|-----------------------------------|---------|-------------------|------------------------------------|---------|---------|---------|

| RXFUL31                                                               | RXFUL30                           | RXFUL29 | RXFUL28           | RXFUL27                            | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15                                                                |                                   |         |                   |                                    |         |         | bit 8   |

|                                                                       |                                   |         |                   |                                    |         |         |         |

| R/C-0                                                                 | R/C-0                             | R/C-0   | R/C-0             | R/C-0                              | R/C-0   | R/C-0   | R/C-0   |

| RXFUL23                                                               | RXFUL22                           | RXFUL21 | RXFUL20           | RXFUL19                            | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7                                                                 | •                                 |         |                   | •                                  |         | •       | bit 0   |

|                                                                       |                                   |         |                   |                                    |         |         |         |

| Legend: C = Writable bit, but only '0                                 |                                   |         | oit, but only '0' | 0' can be written to clear the bit |         |         |         |

| R = Readable                                                          | R = Readable bit W = Writable bit |         | bit               | U = Unimplemented bit, read as '0' |         |         |         |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is ur |                                   |         | x = Bit is unkr   | nown                               |         |         |         |

bit 15-0 **RXFUL<31:16>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

## 21.5 ECAN Message Buffers

ECAN Message Buffers are part of DMA RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the DMA RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

## BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0    | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-----|-----|-------|-------|-------|-------|-------|

| —      | —   | —   | SID10 | SID9  | SID8  | SID7  | SID6  |

| bit 15 |     |     |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID5  | SID4  | SID3  | SID2  | SID1  | SID0  | SRR   | IDE   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                    |

|-----------|-----------------------------------------------|

| bit 12-2  | SID<10:0>: Standard Identifier bits           |

| bit 1     | SRR: Substitute Remote Request bit            |

|           | When TXIDE = 0:                               |

|           | 1 = Message will request remote transmission  |

|           | 0 = Normal message                            |

|           | When TXIDE = 1:                               |

|           | The SRR bit must be set to '1'.               |

| bit 0     | IDE: Extended Identifier bit                  |

|           | 1 = Message will transmit extended identifier |

0 = Message will transmit standard identifier

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0    | U-0   | U-0   | U-0   | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | EID17 | EID16 | EID15 | EID14 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| EID13  | EID12 | EID11 | EID10 | EID9  | EID8  | EID7  | EID6  |

bit 7

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

bit 0

## 22.4 USB Control Registers

## REGISTER 22-1: UxOTGSTAT: USB OTG STATUS REGISTER

| U-0            | U-0                                                                                                                                                                                       | U-0               | U-0               | U-0               | U-0            | U-0            | U-0      |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|----------------|----------------|----------|--|--|

| _              | —                                                                                                                                                                                         | —                 | _                 | —                 | —              | _              | _        |  |  |

| bit 15         |                                                                                                                                                                                           |                   |                   |                   |                | •              | bit 8    |  |  |

|                |                                                                                                                                                                                           |                   |                   |                   |                |                |          |  |  |

| R-0, HSC       | U-0                                                                                                                                                                                       | R-0, HSC          | U-0               | R-0, HSC          | R-0, HSC       | U-0            | R-0, HSC |  |  |

| ID             | —                                                                                                                                                                                         | LSTATE            |                   | SESVD             | SESEND         |                | VBUSVD   |  |  |

| bit 7          |                                                                                                                                                                                           |                   |                   |                   |                |                | bit (    |  |  |

| Legend:        |                                                                                                                                                                                           | U = Unimplem      | ented bit, read   | d as '0'          |                |                |          |  |  |

| R = Readabl    | e bit                                                                                                                                                                                     | W = Writable b    |                   | HSC = Hardw       | are Settable/C | learable bit   |          |  |  |

| -n = Value at  | POR                                                                                                                                                                                       | '1' = Bit is set  |                   | '0' = Bit is clea | ared           | x = Bit is unk | nown     |  |  |

|                |                                                                                                                                                                                           |                   |                   |                   |                |                |          |  |  |

| bit 15-8       | Unimplemen                                                                                                                                                                                | ted: Read as '0   | ,                 |                   |                |                |          |  |  |

| bit 7          | ID: ID Pin State Indicator bit                                                                                                                                                            |                   |                   |                   |                |                |          |  |  |

|                | 1 = No cable is attached or a Type B plug has been plugged into the USB receptacle                                                                                                        |                   |                   |                   |                |                |          |  |  |