Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 512KB (170K x 24)                                                               |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 24K x 16                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x10/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

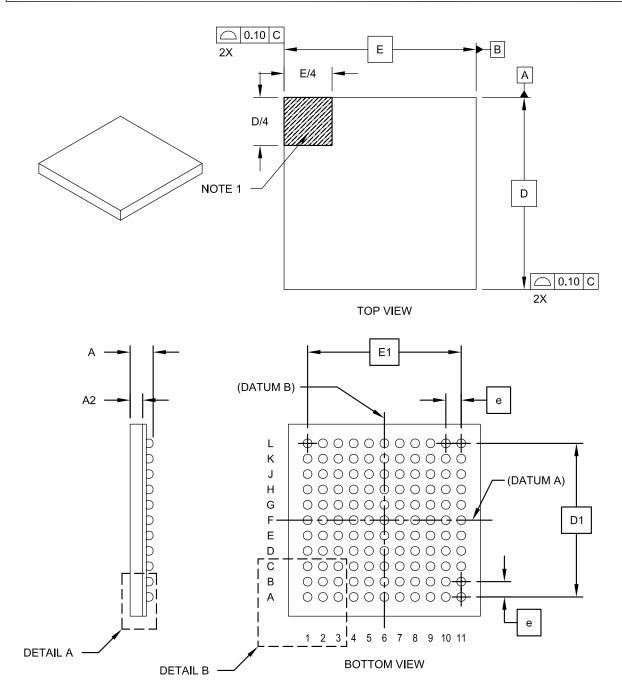

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gp806t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

|     |          |          |           | GU810<br>GU810 |           |          |           |           |           |           |              |

|-----|----------|----------|-----------|----------------|-----------|----------|-----------|-----------|-----------|-----------|--------------|

|     | 1        | 2        | 3         | 4              | 5         | 6        | 7         | 8         | 9         | 10        | 11           |

| ۹ ( | O<br>RE4 | O<br>RE3 | RG13      | O<br>RE0       | RG0       | RF1      | O<br>Vdd  | NC        | RD12      | RD2       | RD1          |

| 3   | NC       | RG15     | O<br>RE2  | O<br>RE1       | O<br>RA7  | RF0      | O<br>VCAP | RD5       | RD3       | ⊖<br>Vss  | O<br>RC14    |

| c   | O<br>RE6 | O<br>VDD | RG12      | RG14           | O<br>RA6  | NC       | O<br>RD7  | RD4       | NC        | O<br>RC13 | <b>R</b> D11 |

| D   | O<br>RC1 | O<br>RE7 | O<br>RE5  | NC             | NC        | NC       | O<br>RD6  | RD13      | RD0       | NC        | RD10         |

| E   | O<br>RC4 | C<br>RC3 | O<br>RG6  | O<br>RC2       | NC        | RG1      | NC        | RA15      | RD8       | RD9       | RA14         |

| F   | MCLR     | O<br>RG8 | O<br>RG9  | O<br>RG7       | ⊖<br>Vss  | NC       | NC        |           | O<br>RC12 | ⊖<br>Vss  | O<br>RC15    |

| G   | O<br>RE8 | O<br>RE9 | RA0       | NC             | O<br>Vdd  | ⊖<br>Vss | ⊖<br>Vss  | NC        | RA5       | RA3       | RA4          |

| н   | O<br>RB5 | O<br>RB4 | NC        | NC             | NC        | O<br>Vdd | NC        | VBUS      | UUSB3V3   | O<br>RG2  | RA2          |

| J   | O<br>RB3 | O<br>RB2 | O<br>RB7  | O<br>AVDD      | O<br>RB11 | RA1      | O<br>RB12 | NC        | NC        | RF8       | O<br>RG3     |

| к   | O<br>RB1 | O<br>RB0 | O<br>RA10 | O<br>RB8       | NC        | RF12     | O<br>RB14 |           | RD15      | RF3       | RF2          |

| L   | O<br>RB6 | O<br>RA9 | )<br>AVss | O<br>RB9       | O<br>RB10 | RF13     | O<br>RB13 | O<br>RB15 | RD14      | RF4       | RF5          |

# Pin Diagrams (Continued)

# TABLE 4-40: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMU814 DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13       | Bit 12 | Bit 11   | Bit 10 | Bit 9 | Bit 8 | Bit 7      | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------------|--------------|--------|----------|--------|-------|-------|------------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR35      | 06E6  | _      |              | IC14R<6:0>   |        |          |        |       |       | —          | IC13R<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR36      | 06E8  | -      |              | IC16R<6:0>   |        |          |        |       |       | _          | IC15R<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR37      | 06EA  | _      | SYNCI1R<6:0> |              |        |          |        |       | _     | OCFCR<6:0> |              |       |       |            |       | 0000  |       |               |

| RPINR38      | 06EC  | _      |              | DTCMP1R<6:0> |        |          |        |       |       | —          | SYNCI2R<6:0> |       |       |            |       |       | 0000  |               |

| RPINR39      | 06EE  |        |              | DTCMP3R<6:0> |        |          |        |       |       | _          |              |       | D     | TCMP2R<6:  | 0>    |       |       | 0000          |

| RPINR40      | 06F0  |        |              |              | D      | TCMP5R<6 | 0>     |       |       | _          |              |       | D     | TCMP4R<6:  | 0>    |       |       | 0000          |

| RPINR41      | 06F2  |        |              | DTCMP7R<6:0> |        |          |        |       |       | _          | DTCMP6R<6:0> |       |       |            |       |       | 0000  |               |

| RPINR42      | 06F4  |        |              | FLT6R<6:0>   |        |          |        |       |       | _          | FLT5R<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR43      | 06F6  | _      | _            | _            | _      | _        | _      | _     | _     | —          |              |       |       | FLT7R<6:0> | •     |       |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## REGISTER 5-1: NVMCON: NON-VOLATILE MEMORY (NVM) CONTROL REGISTER

| REGISTER 5            | 5-1: NVMCC                                 | ON: NON-VO                        | DLATILE MEI            | MORY (NVM            | ) CONTROL            | REGISTER               |                      |

|-----------------------|--------------------------------------------|-----------------------------------|------------------------|----------------------|----------------------|------------------------|----------------------|

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                       | R/W-0 <sup>(1)</sup>              | R/W-0                  | U-0                  | U-0                  | U-0                    | U-0                  |

| WR                    | WREN                                       | WRERR                             | NVMSIDL <sup>(2)</sup> | —                    | —                    | _                      | —                    |

| bit 15                |                                            |                                   |                        |                      |                      |                        | bit 8                |

|                       |                                            |                                   |                        | (4)                  | (4)                  | (4)                    | (4)                  |

| U-0                   | U-0                                        | U-0                               | U-0                    | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup> |

|                       | _                                          |                                   |                        |                      | NVMOP                | <3:0> <sup>(3,4)</sup> |                      |

| bit 7                 |                                            |                                   |                        |                      |                      |                        | bit (                |

| Legend:               |                                            | <u> </u>                          | ble Only bit           |                      |                      |                        |                      |

| R = Readable          | hit                                        | W = Writab                        | -                      |                      | mented bit, read     | l as 'O'               |                      |

| -n = Value at         |                                            | '1' = Bit is s                    |                        | '0' = Bit is cle     |                      | x = Bit is unkr        |                      |

|                       | FOR                                        | 1 - DIL 15 3                      | 501                    |                      | aleu                 |                        | IUWII                |

| bit 15                | WR: Write Cor                              | ntrol bit <sup>(1)</sup>          |                        |                      |                      |                        |                      |

|                       | 1 = Initiates a                            | Flash memo                        | ry program or          | erase operation      | on; the operatic     | on is self-timed       | and the bit is       |

|                       | cleared by                                 | / hardware or                     | ice operation is       | s complete           |                      |                        |                      |

|                       | 0 = Program o                              | -                                 | ation is comple        | te and inactive      | 9                    |                        |                      |

| bit 14                | WREN: Write I                              |                                   |                        |                      |                      |                        |                      |

|                       | 1 = Enables F                              |                                   |                        |                      |                      |                        |                      |

| 1 11 4 0              | 0 = Inhibits Fla                           |                                   | •                      | าร                   |                      |                        |                      |

| bit 13                | WRERR: Write                               | •                                 | •                      |                      |                      |                        | 1                    |

|                       |                                            | er program or<br>t attempt of the |                        | e attempt or te      | rmination has oc     | curred (bit is se      | et automaticali      |

|                       | 0 = The progra                             | •                                 | ,                      | leted normally       | /                    |                        |                      |

| bit 12                | NVMSIDL: NV                                |                                   |                        | -                    |                      |                        |                      |

|                       | 1 = Flash volta                            |                                   |                        | d-by mode du         | ring Idle mode       |                        |                      |

|                       | 0 = Flash volta                            | age regulator                     | is active during       | g Idle mode          | -                    |                        |                      |

| bit 11-4              | Unimplement                                | ed: Read as '                     | 0'                     |                      |                      |                        |                      |

| bit 3-0               | NVMOP<3:0>                                 | : NVM Operat                      | tion Select bits       | (1,3,4)              |                      |                        |                      |

|                       | 1111 = Reserv                              | ved                               |                        |                      |                      |                        |                      |

|                       | 1110 = Reserv                              |                                   |                        |                      |                      |                        |                      |

|                       | 1101 = Bulk e<br>1100 = Reserv             |                                   | program Flash          | memory               |                      |                        |                      |

|                       | 1011 = Reserv                              |                                   |                        |                      |                      |                        |                      |

|                       | 1010 = Bulk e                              |                                   | program Flash          | n memory             |                      |                        |                      |

|                       | 0011 <b>= Memo</b>                         |                                   |                        |                      |                      |                        |                      |

|                       | 0010 <b>= Memo</b>                         |                                   |                        | )                    |                      |                        |                      |

|                       | 0001 <b>= Memo</b><br>0000 <b>= Progra</b> |                                   |                        |                      |                      |                        |                      |

|                       |                                            | a cingio O                        |                        |                      |                      |                        |                      |

| Note 1: Th            | ese bits can only                          | be reset on a                     | POR.                   |                      |                      |                        |                      |

|                       | his bit is set, upo<br>erational.          | n exiting Idle                    | mode, there is         | a delay (Tvre        | G) before Flash      | memory beco            | mes                  |

| 3: All                | other combinatio                           | ons of NVMO                       | ><3:0> are unii        | mplemented.          |                      |                        |                      |

- **3:** All other combinations of NVMOP<3:0> are unimplemented.

- 4: Execution of the PWRSAV instruction is ignored while any of the NVM operations are in progress.

- 5: Two adjacent words are programmed during execution of this operation.

| R/W-0<br>CHEN<br>bit 15 | R/W-0<br>SIZE                                                                                                                                                          | R/W-0<br>DIR                       | R/W-0           | R/W-0             | U-0              | U-0              | U-0          |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|-------------------|------------------|------------------|--------------|--|--|--|--|

| -                       | SIZE                                                                                                                                                                   |                                    |                 |                   |                  |                  |              |  |  |  |  |

| bit 15                  |                                                                                                                                                                        | DIR                                | HALF            | NULLW             |                  |                  | _            |  |  |  |  |

|                         |                                                                                                                                                                        |                                    |                 |                   |                  |                  | bit 8        |  |  |  |  |

| U-0                     | U-0                                                                                                                                                                    | R/W-0                              | R/W-0           | U-0               | U-0              | R/W-0            | R/W-0        |  |  |  |  |

| _                       | _                                                                                                                                                                      | AMODE                              | E<1:0>          | —                 | _                | MODE             | <1:0>        |  |  |  |  |

| bit 7                   |                                                                                                                                                                        |                                    |                 |                   |                  |                  | bit C        |  |  |  |  |

|                         |                                                                                                                                                                        |                                    |                 |                   |                  |                  |              |  |  |  |  |

| Legend:                 | .:.                                                                                                                                                                    |                                    | L :4            |                   | <b></b>          |                  |              |  |  |  |  |

| R = Readable I          |                                                                                                                                                                        | W = Writable                       | DIT             | -                 | nented bit, read |                  |              |  |  |  |  |

| -n = Value at P         | OR                                                                                                                                                                     | '1' = Bit is set                   |                 | '0' = Bit is clea | ared             | x = Bit is unkn  | own          |  |  |  |  |

| bit 15                  | CHEN: Chanr                                                                                                                                                            | nel Enable bit                     |                 |                   |                  |                  |              |  |  |  |  |

|                         | 1 = Channel                                                                                                                                                            | is enabled                         |                 |                   |                  |                  |              |  |  |  |  |

|                         | 0 = Channel                                                                                                                                                            | is disabled                        |                 |                   |                  |                  |              |  |  |  |  |

| bit 14                  | SIZE: Data Tr                                                                                                                                                          | ansfer Size bit                    |                 |                   |                  |                  |              |  |  |  |  |

|                         | 1 = Byte                                                                                                                                                               |                                    |                 |                   |                  |                  |              |  |  |  |  |

|                         | 0 = Word                                                                                                                                                               |                                    |                 |                   |                  |                  |              |  |  |  |  |

| bit 13                  | <b>DIR</b> : Transfer Direction bit (source/destination bus select)                                                                                                    |                                    |                 |                   |                  |                  |              |  |  |  |  |

|                         | <ul> <li>1 = Reads from DPSRAM (or RAM) address, writes to peripheral address</li> <li>0 = Reads from peripheral address, writes to DPSRAM (or RAM) address</li> </ul> |                                    |                 |                   |                  |                  |              |  |  |  |  |

|                         | 0 = Reads fro                                                                                                                                                          | om peripheral a                    | ddress, write   | s to DPSRAM (     | or RAM) addre    | SS               |              |  |  |  |  |

| bit 12                  | HALF: Block Transfer Interrupt Select bit                                                                                                                              |                                    |                 |                   |                  |                  |              |  |  |  |  |

|                         | 1 = Initiates in                                                                                                                                                       | nterrupt when h                    | half of the dat | a has been mo     | ved              |                  |              |  |  |  |  |

|                         | 0 = Initiates in                                                                                                                                                       | nterrupt when a                    | all of the data | has been move     | ed               |                  |              |  |  |  |  |

| bit 11                  | NULLW: Null Data Peripheral Write Mode Select bit                                                                                                                      |                                    |                 |                   |                  |                  |              |  |  |  |  |

|                         |                                                                                                                                                                        |                                    | eral in additio | on to DPSRAM      | (or RAM) write   | (DIR bit must al | so be clear) |  |  |  |  |

|                         | 0 = Normal o                                                                                                                                                           | -                                  |                 |                   |                  |                  |              |  |  |  |  |

| bit 10-6                | •                                                                                                                                                                      | ted: Read as '                     |                 |                   |                  |                  |              |  |  |  |  |

| bit 5-4                 | AMODE<1:0>: DMA Channel Addressing Mode Select bits                                                                                                                    |                                    |                 |                   |                  |                  |              |  |  |  |  |

|                         | 11 = Reserved                                                                                                                                                          |                                    |                 |                   |                  |                  |              |  |  |  |  |

|                         | 10 = Peripheral Indirect Addressing mode                                                                                                                               |                                    |                 |                   |                  |                  |              |  |  |  |  |

|                         | 01 = Register Indirect without Post-Increment mode<br>00 = Register Indirect with Post-Increment mode                                                                  |                                    |                 |                   |                  |                  |              |  |  |  |  |

| bit 3-2                 | -                                                                                                                                                                      | ted: Read as '                     |                 | it mode           |                  |                  |              |  |  |  |  |

| bit 1-0                 | -                                                                                                                                                                      |                                    |                 | odo Soloot hito   |                  |                  |              |  |  |  |  |

| DIL 1-0                 |                                                                                                                                                                        |                                    |                 | ode Select bits   |                  | the each DNAA h  | (ffor)       |  |  |  |  |

|                         |                                                                                                                                                                        | ous, Ping-Pong n<br>ous, Ping-Pong |                 |                   | k transfer from  | /to each DMA b   | uner)        |  |  |  |  |

|                         |                                                                                                                                                                        | ot, Ping-Pong n                    |                 |                   |                  |                  |              |  |  |  |  |

|                         | <u></u> 010 010                                                                                                                                                        |                                    |                 |                   |                  |                  |              |  |  |  |  |

#### REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup> (CONTINUED)

| bit 3 | <b>CF:</b> Clock Fail Detect bit (read/clear by application)<br>1 = FSCM has detected clock failure<br>0 = FSCM has not detected clock failure |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Unimplemented: Read as '0'                                                                                                                     |

| bit 1 | LPOSCEN: Secondary (LP) Oscillator Enable bit                                                                                                  |

|       | <ul><li>1 = Enables Secondary Oscillator</li><li>0 = Disables Secondary Oscillator</li></ul>                                                   |

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **Section 7. "Oscillator"** (DS70580) in the *"dsPIC33E/PIC24E Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- **3:** This register resets only on a Power-on Reset (POR).

## REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit |

|-------|---------------------------------------------------|

|       | 1 = Output Compare 4 module is disabled           |

|       | 0 = Output Compare 4 module is enabled            |

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit |

|       | 1 = Output Compare 3 module is disabled           |

|       | 0 = Output Compare 3 module is enabled            |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit |

|       | 1 = Output Compare 2 module is disabled           |

|       | 0 = Output Compare 2 module is enabled            |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit |

|       | 1 = Output Compare 1 module is disabled           |

|       |                                                   |

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |  |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|--|

| _               |       | —                |       | —                | _                | —               | —     |  |

| bit 15          |       |                  |       |                  |                  |                 | bit 8 |  |

|                 |       |                  |       |                  |                  |                 |       |  |

| U-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |

| —               |       | FLT7R<6:0>       |       |                  |                  |                 |       |  |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |  |

|                 |       |                  |       |                  |                  |                 |       |  |

| Legend:         |       |                  |       |                  |                  |                 |       |  |

| R = Readable b  | pit   | W = Writable I   | oit   | U = Unimpler     | nented bit, read | as '0'          |       |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |

| •               |       |                  |       |                  |                  |                 |       |  |

bit 15-7Unimplemented: Read as '0'bit 6-0FLT7R<6:0>: Assign PWM Fault 7 to 1

bit 6-0

FLT7R<6:0>: Assign PWM Fault 7 to the Corresponding RPn/RPIn Pin bits (see Table 11-2 for input pin selection numbers)

1111111 = Input tied to RP127

.

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

REGISTER 11-44: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0                         | U-0 | R/W-0        | R/W-0      | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |  |  |

|-----------------------------|-----|--------------|------------|------------------------------------|--------|--------------------|-------|--|--|

| _                           | _   |              |            | RP65F                              | ₹<5:0> |                    |       |  |  |

| bit 15                      |     |              |            |                                    |        |                    | bit 8 |  |  |

| U-0                         | U-0 | R/W-0        | R/W-0      | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |  |  |

| _                           | -   |              | RP64R<5:0> |                                    |        |                    |       |  |  |

| bit 7                       |     |              |            |                                    |        |                    | bit 0 |  |  |

| Legend:                     |     |              |            |                                    |        |                    |       |  |  |

| R = Readable                | bit | W = Writable | bit        | U = Unimplemented bit, read as '0' |        |                    |       |  |  |

| -n = Value at POR '1' = Bit |     |              |            | '0' = Bit is clea                  | red    | x = Bit is unknown |       |  |  |

bit 13-8**RP65R<5:0>:** Peripheral Output Function is Assigned to RP65 Output Pin bits<br/>(see Table 11-3 for peripheral function numbers)bit 7-6**Unimplemented:** Read as '0'

bit 5-0 **RP64R<5:0>:** Peripheral Output Function is Assigned to RP64 Output Pin bits (see Table 11-3 for peripheral function numbers)

## 15.2 Output Compare Control Registers

#### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0 | R/W-0       | R/W-0 | R/W-0  | R/W-0  |

|--------|-----|--------|-------|-------------|-------|--------|--------|

|        | —   | OCSIDL |       | OCTSEL<2:0> | >     | ENFLTC | ENFLTB |

| bit 15 |     |        |       |             |       |        | bit 8  |

| R/W-0  | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0    | R/W-0 | R/W-0    | R/W-0 |

|--------|------------|------------|------------|----------|-------|----------|-------|

| ENFLTA | OCFLTC     | OCFLTB     | OCFLTA     | TRIGMODE |       | OCM<2:0> |       |

| bit 7  |            |            |            |          |       |          | bit 0 |

| Legend:           | HCS = Hardware Settable/Clearable bit |                                    |                    |  |  |

|-------------------|---------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-14    | Unimplemented: Read as '0'                                                                                                                          |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13       | OCSIDL: Stop Output Compare x in Idle Mode Control bit                                                                                              |

|              | 1 = Output Compare x Halts in CPU Idle mode                                                                                                         |

|              | 0 = Output Compare x continues to operate in CPU Idle mode                                                                                          |

| bit 12-10    | OCTSEL<2:0>: Output Compare x Clock Select bits                                                                                                     |

|              | 111 = Peripheral clock (FP)                                                                                                                         |

|              | 110 = Reserved                                                                                                                                      |

|              | 101 = Reserved<br>100 = Clock source of T1CLK is the clock source of OCx (only the synchronous clock is supported)                                  |

|              | 011 = Clock source of T5CLK is the clock source of OCx (only the synchronous clock is supported)                                                    |

|              | 010 = Clock source of T4CLK is the clock source of OCx                                                                                              |

|              | 001 = Clock source of T3CLK is the clock source of OCx                                                                                              |

|              | 000 = Clock source of T2CLK is the clock source of OCx                                                                                              |

| bit 9        | ENFLTC: Fault C Input Enable bit                                                                                                                    |

|              | 1 = Output Compare Fault C input (OCFC) is enabled                                                                                                  |

| <b>b</b> # 0 | 0 = Output Compare Fault C input (OCFC) is disabled                                                                                                 |

| bit 8        | ENFLTB: Fault B Input Enable bit                                                                                                                    |

|              | <ul> <li>1 = Output Compare Fault B input (OCFB) is enabled</li> <li>0 = Output Compare Fault B input (OCFB) is disabled</li> </ul>                 |

| bit 7        | ENFLTA: Fault A Input Enable bit                                                                                                                    |

| Sit 7        | 1 = Output Compare Fault A input (OCFA) is enabled                                                                                                  |

|              | 0 = Output Compare Fault A input (OCFA) is disabled                                                                                                 |

| bit 6        | OCFLTC: PWM Fault C Condition Status bit                                                                                                            |

|              | 1 = PWM Fault C condition on OCFC pin has occurred                                                                                                  |

|              | 0 = No PWM Fault C condition on OCFC pin has occurred                                                                                               |

| bit 5        | OCFLTB: PWM Fault B Condition Status bit                                                                                                            |

|              | 1 = PWM Fault B condition on OCFB pin has occurred                                                                                                  |

|              | 0 = No PWM Fault B condition on OCFB pin has occurred                                                                                               |

| bit 4        | OCFLTA: PWM Fault A Condition Status bit                                                                                                            |

|              | <ul> <li>1 = PWM Fault A condition on OCFA pin has occurred</li> <li>0 = No PWM Fault A condition on OCFA pin has occurred</li> </ul>               |

| h# 2         | · ·                                                                                                                                                 |

| bit 3        | <b>TRIGMODE:</b> Trigger Status Mode Select bit                                                                                                     |

|              | <ul> <li>1 = TRIGSTAT (OCxCON2&lt;6&gt;) is cleared when OCxRS = OCxTMR or in software</li> <li>0 = TRIGSTAT is cleared only by software</li> </ul> |

|              |                                                                                                                                                     |

|              |                                                                                                                                                     |

Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

#### REGISTER 16-1: PTCON: PWM TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup>                                                                                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 111 = Reserved                                                                                                                                                                  |

|         | •                                                                                                                                                                               |

|         | •                                                                                                                                                                               |

|         | •                                                                                                                                                                               |

|         | 010 = Reserved<br>001 = SYNCI2<br>000 = SYNCI1                                                                                                                                  |

| bit 3-0 | SEVTPS<3:0>: PWM Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                             |

|         | 1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event                                                                                   |

|         | •                                                                                                                                                                               |

|         | •                                                                                                                                                                               |

|         | •                                                                                                                                                                               |

|         | 0001 = 1:2 Postscaler generates Special Event Trigger on every second compare match event<br>0000 = 1:1 Postscaler generates Special Event Trigger on every compare match event |

**Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCIx feature, the user application must program the Period register with a value that is slightly larger than the expected period of the external synchronization input signal.

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

#### REGISTER 16-6: STCON2: PWM SECONDARY CLOCK DIVIDER SELECT REGISTER 2

| U-0                               | U-0 | U-0              | U-0 | U-0                                | U-0                                 | U-0                         | U-0   |  |

|-----------------------------------|-----|------------------|-----|------------------------------------|-------------------------------------|-----------------------------|-------|--|

| —                                 | -   | —                |     | _                                  | —                                   | —                           | —     |  |

| bit 15                            |     |                  |     |                                    |                                     |                             | bit 8 |  |

|                                   |     |                  |     |                                    |                                     |                             |       |  |

| U-0                               | U-0 | U-0              | U-0 | U-0                                | R/W-0                               | R/W-0                       | R/W-0 |  |

| _                                 | —   | _                | _   |                                    | P                                   | PCLKDIV<2:0> <sup>(1)</sup> |       |  |

| bit 7                             |     |                  |     |                                    |                                     |                             | bit 0 |  |

|                                   |     |                  |     |                                    |                                     |                             |       |  |

| Legend:                           |     |                  |     |                                    |                                     |                             |       |  |

| R = Readable bit W = Writable bit |     |                  |     | U = Unimplemented bit, read as '0' |                                     |                             |       |  |

| -n = Value at P                   | OR  | '1' = Bit is set |     | '0' = Bit is cle                   | = Bit is cleared x = Bit is unknown |                             |       |  |

bit 15-3 Unimplemented: Read as '0'

bit 2-0 PCLKDIV<2:0>: PWM Input Clock Prescaler (Divider) Select bits<sup>(1)</sup>

- 111 = Reserved 110 = Divide-by-64

- 101 = Divide-by-32

- 100 = Divide-by-32

- 011 = Divide-by-8

- 010 = Divide by 0

- 001 = Divide-by-2

- 000 = Divide-by-1, maximum PWM timing resolution (power-on default)

- **Note 1:** These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

#### **REGISTER 16-7:** STPER: SECONDARY MASTER TIME BASE PERIOD REGISTER<sup>(1)</sup>

| R/W-1                                                                | R/W-1 | R/W-1 | R/W-1 | R/W-1   | R/W-1 | R/W-1           | R/W-1 |

|----------------------------------------------------------------------|-------|-------|-------|---------|-------|-----------------|-------|

|                                                                      |       |       | STPE  | R<15:8> |       |                 |       |

| bit 15                                                               |       |       |       |         |       |                 | bit 8 |

| R/W-1                                                                | R/W-1 | R/W-1 | R/W-1 | R/W-1   | R/W-0 | R/W-0           | R/W-0 |

|                                                                      |       |       |       | R<7:0>  |       |                 |       |

| bit 7                                                                |       |       |       |         |       |                 | bit 0 |

|                                                                      |       |       |       |         |       |                 |       |

| Legend:                                                              |       |       |       |         |       |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       |         |       |                 |       |

| -n = Value at POR '1' = Bit is set '0' = Bit                         |       |       |       |         | ared  | x = Bit is unkr | nown  |

bit 15-0 STPER<15:0>: Secondary Master Time Base (PMTMR) Period Value bits

## 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXX(MC/MU)8XX DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/ 810/814 and PIC24EPXXX(GP/GU)810/ 814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Quadrature Encoder Interface (QEI)" (DS70601) of the "dsPIC33E/PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- · 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- · 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High Register

- 32-Bit Position Compare Low Register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- · External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

**Note:** An 'x' used in the names of pins, control/ status bits and registers denotes a particular Quadrature Encoder Interface (QEI) module number (x = 1 or 2).

#### 17.2 QEI Control Registers

| R/W-0         | U-0                                                                                                 | R/W-0                                                                                                                       | R/W-0                                                                           | R/W-0                                                                                                            | R/W-0                                                  | R/W-0           | R/W-0                        |

|---------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------|------------------------------|

| QEIEN         |                                                                                                     | QEISIDL                                                                                                                     |                                                                                 | PIMOD<2:0>                                                                                                       | [1]                                                    | IMV<            | 1:0> <b>(2)</b>              |

| bit 15        |                                                                                                     |                                                                                                                             |                                                                                 |                                                                                                                  |                                                        |                 | bit                          |

| U-0           | R/W-0                                                                                               | R/W-0                                                                                                                       | R/W-0                                                                           | R/W-0                                                                                                            | R/W-0                                                  | R/W-0           | R/W-0                        |

| _             | 1                                                                                                   | NTDIV<2:0>(3)                                                                                                               |                                                                                 | CNTPOL                                                                                                           | GATEN                                                  | CCM             | <1:0>                        |

| bit 7         |                                                                                                     |                                                                                                                             |                                                                                 |                                                                                                                  |                                                        |                 | bit                          |

| Legend:       |                                                                                                     |                                                                                                                             |                                                                                 |                                                                                                                  |                                                        |                 |                              |

| R = Readable  | e bit                                                                                               | W = Writable I                                                                                                              | oit                                                                             | U = Unimpler                                                                                                     | mented bit, read                                       | d as '0'        |                              |

| -n = Value at | POR                                                                                                 | '1' = Bit is set                                                                                                            |                                                                                 | '0' = Bit is cle                                                                                                 | ared                                                   | x = Bit is unkr | nown                         |

| bit 14        | 0 = Module co                                                                                       | ounters are ena<br>ounters are disa<br><b>ted:</b> Read as '0                                                               | abled, but SF                                                                   | Rs can be read                                                                                                   | d or written to                                        |                 |                              |

| bit 13        | 1 = Discontine                                                                                      | I Stop in Idle M<br>ues module ope<br>s module opera                                                                        | eration when                                                                    | device enters I<br>lode                                                                                          | dle mode                                               |                 |                              |

| bit 12-10     | PIMOD<2:0>                                                                                          | Position Coun                                                                                                               | ter Initializat                                                                 | ion Mode Selec                                                                                                   | t bits <sup>(1)</sup>                                  |                 |                              |

|               | 101 = Resets<br>100 = Secon<br>registe<br>011 = First ir<br>registe<br>010 = Next ir<br>001 = Every | o Count mode for<br>the position co<br>d index event a<br>r<br>ndex event after<br>r<br>ndex input even<br>index input even | ounter when<br>fter home ev<br>er home eve<br>t initializes th<br>nt resets the | ounter<br>the position cou<br>ent initializes po<br>nt initializes po<br>ne position courter<br>position counter | osition counter<br>osition counter<br>oter with conten | with contents o | f the QEIxIC<br>of the QEIxI |

| bit 9-8       | IMV<1:0>: Ind                                                                                       | dex Match Valu                                                                                                              | e bits <sup>(2)</sup>                                                           |                                                                                                                  |                                                        |                 |                              |

|               | 10 = Index n                                                                                        | natch occurs wh<br>natch occurs wh<br>natch occurs wh                                                                       | nen QEB = 1<br>nen QEB = 0                                                      | and QEA = 0<br>and QEA = 1                                                                                       |                                                        |                 |                              |

|               |                                                                                                     | iput event uoes                                                                                                             | not ancer p                                                                     | osition counter                                                                                                  |                                                        |                 |                              |

#### REGISTER 17-1: QEIxCON: QEIx CONTROL REGISTER

- 2: When CCM = 00, and QEA and QEB values match Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

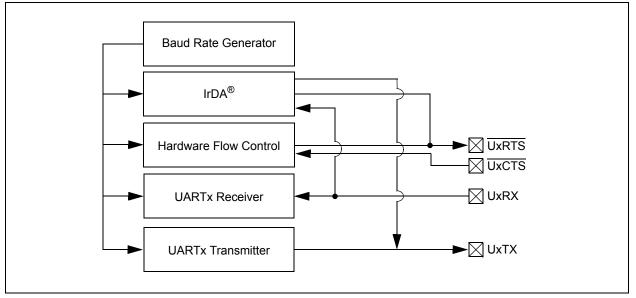

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/ 810/814 and PIC24EPXXX(GP/GU)810/ 814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "UART" (DS70582) of the "dsPIC33E/PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 family of devices contains four UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for All UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTX SIMPLIFIED BLOCK DIAGRAM

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| U-0           | U-0                                                   | U-0                                 | U-0                                 | U-0                         | U-0              | U-0             | U-0            |  |  |  |

|---------------|-------------------------------------------------------|-------------------------------------|-------------------------------------|-----------------------------|------------------|-----------------|----------------|--|--|--|

| —             | —                                                     | —                                   | _                                   | —                           |                  | —               | —              |  |  |  |

| bit 15        |                                                       |                                     |                                     |                             |                  |                 | bit 8          |  |  |  |

|               |                                                       |                                     |                                     |                             |                  |                 |                |  |  |  |

| U-0           | R-x, HSC                                              | R/W-0                               | U-0                                 |                             |                  |                 |                |  |  |  |

| _             | SE0 PKTDIS — HOSTEN <sup>(1)</sup> RESUME PPBRST USBE |                                     |                                     |                             |                  |                 |                |  |  |  |

| bit 7         |                                                       |                                     |                                     |                             |                  |                 | bit 0          |  |  |  |

|               |                                                       |                                     |                                     |                             |                  |                 |                |  |  |  |

| Legend:       |                                                       | •                                   | nented bit, read                    |                             |                  |                 |                |  |  |  |

| R = Readab    |                                                       | W = Writable                        | bit                                 | HSC = Hardwa                |                  |                 |                |  |  |  |

| -n = Value a  | It POR                                                | '1' = Bit is set                    |                                     | '0' = Bit is clea           | ared             | x = Bit is unkr | iown           |  |  |  |

|               |                                                       |                                     |                                     |                             |                  |                 |                |  |  |  |

| bit 15-7      | -                                                     | ted: Read as '                      |                                     |                             |                  |                 |                |  |  |  |

| bit 6         |                                                       | gle-Ended Zero                      | •                                   |                             |                  |                 |                |  |  |  |

|               | Ų                                                     | nded zero is act<br>e-ended zero is |                                     | B bus                       |                  |                 |                |  |  |  |

| 6.4. <i>E</i> | •                                                     |                                     |                                     |                             |                  |                 |                |  |  |  |

| bit 5         |                                                       | ket Transfer Di                     |                                     |                             |                  |                 |                |  |  |  |

|               |                                                       | n and packet pr                     |                                     | lisabled; automa<br>enabled | allcally set whe | In a SETUP LOP  | en is received |  |  |  |

| bit 4         |                                                       | ted: Read as '                      | •                                   |                             |                  |                 |                |  |  |  |

| bit 3         | •                                                     | B Host Mode E                       |                                     |                             |                  |                 |                |  |  |  |

|               |                                                       |                                     |                                     | wns on D+ and               | D- are activate  | ed in hardware  |                |  |  |  |

|               | 0 = USB hos                                           | t capability is d                   | isabled                             |                             |                  |                 |                |  |  |  |

| bit 2         | RESUME: US                                            | SB Resume Sig                       | naling Enable                       | bit                         |                  |                 |                |  |  |  |

|               |                                                       | signaling is act                    |                                     |                             |                  |                 |                |  |  |  |

|               |                                                       | signaling is dis                    |                                     |                             |                  |                 |                |  |  |  |

| bit 1         |                                                       | g-Pong Buffers                      |                                     |                             |                  |                 |                |  |  |  |

|               |                                                       |                                     | uffer Pointers t<br>ers are not res | to the EVEN but<br>et       | ffer descriptor  | banks           |                |  |  |  |

|               | 0 = Ping-Poi                                          | ng buner i onto                     |                                     | •••                         |                  |                 |                |  |  |  |

| bit 0         | C C                                                   | B Module Enabl                      |                                     |                             |                  |                 |                |  |  |  |

## REGISTER 22-5: UxCON: USB CONTROL REGISTER (DEVICE MODE)

**Note 1:** This bit should be '0' in Device mode.

| R/W-0                              | U-0                                        | U-0                                                                                                                                        | R/W-0                     | R/W-0            | R/W-0                   | R/W-0           | R/W-0 |  |  |

|------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------|-------------------------|-----------------|-------|--|--|

| CH0NB                              |                                            | _                                                                                                                                          |                           |                  | CH0SB<4:0>              | [1]             |       |  |  |

| bit 15                             |                                            |                                                                                                                                            |                           |                  |                         |                 | bit 8 |  |  |

| R/W-0                              | U-0                                        | U-0                                                                                                                                        | R/W-0                     | R/W-0            | R/W-0                   | R/W-0           | R/W-0 |  |  |

| CH0NA                              |                                            |                                                                                                                                            | CH0SA<4:0> <sup>(1)</sup> |                  |                         |                 |       |  |  |

| bit 7                              |                                            |                                                                                                                                            |                           |                  |                         |                 | bit 0 |  |  |

|                                    |                                            |                                                                                                                                            |                           |                  |                         |                 |       |  |  |

| Legend:<br>R = Readabl             | e bit                                      | W = Writable t                                                                                                                             | bit                       | U = Unimple      | mented bit, rea         | ad as '0'       |       |  |  |

| -n = Value at POR (1' = Bit is set |                                            |                                                                                                                                            |                           | '0' = Bit is cle |                         | x = Bit is unkr | nown  |  |  |

| bit 12-8<br>bit 7                  | Same definiti<br>CH0NA: Cha<br>1 = Channel | <ul> <li>Channel 0 Poi<br/>on as bits&lt;4:0&gt;.</li> <li>Innel 0 Negative</li> <li>0 negative input</li> <li>0 negative input</li> </ul> | Input Select t            |                  |                         |                 |       |  |  |

| bit 6-5                            |                                            | ited: Read as '0                                                                                                                           |                           |                  |                         |                 |       |  |  |

| bit 4-0                            | •                                          | Channel 0 Po                                                                                                                               |                           | elect for Sampl  | e A bits <sup>(1)</sup> |                 |       |  |  |

|                                    |                                            | annel 0 positive i<br>annel 0 positive i                                                                                                   |                           |                  |                         |                 |       |  |  |

|                                    | •                                          |                                                                                                                                            |                           |                  |                         |                 |       |  |  |

|                                    | •                                          |                                                                                                                                            |                           |                  |                         |                 |       |  |  |

|                                    | 00001 <b>= Cha</b>                         | annel 0 positive i<br>annel 0 positive i<br>annel 0 positive i                                                                             | nput is AN1               |                  |                         |                 |       |  |  |

#### REGISTER 23-7: ADxCHS0: ADCx INPUT CHANNEL 0 SELECT REGISTER