Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 83                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 121-TFBGA                                                                      |

| Supplier Device Package    | 121-TFBGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gu810-i-bg |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

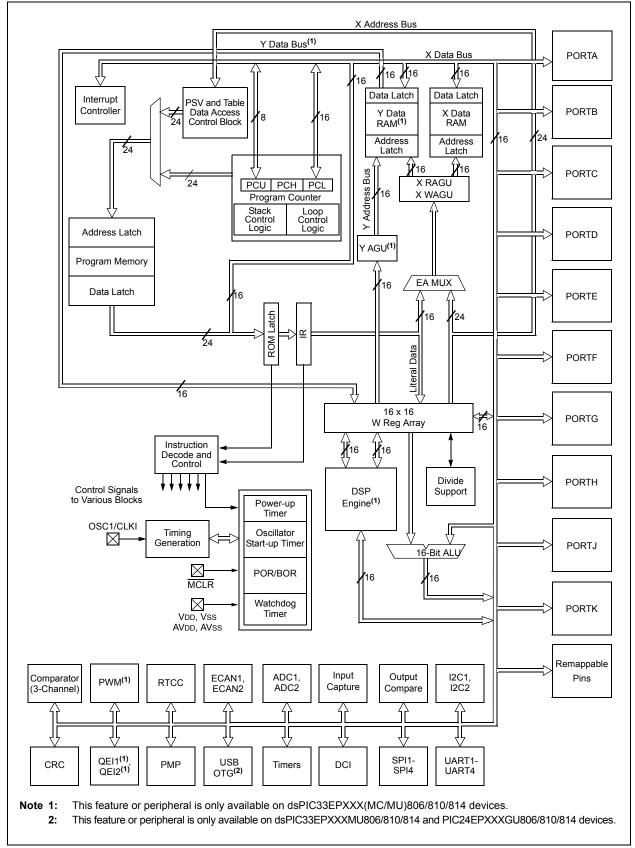

## FIGURE 3-1: dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 CPU BLOCK DIAGRAM

#### 3.5 **Programmer's Model**

The programmer's model is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, all devices in this family contain control registers for interrupts, while the dsPIC33EPXXX(GP/MC/MU)806/810/814 devices contain control registers for Modulo and Bit-reversed Addressing. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory mapped, as shown in Table 4-1.

| Register(s) Name                                      | Description                                               |

|-------------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                        | Working Register Array                                    |

| ACCA, ACCB                                            | 40-Bit DSP Accumulators                                   |

| PC                                                    | 23-Bit Program Counter                                    |

| SR                                                    | ALU and DSP Engine Status register                        |

| SPLIM                                                 | Stack Pointer Limit Value register                        |

| TBLPAG                                                | Table Memory Page Address register                        |

| DSRPAG                                                | Extended Data Space (EDS) Read Page register              |

| DSWPAG                                                | Extended Data Space (EDS) Write Page register             |

| RCOUNT                                                | REPEAT Loop Count register                                |

| DCOUNT <sup>(1)</sup>                                 | DO Loop Count register                                    |

| DOSTARTH <sup>(1,2)</sup> , DOSTARTL <sup>(1,2)</sup> | DO Loop Start Address register (High and Low)             |

| DOENDH <sup>(1)</sup> , DOENDL <sup>(1)</sup>         | DO Loop End Address register (High and Low)               |

| CORCON                                                | Contains DSP Engine, DO Loop Control and Trap Status bits |

#### TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

Note 1: This register is available on dsPIC33EPXXX(GP/MC/MU)806/810/814 devices only.

2: The DOSTARTH and DOSTARTL registers are read-only.

#### TABLE 4-55: PORTA REGISTER MAP FOR dsPIC33EPXXXMU810/814 AND PIC24EPXXXGU810/814 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|--------|--------|--------|---------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | TRISA15 | TRISA14 | _      | _      | _      | TRISA10 | TRISA9 | —     | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | C6FF          |

| PORTA        | 0E02  | RA15    | RA14    | _      | _      | _      | RA10    | RA9    | _     | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | XXXX          |

| LATA         | 0E04  | LATA15  | LATA14  | _      | _      | _      | LATA10  | LATA9  | _     | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | XXXX          |

| ODCA         | 0E06  | ODCA15  | ODCA14  | _      | _      | _      | _       | _      | _     | _      | _      | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | CNIEA15 | CNIEA14 | _      | _      | _      | CNIEA10 | CNIEA9 | _     | CNIEA7 | CNIEA6 | CNIEA5 | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | CNPUA15 | CNPUA14 | _      | _      | _      | CNPUA10 | CNPUA9 | _     | CNPUA7 | CNPUA6 | CNPUA5 | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | CNPDA15 | CNPDA14 | _      | _      | _      | CNPDA10 | CNPDA9 | _     | CNPDA7 | CNPDA6 | CNPDA5 | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | —       | _       | _      | _      | _      | ANSA10  | ANSA9  | -     | ANSA7  | ANSA6  | _      | _      | _      | _      | _      | _      | 06C0          |

Legend: x = unknown value on Reset, -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-56:PORTB REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | XXXX          |

| ODCB         | 0E16  | -       | -       | _       | _       | _       | _       | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | ANSB15  | ANSB14  | ANSB13  | ANSB12  | ANSB11  | ANSB10  | ANSB9  | ANSB8  | ANSB7  | ANSB6  | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | FFFF          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTC REGISTER MAP FOR dsPIC33EPXXXMU810/814 AND PIC24EPXXXGU810/814 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-------|---------------|

| TRISC        | 0E20  | TRISC15 | TRISC14 | TRISC13 | TRISC12 |        | _      |       | _     | _     |       |       | TRISC4 | TRISC3 | TRISC2 | TRISC1 |       | F01E          |

| PORTC        | 0E22  | RC15    | RC14    | RC13    | RC12    | _      | _      |       | —     | _     |       |       | RC4    | RC3    | RC2    | RC1    | —     | XXXX          |

| LATC         | 0E24  | LATC15  | LATC14  | LATC13  | LATC12  | _      | _      |       | —     | _     |       |       | LATC4  | LATC3  | LATC2  | LATC1  | —     | XXXX          |

| ODCC         | 0E26  | —       | _       | _       | —       | _      | _      |       | —     | _     |       |       |        |        | _      | —      | —     | 0000          |

| CNENC        | 0E28  | CNIEC15 | CNIEC14 | CNIEC13 | CNIEC12 | _      | _      |       | —     | _     |       |       | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | —     | 0000          |

| CNPUC        | 0E2A  | CNPUC15 | CNPUC14 | CNPUC13 | CNPUC12 |        | -      |       | —     |       |       |       | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | —     | 0000          |

| CNPDC        | 0E2C  | CNPDC15 | CNPDC14 | CNPDC13 | CNPDC12 | _      | _      | _     | _     | _     | _     | _     | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | —     | 0000          |

| ANSELC       | 0E2E  | —       | ANSC14  | ANSC13  | _       | _      | _      | _     | _     | _     | _     | _     | ANSC4  | ANSC3  | ANSC2  | ANSC1  | _     | 601E          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

#### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER (CONTINUED)

| bit 2 | RQCOL2: Channel 2 Transfer Request Collision Flag bit                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = User FORCE and interrupt-based request collision detected</li><li>0 = No request collision detected</li></ul> |

| bit 1 | RQCOL1: Channel 1 Transfer Request Collision Flag bit                                                                     |

|       | 1 = User FORCE and interrupt-based request collision detected                                                             |

|       | 0 = No request collision detected                                                                                         |

| bit 0 | RQCOL0: Channel 0 Transfer Request Collision Flag bit                                                                     |

|       | 1 = User FORCE and interrupt-based request collision detected                                                             |

|       | 0 = No request collision detected                                                                                         |

| Input Name <sup>(1)</sup>                      | Function Name | Register | Configuration Bits |

|------------------------------------------------|---------------|----------|--------------------|

| DCI Data Input                                 | CSDI          | RPINR24  | CSDIR<6:0>         |

| DCI Clock Input                                | CSCKIN        | RPINR24  | CSCKR<6:0>         |

| DCI FSYNC Input                                | COFSIN        | RPINR25  | COFSR<6:0>         |

| CAN1 Receive                                   | C1RX          | RPINR26  | C1RXR<6:0>         |

| CAN2 Receive                                   | C2RX          | RPINR26  | C2RXR<6:0>         |

| UART3 Receive                                  | U3RX          | RPINR27  | U3RXR<6:0>         |

| UART3 Clear-to-Send                            | U3CTS         | RPINR27  | U3CTSR<6:0>        |

| UART4 Receive                                  | U4RX          | RPINR28  | U4RXR<6:0>         |

| UART4 Clear-to-Send                            | U4CTS         | RPINR28  | U4CTSR<6:0>        |

| SPI3 Data Input                                | SDI3          | RPINR29  | SDI3R<6:0>         |

| SPI3 Clock Input                               | SCK3          | RPINR29  | SCK3R<6:0>         |

| SPI3 Slave Select                              | SS3           | RPINR30  | SS3R<6:0>          |

| SPI4 Data Input                                | SDI4          | RPINR31  | SDI4R<6:0>         |

| SPI4 Clock Input                               | SCK4          | RPINR31  | SCK4R<6:0>         |

| SPI4 Slave Select                              | SS4           | RPINR32  | SS4R<6:0>          |

| Input Capture 9                                | IC9           | RPINR33  | IC9R<6:0>          |

| nput Capture 10                                | IC10          | RPINR33  | IC10R<6:0>         |

| nput Capture 11                                | IC11          | RPINR34  | IC11R<6:0>         |

| nput Capture 12                                | IC12          | RPINR34  | IC12R<6:0>         |

| nput Capture 13                                | IC13          | RPINR35  | IC13R<6:0>         |

| nput Capture 14                                | IC14          | RPINR35  | IC14R<6:0>         |

| nput Capture 15                                | IC15          | RPINR36  | IC15R<6:0>         |

| nput Capture 16                                | IC16          | RPINR36  | IC16R<6:0>         |

| Output Compare Fault C                         | OCFC          | RPINR37  | OCFCR<6:0>         |

| PWM Fault 5 <sup>(2)</sup>                     | FLT5          | RPINR42  | FLT5R<6:0>         |

| PWM Fault 6 <sup>(2)</sup>                     | FLT6          | RPINR42  | FLT6R<6:0>         |

| PWM Fault 7 <sup>(2)</sup>                     | FLT7          | RPINR43  | FLT7R<6:0>         |

| PWM Dead-Time<br>Compensation 1 <sup>(2)</sup> | DTCMP1        | RPINR38  | DTCMP1R<6:0>       |

| PWM Dead-Time<br>Compensation 2 <sup>(2)</sup> | DTCMP2        | RPINR39  | DTCMP2R<6:0>       |

| PWM Dead-Time<br>Compensation 3 <sup>(2)</sup> | DTCMP3        | RPINR39  | DTCMP3R<6:0>       |

| PWM Dead-Time<br>Compensation 4 <sup>(2)</sup> | DTCMP4        | RPINR40  | DTCMP4R<6:0>       |

| PWM Dead-Time<br>Compensation 5 <sup>(2)</sup> | DTCMP5        | RPINR40  | DTCMP5R<6:0>       |

| PWM Dead-Time<br>Compensation 6 <sup>(2)</sup> | DTCMP6        | RPINR41  | DTCMP6R<6:0>       |

| PWM Dead-Time<br>Compensation 7 <sup>(2)</sup> | DTCMP7        | RPINR41  | DTCMP7R<6:0>       |

| PWM Synch Input 1 <sup>(2)</sup>               | SYNCI1        | RPINR37  | SYNCI1R<6:0>       |

| PWM Synch Input 2 <sup>(2)</sup>               | SYNCI2        | RPINR38  | SYNCI2R<6:0>       |

| TABLE 11-1: | SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION) (CONTINUED) |

|-------------|---------------------------------------------------------------|

|-------------|---------------------------------------------------------------|

Note 1: Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

2: This input source is available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

| Peripheral Pin Select<br>Input Register Value | Input/<br>Output | Pin Assignment | Peripheral Pin Select<br>Input Register Value | Input/<br>Output | Pin Assignment |

|-----------------------------------------------|------------------|----------------|-----------------------------------------------|------------------|----------------|

| 010 1011                                      | I                | RPI43          | 101 1000                                      | I                | RPI88          |

| 010 1100                                      | I                | RPI44          | 101 1001                                      | I                | RPI89          |

| 101 1010                                      | —                | Reserved       | 110 1101                                      | I/O              | RP109          |

| 101 1011                                      | —                | Reserved       | 110 1110                                      | _                | Reserved       |

| 101 1100                                      | —                | Reserved       | 110 1111                                      | —                | Reserved       |

| 101 1101                                      | —                | Reserved       | 111 0000                                      | I/O              | RP112          |

| 101 1110                                      | —                | Reserved       | 111 0001                                      | I/O              | RP113          |

| 101 1111                                      | —                | Reserved       | 111 0010                                      | _                | Reserved       |

| 110 0000                                      | I/O              | RP96           | 111 0011                                      | _                | Reserved       |

| 110 0001                                      | I/O              | RP97           | 111 0100                                      |                  | Reserved       |

| 110 0010                                      | I/O              | RP98           | 111 0101                                      | —                | Reserved       |

| 110 0011                                      | I/O              | RP99           | 111 0110                                      | I/O              | RP118          |

| 110 0100                                      | I/O              | RP100          | 111 0111                                      | I                | RPI119         |

| 110 0101                                      | I/O              | RP101          | 111 1000                                      | I/O              | RP120          |

| 110 0110                                      | I/O              | RP102          | 111 1001                                      | I                | RPI121         |

| 110 0111                                      | —                | Reserved       | 111 1010                                      |                  | Reserved       |

| 110 1000                                      | I/O              | RP104          | 111 1011                                      | —                | Reserved       |

| 110 1001                                      | —                | Reserved       | 111 1100                                      | I                | RPI124         |

| 110 1010                                      | —                | Reserved       | 111 1101                                      | I/O              | RP125          |

| 110 1011                                      | _                | Reserved       | 111 1110                                      | I/O              | RP126          |

| 110 1100                                      | I/O              | RP108          | 111 1111                                      | I/O              | RP127          |

#### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

Note 1: See Section 11.4.4.2 "Virtual Connections" for more information on selecting this pin assignment.

#### 11.5 I/O Helpful Tips

- In some cases, certain pins, as defined in 1. Table 32-9 in Section 32.0 "Electrical Characteristics" under "Injection Current", have internal protection diodes to VDD and VSS; the term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin, (i.e., ANx, see Table 1-1 in Section 1.0 "Device Overview"), are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin, automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared analog pin (see Table 1-1 in Section 1.0 "Device Overview"), the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left to right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1; this indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin. Dedicated peripheral functions are always higher priority than remappable functions. I/O pins are always the lowest priority.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD-0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in **Section 32.0 "Electrical Characteristics"** for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input, provided there is no external analog input, such as for a built-in self test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including any pin with a single output from either a dedicated or remappable "output".

| U-0                | R/W-0                                      | R/W-0                                                                                    | R/W-0                                          | R/W-0             | R/W-0         | R/W-0            | R/W-0 |

|--------------------|--------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|---------------|------------------|-------|

| _                  |                                            |                                                                                          |                                                | INT3R<6:0>        |               |                  |       |

| bit 15             | ŀ                                          |                                                                                          |                                                |                   |               |                  | bit 8 |

|                    |                                            |                                                                                          |                                                |                   |               |                  |       |

| U-0                | R/W-0                                      | R/W-0                                                                                    | R/W-0                                          | R/W-0             | R/W-0         | R/W-0            | R/W-0 |

| _                  |                                            |                                                                                          |                                                | INT2R<6:0>        |               |                  |       |

| bit 7              |                                            |                                                                                          |                                                |                   |               |                  | bit C |

|                    |                                            |                                                                                          |                                                |                   |               |                  |       |

| Legend:            |                                            |                                                                                          |                                                |                   |               |                  |       |

| R = Readab         |                                            | W = Writable                                                                             |                                                | U = Unimplem      |               |                  |       |

| -n = Value a       | at POR                                     | '1' = Bit is set                                                                         |                                                | '0' = Bit is clea | ared          | x = Bit is unkr  | nown  |

|                    | INT3R<6:0>:<br>(see Table 11               | I-2 for input pin                                                                        | al Interrupt 3 (<br>selection num              | ,                 | rresponding I | RPn/RPIn Pin bit | ts    |

| bit 15<br>bit 14-8 | INT3R<6:0><br>(see Table 11<br>1111111 = I | : Assign Externa<br>I-2 for input pin<br>nput tied to RP <sup>-</sup><br>nput tied to CM | al Interrupt 3 (<br>selection num<br>127<br>P1 | ,                 | rresponding I | RPn/RPIn Pin bil | ts    |

|                    | INT3R<6:0><br>(see Table 11<br>1111111 = I | : Assign Externa<br>I-2 for input pin<br>nput tied to RP1                                | al Interrupt 3 (<br>selection num<br>127<br>P1 | ,                 | rresponding I | RPn/RPIn Pin bil | is    |

#### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

|                | R/W-0                          | R/W-0                                                     | R/W-0                          | U-0               | U-0              | U-0             | R/W-0      |

|----------------|--------------------------------|-----------------------------------------------------------|--------------------------------|-------------------|------------------|-----------------|------------|

| FLTMD          | FLTOUT                         | FLTTRIEN                                                  | OCINV                          | _                 | _                | _               | OC32       |

| bit 15         | •                              | · · · · ·                                                 |                                | •                 | •                |                 | bit        |

| DAMO           |                                |                                                           | DAMO                           |                   |                  |                 |            |

| R/W-0          | R/W-0 HS                       | R/W-0                                                     | R/W-0                          | R/W-1             | R/W-1            | R/W-0           | R/W-0      |

| OCTRIG         | TRIGSTAT                       | OCTRIS                                                    |                                |                   | SYNCSEL<4:0      | >               | L :4       |

| bit 7          |                                |                                                           |                                |                   |                  |                 | bit        |

| Legend:        |                                | HS = Hardwar                                              | e Settable bit                 |                   |                  |                 |            |

| R = Readable   | e bit                          | W = Writable b                                            | oit                            | U = Unimpler      | mented bit, read | l as '0'        |            |

| -n = Value at  | POR                            | '1' = Bit is set                                          |                                | '0' = Bit is cle  | ared             | x = Bit is unkr | nown       |

|                |                                |                                                           |                                |                   |                  |                 |            |

| bit 15         | FLTMD: Fault                   | t Mode Select bi                                          | it                             |                   |                  |                 |            |

|                |                                | de is maintaine                                           |                                |                   | removed; the c   | orresponding    | OCFLTx bit |

|                |                                | n software and a<br>de is maintained                      |                                |                   | noved and a nov  | W D\\//M pariad | etarte     |

| bit 14         | FLTOUT: Fau                    |                                                           |                                |                   | noveu anu a ne   |                 | SIGNS      |

| UIL 14         |                                | tput is driven hig                                        | nh on a Fault                  |                   |                  |                 |            |

|                |                                | put is driven low                                         |                                |                   |                  |                 |            |

| bit 13         | FLTTRIEN: F                    | ault Output Stat                                          | e Select bit                   |                   |                  |                 |            |

|                |                                | is tri-stated on F                                        |                                |                   |                  |                 |            |

|                |                                | I/O state defined                                         | d by FLTOUT                    | bit on Fault co   | ndition          |                 |            |

| bit 12         | OCINV: OCM                     |                                                           |                                |                   |                  |                 |            |

|                | 1 = OCx outp<br>0 = OCx outp   | out is inverted<br>out is not inverte                     | d                              |                   |                  |                 |            |

| bit 11-9       | •                              | ted: Read as '0                                           |                                |                   |                  |                 |            |

| bit 8          | -                              | de Two OCx Mo                                             |                                | e bit (32-bit ope | ration)          |                 |            |

|                |                                | module operati                                            |                                | · ·               | ,                |                 |            |

|                | 0 = Cascade                    | module operati                                            | on is disabled                 | t                 |                  |                 |            |

| bit 7          |                                | x Trigger/Sync S                                          |                                |                   |                  |                 |            |

|                | 00                             | OCx from sourc<br>nizes OCx with s                        | U U                            |                   |                  |                 |            |

|                | -                              |                                                           | -                              |                   |                  |                 |            |

| bit 6          | TRIGSTAT: T                    | imer Trigger Sta                                          | itus bit                       |                   |                  |                 |            |

| bit 6          | 1 = Timer sou                  | imer Trigger Sta<br>urce has been ti                      | riggered and                   | -                 |                  |                 |            |

|                | 1 = Timer sou<br>0 = Timer sou | urce has been to<br>urce has not bee                      | riggered and<br>en triggered a | and is being hel  | d clear          |                 |            |

| bit 6<br>bit 5 | 1 = Timer sou<br>0 = Timer sou | urce has been ti<br>urce has not been<br>x Output Pin Dir | riggered and<br>en triggered a | and is being hel  | d clear          |                 |            |

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

2: When the OCy module is turned OFF, it sends a trigger out signal. If the OCx module uses the OCy module as a Trigger source, the OCy module must be unselected as a Trigger source prior to disabling it.

#### REGISTER 16-19: IOCONX: PWMx I/O CONTROL REGISTER (CONTINUED)

| bit 3-2 | CLDAT<1:0>: Data for PWMxH and PWMxL Pins if CLMOD is Enabled bits                                                                                                                                              |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | IFLTMOD (FCLCONx<15>) = 0: Normal Fault mode:                                                                                                                                                                   |

|         | If current limit is active, PWMxH is driven to the state specified by CLDAT<1>.                                                                                                                                 |

|         | If current limit is active, PWMxL is driven to the state specified by CLDAT<0>.                                                                                                                                 |

|         | IFLTMOD (FCLCONx<15>) = 1: Independent Fault mode:                                                                                                                                                              |

|         | The CLDAT<1:0> bits are ignored.                                                                                                                                                                                |

| bit 1   | SWAP: Swap PWMxH and PWMxL Pins bit                                                                                                                                                                             |

|         | 1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins                                                                                                              |

|         | 0 = PWMxH and PWMxL pins are mapped to their respective pins                                                                                                                                                    |

| bit 0   | OSYNC: Output Override Synchronization bit                                                                                                                                                                      |

|         | <ul> <li>1 = Output overrides via the OVRDAT&lt;1:0&gt; bits are synchronized to the PWM time base</li> <li>0 = Output overrides via the OVDDAT&lt;1:0&gt; bits occur on the next CPU clock boundary</li> </ul> |

|         |                                                                                                                                                                                                                 |

Note 1: These bits should not be changed after the PWM module is enabled (PTEN = 1).

#### **REGISTER 17-10: INDXxHLD: INDEX COUNTER x HOLD REGISTER**

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|----------------------------------------------------------------------|-------|------------------|-------|------------------|-------|-----------------|-------|

|                                                                      |       |                  | INDXH | LD<15:8>         |       |                 |       |

| bit 15                                                               |       |                  |       |                  |       |                 | bit 8 |

|                                                                      |       |                  |       |                  |       |                 |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|                                                                      |       |                  | INDX  | ILD<7:0>         |       |                 |       |

| bit 7                                                                |       |                  |       |                  |       |                 | bit 0 |

|                                                                      |       |                  |       |                  |       |                 |       |

| Legend:                                                              |       |                  |       |                  |       |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                  |       |                 |       |

| -n = Value at P                                                      | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared  | x = Bit is unkr | nown  |

|                                                                      |       |                  |       |                  |       |                 |       |

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDXxCNTH bits

#### REGISTER 17-11: QEIxICH: QEIx INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|----------------|-------|

|                 |       |                  | QEIIC | <31:24>          |                 |                |       |

| bit 15          |       |                  |       |                  |                 |                | bit 8 |

|                 |       |                  |       |                  |                 |                |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

|                 |       |                  | QEIIC | <23:16>          |                 |                |       |

| bit 7           |       |                  |       |                  |                 |                | bit 0 |

|                 |       |                  |       |                  |                 |                |       |

| Legend:         |       |                  |       |                  |                 |                |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimplen     | nented bit, rea | ad as '0'      |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unk | nown  |

bit 15-0 **QEIIC<31:16>:** QEIx High Word Used to Form 32-Bit Initialization/Capture Register (QEIxIC) bits

#### REGISTER 17-12: QEIxICL: QEIx INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|-------|----------------|-------|-----------------------------------------|-------|-------|-------|--|

|                                    |       |                | QEIIO | C<15:8>                                 |       |       |       |  |

| bit 15                             |       |                |       |                                         |       |       | bit 8 |  |

|                                    |       |                |       |                                         |       |       |       |  |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |       |                | QEII  | C<7:0>                                  |       |       |       |  |

| bit 7                              |       |                |       |                                         |       |       | bit 0 |  |

|                                    |       |                |       |                                         |       |       |       |  |

| Legend:                            |       |                |       |                                         |       |       |       |  |

| R = Readable                       | bit   | W = Writable b | oit   | U = Unimplemented bit, read as '0'      |       |       |       |  |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

bit 15-0 QEIIC<15:0>: QEIx Low Word Used to Form 32-Bit Initialization/Capture Register (QEIxIC) bits

### dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| R/W-0                                                                        | R/W-0                                       | R/W-0            | R/W-0                                          | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |  |

|------------------------------------------------------------------------------|---------------------------------------------|------------------|------------------------------------------------|-----------------------------------------|-----------------|----------|-------|--|--|

|                                                                              | F7BF                                        | P<3:0>           |                                                | F6BP<3:0>                               |                 |          |       |  |  |

| bit 15                                                                       |                                             |                  |                                                |                                         |                 |          | bit 8 |  |  |

| R/W-0                                                                        | R/W-0                                       | R/W-0            | R/W-0                                          | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |  |  |

|                                                                              | F5BP<3:0>                                   |                  |                                                |                                         | F4BI            | ><3:0>   |       |  |  |

| pit 7                                                                        |                                             |                  |                                                |                                         |                 |          | bit 0 |  |  |

| Legend:                                                                      | lo hit                                      | M = Mritabla     | <b>h</b> it                                    |                                         | control hit roo | d aa (0) |       |  |  |

| R = Readab                                                                   |                                             | W = Writable     |                                                | U = Unimplen                            |                 |          |       |  |  |

| -n = Value a                                                                 | t POR                                       | '1' = Bit is set |                                                | '0' = Bit is cleared x = Bit is unknown |                 |          | IOWN  |  |  |

| bit 15-12                                                                    | F7BP<3:0>: RX Buffer Mask for Filter 7 bits |                  |                                                |                                         |                 |          |       |  |  |

| 1111 = Filter hits received in RX FI<br>1110 = Filter hits received in RX Bu |                                             |                  |                                                |                                         |                 |          |       |  |  |

|                                                                              |                                             |                  | n RX FIFO bu                                   |                                         |                 |          |       |  |  |

|                                                                              |                                             |                  | n RX FIFO bu                                   |                                         |                 |          |       |  |  |

|                                                                              | 1110 <b>= Filte</b>                         |                  | n RX FIFO bu                                   |                                         |                 |          |       |  |  |

|                                                                              | 1110 = Filte<br>•<br>•<br>•<br>•            |                  | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | 4                                       |                 |          |       |  |  |

- bit 7-4 F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bit 15-12)

- bit 3-0 F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bit 15-12)

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                         | R/W-0                                      | R/W-0           | R/W-0                              | R/W-0 | R/W-0              | R/W-0   |  |

|---------------|-----------------------------------------------|--------------------------------------------|-----------------|------------------------------------|-------|--------------------|---------|--|

|               | F11B                                          | P<3:0>                                     |                 |                                    | F10E  | 3P<3:0>            |         |  |

| bit 15        |                                               |                                            |                 |                                    |       |                    | bit 8   |  |

| R/W-0         | R/W-0                                         | R/W-0                                      | R/W-0           | R/W-0                              | R/W-0 | R/W-0              | R/W-0   |  |

| 10,00-0       | -                                             | P<3:0>                                     | 10.00-0         |                                    | -     | P<3:0>             | 10.00-0 |  |

| bit 7         | 1 3 01                                        | 10.02                                      |                 |                                    | 100   | 1 3.02             | bit 0   |  |

|               |                                               |                                            |                 |                                    |       |                    | bit o   |  |

| Legend:       |                                               |                                            |                 |                                    |       |                    |         |  |

| R = Readabl   | e bit                                         | W = Writable                               | bit             | U = Unimplemented bit, read as '0' |       |                    |         |  |

| -n = Value at | POR                                           | '1' = Bit is set                           | :               | '0' = Bit is clea                  | ared  | x = Bit is unknown |         |  |

|               |                                               |                                            |                 |                                    |       |                    |         |  |

| bit 15-12     | F11BP<3:0                                     | RX Buffer Ma                               | sk for Filter 1 | 1 bits                             |       |                    |         |  |

|               | 1111 = Filter hits received in RX FIFO buffer |                                            |                 |                                    |       |                    |         |  |

|               | 1111 = Filte                                  | er hits received in                        | h RX FIFO bu    | lmer                               |       |                    |         |  |

|               |                                               | er hits received in<br>er hits received in |                 | -                                  |       |                    |         |  |

|               |                                               |                                            |                 | -                                  |       |                    |         |  |

|          | •                                                                        |

|----------|--------------------------------------------------------------------------|

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F10BP<3:0>: RX Buffer Mask for Filter 10 bits (same values as bit 15-12) |

| bit 7-4  | F9BP<3:0>: RX Buffer Mask for Filter 9 bits (same values as bit 15-12)   |

| bit 3-0  | F8BP<3:0>: RX Buffer Mask for Filter 8 bits (same values as bit 15-12)   |

### dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| U-0                           | U-0                                                                                                                               | U-0                                                                                                               | U-0                                                                                                                                          | U-0                                                                           | U-0            | U-0            | U-0    |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------|----------------|--------|--|--|--|--|

|                               |                                                                                                                                   | —                                                                                                                 |                                                                                                                                              |                                                                               | _              |                | —      |  |  |  |  |

| bit 15                        | •                                                                                                                                 |                                                                                                                   |                                                                                                                                              |                                                                               |                |                | bit    |  |  |  |  |

|                               |                                                                                                                                   |                                                                                                                   |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

| R/W-0                         | R/W-0                                                                                                                             | U-0                                                                                                               | R/W-0                                                                                                                                        | R/W-0                                                                         | R/W-0          | R/W-0          | R/W-0  |  |  |  |  |

| LSPD <sup>(1)</sup>           | RETRYDIS <sup>(1)</sup>                                                                                                           |                                                                                                                   | EPCONDIS                                                                                                                                     | EPRXEN                                                                        | EPTXEN         | EPSTALL        | EPHSHK |  |  |  |  |

| bit 7                         |                                                                                                                                   |                                                                                                                   |                                                                                                                                              |                                                                               |                |                | bit    |  |  |  |  |

| Logondu                       |                                                                                                                                   |                                                                                                                   |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

| L <b>egend:</b><br>R = Readab | lo hit                                                                                                                            | W = Writable                                                                                                      | - hit                                                                                                                                        |                                                                               | ontod bit road | L ac 'O'       |        |  |  |  |  |

| -n = Value a                  |                                                                                                                                   | '1' = Bit is se                                                                                                   |                                                                                                                                              | U = Unimplemented bit, read as '0'<br>'0' = Bit is cleared x = Bit is unknown |                |                |        |  |  |  |  |

|                               | IFUR                                                                                                                              |                                                                                                                   | 51                                                                                                                                           |                                                                               | areu           | X – DILIS UIKI |        |  |  |  |  |

| bit 15-8                      | Unimplement                                                                                                                       | ed: Read as                                                                                                       | 'O'                                                                                                                                          |                                                                               |                |                |        |  |  |  |  |

| bit 7                         | -                                                                                                                                 |                                                                                                                   |                                                                                                                                              | le bit (UEP0 on                                                               | 1)(1)          |                |        |  |  |  |  |

|                               | LSPD: Low-Speed Direct Connection Enable bit (UEP0 only) <sup>(1)</sup><br>1 = Direct connection to a low-speed device is enabled |                                                                                                                   |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

|                               |                                                                                                                                   |                                                                                                                   | ow-speed device                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

| oit 6                         | <b>RETRYDIS:</b> Retry Disable bit (UEP0 only) <sup>(1)</sup>                                                                     |                                                                                                                   |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

|                               | <ul> <li>1 = Retry NAK transactions is disabled</li> <li>0 = Retry NAK transactions is enabled; retry done in hardware</li> </ul> |                                                                                                                   |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

|                               |                                                                                                                                   |                                                                                                                   |                                                                                                                                              | y done in hard                                                                | ware           |                |        |  |  |  |  |

| bit 5                         | Unimplement                                                                                                                       | ed: Read as                                                                                                       | '0'                                                                                                                                          |                                                                               |                |                |        |  |  |  |  |

| oit 4                         |                                                                                                                                   | EPCONDIS: Bidirectional Endpoint Control bit                                                                      |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

|                               |                                                                                                                                   | If EPTXEN and EPRXEN = 1:<br>1 =  Disable Endpoint n from control transfers; only TX and RX transfers are allowed |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

|                               |                                                                                                                                   |                                                                                                                   | n control transfe<br>control (SETUP)                                                                                                         |                                                                               |                |                | wod    |  |  |  |  |

|                               |                                                                                                                                   | -                                                                                                                 | of EPTXEN and I                                                                                                                              |                                                                               |                |                | weu    |  |  |  |  |

|                               | This bit is ignor                                                                                                                 |                                                                                                                   |                                                                                                                                              | LFRALN.                                                                       |                |                |        |  |  |  |  |

| bit 3                         | EPRXEN: End                                                                                                                       |                                                                                                                   | e Enable bit                                                                                                                                 |                                                                               |                |                |        |  |  |  |  |

|                               | 1 = Endpoint r                                                                                                                    | -                                                                                                                 |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

|                               | 0 = Endpoint r                                                                                                                    |                                                                                                                   |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

| bit 2                         | EPTXEN: End                                                                                                                       | point Transm                                                                                                      | it Enable bit                                                                                                                                |                                                                               |                |                |        |  |  |  |  |

|                               | 1 = Endpoint r                                                                                                                    |                                                                                                                   |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

|                               | 0 = Endpoint r                                                                                                                    |                                                                                                                   |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

| bit 1                         |                                                                                                                                   | EPSTALL: Endpoint Stall Status bit                                                                                |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

|                               | 1 = Endpoint r                                                                                                                    |                                                                                                                   | llad                                                                                                                                         |                                                                               |                |                |        |  |  |  |  |

| -:                            | 0 = Endpoint r                                                                                                                    |                                                                                                                   |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

| oit 0                         | EPHSHK: Endpoint Handshake Enable bit                                                                                             |                                                                                                                   |                                                                                                                                              |                                                                               |                |                |        |  |  |  |  |

|                               | 1 <b>—</b> Example 1                                                                                                              | handahalia !-                                                                                                     | <ul> <li>1 = Endpoint handshake is enabled</li> <li>0 = Endpoint handshake is disabled (typically used for isochronous endpoints)</li> </ul> |                                                                               |                |                |        |  |  |  |  |

**Note 1:** These bits are available only for UxEP0 and only in Host mode. For all other UxEPn registers, these bits are always unimplemented and read as '0'.

| R/W-0                             | U-0                                        | U-0                                                                                                                                        | R/W-0                       | R/W-0            | R/W-0                   | R/W-0           | R/W-0 |  |  |  |

|-----------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-------------------------|-----------------|-------|--|--|--|