Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 83                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gu810-i-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

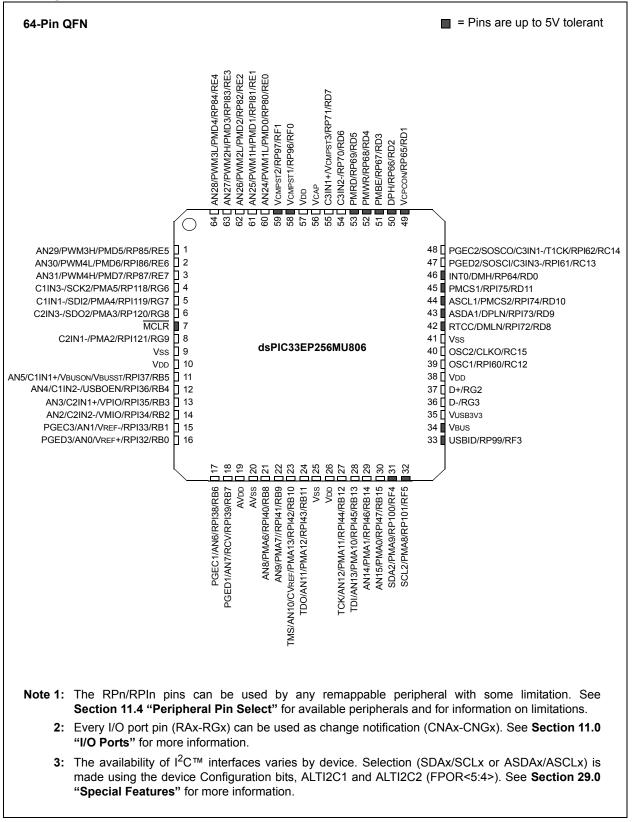

### **Pin Diagrams**

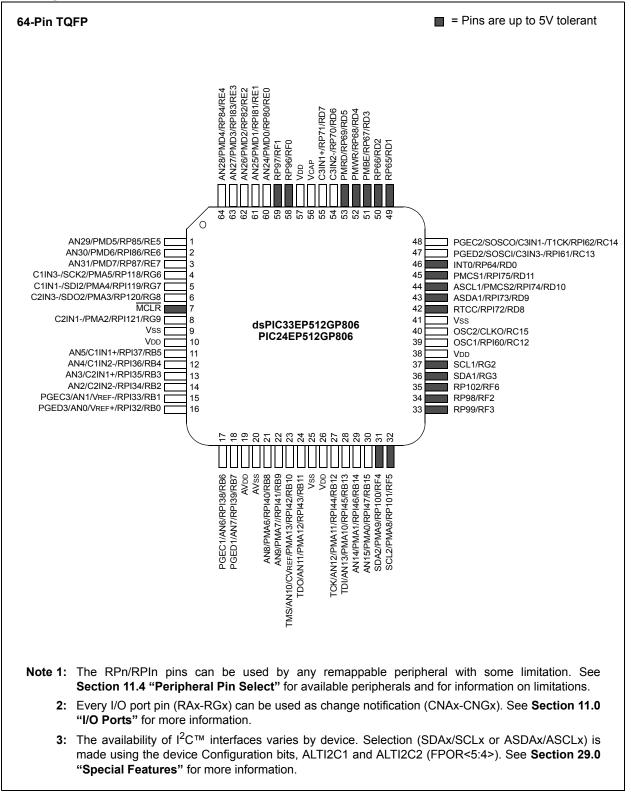

## Pin Diagrams (Continued)

### 3.8 Arithmetic Logic Unit (ALU)

The ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.9 DSP Engine (dsPIC33EPXXX(GP/ MC/MU)806/810/814 Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are: ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed, unsigned or mixed-sign DSP multiply (US)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

| Instruction | Algebraic<br>Operation                          | ACC Write<br>Back |

|-------------|-------------------------------------------------|-------------------|

| CI D        | A = 0                                           | Yes               |

| CLR<br>ED   | $A = 0$ $A = (x - y)^2$                         | No                |

| ED          | $A = (x - y)$ $A = A + (x - y)^2$               | No                |

| MAC         | $A = A + (x \bullet y)$ $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$                                   | No                |

| MOVSAC      | No change in A                                  | Yes               |

| MPY         | $A = x \bullet y$                               | No                |

| MPY         | $A = x^2$                                       | No                |

| MPY.N       | $A = -x \bullet y$                              | No                |

| MSC         | $A = A - x \bullet y$                           | Yes               |

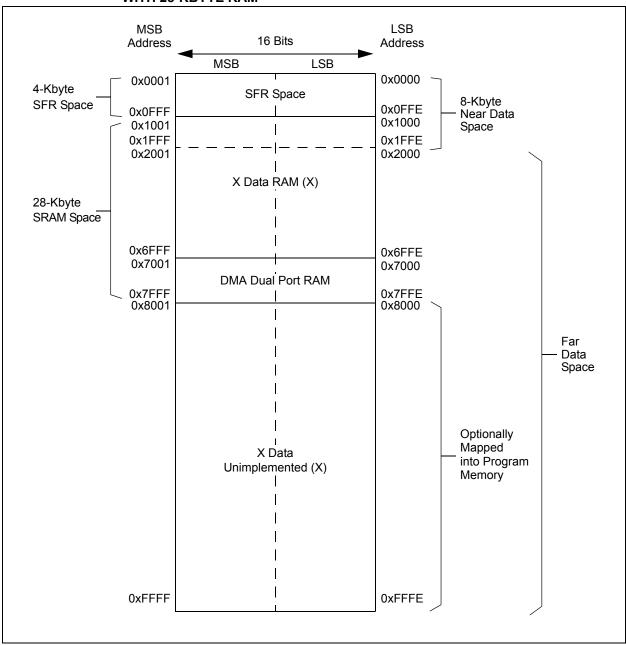

FIGURE 4-6: DATA MEMORY MAP FOR PIC24EP256GU810/814 DEVICES WITH 28-KBYTE RAM

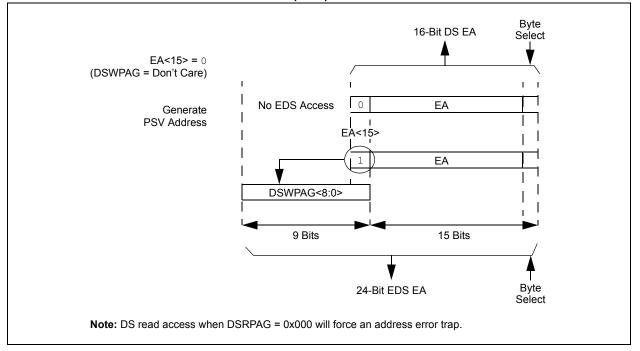

### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers DSxPAG, in combination with the upper half of data space address can provide up to 16 Mbytes of additional address space in the EDS and 12 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS, only. The data space and EDS can be read from and written to using DSRPAG and DSWPAG, respectively.

### REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

bit 7

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | N     | OV    | Z     | С     |

bit 0

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2,3)</sup>

- 111 = CPU Interrupt Priority Level is 7 (15, user interrupts are disabled)

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

- Note 1: For complete register details, see Register 3-1: "SR: CPU Status Register".

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

### 11.4.4.2 Virtual Connections

The dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 devices support virtual (internal) connections to the output of the comparator modules, CMP1OUT, CMP2OUT and CMP3OUT (see Figure 25-1 in Section 25.0 "Comparator Module"). In addition, dsPIC33EPXXXMU806/810/814 devices support virtual connections to the filtered QEI module inputs, FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXX(MC/ MU)8XX Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of `b000001, the output of the analog comparator, CMP1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device. Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled, and its inputs must be connected to a physical RPn/RPIn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn/RPIn pins is possible. This includes both many-to-one and one-tomany mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

# EXAMPLE 11-2: CONNECTING IC1 TO HOME1 DIGITAL FILTER INPUT ON PIN 3 OF THE dsPIC33EP512MU810 DEVICE

RPINR15 = 0x5600; /\* Connect the QEI1 HOME1 input to RP86 (pin 3) \*/

RPINR7 = 0x009; /\* Connect the IC1 input to the digital filter on the FHOME1 input \*/

QEI1IOC = 0x4000; /\* Enable the QEI digital filter \*/

QEI1CON = 0x8000; /\* Enable the QEI module \*/

|                    | R/W-0                                      | R/W-0                                                                                                           | R/W-0                                        | R/W-0             | R/W-0        | R/W-0           | R/W-0    |

|--------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------|--------------|-----------------|----------|

| _                  |                                            |                                                                                                                 |                                              | T7CKR<6:0>        |              |                 |          |

| bit 15             |                                            |                                                                                                                 |                                              |                   |              |                 | bit      |

|                    |                                            |                                                                                                                 |                                              |                   |              |                 |          |

| U-0                | R/W-0                                      | R/W-0                                                                                                           | R/W-0                                        | R/W-0             | R/W-0        | R/W-0           | R/W-0    |

|                    |                                            |                                                                                                                 |                                              | T6CKR<6:0>        |              |                 |          |

| bit 7              |                                            |                                                                                                                 |                                              |                   |              |                 | bit      |

|                    |                                            |                                                                                                                 |                                              |                   |              |                 |          |

| Legend:            |                                            |                                                                                                                 |                                              |                   |              |                 |          |

| R = Readab         |                                            | W = Writable                                                                                                    |                                              | U = Unimplem      |              |                 |          |

| -n = Value a       | t POR                                      | '1' = Bit is set                                                                                                |                                              | '0' = Bit is clea | ared         | x = Bit is unkr | nown     |

|                    | T7CKR<6:0><br>(see Table 11                | <ul> <li>ted: Read as 'i</li> <li>Assign Timer'</li> <li>I-2 for input pin</li> <li>nput tied to RP'</li> </ul> | 7 External Clo<br>selection num              |                   | e Correspond | ling RPn/RPIn F | Pin bits |

| bit 15<br>bit 14-8 | T7CKR<6:0><br>(see Table 11<br>1111111 = I | Assign Timer<br>I-2 for input pin<br>nput tied to RP <sup>2</sup><br>nput tied to CM                            | 7 External Clo<br>selection num<br>127<br>P1 |                   | e Correspond | ling RPn/RPIn F | 'in bits |

|                    | T7CKR<6:0><br>(see Table 11<br>1111111 = I | Assign Timer<br>I-2 for input pin<br>nput tied to RP <sup>2</sup>                                               | 7 External Clo<br>selection num<br>127<br>P1 |                   | e Correspond | ling RPn/RPIn F | Pin bits |

### REGISTER 11-6: RPINR5: PERIPHERAL PIN SELECT INPUT REGISTER 5

### REGISTER 11-17: RPINR16: PERIPHERAL PIN SELECT INPUT REGISTER 16 (dsPIC33EPXXXMU806/810/814 DEVICES ONLY)

| U-0          | R/W-0         | R/W-0                                                                | R/W-0         | R/W-0            | R/W-0           | R/W-0             | R/W-0 |

|--------------|---------------|----------------------------------------------------------------------|---------------|------------------|-----------------|-------------------|-------|

|              |               |                                                                      |               | QEB2R<6:0>(      | 1)              |                   |       |

| bit 15       |               |                                                                      |               |                  |                 |                   | bit 8 |

|              |               |                                                                      |               |                  |                 |                   |       |

| U-0          | R/W-0         | R/W-0                                                                | R/W-0         | R/W-0            | R/W-0           | R/W-0             | R/W-0 |

| —            |               |                                                                      |               | QEA2R<6:0>(      | 1)              |                   |       |

| bit 7        |               |                                                                      |               |                  |                 |                   | bit C |

|              |               |                                                                      |               |                  |                 |                   |       |

| Legend:      |               |                                                                      |               |                  |                 |                   |       |

| R = Readab   | ole bit       | W = Writable                                                         | bit           | U = Unimpler     | nented bit, rea | id as '0'         |       |

| -n = Value a | it POR        | '1' = Bit is set                                                     |               | '0' = Bit is cle | ared            | x = Bit is unkr   | nown  |

|              | 0000001 =     | nput tied to RP <sup>-</sup><br>nput tied to CM<br>nput tied to Vss  | P1            |                  |                 |                   |       |

| bit 7        | Unimpleme     | nted: Read as '                                                      | 0'            |                  |                 |                   |       |

| bit 6-0      | (see Table 17 | >: Assign A (QE<br>I-2 for input pin<br>nput tied to RP <sup>2</sup> | selection nun |                  | 'n/RPIn Pin bi  | <sub>'S</sub> (1) |       |

Note 1: These bits are available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                               |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                        |

|       | <ul> <li>1 = Receiver is Idle</li> <li>0 = Receiver is active</li> </ul>                                                                                                                                                    |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                   |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                 |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                  |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                    |

|       | 0 = Framing error has not been detected                                                                                                                                                                                     |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                                                                             |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets<br/>the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                        |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                               |

|       |                                                                                                                                                                                                                             |

**Note 1:** Refer to **Section 17. "UART**" (DS70582) in the *"dsPIC33E/PIC24E Family Reference Manual"* for information on enabling the UARTx module for transmit operation.

| U-0                                   | U-0                                                                                                                                                         | U-0                                                                                                                                                               | U-0                                                                                          | U-0                                                     | U-0                 | U-0                   | U-0   |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------|-----------------------|-------|

| _                                     | —                                                                                                                                                           | —                                                                                                                                                                 | _                                                                                            | —                                                       | _                   | —                     | _     |

| bit 15                                | ·                                                                                                                                                           | •                                                                                                                                                                 |                                                                                              |                                                         |                     |                       | bit 8 |

|                                       |                                                                                                                                                             |                                                                                                                                                                   |                                                                                              |                                                         |                     |                       |       |

| R-0, HSC                              | R-0, HSC                                                                                                                                                    | R-0, HSC                                                                                                                                                          | R-0, HSC                                                                                     | R-0, HSC                                                | R-0, HSC            | U-0                   | U-0   |

|                                       | ENDPT                                                                                                                                                       | <3:0> <sup>(2)</sup>                                                                                                                                              |                                                                                              | DIR                                                     | PPBI <sup>(1)</sup> | —                     | —     |

| bit 7                                 |                                                                                                                                                             |                                                                                                                                                                   |                                                                                              |                                                         |                     |                       | bit ( |

| Legend:                               |                                                                                                                                                             | U = Unimplen                                                                                                                                                      | nented bit, read                                                                             | 1 as '0'                                                |                     |                       |       |

| R = Readable                          | e bit                                                                                                                                                       | W = Writable                                                                                                                                                      |                                                                                              | HSC = Hardw                                             | are Settable/C      | learable bit          |       |

| -n = Value at                         | POR                                                                                                                                                         | '1' = Bit is set                                                                                                                                                  |                                                                                              | '0' = Bit is clea                                       | ared                | x = Bit is unkn       | own   |

|                                       | ENDPT<3:0><br>(represents th                                                                                                                                |                                                                                                                                                                   | t Activity Numb                                                                              | er bits<br>T updated by th                              | ne last USB tra     | nsfer) <sup>(2)</sup> |       |

|                                       | ENDPT<3:0>                                                                                                                                                  | : Last Endpoint<br>le number of th<br>pint 15                                                                                                                     | t Activity Numb                                                                              |                                                         | ne last USB tra     | nsfer) <sup>(2)</sup> |       |

|                                       | ENDPT<3:0><br>(represents the<br>1111 = Endpo                                                                                                               | : Last Endpoint<br>le number of th<br>bint 15<br>bint 14<br>bint 1                                                                                                | t Activity Numb                                                                              |                                                         | ne last USB tra     | nsfer) <sup>(2)</sup> |       |

| bit 7-4                               | ENDPT<3:0><br>(represents th<br>1111 = Endpo<br>1110 = Endpo<br>•<br>•<br>•<br>•<br>0001 = Endpo<br>0000 = Endpo                                            | : Last Endpoint<br>le number of th<br>bint 15<br>bint 14<br>bint 1                                                                                                | t Activity Numb<br>e endpoint BD                                                             | T updated by th                                         | ne last USB tra     | nsfer) <sup>(2)</sup> |       |

| bit 7-4                               | ENDPT<3:0><br>(represents th<br>1111 = Endpo<br>1110 = Endpo<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | : Last Endpoint<br>le number of th<br>bint 15<br>bint 14<br>bint 1<br>bint 1                                                                                      | t Activity Numb<br>e endpoint BD<br>Direction Indica<br>s a transmit tra                     | T updated by th<br>itor bit<br>nsfer (TX)               | ne last USB tra     | nsfer) <sup>(2)</sup> |       |

| bit 15-8<br>bit 7-4<br>bit 3<br>bit 2 | ENDPT<3:0><br>(represents th<br>1111 = Endpo<br>1110 = Endpo<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | : Last Endpoint<br>le number of th<br>pint 15<br>pint 14<br>pint 1<br>fer Descriptor I<br>transaction was                                                         | t Activity Numb<br>e endpoint BD<br>Direction Indica<br>s a transmit tra<br>s a receive tran | T updated by th<br>itor bit<br>nsfer (TX)<br>isfer (RX) | ne last USB tra     | nsfer) <sup>(2)</sup> |       |

| bit 7-4                               | ENDPT<3:0><br>(represents th<br>1111 = Endpo<br>1110 = Endpo<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | : Last Endpoint<br>le number of th<br>bint 15<br>bint 14<br>bint 0<br>fer Descriptor I<br>transaction was<br>transaction was<br>ong Buffer Des<br>transaction was | Direction Indicates a transmit trans<br>criptor Pointer<br>to the ODD b                      | T updated by th<br>itor bit<br>nsfer (TX)<br>isfer (RX) | bank                | nsfer) <sup>(2)</sup> |       |

##

Note 1: This bit is only valid for endpoints with available EVEN and ODD buffer descriptor registers.

2: In Host mode, all transactions are processed through Endpoint 0 and the Endpoint 0 BDTs. Therefore, ENDPT<3:0> will always read as '0000'.

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| U-0                           | U-0                     | U-0                                                                             | U-0                                  | U-0               | U-0                 | U-0             | U-0    |  |  |  |  |

|-------------------------------|-------------------------|---------------------------------------------------------------------------------|--------------------------------------|-------------------|---------------------|-----------------|--------|--|--|--|--|

|                               |                         | —                                                                               |                                      |                   |                     |                 | —      |  |  |  |  |

| bit 15                        | •                       |                                                                                 |                                      |                   |                     |                 | bit    |  |  |  |  |

|                               |                         |                                                                                 |                                      |                   |                     |                 |        |  |  |  |  |

| R/W-0                         | R/W-0                   | U-0                                                                             | R/W-0                                | R/W-0             | R/W-0               | R/W-0           | R/W-0  |  |  |  |  |

| LSPD <sup>(1)</sup>           | RETRYDIS <sup>(1)</sup> |                                                                                 | EPCONDIS                             | EPRXEN            | EPTXEN              | EPSTALL         | EPHSHK |  |  |  |  |

| bit 7                         |                         |                                                                                 |                                      |                   |                     |                 | bit    |  |  |  |  |

| Logondu                       |                         |                                                                                 |                                      |                   |                     |                 |        |  |  |  |  |

| L <b>egend:</b><br>R = Readab | lo hit                  | W = Writable                                                                    | - hit                                | U = Unimplem      | ontod hit road      |                 |        |  |  |  |  |

| -n = Value a                  |                         | '1' = Bit is se                                                                 |                                      | '0' = Bit is clea |                     | x = Bit is unkr | 0.000  |  |  |  |  |

|                               | IFUR                    |                                                                                 | 51                                   |                   | lieu                |                 |        |  |  |  |  |

| bit 15-8                      | Unimplement             | ed: Read as                                                                     | 'O'                                  |                   |                     |                 |        |  |  |  |  |

| bit 7                         | -                       |                                                                                 | onnection Enabl                      | le bit (UEP0 on   | <sub>llv)</sub> (1) |                 |        |  |  |  |  |

|                               |                         |                                                                                 | ow-speed device                      |                   |                     |                 |        |  |  |  |  |

|                               |                         |                                                                                 | ow-speed device                      |                   |                     |                 |        |  |  |  |  |

| oit 6                         | RETRYDIS: R             | etry Disable I                                                                  | oit (UEP0 only) <sup>(1</sup>        | )                 |                     |                 |        |  |  |  |  |

|                               |                         | 1 = Retry NAK transactions is disabled                                          |                                      |                   |                     |                 |        |  |  |  |  |

|                               |                         |                                                                                 | s is enabled; retr                   | y done in hard    | ware                |                 |        |  |  |  |  |

| bit 5                         | Unimplement             | ed: Read as                                                                     | '0'                                  |                   |                     |                 |        |  |  |  |  |

| bit 4                         |                         |                                                                                 | indpoint Control                     | bit               |                     |                 |        |  |  |  |  |

|                               | If EPTXEN and           |                                                                                 |                                      |                   |                     |                 |        |  |  |  |  |

|                               |                         |                                                                                 | n control transfe<br>control (SETUP) |                   |                     |                 | wod    |  |  |  |  |

|                               |                         | -                                                                               | of EPTXEN and I                      |                   |                     |                 | weu    |  |  |  |  |

|                               | This bit is ignor       |                                                                                 |                                      | LFRALN.           |                     |                 |        |  |  |  |  |

| bit 3                         | •                       |                                                                                 | e Enable bit                         |                   |                     |                 |        |  |  |  |  |

|                               |                         | <b>EPRXEN:</b> Endpoint Receive Enable bit<br>1 = Endpoint n receive is enabled |                                      |                   |                     |                 |        |  |  |  |  |

|                               | 0 = Endpoint r          |                                                                                 |                                      |                   |                     |                 |        |  |  |  |  |

| bit 2                         | EPTXEN: End             | point Transm                                                                    | it Enable bit                        |                   |                     |                 |        |  |  |  |  |

|                               | 1 = Endpoint r          | 1 = Endpoint n transmit is enabled                                              |                                      |                   |                     |                 |        |  |  |  |  |

|                               | 0 = Endpoint r          |                                                                                 |                                      |                   |                     |                 |        |  |  |  |  |

| bit 1                         |                         | EPSTALL: Endpoint Stall Status bit                                              |                                      |                   |                     |                 |        |  |  |  |  |

|                               | 1 = Endpoint r          |                                                                                 | llad                                 |                   |                     |                 |        |  |  |  |  |

| -:                            | 0 = Endpoint r          |                                                                                 |                                      |                   |                     |                 |        |  |  |  |  |

| oit 0                         |                         | •                                                                               | nake Enable bit                      |                   |                     |                 |        |  |  |  |  |

|                               | 1 = Endpoint ł          | handakelie !-                                                                   | anablad                              |                   |                     |                 |        |  |  |  |  |

**Note 1:** These bits are available only for UxEP0 and only in Host mode. For all other UxEPn registers, these bits are always unimplemented and read as '0'.

| DC CHARACT            | ERISTICS                  |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |        |        |           |  |  |  |

|-----------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|-----------|--|--|--|

| Param. <sup>(2)</sup> | Typ. <sup>(3)</sup>       | Max. | Units                                                                                                                                                                                                                                                                             |        |        |           |  |  |  |

| Operating Cur         | rent (IDD) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                   | ·      |        |           |  |  |  |

| DC20d                 | 12                        | 18   | mA                                                                                                                                                                                                                                                                                | -40°C  |        |           |  |  |  |

| DC20a                 | 12                        | 18   | mA                                                                                                                                                                                                                                                                                | +25°C  | 3.3V   | 10 MIPS   |  |  |  |

| DC20b                 | 13                        | 20   | mA                                                                                                                                                                                                                                                                                | +85°C  | 3.30   | 10 101195 |  |  |  |

| DC20c                 | 14                        | 21   | mA                                                                                                                                                                                                                                                                                | +125°C |        |           |  |  |  |

| DC22d                 | 23                        | 35   | mA                                                                                                                                                                                                                                                                                | -40°C  |        |           |  |  |  |

| DC22a                 | 24                        | 36   | mA                                                                                                                                                                                                                                                                                | +25°C  | - 3.3V | 20 MIPS   |  |  |  |

| DC22b                 | 24                        | 36   | mA                                                                                                                                                                                                                                                                                | +85°C  | 5.50   | 20 WIF 3  |  |  |  |

| DC22c                 | 25                        | 38   | mA                                                                                                                                                                                                                                                                                | +125°C |        |           |  |  |  |

| DC24d                 | 42                        | 63   | mA                                                                                                                                                                                                                                                                                | -40°C  |        |           |  |  |  |

| DC24a                 | 43                        | 65   | mA                                                                                                                                                                                                                                                                                | +25°C  | - 3.3V | 40 MIPS   |  |  |  |

| DC24b                 | 44                        | 66   | mA                                                                                                                                                                                                                                                                                | +85°C  | 3.3V   | 40 101173 |  |  |  |

| DC24c                 | 45                        | 68   | mA                                                                                                                                                                                                                                                                                | +125°C |        |           |  |  |  |

| DC25d                 | 61                        | 92   | mA                                                                                                                                                                                                                                                                                | -40°C  |        |           |  |  |  |

| DC25a                 | 62                        | 93   | mA                                                                                                                                                                                                                                                                                | +25°C  | 3.3V   | 60 MIPS   |  |  |  |

| DC25b                 | 62                        | 93   | mA                                                                                                                                                                                                                                                                                | +85°C  | 5.30   | 00 1011-5 |  |  |  |

| DC25c                 | 63                        | 95   | mA                                                                                                                                                                                                                                                                                | +125°C |        |           |  |  |  |

| DC26d                 | 69                        | 104  | mA                                                                                                                                                                                                                                                                                | -40°C  |        |           |  |  |  |

| DC26a                 | 70                        | 105  | mA                                                                                                                                                                                                                                                                                | +25°C  | 3.3V   | 70 MIPS   |  |  |  |

| DC26b                 | 70                        | 105  | mA                                                                                                                                                                                                                                                                                | +85°C  |        |           |  |  |  |

### TABLE 32-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC Clock Overshoot/Undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (defined PMDx bits are set to zero and unimplemented PMDx bits are set to one)

- CPU is executing while (1) statement

- JTAG is disabled

- 2: These parameters are characterized but not tested in manufacturing.

- **3:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

|        |        |                                                                         | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |       |       |                                      |  |

|--------|--------|-------------------------------------------------------------------------|-------------------------------------------------------|---------------------|-------|-------|--------------------------------------|--|

| Param. | Symbol | Characteristic                                                          | Min.                                                  | Typ. <sup>(2)</sup> | Max.  | Units | Conditions                           |  |

|        |        | Cloc                                                                    | k Parame                                              | ters                |       |       |                                      |  |

| AD50   | Tad    | ADC Clock Period                                                        | 117.6                                                 |                     | _     | ns    |                                      |  |

| AD51   | tRC    | ADC Internal RC Oscillator<br>Period                                    | —                                                     | 250                 |       | ns    |                                      |  |

|        |        | Con                                                                     | version R                                             | ate                 |       |       | ·                                    |  |

| AD55   | tCONV  | Conversion Time                                                         |                                                       | 14 Tad              |       | ns    |                                      |  |

| AD56   | FCNV   | Throughput Rate                                                         |                                                       | —                   | 500   | Ksps  |                                      |  |

| AD57   | TSAMP  | Sample Time                                                             | 3 Tad                                                 | _                   | _     |       |                                      |  |

|        |        | Timir                                                                   | ig Parame                                             | ters                |       |       |                                      |  |

| AD60   | tPCS   | Conversion Start from Sample<br>Trigger <sup>(1)</sup>                  | 2 Tad                                                 | —                   | 3 Tad | _     | Auto-Convert Trigger<br>not selected |  |

| AD61   | tPSS   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(1)</sup>           | 2 Tad                                                 | —                   | 3 Tad | _     |                                      |  |

| AD62   | tcss   | Conversion Completion to<br>Sample Start (ASAM = $1$ ) <sup>(1)</sup>   | —                                                     | 0.5 TAD             | —     |       |                                      |  |

| AD63   | tDPU   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(1)</sup> | —                                                     | —                   | 20    | μS    | See Note 3                           |  |

### TABLE 32-57: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

**Note 1:** Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

2: These parameters are characterized but not tested in manufacturing.

**3:** The tDPU parameter is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (ADxCON1<15>) = 1). During this time, the ADC result is indeterminate.

4: Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, Comparator and DAC will have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 32-11 for the minimum and maximum BOR values.

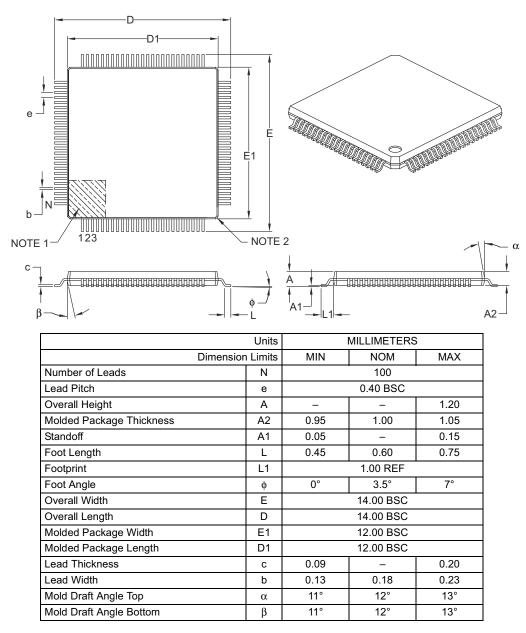

### 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2009-2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-62076-624-8

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.