Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 83                                                                             |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gu810-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4-12: PWM REGISTER MAP FOR dsPIC33EPXXX(MC/MU)806/810/814 DEVICES ONLY

| File Name | Addr. | Bit 15   | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8     | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3 | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

|-----------|-------|----------|--------|--------|--------|--------|--------|---------|-----------|--------|-------|--------|---------|-------|-------|------------|-------|---------------|

| PTCON     | 0C00  | PTEN     |        | PTSIDL | SESTAT | SEIEN  | EIPU   | SYNCPOL | SYNCOEN   | SYNCEN | SY    | NCSRC< | 2:0>    |       | SEV   | TPS<3:0>   |       | 0000          |

| PTCON2    | 0C02  | _        |        | _      | _      | _      | —      | _       | _         | _      | _     | _      | —       | —     |       | PCLKDIV<2: | 0>    | 0000          |

| PTPER     | 0C04  |          |        |        |        |        |        |         | PTPER<15  | 5:0>   |       |        |         |       |       |            |       | FFF8          |

| SEVTCMP   | 0C06  |          |        |        |        |        |        |         | SEVTCMP<  | 15:0>  |       |        |         |       |       |            |       | 0000          |

| MDC       | 0C0A  |          |        |        |        |        |        |         | MDC<15:   | 0>     |       |        |         |       |       |            |       | 0000          |

| STCON     | 0C0E  | _        | _      | _      | SESTAT | SEIEN  | EIPU   | SYNCPOL | SYNCOEN   | SYNCEN | SY    | NCSRC< | 2:0>    |       | SEV   | TPS<3:0>   |       | 0000          |

| STCON2    | 0C10  | _        |        | _      | _      | —      | _      | —       | —         | _      | _     | _      | _       | —     | I     | PCLKDIV<2: | 0>    | 0000          |

| STPER     | 0C12  |          |        |        |        |        |        |         | STPER<15  | 5:0>   |       |        |         |       |       |            |       | FFF8          |

| SSEVTCMP  | 0C14  |          |        |        |        |        |        | :       | SSEVTCMP< | :15:0> |       |        |         |       |       |            |       | 0000          |

| CHOP      | 0C1A  | CHPCLKEN |        | _      | —      | —      | —      |         |           |        |       | CHOPC  | _K<9:0> |       |       |            |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXX(MC/MU)806/810/814 DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14                                                                 | Bit 13                                                                                                                                                  | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8     | Bit 7    | Bit 6  | Bit 5 | Bit 4 | Bit 3   | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|-------|---------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|----------|-----------|----------|--------|-------|-------|---------|----------|---------|---------|---------------|

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT                                                                 | TRGSTAT                                                                                                                                                 | FLTIEN | CLIEN  | TRGIEN | ITB      | MDCS      | DTC<     | :1:0>  | DTCP  |       | MTBS    | CAM      | XPRES   | IUE     | 0000          |

| IOCON1    | 0C22  | PENH    | PENL                                                                   | POLH         POLL         PMOD<1:0>         OVRENH         OVRENL         OVRDAT<1:0>         FLTDAT<1:0>         CLDAT<1:0>         SWAP         OSYNC |        |        |        |          |           |          |        |       |       |         | 0000     |         |         |               |

| FCLCON1   | 0C24  | IFLTMOD |                                                                        | CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0>                                                                                                   |        |        |        |          |           |          |        |       |       | 0000    |          |         |         |               |

| PDC1      | 0C26  |         | PDC1<15:0> 00                                                          |                                                                                                                                                         |        |        |        |          |           |          |        | 0000  |       |         |          |         |         |               |

| PHASE1    | 0C28  |         | PHASE1<15:0> 000                                                       |                                                                                                                                                         |        |        |        |          |           |          |        | 0000  |       |         |          |         |         |               |

| DTR1      | 0C2A  | _       | — DTR1<13:0>                                                           |                                                                                                                                                         |        |        |        |          |           |          | 0000   |       |       |         |          |         |         |               |

| ALTDTR1   | 0C2C  | _       | _                                                                      |                                                                                                                                                         |        |        |        |          | A         | LTDTR1<1 | 3:0>   |       |       |         |          |         |         | 0000          |

| SDC1      | 0C2E  |         |                                                                        |                                                                                                                                                         |        |        |        |          | SDC1<15:0 | )>       |        |       |       |         |          |         |         | 0000          |

| SPHASE1   | 0C30  |         |                                                                        |                                                                                                                                                         |        |        |        | ç        | SPHASE1<1 | 5:0>     |        |       |       |         |          |         |         | 0000          |

| TRIG1     | 0C32  |         |                                                                        |                                                                                                                                                         |        |        |        |          | TRGCMP<1  | 5:0>     |        |       |       |         |          |         |         | 0000          |

| TRGCON1   | 0C34  |         | TRGDI                                                                  | V<3:0>                                                                                                                                                  |        | _      | _      | _        | _         | _        | _      |       |       | TRG     | STRT<5:0 | >       |         | 0000          |

| PWMCAP1   | 0C38  |         |                                                                        |                                                                                                                                                         |        |        |        | F        | WMCAP1<1  | 5:0>     |        |       |       |         |          |         |         | 0000          |

| LEBCON1   | 0C3A  | PHR     | R PHF PLR PLF FLTLEBEN CLLEBEN — — — — BCH BCL BPHH BPHL BPLH BPLL 000 |                                                                                                                                                         |        |        |        |          |           |          |        | 0000  |       |         |          |         |         |               |

| LEBDLY1   | 0C3C  | _       | -                                                                      | _                                                                                                                                                       | _      |        | •      | •        | •         |          | LEB<11 | :0>   |       |         | •        | •       | •       | 0000          |

| AUXCON1   | 0C3E  | _       |                                                                        | _                                                                                                                                                       | _      |        | BLANKS | SEL<3:0> |           | _        |        |       | CHOPS | EL<3:0> |          | CHOPHEN | CHOPLEN | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|                | • · . | ••••••   | .,                                                                                            | -, 0/    |        |        |        |       |          |             |          |       |              | -        | _     |        | -     |               |  |  |  |  |  |  |  |  |

|----------------|-------|----------|-----------------------------------------------------------------------------------------------|----------|--------|--------|--------|-------|----------|-------------|----------|-------|--------------|----------|-------|--------|-------|---------------|--|--|--|--|--|--|--|--|

| File Name      | Addr. | Bit 15   | Bit 14                                                                                        | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7       | Bit 6    | Bit 5 | Bit 4        | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |  |  |  |  |  |  |  |  |

| U1MODE         | 0220  | UARTEN   | _                                                                                             | USIDL    | IREN   | RTSMD  | _      | UEN<  | <1:0>    | WAKE        | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |  |  |  |  |  |  |  |  |

| U1STA          | 0222  | UTXISEL1 | UTXINV                                                                                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS       | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |  |  |  |  |  |  |  |  |

| U1TXREG        | 0224  | _        | _                                                                                             | _        | _      | —      | _      | _     |          |             |          | UART  | k Transmit F | Register |       |        |       | XXXX          |  |  |  |  |  |  |  |  |

| U1RXREG        | 0226  | _        | _                                                                                             | _        |        | —      | _      | —     |          |             |          | UART  | xReceive R   | egister  |       |        |       | 0000          |  |  |  |  |  |  |  |  |

| U1BRG          | 0228  |          |                                                                                               |          |        |        |        | Baud  | Rate Gen | erator Pres | scaler   |       |              |          |       |        |       | 0000          |  |  |  |  |  |  |  |  |

| U2MODE         | 0230  | UARTEN   |                                                                                               | USIDL    | IREN   | RTSMD  | —      | UEN<  | <1:0>    | WAKE        | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |  |  |  |  |  |  |  |  |

| U2STA          | 0232  | UTXISEL1 | UTXINV                                                                                        | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS       | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |  |  |  |  |  |  |  |  |

| U2TXREG        | 0234  | —        |                                                                                               |          |        | —      | —      | —     |          |             |          | UART  | k Transmit F | Register |       |        |       | XXXX          |  |  |  |  |  |  |  |  |

| U2RXREG        | 0236  | _        | UARTx Receive Register                                                                        |          |        |        |        |       |          |             | 0000     |       |              |          |       |        |       |               |  |  |  |  |  |  |  |  |

| U2BRG          | 0238  |          |                                                                                               |          |        |        |        | Baud  | Rate Gen | erator Pres | scaler   |       |              |          |       |        |       | 0000          |  |  |  |  |  |  |  |  |

| U3MODE         | 0250  | UARTEN   | _                                                                                             | USIDL    | IREN   | RTSMD  | —      | UEN<  | <1:0>    | WAKE        | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |  |  |  |  |  |  |  |  |

| U3STA          | 0252  | UTXISEL1 | UTXINV                                                                                        | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT     | URXIS       | SEL<1:0> | ADDEN | RIDLE        | PERR     | FERR  | OERR   | URXDA | 0110          |  |  |  |  |  |  |  |  |

| <b>U3TXREG</b> | 0254  | —        | _                                                                                             | _        | _      | —      | _      | —     |          |             |          | UART  | x Transmit F | Register |       |        |       | xxxx          |  |  |  |  |  |  |  |  |

| <b>U3RXREG</b> | 0256  | —        | —                                                                                             | —        | —      | —      | _      |       |          |             |          | UART  | x Receive R  | legister |       |        |       | 0000          |  |  |  |  |  |  |  |  |

| U3BRG          | 0258  |          |                                                                                               |          |        |        |        | Baud  | Rate Gen | erator Pres | scaler   | -     | -            |          |       |        | -     | 0000          |  |  |  |  |  |  |  |  |

| U4MODE         | 02B0  | UARTEN   | _                                                                                             | USIDL    | IREN   | RTSMD  | _      | UEN<  | <1:0>    | WAKE        | LPBACK   | ABAUD | URXINV       | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |  |  |  |  |  |  |  |  |

| U4STA          | 02B2  | UTXISEL1 | ISEL1 UTXINV UTXISEL0 — UTXBRK UTXEN UTXBF TRMT URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXDA |          |        |        |        |       |          |             | 0110     |       |              |          |       |        |       |               |  |  |  |  |  |  |  |  |

| U4TXREG        | 02B4  | _        | _                                                                                             | _        | _      | _      | _      | _     |          |             |          | UART  | k Transmit F | Register |       |        |       | xxxx          |  |  |  |  |  |  |  |  |

| U4RXREG        | 02B6  | _        | _                                                                                             | —        | _      | -      | _      | —     |          |             |          | UART  | x Receive R  | legister |       |        |       | 0000          |  |  |  |  |  |  |  |  |

| U4BRG          | 02B8  |          |                                                                                               |          |        |        |        | Baud  | Rate Gen | erator Pres | scaler   |       |              |          |       |        |       | 0000          |  |  |  |  |  |  |  |  |

|                |       |          |                                                                                               |          |        |        |        |       |          |             |          |       |              |          |       |        |       |               |  |  |  |  |  |  |  |  |

## TABLE 4-23: UART1, UART2, UART3 and UART4 REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER 5-2: | NVMADRU: NONVOLATILE MEMORY UPPER ADDRESS REGISTER |

|---------------|----------------------------------------------------|

|---------------|----------------------------------------------------|

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0             | U-0             | U-0   |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| —               | —     | —                | —     | —                | _               | —               | —     |

| bit 15          | •     |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | NVMAE | )RU<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared           | x = Bit is unkı | nown  |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

| 511 15-0 |                            |

bit 7-0 **NVMADRU<7:0>:** Nonvolatile Memory Upper Write Address bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-3: NVMADR: NONVOLATILE MEMORY ADDRESS REGISTER

| R/W-x          | R/W-x | R/W-x            | R/W-x | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|----------------|-------|------------------|-------|--------------|------------------|----------|-------|

|                |       |                  | NVMA  | DR<15:8>     |                  |          |       |

| bit 15         |       |                  |       |              |                  |          | bit 8 |

|                |       |                  |       |              |                  |          |       |

| R/W-x          | R/W-x | R/W-x            | R/W-x | R/W-x        | R/W-x            | R/W-x    | R/W-x |

|                |       |                  | NVMA  | DR<7:0>      |                  |          |       |

| bit 7          |       |                  |       |              |                  |          | bit 0 |

|                |       |                  |       |              |                  |          |       |

| Legend:        |       |                  |       |              |                  |          |       |

| R = Readable I | bit   | W = Writable bit | t     | U = Unimpler | mented bit, read | d as '0' |       |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 NVMADR<15:0>: Nonvolatile Memory Write Address bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| W-0   | W-0 | W-0 | W-0   | W-0     | W-0 | W-0 | W-0   |

|-------|-----|-----|-------|---------|-----|-----|-------|

|       |     |     | NVMKE | EY<7:0> |     |     |       |

| bit 7 |     |     |       |         |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

## 6.1 Resets Resources

Many useful resources related to Resets are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en554310              |

#### 6.1.1 KEY RESOURCES

- Section 8. "Reset" (DS70602) in the "dsPIC33E/ PIC24E Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- · Development Tools

## 6.2 RCON Control Register

All types of device Resets set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

| U-0                | R/W-0                                      | R/W-0                                                                                    | R/W-0                                          | R/W-0             | R/W-0         | R/W-0            | R/W-0 |

|--------------------|--------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|---------------|------------------|-------|

| _                  |                                            |                                                                                          |                                                | INT3R<6:0>        |               |                  |       |

| bit 15             | ŀ                                          |                                                                                          |                                                |                   |               |                  | bit 8 |

|                    |                                            |                                                                                          |                                                |                   |               |                  |       |

| U-0                | R/W-0                                      | R/W-0                                                                                    | R/W-0                                          | R/W-0             | R/W-0         | R/W-0            | R/W-0 |

| _                  |                                            |                                                                                          |                                                | INT2R<6:0>        |               |                  |       |

| bit 7              |                                            |                                                                                          |                                                |                   |               |                  | bit C |

|                    |                                            |                                                                                          |                                                |                   |               |                  |       |

| Legend:            |                                            |                                                                                          |                                                |                   |               |                  |       |

| R = Readab         |                                            | W = Writable                                                                             |                                                | U = Unimplem      |               |                  |       |

| -n = Value a       | at POR                                     | '1' = Bit is set                                                                         |                                                | '0' = Bit is clea | ared          | x = Bit is unkr  | nown  |

|                    | INT3R<6:0>:<br>(see Table 11               | I-2 for input pin                                                                        | al Interrupt 3 (<br>selection num              | ,                 | rresponding I | RPn/RPIn Pin bit | ts    |

| bit 15<br>bit 14-8 | INT3R<6:0><br>(see Table 11<br>1111111 = I | : Assign Externa<br>I-2 for input pin<br>nput tied to RP <sup>-</sup><br>nput tied to CM | al Interrupt 3 (<br>selection num<br>127<br>P1 | ,                 | rresponding I | RPn/RPIn Pin bil | ts    |

|                    | INT3R<6:0><br>(see Table 11<br>1111111 = I | : Assign Externa<br>I-2 for input pin<br>nput tied to RP1                                | al Interrupt 3 (<br>selection num<br>127<br>P1 | ,                 | rresponding I | RPn/RPIn Pin bil | is    |

#### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

## 17.2 QEI Control Registers

| R/W-0         | U-0                                                                                                 | R/W-0                                                                                                                    | R/W-0                                                                  | R/W-0                                                                                                            | R/W-0                                                  | R/W-0           | R/W-0                        |

|---------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------|------------------------------|

| QEIEN         |                                                                                                     | QEISIDL                                                                                                                  |                                                                        | PIMOD<2:0>                                                                                                       | [1]                                                    | IMV<            | 1:0> <b>(2)</b>              |

| bit 15        |                                                                                                     |                                                                                                                          |                                                                        |                                                                                                                  |                                                        |                 | bit                          |

| U-0           | R/W-0                                                                                               | R/W-0                                                                                                                    | R/W-0                                                                  | R/W-0                                                                                                            | R/W-0                                                  | R/W-0           | R/W-0                        |

| _             | -                                                                                                   | INTDIV<2:0> <sup>(3)</sup>                                                                                               |                                                                        | CNTPOL                                                                                                           | GATEN                                                  |                 | <1:0>                        |

| bit 7         |                                                                                                     | -                                                                                                                        |                                                                        |                                                                                                                  |                                                        |                 | bit                          |

| Legend:       |                                                                                                     |                                                                                                                          |                                                                        |                                                                                                                  |                                                        |                 |                              |

| R = Readable  | e bit                                                                                               | W = Writable b                                                                                                           | oit                                                                    | U = Unimpler                                                                                                     | mented bit, read                                       | d as '0'        |                              |

| -n = Value at | POR                                                                                                 | '1' = Bit is set                                                                                                         |                                                                        | '0' = Bit is cle                                                                                                 | ared                                                   | x = Bit is unkr | nown                         |

| bit 14        | 0 = Module co                                                                                       | ounters are ena<br>ounters are disa<br><b>ted:</b> Read as '0                                                            | abled, but SF                                                          | Rs can be read                                                                                                   | d or written to                                        |                 |                              |

|               | -                                                                                                   |                                                                                                                          |                                                                        |                                                                                                                  |                                                        |                 |                              |

| bit 13        | 1 = Discontine                                                                                      | I Stop in Idle M<br>ues module ope<br>s module opera                                                                     | eration when                                                           | device enters I<br>lode                                                                                          | dle mode                                               |                 |                              |

| bit 12-10     |                                                                                                     |                                                                                                                          |                                                                        | ion Mode Selec                                                                                                   | t bits <sup>(1)</sup>                                  |                 |                              |

|               | 101 = Resets<br>100 = Secon<br>registe<br>011 = First ir<br>registe<br>010 = Next ir<br>001 = Every | b Count mode for<br>a the position co<br>d index event a<br>r<br>ndex event after<br>ndex input even<br>index input even | ounter when<br>fter home event<br>fter home event<br>t initializes the | ounter<br>the position cou<br>ent initializes po<br>nt initializes po<br>ne position courter<br>position counter | osition counter<br>osition counter<br>oter with conten | with contents o | f the QEIxIC<br>of the QEIxI |

| bit 9-8       | IMV<1:0>: Ind                                                                                       | dex Match Valu                                                                                                           | e bits <sup>(2)</sup>                                                  |                                                                                                                  |                                                        |                 |                              |

|               | 10 = Index n<br>01 = Index n                                                                        | natch occurs wh<br>natch occurs wh<br>natch occurs wh<br>nput event does                                                 | nen QEB = 1<br>nen QEB = 0                                             | and QEA = 0<br>and QEA = 1                                                                                       |                                                        |                 |                              |

| bit 7         |                                                                                                     | ted: Read as '0                                                                                                          |                                                                        |                                                                                                                  |                                                        |                 |                              |

#### REGISTER 17-1: QEIxCON: QEIx CONTROL REGISTER

- 2: When CCM = 00, and QEA and QEB values match Index Match Value (IMV), the POSCNTH and POSCNTL registers are reset.

- 3: The selected clock rate should be at least twice the expected maximum quadrature count rate.

## 21.0 ENHANCED CAN (ECAN™) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/ 810/814 and PIC24EPXXX(GP/GU)810/ 814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70353) of the "dsPIC33E/ PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 devices contain two ECAN modules.

The ECANx module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN Specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN Specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details. The ECANx module features are as follows:

- Implementation of the CAN Protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and Extended Data Frames

- 0-8 Bytes Data Length

- Programmable Bit Rate up to 1 Mbit/sec

- Automatic Response to Remote Transmission Requests

- Up to 8 Transmit Buffers with Application-Specific Prioritization and Abort Capability (each buffer can contain up to 8 bytes of data)

- Up to 32 Receive Buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 Full (standard/extended identifier) Acceptance Filters

- Three Full Acceptance Filter Masks

- DeviceNet<sup>™</sup> Addressing Support

- Programmable Wake-up Functionality with Integrated Low-Pass Filter

- Programmable Loopback mode Supports Self-Test Operation

- Signaling via Interrupt Capabilities for all CAN Receiver and Transmitter Error States

- · Programmable Clock Source

- Programmable Link to Input Capture Module (IC2 for the ECAN1 and ECAN2 modules) for Time-Stamping and Network Synchronization

- · Low-Power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

## REGISTER 22-15: UxIR: USB INTERRUPT STATUS REGISTER (HOST MODE ONLY)

| U-0          | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |  |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| —            | —   | —   | —   | —   | —   | —   | —   |  |  |

| bit 15 bit 8 |     |     |     |     |     |     |     |  |  |

| R/K-0, HS | R-0    | R/K-0, HS |

|-----------|-----------|-----------|-----------|-----------|-----------|--------|-----------|

| STALLIF   | ATTACHIF  | RESUMEIF  | IDLEIF    | TRNIF     | SOFIF     | UERRIF | DETACHIF  |

| bit 7     |           |           |           |           |           |        | bit 0     |

| Legend:           | U = Unimplemented bit, read as '0' |                            |                    |  |  |  |

|-------------------|------------------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | K = Write '1' to clear bit         | HS = Hardware Settable bit |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

| bit 15-8 | Unimplemented: Read as '0'                                                                                                                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | STALLIF: STALL Handshake Interrupt bit                                                                                                                                                                                        |

|          | 1 = A STALL handshake was sent by the peripheral device during the handshake phase of the transaction in Device mode                                                                                                          |

|          | 0 = A STALL handshake has not been sent                                                                                                                                                                                       |

| bit 6    | ATTACHIF: Peripheral Attach Interrupt bit                                                                                                                                                                                     |

|          | 1 = A peripheral attachment has been detected by the module; set if the bus state is not SE0 and there has been no bus activity for 2.5 $\mu$ s                                                                               |

|          | 0 = No peripheral attachment is detected                                                                                                                                                                                      |

| bit 5    | RESUMEIF: Resume Interrupt bit                                                                                                                                                                                                |

|          | 1 = A K-State is observed on the D+ or D- pin for 2.5 μs (differential '1' for low speed, differential '0' for full speed)                                                                                                    |

|          | 0 = No K-State is observed                                                                                                                                                                                                    |

| bit 4    | IDLEIF: Idle Detect Interrupt bit                                                                                                                                                                                             |

|          | <ul> <li>1 = Idle condition is detected (constant Idle state of 3 ms or more)</li> <li>0 = No Idle condition is detected</li> </ul>                                                                                           |

| bit 3    | TRNIF: Token Processing Complete Interrupt bit                                                                                                                                                                                |

|          | <ul> <li>1 = Processing of current token is complete; read USTAT register for endpoint BDT information</li> <li>0 = Processing of current token is not complete; clear USTAT register or load next token from STAT</li> </ul> |

| bit 2    | SOFIF: Start-of-Frame Token Interrupt bit                                                                                                                                                                                     |

|          | <ul><li>1 = Start-of-Frame threshold is reached by the host</li><li>0 = No Start-of-Frame token threshold is reached</li></ul>                                                                                                |

| bit 1    | UERRIF: USB Error Condition Interrupt bit                                                                                                                                                                                     |

|          | 1 = An unmasked error condition has occurred; only error states enabled in the UxEIE register can set this bit                                                                                                                |

|          | 0 = No unmasked error condition has occurred                                                                                                                                                                                  |

| bit 0    | DETACHIF: Detach Interrupt bit                                                                                                                                                                                                |

|          | <ul> <li>1 = A peripheral detachment has been detected by the module</li> <li>0 = No peripheral detachment has been detected</li> </ul>                                                                                       |

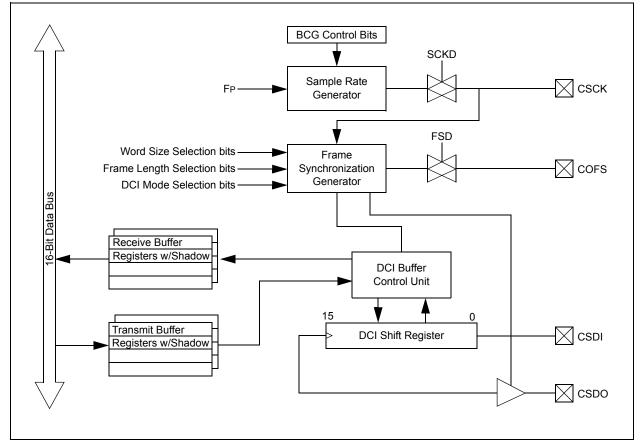

## 24.0 DATA CONVERTER INTERFACE (DCI) MODULE

- Note 1: This data sheet is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 20. Data Converter Interface (DCI)" (DS70356) of the "dsPIC33E/PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 24.1 Module Introduction

The Data Converter Interface (DCI) module allows simple interfacing of devices, such as audio coder/ decoders (Codecs), ADC and D/A Converters. The following interfaces are supported:

- Framed Synchronous Serial Transfer (Single or Multi-Channel)

- Inter-IC Sound (I<sup>2</sup>S) Interface

- AC-Link Compliant mode

General features include:

- Programmable word size up to 16 bits

- Supports up to 16 time slots, for a maximum frame size of 256 bits

- Data buffering for up to 4 samples without CPU overhead

FIGURE 24-1: DCI MODULE BLOCK DIAGRAM

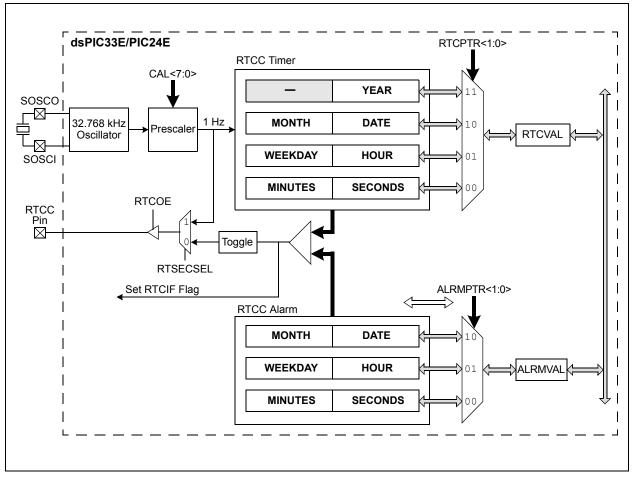

#### FIGURE 26-1: RTCC BLOCK DIAGRAM

## 26.1 Writing to the RTCC Timer

Note: To allow the RTCC module to be clocked by the secondary crystal oscillator, the Secondary Oscillator Enable (LPOSCEN) bit in the Oscillator Control (OSCCON<1>) register must be set. For further details, refer to Section 7. "Oscillator" (DS70580) in the "dsPIC33E/PIC24E Family Reference Manual".

The user application can configure the time and calendar by writing the desired seconds, minutes, hours, weekday, date, month and year to the RTCC registers. Under normal operation, writes to the RTCC Timer registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To write to the RTCC register, the RTCWREN bit (RCFGCAL<13>) must be set. Setting the RTCWREN bit allows writes to the RTCC registers. Conversely, clearing the RTCWREN bit prevents writes.

To set the RTCWREN bit, the following procedure must be executed. The RTCWREN bit can be cleared at any time:

- 1. Write 0x55 to NVMKEY.

- 2. Write 0xAA to NVMKEY.

- 3. Set the RTCWREN bit using a single-cycle instruction.

The RTCC module is enabled by setting the RTCEN bit (RCFGCAL<15>). To set or clear the RTCEN bit, the RTCWREN bit (RCFGCAL<13>) must be set.

If the entire clock (hours, minutes and seconds) needs to be corrected, it is recommended that the RTCC module should be disabled to avoid coincidental write operation when the timer increments. Therefore, it stops the clock from counting while writing to the RTCC Timer register.

## 26.2 RTCC Resources

Many useful resources related to RTCC are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the<br>product page using the link above, enter |

|-------|-----------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                               |

|       | http://www.microchip.com/wwwproducts/                                                   |

|       | Devices.aspx?dDocName=en554310                                                          |

#### 26.2.1 KEY RESOURCES

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS70584) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

| U-0             | U-0                                                           | U-0              | U-0 | U-0              | U-0   | U-0                     | U-0              |  |

|-----------------|---------------------------------------------------------------|------------------|-----|------------------|-------|-------------------------|------------------|--|

| —               | —                                                             | —                | —   | —                | —     | —                       | —                |  |

| bit 15          |                                                               |                  |     |                  |       |                         | bit 8            |  |

|                 |                                                               |                  |     |                  |       |                         |                  |  |

| U-0             | U-0                                                           | U-0              | U-0 | U-0              | U-0   | R/W-0                   | R/W-0            |  |

| _               | —                                                             | —                | —   | —                | —     | RTSECSEL <sup>(1)</sup> | PMPTTL           |  |

| bit 7           |                                                               | -                |     |                  |       |                         | bit 0            |  |

|                 |                                                               |                  |     |                  |       |                         |                  |  |

| Legend:         |                                                               |                  |     |                  |       |                         |                  |  |

| R = Readable    | = Readable bit W = Writable bit U = Unimplemented bit, read a |                  |     | d as '0'         |       |                         |                  |  |

| -n = Value at F | POR                                                           | '1' = Bit is set |     | '0' = Bit is cle | eared | x = Bit is unknow       | = Bit is unknown |  |

|                 |                                                               |                  |     |                  |       |                         |                  |  |

#### REGISTER 26-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| bit 15-2 | Unimplemented: Read as '0'                                                                                                         |

|----------|------------------------------------------------------------------------------------------------------------------------------------|

| bit 1    | RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(1)</sup>                                                                      |

|          | <ul> <li>1 = RTCC seconds clock is selected for the RTCC pin</li> <li>0 = RTCC alarm pulse is selected for the RTCC pin</li> </ul> |

| bit 0    | Not used by the RTCC module.                                                                                                       |

Not used by the RTCC module.

**Note 1:** To enable the actual RTCC output, the RTCOE bit (RCFGCAL<10>) must be set.

| DC CHA   | RACTER                                                                     | ISTICS                                                                                          | <b>Standar</b><br>(unless<br>Operatin | otherwi | ise stat | anditions: 3.0V to 3.6V<br>ed)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                                       |  |

|----------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| Param.   | Symbol                                                                     | Characteristic                                                                                  | Min.                                  | Тур.    | Max.     | Units                                                                                                                                           | Conditions                                            |  |

|          | Voi                                                                        | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins – All I/O Pins<br>except OSC2 and SOSCO  |                                       | _       | 0.4      | V                                                                                                                                               | $IOL \le 10 \text{ mA}, \text{ VDD} = 3.3 \text{V}$   |  |

| DO10 Vol | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins – OSC2 and<br>SOSCO | _                                                                                               | _                                     | 0.4     | V        | Iol $\leq$ 15 mA, Vdd = 3.3V                                                                                                                    |                                                       |  |

| D000     | Maria                                                                      | Output High Voltage<br>I/O Pins:<br>4x Sink Driver Pins – All I/O Pins<br>except OSC2 and SOSCO | 2.4                                   | _       | _        | V                                                                                                                                               | ІОН ≥ -10 mA, VDD = 3.3V                              |  |

| DO20     | Vон                                                                        | Output High Voltage<br>I/O Pins:<br>8x Sink Driver Pins – OSC2 and<br>SOSCO                     | 2.4                                   | _       | _        | V                                                                                                                                               | ІОн ≥ -15 mA, VDD = 3.3V                              |  |

|          |                                                                            | Output High Voltage                                                                             | 1.5 <sup>(1)</sup>                    | _       | —        |                                                                                                                                                 | IOH $\ge$ -14 mA, VDD = 3.3V                          |  |

|          |                                                                            | 4x Sink Driver Pins – All I/O Pins                                                              | 2.0 <sup>(1)</sup>                    | —       | —        | V                                                                                                                                               | ІОН ≥ -12 mA, VDD = 3.3V                              |  |

| DO20A    | Vout                                                                       | except OSC2 and SOSCO                                                                           | 3.0 <sup>(1)</sup>                    | _       | _        |                                                                                                                                                 | $IOH \ge -7 \text{ mA}, \text{ VDD} = 3.3 \text{V}$   |  |

| DOZUA    | VUHI                                                                       | Output High Voltage                                                                             | 1.5 <sup>(1)</sup>                    |         | _        |                                                                                                                                                 | $IOH \ge -22 \text{ mA}, \text{ VDD} = 3.3 \text{ V}$ |  |

|          |                                                                            | I/O Pins:<br>8x Sink Driver Pins – OSC2 and                                                     | 2.0 <sup>(1)</sup>                    |         | _        | V                                                                                                                                               | IOH ≥ -18 mA, VDD = 3.3V                              |  |

|          |                                                                            | SOSCO                                                                                           | 3.0 <sup>(1)</sup>                    |         | _        | ]                                                                                                                                               | IOH ≥ -10 mA, VDD = 3.3V                              |  |

Note 1: Parameters are characterized, but not tested.

#### TABLE 32-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to $3.6V^{(2)}$ (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |  |                     |      |      |       |            |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------------------|------|------|-------|------------|

| Param.             | Symbol | Characteristic                                                                                                                                                                                                |  | Min. <sup>(1)</sup> | Тур. | Max. | Units | Conditions |

| BO10               | VBOR   | BOR Event on VDD Transition<br>High-to-Low                                                                                                                                                                    |  | 2.7                 |      | 2.9  | V     | Vdd        |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

2: Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, Comparator and DAC will have degraded performance. Device functionality is tested but not characterized.

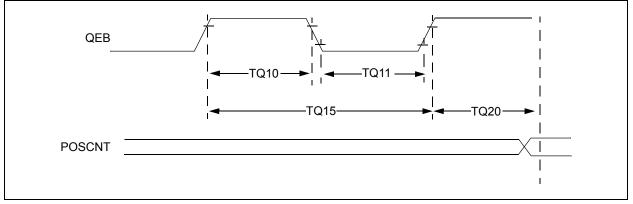

#### TABLE 32-26: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                          |   |     |    |                                  |

|--------------------|-----------|------------------------------------|------------------------------------------------------|------------------------------------------|---|-----|----|----------------------------------|

| Param.             | Symbol    | Characte                           | eristic <sup>(1)</sup>                               | Min. Typ. Max. Units Conditions          |   |     |    | Conditions                       |

| TQ10               | TtQH      | TQCK High<br>Time                  | Synchronous, with Prescaler                          | -                                        |   |     | ns | Must also meet<br>Parameter TQ15 |

| TQ11               | TtQL      | TQCK Low<br>Time                   | Synchronous, with Prescaler                          | [Greater of<br>(12.5 or 0.5 Tcy)/N] + 25 | _ | _   | ns | Must also meet<br>Parameter TQ15 |

| TQ15               | TtQP      | TQCP Input<br>Period               | Synchronous, with Prescaler                          | [Greater of (<br>25 or Tcy)/N] + 50      | _ | _   | ns |                                  |

| TQ20               | TCKEXTMRL | Delay from Exte<br>Clock Edge to T |                                                      | —                                        | 1 | Тсү | _  |                                  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

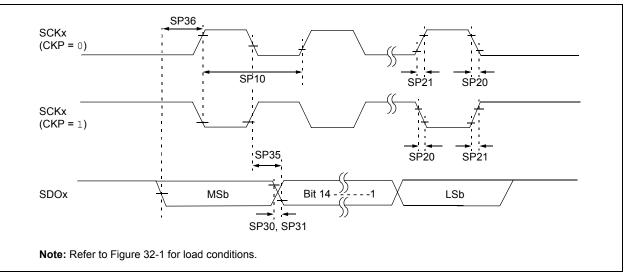

#### FIGURE 32-24: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

#### TABLE 32-42: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                                                                          |                                              |    | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |            |     |                                      |

|--------------------|------------------------------------------------------------------------------------------|----------------------------------------------|----|----------------------------------------------------------|------------|-----|--------------------------------------|

| Param.             | aram. Symbol Characteristic <sup>(1)</sup> Min. Typ. <sup>(2)</sup> Max. Units Condition |                                              |    |                                                          | Conditions |     |                                      |

| SP10               | TscP                                                                                     | Maximum SCKx Frequency                       |    | _                                                        | 15         | MHz | See Note 3                           |

| SP20               | TscF                                                                                     | SCKx Output Fall Time                        | -  | —                                                        |            | ns  | See Parameter DO32 and Note 4        |

| SP21               | TscR                                                                                     | SCKx Output Rise Time                        | -  | —                                                        |            | ns  | See Parameter DO31 and <b>Note 4</b> |

| SP30               | TdoF                                                                                     | SDOx Data Output Fall Time                   | -  | —                                                        | _          | ns  | See Parameter DO32 and <b>Note 4</b> |

| SP31               | TdoR                                                                                     | SDOx Data Output Rise Time                   | -  | —                                                        |            | ns  | See Parameter DO31 and Note 4        |

| SP35               | TscH2doV,<br>TscL2doV                                                                    | SDOx Data Output Valid after<br>SCKx Edge    | -  | 6                                                        | 20         | ns  |                                      |

| SP36               | TdiV2scH,<br>TdiV2scL                                                                    | SDOx Data Output Setup to<br>First SCKx Edge | 30 | —                                                        | _          | ns  |                                      |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

# TABLE 32-46:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

|        |                       |                                                                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |      |       |                                      |  |

|--------|-----------------------|------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|------|-------|--------------------------------------|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                                | Min.                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                           |  |

| SP70   | TscP                  | Maximum SCKx Input Frequency                                                 | _                                                     | _                   | 11   | MHz   | See Note 3                           |  |

| SP72   | TscF                  | SCKx Input Fall Time                                                         | —                                                     |                     |      | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP73   | TscR                  | SCKx Input Rise Time                                                         | —                                                     | _                   | _    | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP30   | TdoF                  | SDOx Data Output Fall Time                                                   | —                                                     | _                   | _    | ns    | See Parameter DO32 and <b>Note 4</b> |  |

| SP31   | TdoR                  | SDOx Data Output Rise Time                                                   | —                                                     | _                   | _    | ns    | See Parameter DO31 and <b>Note 4</b> |  |

| SP35   | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                    | —                                                     | 6                   | 20   | ns    |                                      |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                                 | 30                                                    | _                   |      | ns    |                                      |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                   | 30                                                    | _                   | _    | ns    |                                      |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                    | 30                                                    | —                   |      | ns    |                                      |  |

| SP50   | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx $\downarrow$<br>Input | 120                                                   | —                   | _    | ns    |                                      |  |

| SP51   | TssH2doZ              | SSx ↑ to SDOx Output,<br>High-Impedance                                      | 10                                                    | —                   | 50   | ns    | See Note 4                           |  |

| SP52   | TscH2ssH,<br>TscL2ssH | SSx ↑ after SCKx Edge                                                        | 1.5 Tcy + 40                                          | —                   | _    | ns    | See Note 4                           |  |

| SP60   | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                     | —                                                     | —                   | 50   | ns    |                                      |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCKx clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

NOTES:

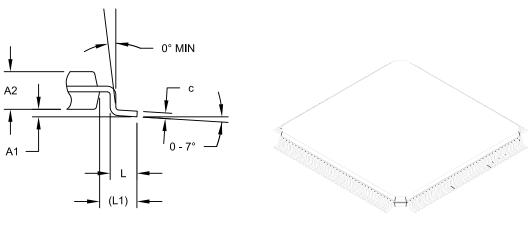

#### 144-Lead Plastic Thin Quad Flatpack (PH)-16x16x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | MILLIMETERS |             |      |      |  |  |

|-------------------------|-------------|-------------|------|------|--|--|

| Dimens                  | MIN         | NOM         | MAX  |      |  |  |

| Number of Pins          | N           | 144         |      |      |  |  |

| Lead Pitch              | е           | 0.40 BSC    |      |      |  |  |

| Overall Height          | A           | -           | -    | 1.20 |  |  |

| Molded PackageThickness | A2          | 0.95        | 1.00 | 1.05 |  |  |

| Standoff                | A1          | 0.05        | -    | 0.15 |  |  |

| Foot Length             | L           | 0.45        | 0.60 | 0.75 |  |  |

| Footprint               | L1          | 1.00 REF    |      |      |  |  |

| Overall Width           | D           | 18.00 BSC   |      |      |  |  |

| Overall Length          | E           | 18.00 BSC   |      |      |  |  |

| Molded Body Width       | D1          | 16.00 BSC   |      |      |  |  |

| Molded Body Length      | E1          | 16.00 BSC   |      |      |  |  |

| Lead Thickness          | С           | 0.09 - 0.20 |      |      |  |  |

| Lead Width              | b           | 0.13        | -    | 0.23 |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-155B Sheet 2 of 2

### TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                                                                                               | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |