Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 122                                                                            |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 144-LQFP                                                                       |

| Supplier Device Package    | 144-LQFP (20x20)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gu814-e-pl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

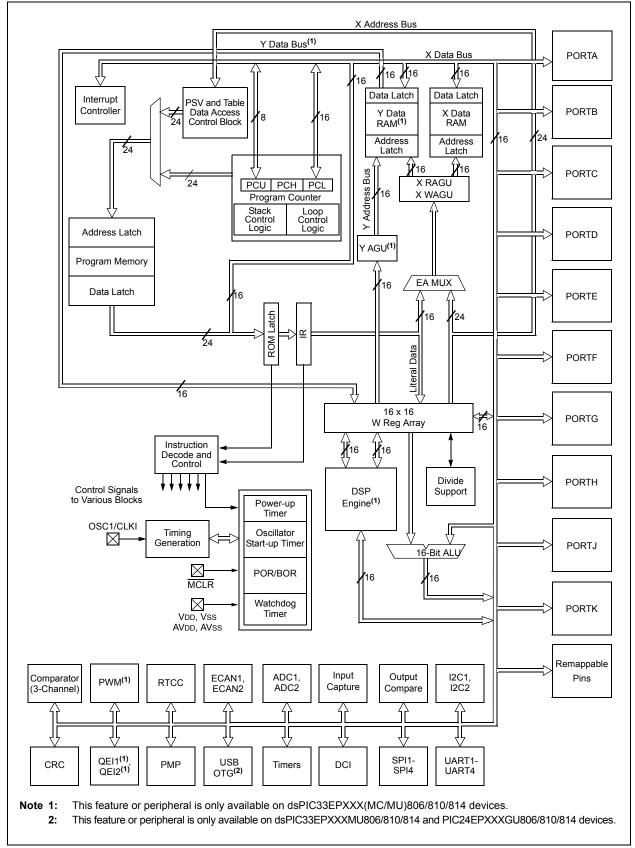

## FIGURE 3-1: dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 CPU BLOCK DIAGRAM

## 3.8 Arithmetic Logic Unit (ALU)

The ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

## 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.9 DSP Engine (dsPIC33EPXXX(GP/ MC/MU)806/810/814 Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulator-to-accumulator operations that require no additional data. These instructions are: ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed, unsigned or mixed-sign DSP multiply (US)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

|-------------|-------------------------|-------------------|

|             |                         |                   |

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

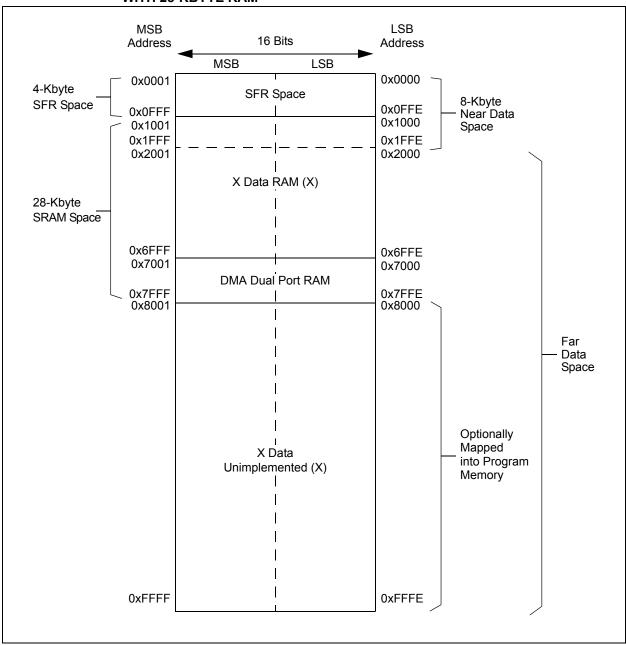

FIGURE 4-6: DATA MEMORY MAP FOR PIC24EP256GU810/814 DEVICES WITH 28-KBYTE RAM

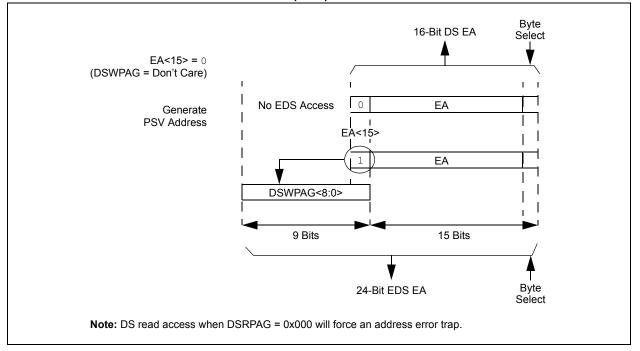

### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers DSxPAG, in combination with the upper half of data space address can provide up to 16 Mbytes of additional address space in the EDS and 12 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS, only. The data space and EDS can be read from and written to using DSRPAG and DSWPAG, respectively.

#### 4.4.2 EXTENDED X DATA SPACE

The lower half of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes (0x8000 to 0xFFFF) of Base Data Space, in combination with DSRPAG = 0x00 or DSWPAG = 0x00. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing DSxPAG in software has no effect.

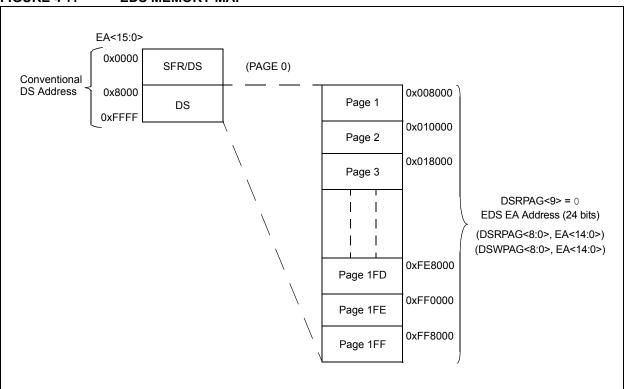

### FIGURE 4-7: EDS MEMORY MAP

The remaining pages including both EDS and PSV pages are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x01 or DSWPAG = 0x01, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the data space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x02 or DSWPAG = 0x02, accesses to the upper 32 Kbytes of the data space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-7.

For more information of the PSV page access using Data Space Page registers refer to **Section 4.5** "**Program Space Visibility from Data Space**" in **Section 4. "Program Memory"** (DS70613) of the "dsPIC33E/PIC24E Family Reference Manual".

| REGISTER        | 10-1: PMD1                      | I: PERIPHER                                                         |                        | E DISABLE C      | ONTROL RE             | GISTER 1             |                |

|-----------------|---------------------------------|---------------------------------------------------------------------|------------------------|------------------|-----------------------|----------------------|----------------|

| R/W-0           | R/W-0                           | R/W-0                                                               | R/W-0                  | R/W-0            | R/W-0                 | R/W-0                | R/W-0          |

| T5MD            | T4MD                            | T3MD                                                                | T2MD                   | T1MD             | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> | DCIMD          |

| bit 15          |                                 |                                                                     |                        |                  |                       |                      | bit 8          |

| DAMA            | DAMA                            | DAALO                                                               | DAMA                   | DAMA             | DAMA                  | DANO                 | DAMA           |

| R/W-0           | R/W-0                           | R/W-0                                                               | R/W-0                  | R/W-0            | R/W-0                 | R/W-0                | R/W-0          |

| l2C1MD<br>bit 7 | U2MD                            | U1MD                                                                | SPI2MD                 | SPI1MD           | C2MD                  | C1MD                 | AD1MD<br>bit ( |

|                 |                                 |                                                                     |                        |                  |                       |                      | bit t          |

| Legend:         |                                 |                                                                     |                        |                  |                       |                      |                |

| R = Readable    | e bit                           | W = Writable                                                        | bit                    | U = Unimpler     | nented bit, rea       | d as '0'             |                |

| -n = Value at   | POR                             | '1' = Bit is set                                                    |                        | '0' = Bit is cle | ared                  | x = Bit is unkno     | own            |

| bit 15          | 1 = Timer5 m                    | 5 Module Disat<br>odule is disable<br>odule is enable               | ed                     |                  |                       |                      |                |

| bit 14          | 1 = Timer4 m                    | 4 Module Disat<br>odule is disable<br>odule is enable               | ed                     |                  |                       |                      |                |

| bit 13          | 1 = Timer3 m                    | 3 Module Disat<br>odule is disable<br>odule is enable               | ed                     |                  |                       |                      |                |

| bit 12          | 1 = Timer2 m                    | 2 Module Disat<br>odule is disable<br>odule is enable               | ed                     |                  |                       |                      |                |

| bit 11          | 1 = Timer1 m                    | 1 Module Disat<br>odule is disable<br>odule is enable               | ed                     |                  |                       |                      |                |

| bit 10          | 1 = QEI1 mod                    | I1 Module Disa<br>dule is disabled<br>dule is enabled               | ble bit <sup>(1)</sup> |                  |                       |                      |                |

| bit 9           | <b>PWMMD:</b> PW<br>1 = PWM mod | /M Module Disa<br>dule is disabled<br>dule is enabled               |                        |                  |                       |                      |                |

| bit 8           |                                 | Module Disable<br>ule is disabled<br>ule is enabled                 | e bit                  |                  |                       |                      |                |

| bit 7           | 1 = I2C1 mod                    | 1 Module Disat<br>lule is disabled<br>lule is enabled               | le bit                 |                  |                       |                      |                |

| bit 6           | 1 = UART2 m                     | 2 Module Disa<br>odule is disabl                                    | ed                     |                  |                       |                      |                |

| bit 5           | 1 = UART1 m                     | <sup>-</sup> 1 Module Disa<br>nodule is disable<br>nodule is enable | ed                     |                  |                       |                      |                |

| bit 4           | 1 = SPI2 mod                    | 2 Module Disal<br>lule is disabled<br>lule is enabled               | ble bit                |                  |                       |                      |                |

| REGISTER 10-1: | PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 |

|----------------|----------------------------------------------------|

| REGISTER ID-1. | FMDT. FERIFIERAL MODULE DISABLE CONTROL REGISTER T |

Note 1: This bit is available on dsPIC33EPXXX(MC/MU)806/810/814 devices only.

| U-0          | R/W-0        | R/W-0                                                                      | R/W-0     | R/W-0             | R/W-0           | R/W-0            | R/W-0  |

|--------------|--------------|----------------------------------------------------------------------------|-----------|-------------------|-----------------|------------------|--------|

|              |              |                                                                            |           | U1CTSR<6:02       | >               |                  |        |

| bit 15       |              |                                                                            |           |                   |                 |                  | bit 8  |

| U-0          | R/W-0        | R/W-0                                                                      | R/W-0     | R/W-0             | R/W-0           | R/W-0            | R/W-0  |

|              | 10.00-0      | 10.00-0                                                                    | 10.00-0   | U1RXR<6:0>        |                 | 1000-0           | 1000-0 |

| bit 7        |              |                                                                            |           | 01101110.0        |                 |                  | bit 0  |

|              |              |                                                                            |           |                   |                 |                  |        |

| Legend:      |              |                                                                            |           |                   |                 |                  |        |

| R = Readab   | ole bit      | W = Writable                                                               | bit       | U = Unimplen      | nented bit, rea | d as '0'         |        |

| -n = Value a | it POR       | '1' = Bit is set                                                           |           | '0' = Bit is clea | ared            | x = Bit is unkr  | nown   |

|              | 1111111 = lr | -2 for input pin<br>nput tied to RP<br>nput tied to CM<br>nput tied to Vss | 127<br>P1 |                   |                 |                  |        |

| bit 7        | Unimplemen   | nted: Read as '                                                            | 0'        |                   |                 |                  |        |

| bit 6-0      |              | <ul> <li>Assign UART</li> <li>2 for input pin</li> </ul>                   |           |                   | rresponding R   | Pn/RPIn Pin bits | 3      |

## REGISTER 11-19: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

## dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

## REGISTER 11-55: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0    | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------------|-------|-------|-------|-------|-------|

| —      | —   | RP108R<5:0> |       |       |       |       |       |

| bit 15 |     |             |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------------|-------|-------|-------|-------|-------|

| —     | —   | RP104R<5:0> |       |       |       |       |       |

| bit 7 |     |             |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                                    |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| bit 15-14 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

| bit 13-8 | <b>RP108R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP108 Output Pin bits |

|----------|-------------------------------------------------------------------------------------------|

|          | (see Table 11-3 for peripheral function numbers)                                          |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP104R<5:0>:** Peripheral Output Function is Assigned to RP104 Output Pin bits (see Table 11-3 for peripheral function numbers)

## REGISTER 11-56: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12

| U-0    | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------------|-------|-------|-------|-------|-------|

| —      | —   | RP112R<5:0> |       |       |       |       |       |

| bit 15 |     |             |       |       |       |       | bit 8 |

| U-0   | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------------|-------|-------|-------|-------|-------|

| —     | —   | RP109R<5:0> |       |       |       |       |       |

| bit 7 |     |             |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP112R<5:0>:** Peripheral Output Function is Assigned to RP112 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RP109R<5:0>:** Peripheral Output Function is Assigned to RP109 Output Pin bits (see Table 11-3 for peripheral function numbers)

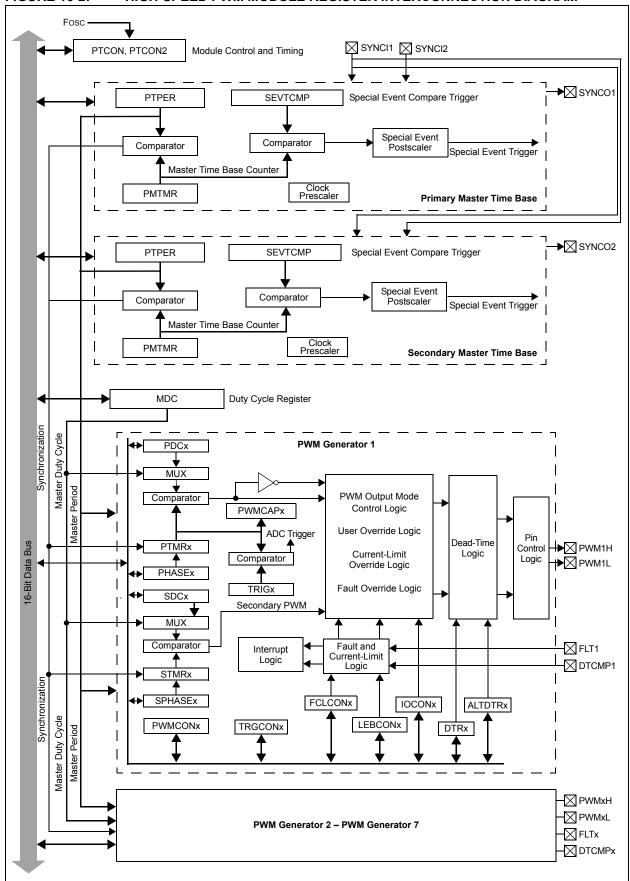

FIGURE 16-2: HIGH-SPEED PWM MODULE REGISTER INTERCONNECTION DIAGRAM

## REGISTER 16-19: IOCONX: PWMx I/O CONTROL REGISTER (CONTINUED)

| bit 3-2 | CLDAT<1:0>: Data for PWMxH and PWMxL Pins if CLMOD is Enabled bits                                                                                                                                              |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | IFLTMOD (FCLCONx<15>) = 0: Normal Fault mode:                                                                                                                                                                   |

|         | If current limit is active, PWMxH is driven to the state specified by CLDAT<1>.                                                                                                                                 |

|         | If current limit is active, PWMxL is driven to the state specified by CLDAT<0>.                                                                                                                                 |

|         | IFLTMOD (FCLCONx<15>) = 1: Independent Fault mode:                                                                                                                                                              |

|         | The CLDAT<1:0> bits are ignored.                                                                                                                                                                                |

| bit 1   | SWAP: Swap PWMxH and PWMxL Pins bit                                                                                                                                                                             |

|         | 1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins                                                                                                              |

|         | 0 = PWMxH and PWMxL pins are mapped to their respective pins                                                                                                                                                    |

| bit 0   | OSYNC: Output Override Synchronization bit                                                                                                                                                                      |

|         | <ul> <li>1 = Output overrides via the OVRDAT&lt;1:0&gt; bits are synchronized to the PWM time base</li> <li>0 = Output overrides via the OVDDAT&lt;1:0&gt; bits occur on the next CPU clock boundary</li> </ul> |

|         |                                                                                                                                                                                                                 |

Note 1: These bits should not be changed after the PWM module is enabled (PTEN = 1).

## REGISTER 18-1: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 1 | SPITBF: SPIx Transmit Buffer Full Status bit                                                                                                                                                                                                                       |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Transmit has not yet started, SPIx transmit buffer is full</li> <li>0 = Transmit has started, SPIx transmit buffer is empty</li> </ul>                                                                                                                |

|       | <u>Standard Buffer Mode:</u><br>Automatically set in hardware when the core writes to the SPIxBUF location, loading the SPIx transmit<br>buffer. Automatically cleared in hardware when the SPIx module transfers data from the SPIx transmit<br>buffer to SPIxSR. |

|       | Enhanced Buffer Mode:<br>Automatically set in hardware when CPU writes to the SPIxBUF location, loading the last available<br>buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write<br>operation.                 |

| bit 0 | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                                                                        |

|       | <ul> <li>1 = Receive complete, SPIx receive buffer is full</li> <li>0 = Receive is incomplete, SPIx receive buffer is empty</li> </ul>                                                                                                                             |

|       | <u>Standard Buffer Mode:</u><br>Automatically set in hardware when SPIx transfers data from SPIxSR to the SPIx receive buffer.<br>Automatically cleared in hardware when the core reads the SPIxBUF location, reading the SPIx<br>receive buffer.                  |

|       | Enhanced Buffer Mode:<br>Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last<br>unread buffer location. Automatically cleared in hardware when a buffer location is available for a                                 |

transfer from SPIxSR.

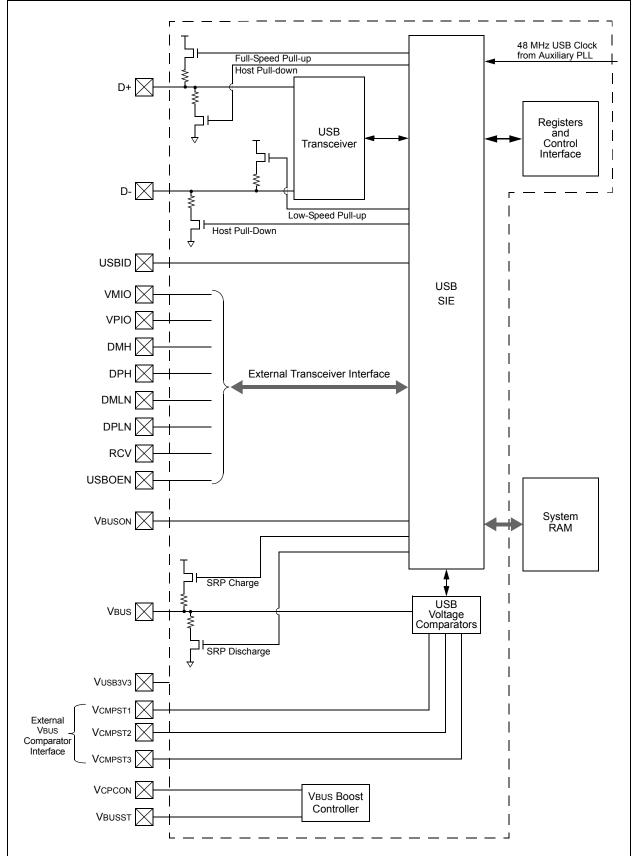

## FIGURE 22-1: USB INTERFACE DIAGRAM

## 23.2 ADC Helpful Tips

- 1. The SMPIx control bits in the ADxCON2 registers:

- a) Determine when the ADC interrupt flag is set and an interrupt is generated, if enabled.

- b) When the CSCNA bit in the ADxCON2 register is set to '1', this determines when the ADC analog scan channel list, defined in the AD1CSSL/AD1CSSH registers, starts over from the beginning.

- c) When the DMA peripheral is not used (ADDMAEN = 0), this determines when the ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0.

- d) When the DMA peripheral is used (ADDMAEN = 1), this determines when the DMA Address Pointer is incremented after a sample/conversion operation. ADC1BUF0 is the only ADC buffer used in this mode. The ADC Result Buffer Pointer to ADC1BUF0-ADC1BUFF gets reset back to the beginning at ADC1BUF0. The DMA address is incremented after completion of every 32nd sample/conversion operation. Conversion results are stored in the ADC1BUF0 register for transfer to RAM using DMA.

- 2. When the DMA module is disabled (ADDMAEN = 0), the ADC has 16 result buffers. ADC conversion results are stored sequentially in ADC1BUF0-ADC1BUFF, regardless of which analog inputs are being used subject to the SMPIx bits and the condition described in 1c) above. There is no relationship between the ANx input being measured and which ADC buffer (ADC1BUF0-ADC1BUFF) that the conversion results will be placed in.

- 3. When the DMA module is disabled (ADDMAEN = 1), the ADC module has only 1 ADC result buffer (i.e., ADC1BUF0) per ADC peripheral and the ADC conversion result must be read, either by the CPU or DMA controller, before the next ADC conversion is complete to avoid overwriting the previous value.

- 4. The DONE bit (ADxCON1<0>) is only cleared at the start of each conversion and is set at the completion of the conversion, but remains set indefinitely, even through the next sample phase until the next conversion begins. If application code is monitoring the DONE bit in any kind of software loop, the user must consider this behavior because the CPU code execution is faster than the ADC. As a result, in Manual Sample mode, particularly where the user's code is setting the SAMP bit (ADxCON1<1>), the DONE bit should also be cleared by the user application just before setting the SAMP bit.

## 23.3 ADC Resources

Many useful resources related to Analog-to-Digital conversion are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en554310                                        |

### 23.3.1 KEY RESOURCES

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33E/PIC24E Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related *"dsPIC33E/PIC24E Family Reference Manual"* Sections

- Development Tools

| U-0                                                                  | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0                     | U-0    |

|----------------------------------------------------------------------|-----|------------------|-----|-----------------------------------------|-----|-------------------------|--------|

| —                                                                    | —   | —                | —   | —                                       | —   | —                       | —      |

| bit 15                                                               |     |                  |     |                                         |     |                         | bit 8  |

|                                                                      |     |                  |     |                                         |     |                         |        |

| U-0                                                                  | U-0 | U-0              | U-0 | U-0                                     | U-0 | R/W-0                   | R/W-0  |

| _                                                                    | _   | —                | —   | —                                       | —   | RTSECSEL <sup>(1)</sup> | PMPTTL |

| bit 7                                                                |     | -                |     |                                         |     |                         | bit 0  |

|                                                                      |     |                  |     |                                         |     |                         |        |

| Legend:                                                              |     |                  |     |                                         |     |                         |        |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  |     | d as '0'                                |     |                         |        |

| -n = Value at F                                                      | POR | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |                         | wn     |

|                                                                      |     |                  |     |                                         |     |                         |        |

#### REGISTER 26-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| bit 15-2 | Unimplemented: Read as '0'                                                                                                         |

|----------|------------------------------------------------------------------------------------------------------------------------------------|

| bit 1    | RTSECSEL: RTCC Seconds Clock Output Select bit <sup>(1)</sup>                                                                      |

|          | <ul> <li>1 = RTCC seconds clock is selected for the RTCC pin</li> <li>0 = RTCC alarm pulse is selected for the RTCC pin</li> </ul> |

| bit 0    | Not used by the RTCC module.                                                                                                       |

Not used by the RTCC module.

**Note 1:** To enable the actual RTCC output, the RTCOE bit (RCFGCAL<10>) must be set.

| <b>TABLE 32-17:</b> | PLL CI | OCK TIMING | SPECIFICATIONS |

|---------------------|--------|------------|----------------|

|---------------------|--------|------------|----------------|

|                              |       |                                                                  | Standard (<br>Operating |      | ure -40°            | $C \le TA \le$ | +85°C f | unless otherwise stated)<br>or Industrial<br>for Extended |

|------------------------------|-------|------------------------------------------------------------------|-------------------------|------|---------------------|----------------|---------|-----------------------------------------------------------|

| Param. Symbol Characteristic |       |                                                                  | tic                     | Min. | Typ. <sup>(1)</sup> | Max.           | Units   | Conditions                                                |

| OS50                         | Fplli | PLL Voltage Controll<br>Oscillator (VCO) Inpu<br>Frequency Range |                         | 0.8  |                     | 8.0            | MHz     | ECPLL, XTPLL modes                                        |

| OS51                         | Fsys  | On-Chip VCO Syster<br>Frequency                                  | n                       | 120  | _                   | 340            | MHz     |                                                           |

| OS52                         | TLOCK | PLL Start-up Time (L                                             | ock Time)               | 0.9  | 1.5                 | 3.1            | mS      |                                                           |

| OS53                         | DCLK  | CLKO Stability (Jitter                                           | ·) <sup>(2)</sup>       | -5   | 0.5                 | 5              | %       |                                                           |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if FOSC = 120 MHz and the SPI bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

# TABLE 32-18: AUXILIARY PLL CLOCK TIMING SPECIFICATIONS (dsPIC33EPXXXMU8XX AND PIC24EPXXXGU8XX DEVICES ONLY)

| AC CHARACTERISTICS |        |                                                                     |      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise<br>stated)Stated) $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |      |       |            |                    |  |

|--------------------|--------|---------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--------------------|--|

| Param.             | Symbol | Characteris                                                         | Min. | Typ. <sup>(1)</sup>                                                                                                                                                                           | Max. | Units | Conditions |                    |  |

| OS54               | AFplli | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |      | 3                                                                                                                                                                                             | _    | 5.5   | MHz        | ECPLL, XTPLL modes |  |

| OS55               | AFsys  | On-Chip VCO System<br>Frequency                                     |      | 60                                                                                                                                                                                            | —    | 120   | MHz        |                    |  |

| OS56               | ATLOCK | PLL Start-up Time (Lock Time)                                       |      | 0.9                                                                                                                                                                                           | 1.5  | 3.1   | mS         |                    |  |

| OS57               | ADCLK  | CLKO Stability (Jitter                                              | .)   | -2                                                                                                                                                                                            | 0.25 | 2     | %          |                    |  |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

|        |        |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V (see Note 1)} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |           |           |         |                                                  |  |

|--------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|---------|--------------------------------------------------|--|

| Param. | Symbol | Characteristic                 | Min.                                                                                                                                                                                                                                                                                                 | Тур.      | Max.      | Units   | Conditions                                       |  |

|        |        | ADC Accuracy (12-Bit Mod       | de) – Mea                                                                                                                                                                                                                                                                                            | sureme    | nts with  | Externa | I VREF+/VREF-                                    |  |

| AD20a  | Nr     | Resolution                     | 12                                                                                                                                                                                                                                                                                                   | 2 Data Bi | ts        | bits    |                                                  |  |

| AD21a  | INL    | Integral Nonlinearity          | -2                                                                                                                                                                                                                                                                                                   |           | +2        | LSb     | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD22a  | DNL    | Differential Nonlinearity      | >-1                                                                                                                                                                                                                                                                                                  | -         | <1        | LSb     | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD23a  | Gerr   | Gain Error                     | 1.25                                                                                                                                                                                                                                                                                                 | 1.5       | 3         | LSb     | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD24a  | EOFF   | Offset Error                   | 1.25                                                                                                                                                                                                                                                                                                 | 1.52      | 2         | LSb     | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD25a  | —      | Monotonicity                   | _                                                                                                                                                                                                                                                                                                    | _         | _         | —       | Guaranteed <sup>(2)</sup>                        |  |

|        |        | ADC Accuracy (12-Bit Mo        | de) – Mea                                                                                                                                                                                                                                                                                            | asureme   | ents with | Interna | I VREF+/VREF-                                    |  |

| AD20a  | Nr     | Resolution                     | 1:                                                                                                                                                                                                                                                                                                   | 2 data bi | ts        | bits    |                                                  |  |

| AD21a  | INL    | Integral Nonlinearity          | -2                                                                                                                                                                                                                                                                                                   | _         | +2        | LSb     | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD22a  | DNL    | Differential Nonlinearity      | >-1                                                                                                                                                                                                                                                                                                  | _         | <1        | LSb     | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD23a  | Gerr   | Gain Error                     | 2                                                                                                                                                                                                                                                                                                    | 3         | 7         | LSb     | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD24a  | EOFF   | Offset Error                   | 2                                                                                                                                                                                                                                                                                                    | 3         | 5         | LSb     | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD25a  | —      | Monotonicity                   | _                                                                                                                                                                                                                                                                                                    |           |           | _       | Guaranteed <sup>(2)</sup>                        |  |

|        |        | Dynamie                        | c Perform                                                                                                                                                                                                                                                                                            | nance (1  | 2-Bit Mo  | de)     |                                                  |  |

| AD30a  | THD    | Total Harmonic Distortion      | —                                                                                                                                                                                                                                                                                                    | _         | -75       | dB      |                                                  |  |

| AD31a  | SINAD  | Signal to Noise and Distortion | 68.5                                                                                                                                                                                                                                                                                                 | 69.5      | _         | dB      |                                                  |  |

| AD32a  | SFDR   | Spurious Free Dynamic<br>Range | 80                                                                                                                                                                                                                                                                                                   | -         | _         | dB      |                                                  |  |

| AD33a  | Fnyq   | Input Signal Bandwidth         | —                                                                                                                                                                                                                                                                                                    | _         | 250       | kHz     |                                                  |  |

| AD34a  | ENOB   | Effective Number of Bits       | 11.09                                                                                                                                                                                                                                                                                                | 11.3      | _         | bits    |                                                  |  |

## TABLE 32-55: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, Comparator and DAC will have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 32-11 for the minimum and maximum BOR values.

2: The Analog-to-Digital conversion result never decreases with an increase in input voltage and has no missing codes.

| AC CHARACTERISTICS |        |                                                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V (see Note 4) \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |       |       |                                      |

|--------------------|--------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|-------|--------------------------------------|

| Param.             | Symbol | Characteristic                                                          | Min.                                                                                                                                                                                                                                                                                          | Typ. <sup>(1)</sup> | Max.  | Units | Conditions                           |

|                    |        | Cloc                                                                    | k Parame                                                                                                                                                                                                                                                                                      | eters               |       |       |                                      |

| AD50               | TAD    | ADC Clock Period                                                        | 76                                                                                                                                                                                                                                                                                            | _                   | _     | ns    |                                      |

| AD51               | tRC    | ADC Internal RC Oscillator Period                                       |                                                                                                                                                                                                                                                                                               | 250                 | _     | ns    |                                      |

|                    |        | Con                                                                     | version F                                                                                                                                                                                                                                                                                     | Rate                |       |       |                                      |

| AD55               | tCONV  | Conversion Time                                                         |                                                                                                                                                                                                                                                                                               | 12 TAD              | _     | —     |                                      |

| AD56               | FCNV   | Throughput Rate                                                         | —                                                                                                                                                                                                                                                                                             | -                   | 1.1   | Msps  | Using sequential<br>sampling         |

| AD57               | TSAMP  | Sample Time                                                             | 2 Tad                                                                                                                                                                                                                                                                                         | —                   | _     | —     |                                      |

|                    |        | Timin                                                                   | g Param                                                                                                                                                                                                                                                                                       | eters               |       |       |                                      |

| AD60               | tPCS   | Conversion Start from Sample<br>Trigger <sup>(2)</sup>                  | 2 Tad                                                                                                                                                                                                                                                                                         | —                   | 3 Tad | —     | Auto-Convert Trigger<br>not selected |

| AD61               | tPSS   | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2)</sup>           | 2 Tad                                                                                                                                                                                                                                                                                         | —                   | 3 Tad | —     |                                      |

| AD62               | tcss   | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2)</sup>      | —                                                                                                                                                                                                                                                                                             | 0.5 Tad             | _     | —     |                                      |

| AD63               | tdpu   | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(2)</sup> | —                                                                                                                                                                                                                                                                                             | —                   | 20    | μs    | See Note 3                           |

## TABLE 32-58: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz may affect linearity performance, especially at elevated temperatures.

**3:** The tDPU parameter is the time required for the ADC module to stabilize at the appropriate level when the module is turned on (ADON (ADxCON1<15>) = 1). During this time, the ADC result is indeterminate.

4: Device is functional at VBORMIN < VDD < VDDMIN. Analog modules: ADC, Comparator and DAC will have degraded performance. Device functionality is tested but not characterized. Refer to Parameter BO10 in Table 32-11 for the minimum and maximum BOR values.

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

|                                                                                                                                                                                                                                                                                                                                                                                                                   | ge. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Architecture:       33       =       16-bit Digital Signal Controller         24       =       16-bit Microcontroller                                                                                                                                                                                                                                                                                             |     |

| Flash Memory Family: EP = Enhanced Performance                                                                                                                                                                                                                                                                                                                                                                    |     |

| Product Group:       MU8 = Motor Control family with USB         GU8 = General Purpose family with USB                                                                                                                                                                                                                                                                                                            |     |

| Pin Count:         06         =         64-pin           10         =         100-pin, 121-pin           14         =         144-pin                                                                                                                                                                                                                                                                             |     |

| Temperature Range:I= $-40^{\circ}$ C to+85°C (Industrial)E= $-40^{\circ}$ C to+125°C (Extended)                                                                                                                                                                                                                                                                                                                   |     |

| Package:       PT       =       10x10 or 12x12 mm TQFP (Thin Quad Flatpack)         PF       =       14x14 mm TQFP (Thin Quad Flatpack)         MR       =       9x9 mm QFN (Plastic Quad Flatpack)         BG       =       10x10 mm TFBGA (Plastic Thin Profile Ball Grid Array)         PH       =       16x16 mm TQFP (Thin Quad Flatpack)         PL       =       20x20 mm LQFP (Low-Profile Quad Flatpack) |     |

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hangzhou Tel: 86-571-2819-3187

Fax: 86-571-2819-3189 China - Hong Kong SAR Tel: 852-2401-1200

Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka Tel: 81-66-152-7160 Fax: 81-66-152-9310

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-536-4818 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

## EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820