Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 60 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 122                                                                            |

| Program Memory Size        | 512KB (170K x 24)                                                              |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 24K x 16                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 144-TQFP                                                                       |

| Supplier Device Package    | 144-TQFP (16x16)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24ep512gu814-i-ph |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

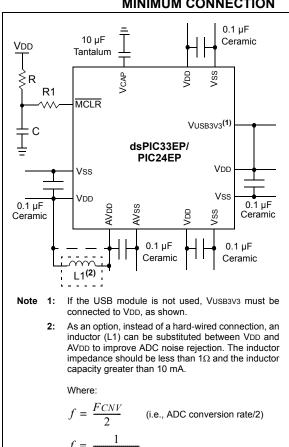

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7 µF to 47 µF.

#### 2.3 **CPU Logic Filter Capacitor** Connection (VCAP)

A low-ESR (< 1 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7 µF (10 µF is recommended), 16V connected to ground. The type can be ceramic or tantalum. See Section 32.0 "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See Section 29.2 "On-Chip Voltage Regulator" for details.

#### Master Clear (MCLR) Pin 2.4

The MCLR pin provides two specific device functions:

- · Device Reset

- · Device Programming and Debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

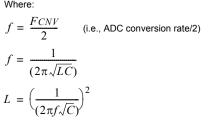

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### EXAMPLE OF MCLR PIN FIGURE 2-2: CONNECTIONS

- **Note 1:**  $R \leq 10 \text{ k}\Omega$  is recommended. A suggested starting value is 10 k $\Omega$ . Ensure that the MCLR pin VIH and VIL specifications are met.

- $R1 \leq 470\Omega$  will limit any current flowing into 2: MCLR from the external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met.

#### REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2 | <ul> <li>SFA: Stack Frame Active Status bit</li> <li>1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and DSWPAG values</li> </ul> |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space                                                                                            |

| bit 1 | RND: Rounding Mode Select bit <sup>(1)</sup>                                                                                                                            |

|       | <ul><li>1 = Biased (conventional) rounding is enabled</li><li>0 = Unbiased (convergent) rounding is enabled</li></ul>                                                   |

| bit 0 | IF: Integer or Fractional Multiplier Mode Select bit <sup>(1)</sup>                                                                                                     |

|       | 1 = Integer mode is enabled for DSP multiply                                                                                                                            |

|       | 0 = Fractional mode is enabled for DSP multiply                                                                                                                         |

- Note 1: This bit is available on dsPIC33EPXXX(GP/MC/MU)806/810/814 devices only.

- **2:** This bit is always read as '0'.

- 3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| <b>TABLE 4-21</b> : | QEI2 REGISTER MAP FOR dsPIC33EPXXX(MC/MU)806/810/814 DEVICES ONLY |

|---------------------|-------------------------------------------------------------------|

|---------------------|-------------------------------------------------------------------|

| File Name | Addr. | Bit 15 | Bit 14        | Bit 13   | Bit 12     | Bit 11                                                                   | Bit 10   | Bit 9    | Bit 8      | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|---------------|----------|------------|--------------------------------------------------------------------------|----------|----------|------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| QEI2CON   | 05C0  | QEIEN  | —             | QEISIDL  |            | PIMOD<2:0>                                                               |          | IMV<     | <1:0>      | —      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI2IOC   | 05C2  | QCAPEN | FLTREN        |          | QFDIV<2:0> | DIV<2:0> OUTFNC<1:0> SWPAB HOMPOL IDXPOL QEBPOL QEAPOL HOME INDEX QEB QE |          |          |            | QEA    | 000x   |            |          |        |        |        |        |               |

| QEI2STAT  | 05C4  | _      | —             | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ                                                                 | PCLEQIEN | POSOVIRQ | POSOVIEN   | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS2CNTL  | 05C6  |        | POSCNT<15:0>  |          |            |                                                                          |          |          |            |        |        |            |          | 0000   |        |        |        |               |

| POS2CNTH  | 05C8  |        | POSCNT<31:16> |          |            |                                                                          |          |          |            |        |        |            |          | 0000   |        |        |        |               |

| POS2HLD   | 05CA  |        | POSHLD<15:0>  |          |            |                                                                          |          |          |            |        |        |            |          | 0000   |        |        |        |               |

| VEL2CNT   | 05CC  |        | VELCNT<15:0>  |          |            |                                                                          |          |          |            |        |        |            |          | 0000   |        |        |        |               |

| INT2TMRL  | 05CE  |        | INTTMR<15:0>  |          |            |                                                                          |          |          |            |        |        |            | 0000     |        |        |        |        |               |

| INT2TMRH  | 05D0  |        | INTTMR<31:16> |          |            |                                                                          |          |          |            |        |        |            | 0000     |        |        |        |        |               |

| INT2HLDL  | 05D2  |        | INTHLD<15:0>  |          |            |                                                                          |          |          |            |        | 0000   |            |          |        |        |        |        |               |

| INT2HLDH  | 05D4  |        |               |          |            |                                                                          |          |          | INTHLD<31: | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX2CNTL | 05D6  |        |               |          |            |                                                                          |          |          | INDXCNT<15 | 5:0>   |        |            |          |        |        |        |        | 0000          |

| INDX2CNTH | 05D8  |        |               |          |            |                                                                          |          | I        | NDXCNT<31  | :16>   |        |            |          |        |        |        |        | 0000          |

| INDX2HLD  | 05DA  |        |               |          |            |                                                                          |          |          | INDXHLD<15 | 5:0>   |        |            |          |        |        |        |        | 0000          |

| QEI2GECL  | 05DC  |        |               |          |            |                                                                          |          |          | QEIGEC<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI2ICL   | 05DC  |        |               |          |            |                                                                          |          |          | QEIIC<15:0 | )>     |        |            |          |        |        |        |        | 0000          |

| QEI2GECH  | 05DE  |        |               |          |            |                                                                          |          |          | QEIGEC<31: | 16>    |        |            |          |        |        |        |        | 0000          |

| QEI2ICH   | 05DE  |        |               |          |            |                                                                          |          |          | QEIIC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| QEI2LECL  | 05E0  |        |               |          |            |                                                                          |          |          | QEILEC<15  | 0>     |        |            |          |        |        |        |        | 0000          |

| QEI2LECH  | 05E2  |        |               |          |            |                                                                          |          |          | QEILEC<31: | 16>    |        |            |          |        |        |        |        | 0000          |

| a secondo |       |        |               |          |            |                                                                          |          |          |            |        |        |            |          |        |        |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

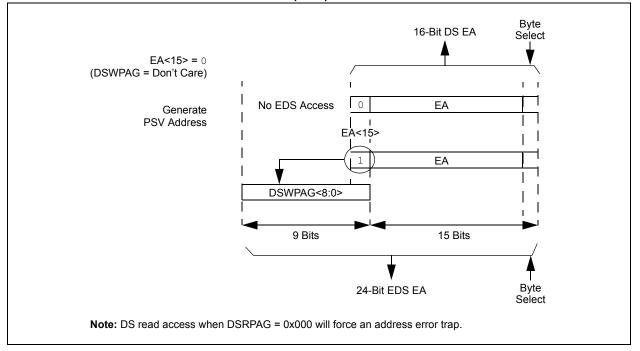

#### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers DSxPAG, in combination with the upper half of data space address can provide up to 16 Mbytes of additional address space in the EDS and 12 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS, only. The data space and EDS can be read from and written to using DSRPAG and DSWPAG, respectively.

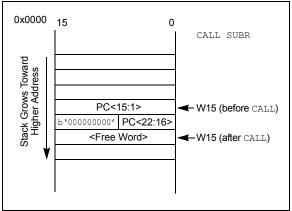

#### 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated software Stack Pointer (SP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

Note: To protect against misaligned stack accesses, W15<0> is fixed to '0' by the hardware.

W15 is initialized to 0x1000 during all Resets. This address ensures that the SP points to valid RAM in all dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814 devices and permits stack availability for non-maskable trap exceptions. These can occur before the SP is initialized by the user software. You can reprogram the SP during initialization to any location within data space.

The Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-9 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> is pushed onto the first available stack word, then PC<22:16> is pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-9. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- Note 1: For main system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging and is therefore, restricted to the address range of 0x0000 to 0xFFFF. The same applies to W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in and across X, Y and DMA RAM spaces, care must be exercised regarding its use, particularly with regard to local automatic variables in a C development environment.

#### FIGURE 4-9: CALL SI

CALL STACK FRAME

#### 4.5 Instruction Addressing Modes

The addressing modes, shown in Table 4-75, form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 < function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

- Note: Not all instructions support all of the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0     | R-0   |

|--------|-------|-------|--------|---------------------|-----|---------|-------|

| VAR    | —     | US<   | 1:0>   | EDT                 |     | DL<2:0> |       |

| bit 15 |       |       |        |                     |     |         | bit 8 |

|        |       |       |        |                     |     |         |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0   | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND     | IF    |

| bit 7  |       |       |        |                     |     |         | bit 0 |

|        |       |       |        |                     |     |         |       |

# REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15 | VAR: Variable Exception Processing Latency Control bit |

|--------|--------------------------------------------------------|

|        | 1 = Variable exception processing is enabled           |

|        | 0 = Fixed exception processing is enabled              |

|        | (2)                                                    |

#### bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

#### Note 1: For complete register details, see Register 3-2: "CORCON: Core Control Register".

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER (CONTINUED)

- bit 2 **PPST2:** Channel 2 Ping-Pong Mode Status Flag bit

- 1 = DMASTB2 register selected0 = DMASTA2 register selected

- bit 1 **PPST1:** Channel 1 Ping-Pong Mode Status Flag bit

- 1 = DMASTB1 register selected

- 0 = DMASTA1 register selected

- bit 0 PPST0: Channel 0 Ping-Pong Mode Status Flag bit

- 1 = DMASTB0 register selected

- 0 = DMASTA0 register selected

| R/W-0        | R/W-0        | R/W-0                            | R/W-0            | R/W-0                             | R/W-0            | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------|------------------|-----------------------------------|------------------|-----------------|-------|

| IC8MD        | IC7MD        | IC6MD                            | IC5MD            | IC4MD                             | IC3MD            | IC2MD           | IC1MD |

| pit 15       |              |                                  |                  |                                   |                  |                 | bit   |

| R/W-0        | R/W-0        | R/W-0                            | R/W-0            | R/W-0                             | R/W-0            | R/W-0           | R/W-0 |

| OC8MD        | OC7MD        | OC6MD                            | OC5MD            | OC4MD                             | OC3MD            | OC2MD           | OC1MD |

| pit 7        | CONNE        | COOMD                            | COOND            | OOHND                             | COOMD            | OOZIND          | bit   |

| Legend:      |              |                                  |                  |                                   |                  |                 |       |

| R = Readabl  | e bit        | W = Writable                     | bit              |                                   | nented bit, read | 1 26 (0)        |       |

| n = Value at |              | '1' = Bit is set                 | bit              | $0^{\circ} = \text{Bit is clear}$ |                  | x = Bit is unkr |       |

|              | PUR          | I = DILIS SEL                    |                  |                                   | areu             | X = DILIS UNKI  | IOWII |

| oit 15       | IC8MD: Input | Capture 8 Mod                    | lule Disable bit |                                   |                  |                 |       |

|              |              | oture 8 module<br>oture 8 module |                  |                                   |                  |                 |       |

| oit 14       | IC7MD: Input | Capture 2 Mod                    | dule Disable bit |                                   |                  |                 |       |

|              |              | oture 7 module<br>oture 7 module |                  |                                   |                  |                 |       |

| oit 13       | IC6MD: Input | Capture 6 Mod                    | dule Disable bit |                                   |                  |                 |       |

|              |              | oture 6 module<br>oture 6 module |                  |                                   |                  |                 |       |

| oit 12       | IC5MD: Input | Capture 5 Mod                    | dule Disable bit |                                   |                  |                 |       |

|              | • •          | oture 5 module<br>oture 5 module |                  |                                   |                  |                 |       |

| oit 11       | IC4MD: Input | Capture 4 Mod                    | dule Disable bit |                                   |                  |                 |       |

|              |              | oture 4 module<br>oture 4 module |                  |                                   |                  |                 |       |

| oit 10       | IC3MD: Input | Capture 3 Mod                    | dule Disable bit |                                   |                  |                 |       |

|              |              | oture 3 module<br>oture 3 module |                  |                                   |                  |                 |       |

| oit 9        | IC2MD: Input | Capture 2 Mod                    | dule Disable bit |                                   |                  |                 |       |

|              |              | oture 2 module<br>oture 2 module |                  |                                   |                  |                 |       |

| oit 8        | IC1MD: Input | Capture 1 Mod                    | dule Disable bit |                                   |                  |                 |       |

|              |              | oture 1 module<br>oture 1 module |                  |                                   |                  |                 |       |

| oit 7        | OC8MD: Out   | put Compare 8                    | Module Disable   | e bit                             |                  |                 |       |

|              | •            | ompare 8 modu<br>ompare 8 modu   |                  |                                   |                  |                 |       |

| oit 6        | OC7MD: Out   | put Compare 7                    | Module Disable   | e bit                             |                  |                 |       |

|              |              | ompare 7 modu<br>ompare 7 modu   |                  |                                   |                  |                 |       |

| oit 5        | OC6MD: Out   | put Compare 6                    | Module Disable   | e bit                             |                  |                 |       |

|              |              | ompare 6 modu<br>ompare 6 modu   |                  |                                   |                  |                 |       |

|              | -            |                                  |                  |                                   |                  |                 |       |

| oit 4        | OC5MD: Out   | put Compare 5                    | Module Disable   | e bit                             |                  |                 |       |

#### REGISTER 11-22: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-0                                | U-0   | U-0          | U-0   | U-0                                     | U-0   | U-0   | U-0   |  |  |  |

|------------------------------------|-------|--------------|-------|-----------------------------------------|-------|-------|-------|--|--|--|

| —                                  | —     | —            | —     | —                                       | —     | —     | —     |  |  |  |

| bit 15                             |       |              |       |                                         |       |       | bit 8 |  |  |  |

|                                    |       |              |       |                                         |       |       |       |  |  |  |

| U-0                                | R/W-0 | R/W-0        | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |  |

| —                                  |       | SS1R<6:0>    |       |                                         |       |       |       |  |  |  |

| bit 7                              |       | bi           |       |                                         |       |       |       |  |  |  |

|                                    |       |              |       |                                         |       |       |       |  |  |  |

| Legend:                            |       |              |       |                                         |       |       |       |  |  |  |

| R = Readable                       | bit   | W = Writable | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |  |  |

| -n = Value at POR '1' = Bit is set |       |              |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |  |

bit 15-7 Unimplemented: Read as '0'

bit 6-0 SS1R<6:0>: Assign SPI1 Slave Select Input (SS1) to the Corresponding RPn/RPIn Pin bits (see Table 11-2 for input pin selection numbers) 1111111 = Input tied to RP127

> . 0000001 = Input tied to CMP1 0000000 = Input tied to Vss

#### REGISTER 11-23: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0                                | U-0   | U-0            | U-0                                     | U-0          | U-0              | U-0      | U-0   |  |  |  |

|------------------------------------|-------|----------------|-----------------------------------------|--------------|------------------|----------|-------|--|--|--|

| _                                  | _     | —              |                                         | _            | _                | _        | —     |  |  |  |

| bit 15                             |       |                |                                         |              |                  |          | bit 8 |  |  |  |

|                                    |       |                |                                         |              |                  |          |       |  |  |  |

| U-0                                | R/W-0 | R/W-0          | R/W-0                                   | R/W-0        | R/W-0            | R/W-0    | R/W-0 |  |  |  |

| —                                  |       | SS2R<6:0>      |                                         |              |                  |          |       |  |  |  |

| bit 7                              |       |                |                                         |              |                  |          | bit 0 |  |  |  |

|                                    |       |                |                                         |              |                  |          |       |  |  |  |

| Legend:                            |       |                |                                         |              |                  |          |       |  |  |  |

| R = Readable                       | bit   | W = Writable I | oit                                     | U = Unimpler | mented bit, read | 1 as '0' |       |  |  |  |

| -n = Value at POR '1' = Bit is set |       |                | '0' = Bit is cleared x = Bit is unknown |              |                  |          |       |  |  |  |

bit 15-7 Unimplemented: Read as '0'

| U-0               | R/W-0                                                                                                                                                                                             | R/W-0             | R/W-0      | R/W-0            | R/W-0           | R/W-0           | R/W-0              |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|------------------|-----------------|-----------------|--------------------|--|--|

| —                 |                                                                                                                                                                                                   |                   | IC10R<6:0> |                  |                 |                 |                    |  |  |

| bit 15            |                                                                                                                                                                                                   |                   |            |                  |                 |                 | bit 8              |  |  |

| U-0               | R/W-0                                                                                                                                                                                             | R/W-0             | R/W-0      | R/W-0            | R/W-0           | R/W-0           | R/W-0              |  |  |

| 0-0               | 10,00-0                                                                                                                                                                                           | 10,00-0           | 10,00-0    | IC9R<6:0>        | 10.00-0         | 10/00-0         | 1000-0             |  |  |

| bit 7             |                                                                                                                                                                                                   |                   |            | 1091(<0.0>       |                 |                 | bit (              |  |  |

|                   |                                                                                                                                                                                                   |                   |            |                  |                 |                 |                    |  |  |

| Legend:           |                                                                                                                                                                                                   |                   |            |                  |                 |                 |                    |  |  |

| R = Readab        | ole bit                                                                                                                                                                                           | W = Writable      | bit        | U = Unimpler     | mented bit, rea | ıd as '0'       |                    |  |  |

| -n = Value at POR |                                                                                                                                                                                                   | '1' = Bit is set  |            | '0' = Bit is cle | ared            | x = Bit is unkr | x = Bit is unknown |  |  |

|                   |                                                                                                                                                                                                   | Input tied to RP  | P1         |                  |                 |                 |                    |  |  |

| bit 7             |                                                                                                                                                                                                   | Input tied to Vss |            |                  |                 |                 |                    |  |  |

| bit 6-0           | Unimplemented: Read as '0'<br>IC9R<6:0>: Assign Input Capture 9 (IC9) to the Corresponding RPn/RPIn Pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111111 = Input tied to RP127 |                   |            |                  |                 |                 |                    |  |  |

|                   | •                                                                                                                                                                                                 |                   | . – .      |                  |                 |                 |                    |  |  |

|                   | 0000001 =                                                                                                                                                                                         | Input tied to CM  | P1         |                  |                 |                 |                    |  |  |

|                   |                                                                                                                                                                                                   |                   |            |                  |                 |                 |                    |  |  |

#### REGISTER 11-33: RPINR33: PERIPHERAL PIN SELECT INPUT REGISTER 33

00000001 = Input tied to CMP 00000000 = Input tied to Vss

#### **REGISTER 15-2:** OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Trigger/Synchronization Source Selection bit        | s |

|---------|-------------------------------------------------------------------|---|

|         | 11111 = No Sync or Trigger source for OCx                         |   |

|         | 11110 = INT2 pin synchronizes or triggers OCx                     |   |

|         | 11101 = INT1 pin synchronizes or triggers OCx                     |   |

|         | 11100 = Reserved                                                  |   |

|         | 11011 = ADC1 module synchronizes or triggers OCx                  |   |

|         | 11010 = CMP3 module synchronizes or triggers OCx                  |   |

|         | 11001 = CMP2 module synchronizes or triggers OCx                  |   |

|         | 11000 = CMP1 module synchronizes or triggers OCx                  |   |

|         | 10111 = IC8 module synchronizes or triggers OCx                   |   |

|         | 10110 = IC7 module synchronizes or triggers OCx                   |   |

|         | 10101 = IC6 module synchronizes or triggers OCx                   |   |

|         | 10100 = IC5 module synchronizes or triggers OCx                   |   |

|         | 10011 = IC4 module synchronizes or triggers OCx                   |   |

|         | 10010 = IC3 module synchronizes or triggers OCx                   |   |

|         | 10001 = IC2 module synchronizes or triggers OCx                   |   |

|         | 10000 = IC1 module synchronizes or triggers OCx                   |   |

|         | 01111 = Timer5 synchronizes or triggers OCx                       |   |

|         | 01110 = Timer4 synchronizes or triggers OCx                       |   |

|         | 01101 = Timer3 synchronizes or triggers OCx                       |   |

|         | 01100 = Timer2 synchronizes or triggers OCx (default)             |   |

|         | 01011 = Timer1 synchronizes or triggers OCx                       |   |

|         | 01010 = No Sync or Trigger source for OCx                         |   |

|         | 01001 = OC9 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 01000 = OC8 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00111 = OC7 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00110 = OC6 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00101 = OC5 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00100 = OC4 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00011 = OC3 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | 00010 = OC2 module synchronizes or triggers $OCx^{(1,2)}$         |   |

|         | $00001 = OC1 \text{ module synchronizes or triggers OCx}^{(1,2)}$ |   |

|         | 00000 = No Sync or Trigger source for OCx                         |   |

- **Note 1:** Do not use the OCx module as its own Sync or Trigger source.

- 2: When the OCy module is turned OFF, it sends a trigger out signal. If the OCx module uses the OCy module as a Trigger source, the OCy module must be unselected as a Trigger source prior to disabling it.

| IFLTMOD<br>bit 15 |                                     | C                                    | 1 SPC - 4.0 - (2 | .3)              |                       | al Day (1)                    |               |

|-------------------|-------------------------------------|--------------------------------------|------------------|------------------|-----------------------|-------------------------------|---------------|

| bit 15            |                                     | CLSRC<4:0> <sup>(2,3)</sup>          |                  |                  | CLPOL <sup>(1)</sup>  | CLMOD                         |               |

|                   |                                     |                                      |                  |                  |                       |                               | bit           |

| R/W-0             | R/W-0                               | R/W-0                                | R/W-0            | R/W-0            | R/W-0                 | R/W-0                         | R/W-0         |

|                   | FL                                  | _TSRC<4:0> <sup>(2,3</sup>           | 3)               |                  | FLTPOL <sup>(1)</sup> | FLTMO                         | D<1:0>        |

| bit 7             |                                     |                                      |                  |                  |                       |                               | bit           |

| Legend:           |                                     |                                      |                  |                  |                       |                               |               |

| R = Readable      | e bit                               | W = Writable                         | bit              | U = Unimple      | mented bit, read      | as '0'                        |               |

| -n = Value at     | POR                                 | '1' = Bit is set                     |                  | '0' = Bit is cle | eared                 | x = Bit is unkn               | own           |

|                   |                                     |                                      |                  |                  |                       |                               |               |

| oit 15            | IFLTMOD: In                         | idependent Fau                       | It Mode Enabl    | le bit           |                       |                               |               |

|                   | 1 = Indepen                         | dent Fault mode                      | e: Current-limi  | t input maps F   | LTDAT<1> to P         | VMxH output a                 | nd Fault inpr |

|                   |                                     |                                      |                  |                  | :0> bits are not u    |                               |               |

|                   |                                     |                                      |                  |                  | .DAT<1:0> bits t      |                               |               |

|                   |                                     |                                      |                  |                  | to the PWMxH a        |                               |               |

| bit 14-10         | CLSRC<4:0>                          | Current-Limit                        | Control Signa    | al Source Sele   | ct for PWM Gen        | erator # bits <sup>(2,3</sup> | )             |

|                   | 11111 <b>= Res</b>                  | served                               |                  |                  |                       |                               |               |

|                   | •                                   |                                      |                  |                  |                       |                               |               |

|                   | •                                   |                                      |                  |                  |                       |                               |               |

|                   | •                                   |                                      |                  |                  |                       |                               |               |

|                   | 01001 <b>= Res</b>                  | served                               |                  |                  |                       |                               |               |

|                   | 01010 <b>= Cor</b>                  | mparator 3                           |                  |                  |                       |                               |               |

|                   | 01001 <b>= Cor</b>                  | mparator 2                           |                  |                  |                       |                               |               |

|                   | 01000 <b>= Cor</b>                  | mparator 1                           |                  |                  |                       |                               |               |

|                   | 00111 <b>= Res</b>                  |                                      |                  |                  |                       |                               |               |

|                   | 00110 <b>= Fau</b>                  |                                      |                  |                  |                       |                               |               |

|                   | 00101 <b>= Fau</b>                  |                                      |                  |                  |                       |                               |               |

|                   | 00100 <b>= Fau</b>                  |                                      |                  |                  |                       |                               |               |

|                   | 00011 = Fau                         |                                      |                  |                  |                       |                               |               |

|                   | 00010 = Fau<br>00001 = Fau          |                                      |                  |                  |                       |                               |               |

|                   | 00000 = Fau                         |                                      |                  |                  |                       |                               |               |

| bit 9             |                                     | rent-Limit Polar                     | ity bit for PWN  | I Generator #    | (1)                   |                               |               |

|                   |                                     | cted current-lim                     |                  |                  |                       |                               |               |

|                   | 0 = The selec                       | cted current-lim                     | it source is ac  | tive-high        |                       |                               |               |

| bit 8             | CLMOD: Cur                          | rrent-Limit Mode                     | e Enable bit fo  | r PWM Gener      | rator #               |                               |               |

|                   |                                     | ₋imit mode is er<br>₋imit mode is di |                  |                  |                       |                               |               |

|                   |                                     |                                      |                  |                  |                       |                               |               |

|                   | ese bits should<br>Id unpredictable |                                      | ly when PTEN     | l = 0. Changir   | ng the clock sele     | ction during op               | eration will  |

#### REGISTER 16-21: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER

- 2: When Independent Fault mode is enabled (IFLTMOD = 1) and Fault 1 is used for Fault mode (FLTSRC<4:0> = 01000), the Current-Limit Control Source Select bits (CLSRC<4:0>) should be set to an unused current-limit source to prevent the current-limit source from disabling both the PWMxH and PWMxL outputs.

- **3:** When Independent Fault mode is enabled (IFLTMOD = 1) and Fault 1 is used for Current-Limit mode (CLSRC<4:0> = 01000), the Fault Control Source Select bits (FLTSRC<4:0>) should be set to an unused Fault source to prevent Fault 1 from disabling both the PWMxL and PWMxH outputs.

# 20.3 UARTx Registers

| R/W-0                 | U-0                             | R/W-0                                               | R/W-0                          | R/W-0                                    | U-0                                                                                | R/W-0             | R/W-0            |  |  |

|-----------------------|---------------------------------|-----------------------------------------------------|--------------------------------|------------------------------------------|------------------------------------------------------------------------------------|-------------------|------------------|--|--|

| UARTEN <sup>(1)</sup> | —                               | USIDL                                               | IREN <sup>(2)</sup>            | RTSMD                                    | —                                                                                  | UEN               | <1:0>            |  |  |

| bit 15                |                                 |                                                     |                                |                                          |                                                                                    |                   | bit 8            |  |  |

| R/W-0, HC             | R/W-0                           | R/W-0, HC                                           | R/W-0                          | R/W-0                                    | R/W-0                                                                              | R/W-0             | R/W-0            |  |  |

| WAKE                  | LPBACK                          | ABAUD                                               | URXINV                         | BRGH                                     | PDSEI                                                                              | -                 | STSEL            |  |  |

| bit 7                 | LFDACK                          | ABAUD                                               | URAINV                         | BRGH                                     | FDGEI                                                                              | _<1.0>            | bit (            |  |  |

|                       |                                 |                                                     |                                |                                          |                                                                                    |                   |                  |  |  |

| Legend:               |                                 | HC = Hardwa                                         | re Clearable b                 | bit                                      |                                                                                    |                   |                  |  |  |

| R = Readable          | bit                             | W = Writable                                        | bit                            | U = Unimpler                             | mented bit, read                                                                   | l as '0'          |                  |  |  |

| -n = Value at F       | POR                             | '1' = Bit is set                                    |                                | '0' = Bit is cle                         | ared                                                                               | x = Bit is unkr   | nown             |  |  |

| bit 15                | UARTEN: UA                      | RTx Enable bi                                       | t(1)                           |                                          |                                                                                    |                   |                  |  |  |

|                       |                                 |                                                     |                                |                                          | y UARTx as defin<br>y port latches; L                                              |                   |                  |  |  |

| bit 14                | Unimplemen                      | ted: Read as '                                      | 0'                             |                                          |                                                                                    |                   |                  |  |  |

| bit 13                | USIDL: UART                     | Tx Stop in Idle                                     | Mode bit                       |                                          |                                                                                    |                   |                  |  |  |

|                       |                                 | ues module op<br>s module oper                      |                                |                                          | Idle mode                                                                          |                   |                  |  |  |

| bit 12                | IREN: IrDA <sup>®</sup> I       | Encoder and D                                       | ecoder Enable                  | e bit <sup>(2)</sup>                     |                                                                                    |                   |                  |  |  |

|                       |                                 | oder and deco                                       |                                |                                          |                                                                                    |                   |                  |  |  |

| bit 11                | RTSMD: Mod                      | le Selection for                                    | UxRTS Pin b                    | it                                       |                                                                                    |                   |                  |  |  |

|                       |                                 | in in Simplex n<br>in in Flow Con                   |                                |                                          |                                                                                    |                   |                  |  |  |

| bit 10                | Unimplemen                      | ted: Read as '                                      | 0'                             |                                          |                                                                                    |                   |                  |  |  |

| bit 9-8               | UEN<1:0>: UARTx Pin Enable bits |                                                     |                                |                                          |                                                                                    |                   |                  |  |  |

|                       | 10 = UxTX, U<br>01 = UxTX, U    | JxRX, UxCTS a<br>JxRX and UxR<br>nd UxRX pins a     | and UxRTS pi<br>TS pins are er | ns are enableo<br>nabled an <u>d use</u> | d; UxCTS pin is<br>d an <u>d used</u><br>ed; UxC <u>TS pin is</u><br>S and UxRTS/F | s controlled by   | port latches     |  |  |

| bit 7                 | WAKE: Wake                      | -up on Start Bi                                     | t Detect Durin                 | g Sleep Mode                             | Enable bit                                                                         |                   |                  |  |  |

|                       | hardware                        | ontinues to sar<br>on following r<br>-up is enabled | •                              | K pin; interrupt                         | is generated or                                                                    | n falling edge; b | it is cleared in |  |  |

| bit 6                 |                                 | RTx Loopback                                        | Mode Select                    | bit                                      |                                                                                    |                   |                  |  |  |

|                       | 1 = Enables I                   | Loopback mod                                        | e                              |                                          |                                                                                    |                   |                  |  |  |

| DIL O                 | 0 = Loopback                    | k mode is disal                                     |                                |                                          |                                                                                    |                   |                  |  |  |

|                       | -                               | k mode is disal<br>p-Baud Enable                    |                                |                                          |                                                                                    |                   |                  |  |  |

| bit 5                 | ABAUD: Auto                     | o-Baud Enable                                       | bit<br>surement on t           |                                          | eter – requires re                                                                 | eception of a S   | ync field (55h   |  |  |

REGISTER 20-1: UxMODE: UARTx MODE REGISTER

© 2009-2012 Microchip Technology Inc.

2: This feature is only available for the 16x BRG mode (BRGH = 0).

# dsPIC33EPXXX(GP/MC/MU)806/810/814 and PIC24EPXXX(GP/GU)810/814

| R/W-0        | R/W-0                            | R/W-0                                    | R/W-0                                          | R/W-0                                                                         | R/W-0           | R/W-0    | R/W-0 |  |  |

|--------------|----------------------------------|------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------|-----------------|----------|-------|--|--|

|              | F7BF                             | P<3:0>                                   |                                                | F6BP<3:0>                                                                     |                 |          |       |  |  |

| bit 15       |                                  |                                          |                                                |                                                                               |                 |          | bit 8 |  |  |

| R/W-0        | R/W-0                            | R/W-0                                    | R/W-0                                          | R/W-0                                                                         | R/W-0           | R/W-0    | R/W-0 |  |  |

|              | F5BF                             | P<3:0>                                   |                                                | F4BP<3:0>                                                                     |                 |          |       |  |  |

| bit 7        |                                  |                                          |                                                |                                                                               |                 |          | bit 0 |  |  |

| Legend:      | lo hit                           | M = Mritabla                             | <b>h</b> it                                    |                                                                               | control hit roo | d aa (0) |       |  |  |

| R = Readab   |                                  | W = Writable                             |                                                | U = Unimplemented bit, read as '0'<br>'0' = Bit is cleared x = Bit is unknown |                 |          |       |  |  |

| -n = Value a | t POR                            | '1' = Bit is set                         |                                                | '0' = Bit is cleared x = Bit is u                                             |                 |          | IOWN  |  |  |

| bit 15-12    | F7BP<3:0>:                       | RX Buffer Masl                           | k for Filter 7 k                               | oits                                                                          |                 |          |       |  |  |

|              |                                  |                                          |                                                |                                                                               |                 |          |       |  |  |

|              |                                  | r hits received ir<br>r hits received ir | n RX FIFO bu                                   |                                                                               |                 |          |       |  |  |

|              |                                  |                                          | n RX FIFO bu                                   |                                                                               |                 |          |       |  |  |

|              | 1110 <b>= Filte</b>              |                                          | n RX FIFO bu                                   |                                                                               |                 |          |       |  |  |

|              | 1110 = Filte<br>•<br>•<br>•<br>• |                                          | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | 4                                                                             |                 |          |       |  |  |

- bit 7-4 F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bit 15-12)

- bit 3-0 F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bit 15-12)

#### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0        | R/W-0                                      | R/W-0           | R/W-0                                   | R/W-0 | R/W-0   | R/W-0              |  |  |  |

|---------------|--------------|--------------------------------------------|-----------------|-----------------------------------------|-------|---------|--------------------|--|--|--|

|               | F11B         | P<3:0>                                     |                 |                                         | F10E  | 3P<3:0> |                    |  |  |  |

| bit 15        |              |                                            |                 |                                         |       |         | bit 8              |  |  |  |

| R/W-0         | R/W-0        | R/W-0                                      | R/W-0           | R/W-0                                   | R/W-0 | R/W-0   | R/M/-0             |  |  |  |

| 10,00-0       | -            | P<3:0>                                     | 10.00-0         |                                         | -     | P<3:0>  | W-0 R/W-0<br>bit 0 |  |  |  |

| bit 7         | 1 3 01       | 10.02                                      |                 |                                         | 100   | 1 3.02  | hit 0              |  |  |  |

|               |              |                                            |                 |                                         |       |         | bit o              |  |  |  |

| Legend:       |              |                                            |                 |                                         |       |         |                    |  |  |  |

| R = Readabl   | e bit        | W = Writable                               | bit             | U = Unimplemented bit, read as '0'      |       |         |                    |  |  |  |

| -n = Value at | POR          | '1' = Bit is set                           | :               | '0' = Bit is cleared x = Bit is unknowr |       |         | nown               |  |  |  |

|               |              |                                            |                 |                                         |       |         |                    |  |  |  |

| bit 15-12     | F11BP<3:0    | RX Buffer Ma                               | sk for Filter 1 | 1 bits                                  |       |         |                    |  |  |  |

|               |              |                                            |                 | IFO buffer                              |       |         |                    |  |  |  |

|               | 1111 = Filte | er hits received in                        | h RX FIFO bu    | lπer                                    |       |         |                    |  |  |  |

|               |              | er hits received in<br>er hits received in |                 | -                                       |       |         |                    |  |  |  |

|               |              |                                            |                 | -                                       |       |         |                    |  |  |  |

|          | •                                                                        |

|----------|--------------------------------------------------------------------------|

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F10BP<3:0>: RX Buffer Mask for Filter 10 bits (same values as bit 15-12) |

| bit 7-4  | F9BP<3:0>: RX Buffer Mask for Filter 9 bits (same values as bit 15-12)   |

| bit 3-0  | F8BP<3:0>: RX Buffer Mask for Filter 8 bits (same values as bit 15-12)   |

| Legend:<br>R = Readable I | hit   | W = Writable I | oit   |       | nented bit read | 1 22 (0) |       |

|---------------------------|-------|----------------|-------|-------|-----------------|----------|-------|

| bit 7                     |       |                |       |       |                 |          | bit 0 |

| CSS23                     | CSS22 | CSS21          | CSS20 | CSS19 | CSS18           | CSS17    | CSS16 |

| R/W-0                     | R/W-0 | R/W-0          | R/W-0 | R/W-0 | R/W-0           | R/W-0    | R/W-0 |

| bit 15                    |       |                |       |       |                 |          | bit 8 |

| CSS31                     | CSS30 | CSS29          | CSS28 | CSS27 | CSS26           | CSS25    | CSS24 |

| R/W-0                     | R/W-0 | R/W-0          | R/W-0 | R/W-0 | R/W-0           | R/W-0    | R/W-0 |

## REGISTER 23-8: AD1CSSH: ADC1 INPUT SCAN SELECT REGISTER HIGH<sup>(1,2,3)</sup>

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

CSS<31:16>: ADC1 Input Scan Selection bits

- 1 =Selects ANx for input scan

- 0 = Skips ANx for input scan

- **Note 1:** On devices with less than 32 analog inputs, all ADxCSSH bits can be selected by user software. However, inputs selected for scan without a corresponding input on the device converts to VREFL.

- **2:** CSSx = ANx, where x = 16-31.

- 3: ADC2 only supports analog inputs, AN0-AN15; therefore, no ADC2 Input Scan Select register exists.

#### REGISTER 23-9: ADxCSSL: ADCx INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

| Legend: |       |       |       |       |       |       |       |

|---------|-------|-------|-------|-------|-------|-------|-------|

| bit 7   |       |       |       |       |       |       | bit 0 |

| CSS7    | CSS6  | CSS5  | CSS4  | CSS3  | CSS2  | CSS1  | CSS0  |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| bit 15  |       |       |       |       |       |       | bit 8 |

| CSS15   | CSS14 | CSS13 | CSS12 | CSS11 | CSS10 | CSS9  | CSS8  |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| •                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-0

CSS<15:0>: ADC Input Scan Selection bits

- 1 = Selects ANx for input scan

- 0 = Skips ANx for input scan

- **Note 1:** On devices with less than 16 analog inputs, all ADxCSSL bits can be selected by the user. However, inputs selected for scan without a corresponding input on the device converts to VREFL.

- **2:** CSSx = ANx, where x = 0-15.

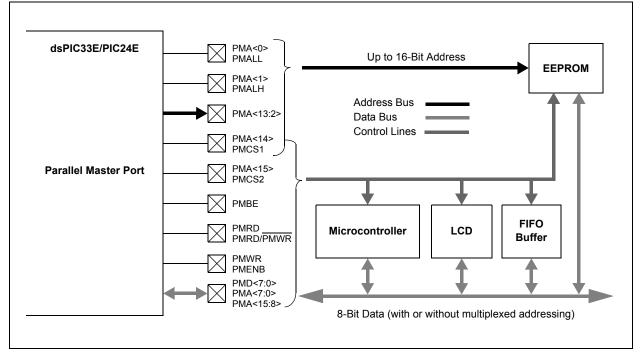

# 28.0 PARALLEL MASTER PORT (PMP)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXX(GP/MC/MU)806/ 810/814 and PIC24EPXXX(GP/GU)810/ 814 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 28. "Parallel Master Port (PMP)" (DS70576) of the "dsPIC33E/PIC24E Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Parallel Master Port (PMP) module is a parallel 8-bit I/O module, specifically designed to communicate with a wide variety of parallel devices, such as communication peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP is highly configurable.

Key features of the PMP module include:

- Eight Data Lines

- Up to 16 Programmable Address Lines

- Up to 2 Chip Select Lines

- Programmable Strobe Options:

- Individual read and write strobes, or

- Read/Write strobe with enable strobe

- Address Auto-Increment/Auto-Decrement

- Programmable Address/Data Multiplexing

- · Programmable Polarity on Control Signals

- Legacy Parallel Slave Port (PSP) Support

- Enhanced Parallel Slave Support:

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable Wait States

#### FIGURE 28-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

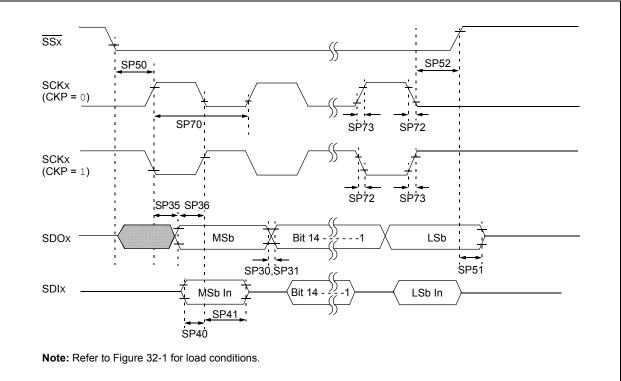

# TABLE 32-39:SPI1, SPI3 AND SPI4 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| АС СНА |                       | rics                                                                      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |       |                                      |

|--------|-----------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                             | Min.                                                                                                                                                                                                 | Typ. <sup>(2)</sup> | Max. | Units | Conditions                           |

| SP70   | TscP                  | Maximum SCKx Input Frequency                                              | _                                                                                                                                                                                                    | _                   | 15   | MHz   | See Note 3                           |

| SP72   | TscF                  | SCKx Input Fall Time                                                      | —                                                                                                                                                                                                    | —                   | _    | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP73   | TscR                  | SCKx Input Rise Time                                                      | _                                                                                                                                                                                                    |                     | —    | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP30   | TdoF                  | SDOx Data Output Fall Time                                                |                                                                                                                                                                                                      |                     | _    | ns    | See Parameter DO32 and <b>Note 4</b> |

| SP31   | TdoR                  | SDOx Data Output Rise Time                                                | —                                                                                                                                                                                                    | _                   | _    | ns    | See Parameter DO31 and <b>Note 4</b> |

| SP35   | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                 | —                                                                                                                                                                                                    | 6                   | 20   | ns    |                                      |

| SP36   | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                              | 30                                                                                                                                                                                                   | _                   | _    | ns    |                                      |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                | 30                                                                                                                                                                                                   | —                   | _    | ns    |                                      |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                                 | 30                                                                                                                                                                                                   | _                   | _    | ns    |                                      |

| SP50   | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx $\downarrow$ Input | 120                                                                                                                                                                                                  | —                   | _    | ns    |                                      |

| SP51   | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance                                    | 10                                                                                                                                                                                                   | —                   | 50   | ns    | See Note 4                           |