Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 13                                                                             |

| Program Memory Size        | 12KB (4K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                 |

| Supplier Device Package    | 18-SOIC                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj12gp201t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

- Note 1: This data sheet sumarizes the features of the PIC24HJ12GP201/202 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/PIC24H Family Reference Manual"*. Please see the Microchip web site (vww.microchip.co)mfor the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated b ts described in this section may not be available on all devices. Refer o Section 4.0 Memory Organization in this data sheet for viee-specific register and bit information.

This document contains **dieve** specific information for the PIC24HJ12GP201/202 devices. PIC24H devices contain extensiveunctionality with a highperformance, 16-bit microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the PIC24HJ12GP201/202 family of devicesTable 1-1 lists the functions of the various pins shown in the pinout diagrams.

### 8.2 Clock Switching Operation

Applications are free towstch among any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time limit the possible side effects of this flexibility, PIC24HJ12GP201/202 devices have a safeguard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMD<1:0> Conf guration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch among the different primary submodes without reprogramming the device.

### 8.2.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to 0. (Refer toSection 19.1 Configuration Bits for further details.) If the FCKSM1 Configuration bit is unprogrammed  $\pounds$ ), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits(OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<O>) has no effect when clock switching is disabled. It is held at all times.

### 8.2.2 OSCILLATOR SWITCHING SEQUENCE

Performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

When the basic sequence isompleted, the system clock hardware responds automatically as follows:

1. The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF (OSCCON<3>) status bits are cleared.

- 3. The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred the COSC status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

- 2: Direct clock swhes between any prmary oscillator mode with PLL and FFC-PLL mode are not permitted. This apples to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- Refer to7. Oscillator (DS70186) in the "dsPIC33F/PIC24H Family Reference Manual" for details.

### 8.3 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate evienthe event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failurexprevent and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the coist fail trap vector.

If the PLL multiplier is each to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

NOTES:

#### REGISTER 10-9: RPINR21: PERIPHERAL PIN SELECT INPUT REGISTER 21

| U-O           | U-O | U-O        | U-O    | U-O      | U-O            | U-O       | U-0        |

|---------------|-----|------------|--------|----------|----------------|-----------|------------|

|               |     |            |        |          |                |           |            |

| bit 15        |     |            |        |          |                |           | bit 8      |

|               |     |            |        |          |                |           |            |

| U-O           | U-O | U-O        | R/W-1  | R/W-1    | R/W-1          | R/W-1     | R/W-1      |

|               |     |            |        |          | SS1R<4:0>      |           |            |

| bit 7         |     | •          |        |          |                |           | bit C      |

|               |     |            |        |          |                |           |            |

| Legend:       |     |            |        |          |                |           |            |

| R = Readable  | bit | W = Writab | le bit | U = Unim | plemented bit, | read as O |            |

| -n = Value at | POR | 1 = Bit is | set    | O = Bit  | is cleared     | x = Bit   | is unknown |

| <u></u>       |     |            |        |          |                |           |            |

bit 15-5 Unimplemented: Read as 0

bit 4-0 SS1R<4:0>: Assign SPI1 Slave Select Input (SS1IN) to the Corresponding RPn pin bits 11111 = Input tied tosy 01111 = Input tied to RP15

> 00001 = Input tied to RP1 00000 = Input tied to RP0

# 16.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

- Note 1: This data sheet sum**a**rizes the features of the PIC24HJ12B201/202 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer toSection 19. Inter-Integrated Circuit (I<sup>2</sup>C) (DS70195) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip websitev(ww.microchip.co)m

- 2: Some registers and associated b ts described in this section may not be available on all devices. Refer o Section 4.0 Memory Organization in this data sheet for vdee-specific register and bit information.

The Inter-Integrated Circuit  $^2 \ (\ )$  module provides complete hardware support for both Slave and Multi-Master modes of the  $^2 \ Cl$  serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

The SCLx pin is clock The SDAx pin is data

The  $I^2C$  module offers the following key features:

$\ensuremath{\mathsf{I}}^2\ensuremath{\mathsf{C}}$  interface supporting both Master and Slave modes of operation

I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addresses

I<sup>2</sup>C Master mode supports 7-bit and 10-bit addresses I<sup>2</sup>C port allows bidirectional transfers between master and slaves

Serial clock sync**r**onization for<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial trarfer (SCLREL control)

I<sup>2</sup>C supports multi-mast**ep**eration, detects bus collision and arbitrates accordingly

### 16.1 Operating Modes

The hardware fully implements all the master and slave functions of the $^{2}$ C Standard and Fast mode specifications, as well as 7-bit and 10-bit addressing.

The I<sup>2</sup>C module can operate either as a slave or a master on an<sup>2</sup>C bus.

The following types of Cloperation are supported:

I<sup>2</sup>C slave operation with 7-bit address

- I<sup>2</sup>C slave operation with 10-bit address

- I<sup>2</sup>C master operation will hbit or 10-bit address

For details about the communication sequence in each of these modes, refer to the Microchip web site (www.microchip.co)mfor the lates Star PIC33F/PIC24H Family Reference Manual" sections.

### 16.2 <sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

I2CxRSR is the shift register used for shifting data I2CxRCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

I2CxTRN is the transmit register to which bytes are written during a transmit operation

I2CxADD register holds the slave address

ADD10 status bit indicates 10-bit Address mode I2CxBRG acts as the Baud Rate Generator

(BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, ist transferred to I2CxRCV, and an interrupt pulse is generated.

### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                                          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                |

| bit 2 | R_W: Read/Write Information bit (when operating Caslave)                                                                                                                                                                              |

|       | 1 = Read indicates data transfer is output from slave<br>0 = Write indicates data transfer is input to slave<br>Hardware set or cle <b>a</b> fter reception of device address byte.                                                   |

| bit 1 | RBF: Receive Buffer Full Status bit<br>1 = Receive complete, I2CxRCV is full<br>0 = Receive not complete, I2CxRCV is empty<br>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV. |

| bit O | TBF: Transmit Buffer Full Status bit<br>1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty<br>Hardware set when software writes I2CxTRN. <b>\∀are</b> clear at completion of data transmission.     |

NOTES:

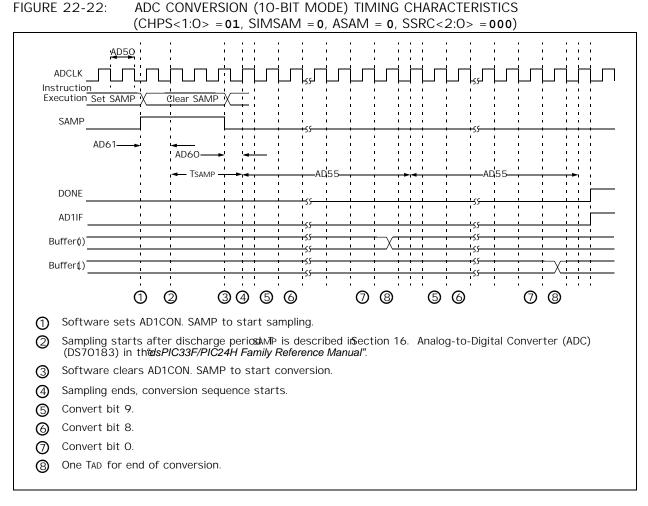

### 18.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet sumarizes the features of the PIC24HJ12B201/202 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer toSection 16. Analog-to-Digital Converter (ADC) with DMA (DS70183) of the"dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.co)m

- 2: Some registers and associated b ts described in this section may not be available on all devices. Refer o Section 4.0 Memory Organization in this data sheet for dee-specific register and bit information.

The PIC24HJ12GP201/202 devices have up to 10 ADC module input channels.

The AD12B bit (AD1CON1<10>), allows each of the ADC modules to be configured as either a 10bit, 4-sample-and-hold ADC (default configuration) or a 12-bit, 1-sample-and-hold ADC.

Note: The ADC module must be disabled before the AD12B bit can be modified.

### 18.1 Key Features

The 10-bit ADC configuration has the following key features:

Successive Approximation (SAR) conversion

Conversion speeds of up to 1.1 Msps

Up to 10 analog input pins

External voltage reference input pins

Simultaneous sampling of up to four analog input pins

Automatic Channel Scan mode

Selectable conversion trigger source

Selectable Buffer Fill modes

Operation during CPU Sleep and Idle modes

16-word conversion result buffer

The 12-bit ADC configuration supports all the above features, except:

In the 12-bit configuratic conversion speeds of up to 500 ksps are supported

There is only one sample-and-hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported

Depending on the particular device pinout, the ADC can have up to 10 analog input pins, designated ANO through AN9. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs can be shared with other analog input pins.

The actual number of analog input pins and external voltage reference input configuration will depend on the specific device. Refer to the device data sheet for further details.

Block diagrams of the ADC module are shown in Figure 18-1 and Figure 18-2

### 18.2 ADC Initialization

To configure the ADC module:

- 1. Select port pins as analog inputs (AD1PCFGH<15:0> or AD1PCFGL<15:0>).

- 2. Select voltage reference source to match expected range on analog inputs (AD1CON2<15:13>).

- 3. Select the analog conversion clock to match desired data rate with processor clock (AD1CON3<7:0>).

- 4. Determine how many sample-and-hold channels will be used (AD1CON2<9:8> and AD1PCFGH<15:0> or AD1PCFGL<15:0>).

- 5. Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- 6. Select the way conversion results are presented in the buffer (AD1CON1<9:8>).

- a) Turn on the ADC module (AD1CON1<15>).

- 7. Configure ADC interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select ADC interrupt priority.

| DC CHARACTERISTICS |        | (unless                                | otherwi | ise state<br>perature | d)<br>-40°℃ | 3.0V to 3.6V<br>A +85°C for Industrial<br>A +125°C for Extended |                                                                        |

|--------------------|--------|----------------------------------------|---------|-----------------------|-------------|-----------------------------------------------------------------|------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                         | Min     | Typ <sup>(1)</sup>    | Max         | Units                                                           | Conditions                                                             |

|                    | lı∟    | Input Leakage Current <sup>(2,3)</sup> |         |                       |             |                                                                 |                                                                        |

| DI50               |        | I/O Pins 5V Tolera(र्सि                |         |                       | -2          | μA                                                              | Vss VPIN VDD,<br>Pin at high-impedance                                 |

| DI51               |        | I/O Pins Not 5V Tolerant               |         |                       | -1          | μA                                                              | Vss VPIN VDD,<br>Pin at high-impedance,<br>-40°C TA +85°C              |

| DI51a              |        | I/O Pins Not 5V Tolerant               |         |                       | -2          | μA                                                              | Shared with external referenc<br>pins, -40°C TA +85°C                  |

| DI51b              |        | I/O Pins Not 5V Tolerant               |         |                       | -3.5        | μA                                                              | Vss VPIN VDD, Pin at<br>high-impedance,<br>-40°C TA +125°C             |

| DI51c              |        | ।/O Pins Not 5V Toleraंतिरे            |         |                       | -8          | μA                                                              | Analog pins shared with<br>external reference pins,<br>-40°C TA +125°C |

| DI55               |        | MCLR                                   |         |                       | -2          | μA                                                              | Vss Vpin Vdd                                                           |

| DI56               |        | OSC1                                   |         |                       | -2          | μA                                                              | Vss VPIN VDD,<br>XT and HS modes                                       |

#### TABLE 22-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Note 1: Data in Typ column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MClpRn is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Highakage current may be measured at different input voltages.

3: Negative current is defined asrrent sourced by the pin.

4: See Pin Diagrams for a list of 5V tolerant pins.

5: VIL source < (\$45 0.3). Characterized but not tested.

6: Non-5V tolerant pinsu/vsource > (MD + 0.3), 5V tolerant pinsu/vsource > 5.5V. Characterized but not tested.

7: Digital 5V tolerant pins cannot tolerate any positiput injection current from input sources > 5.5V.

8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

9: Any number and/or combination of I/O pins not excluded under ICH conditions are permitted provided the mathematical absolute instantaneous sumeon provided the specified limit. Characterized but not tested.

10: These parameters are characterized, but not tested.

| DC CHARACTERISTICS |        |                                                                       | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature -40°CA +85°C for Industrial<br>-40°C TA +125°C for Extended |  |                     |    |                                                                                                                        |

|--------------------|--------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|---------------------|----|------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                        | Min Typ <sup>(1)</sup> Max Units Conditions                                                                                                                   |  |                     |    |                                                                                                                        |

| DI6Oa              | licl   | Input Low Injection Current                                           | 0                                                                                                                                                             |  | -5 <sup>(5,8)</sup> | mA | All pins except MD, Vss, AVDD,<br>AVss, MCLR, VCAP, SOSCI,<br>and SOSCO                                                |

| DI60b              | Іісн   | Input High Injection Current                                          | 0                                                                                                                                                             |  | +5 (6,7,8)          | mA | All pin <u>s except</u> ID, Vss, AVDD,<br>AVss, MCLR, VcAP, SOSCI,<br>SOSCO, and digital 5V-toleran<br>designated pins |

| DI60c              | lict   | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(9)</sup>                                                                                                                                            |  | +20 <sup>(9)</sup>  | mA | Absolute instantaneous sum<br>all – input injection currents<br>from all I/O pins<br>(   ICL +   ICH   ) IICT          |

| TABLE 22-9: | DC CHARACTERISTICS: I/O PI | N INPUT SPECIFICATIONS ( | (CONTINUED) |

|-------------|----------------------------|--------------------------|-------------|

|             |                            |                          |             |

Note 1: Data in Typ column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MClpRn is strongly dependent on the lappopulage level. The specified levels represent normal operating nditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: See Pin Diagrams for a list of 5V tolerant pins.

- 5: VIL source < (\$ 0.3). Characterized but not tested.

- 6: Non-5V tolerant pins⊮/source > (№ + 0.3), 5V tolerant pins⊮ source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any peositiput injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- 9: Any number and/or combination of I/O pins not excluded under ICH conditions are permitted provided the mathematical absolute instantaneous sume injection currents from all pins do not exceed the specified limit. Characterized but not tested.

10: These parameters are characterized, but not tested.

| AC CHARACTERISTICS |           |                                                                       |                                | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature -40°CTA +85°C for Industrial<br>-40°C TA +125°C for Extended |                                              |     |                  |       |                                      |

|--------------------|-----------|-----------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----|------------------|-------|--------------------------------------|

| Param<br>No.       | Symbol    | Characte                                                              | eristic                        |                                                                                                                                                                | Min                                          | Тур | Max              | Units | Conditions                           |

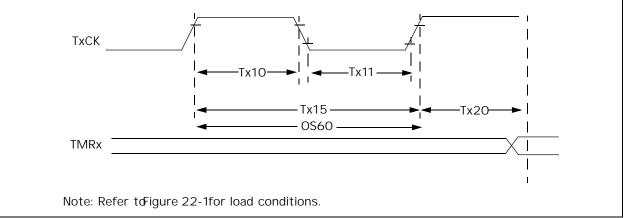

| TA10               | ТтхН      | TxCK High Time                                                        | Synchr<br>no pres              |                                                                                                                                                                | Tcy + 20                                     |     |                  | ns l  | Nust also meet<br>parameter TA15.    |

|                    |           |                                                                       | Synchro<br>with pr             |                                                                                                                                                                | (Tcy + 20)/N                                 | J   |                  | ns    | N = prescale<br>value                |

|                    |           |                                                                       | Asynch                         | ronous                                                                                                                                                         | 20                                           |     |                  | ns    | (1, 8, 64, 256)                      |

| TA11               | ΤτxL      | TxCK Low Time                                                         | Synchronous,<br>no prescaler   |                                                                                                                                                                | (Tcy + 20)                                   |     |                  | ns l  | Must also meet<br>parameter TA15.    |

|                    |           |                                                                       | Synchronous,<br>with prescaler |                                                                                                                                                                | (Tcy + 20)/N                                 | J   |                  | ns    | N = prescale<br>value                |

|                    |           |                                                                       | Asynch                         | ronous                                                                                                                                                         | 20                                           |     |                  | ns    | (1, 8, 64, 256)                      |

| TA15               | ΤτχΡ      | TxCK Input<br>Period                                                  | Synchro<br>no pres             |                                                                                                                                                                | 2 Tcy + 40                                   |     |                  | ns    |                                      |

|                    |           |                                                                       | Synchro<br>with pr             |                                                                                                                                                                | Greater of:<br>40 ns or<br>(2 TCY + 40)<br>N | /   |                  | N =   | prescale<br>value<br>(1, 8, 64, 256) |

|                    |           |                                                                       | Asynch                         | ronous                                                                                                                                                         | 40                                           |     |                  | ns    |                                      |

| OS60               | Ft1       | SOSCI/T1CK Osc<br>frequency Range<br>enabled by settin<br>(T1CON<1>)) | e (oscillator                  |                                                                                                                                                                | DC                                           |     | 50               | kHz   |                                      |

| TA20               | TCKEXTMRL | Delay from External TxCK Clock<br>Edge to Timer Increment             |                                |                                                                                                                                                                | 0.75 ℃Y +<br>40                              |     | 1.75 TCY +<br>40 |       |                                      |

| TABLE 22-22: | TIMFR1 | FXTERNAL | CLOCK | TIMING | REQUIREMENTS | (1) |

|--------------|--------|----------|-------|--------|--------------|-----|

|              |        |          |       |        |              |     |

Note 1: Timer1 is a Type A.

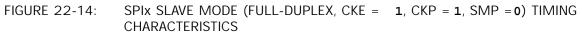

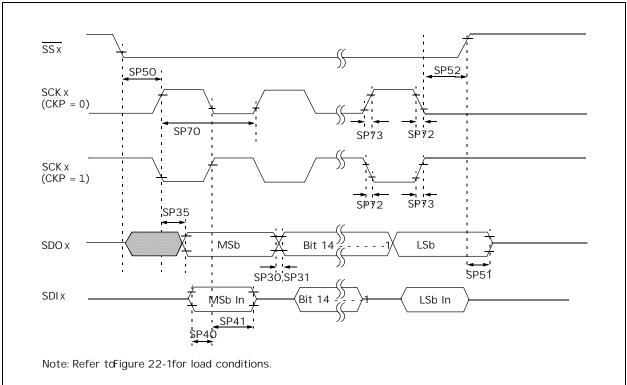

FIGURE 22-16: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

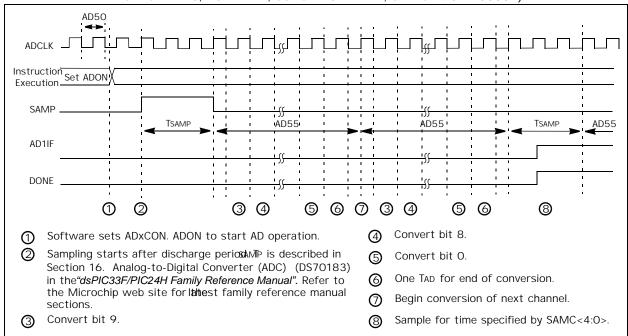

FIGURE 22-23: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:O> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:O> =111, SAMC<4:O> =00001)

NOTES:

### Revision C (May 2008)

This revision includes minor typographical and formatting changes throughout the data sheet text.

The major changes are referenced by their respective section in the following table.

#### TABLE 23-1: MAJOR SECTION UPDATES

| Section Name                                           | Update Description                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Performance, 16-Bit<br>Digital Signal Controllers | Added SSOP to list of available 28-pin packages (Seackaging: and Table 1).<br>Added External Interrupts column to Remappable Peripherals in the Controller<br>Families table and Note 2 (see Table 1).                                                                                                                                                                                                    |

|                                                        | Added Note 1 to all pin diagrams, which references RPn pin usage by remappable peripherals (see Pin Diagrams ).                                                                                                                                                                                                                                                                                           |

| Section 1.0 Device<br>Overview                         | Changed Capture Input pin names from ICO-IC1 to IC1-IC2 and updated description for AVbD (see Table 1-1).                                                                                                                                                                                                                                                                                                 |

| Section 3.0 Memory<br>Organization                     | Updated Reset values for the follogvorFRs: IPCO, IPC2-IPC7, IPC16, and INTTREG (see Table 3-4).                                                                                                                                                                                                                                                                                                           |

|                                                        | The following changes were made to the ADC1 Register Maps:<br>Updated the bit range for AD1CON3 from AD <b>CSO</b> to ADCS <i>-</i> ?:0>)<br>(see Table 3-14 and Table 3-15).<br>Added Bit 6 (PCFG7) and Bit 7 (PCFG6) names to AD1PCFGL (Table 3-14).<br>Added Bit 6 (CSS7) and Bit 7 (CSS6) names to AD1CSSL (see Table 3-14).<br>Changed Bit 5 and Bit 4 in AD1CSSL to unimplemented (see Table 3-14). |

|                                                        | Updated the Reset value for CLKDIV in the System Control Register Map (see Table 3-19).                                                                                                                                                                                                                                                                                                                   |

| Section 4.0 Flash Program<br>Memory                    | UpdatedSection 4.3 Programming Operations with programming time formula.                                                                                                                                                                                                                                                                                                                                  |

| Section 5.0 Resets                                     | Entire section was replaced to maintain consistency with other PIC24H data shee                                                                                                                                                                                                                                                                                                                           |

| Section 7.0 Oscillator<br>Configuration                | Removed the first sentence of the <b>thirck</b> source item (External Clock) in Section 7.1.1.2 Primary                                                                                                                                                                                                                                                                                                   |

|                                                        | Updated the default bit values for DOZE and FRCDIV in the Clock Divisor Register (see Register 7-2).                                                                                                                                                                                                                                                                                                      |

|                                                        | Added the center frequency in the OSCTUN register for the FRC Tuning bits (TUN<5:0>) value011111 and updated the center frequency for bits value10 (see Register 7-4)                                                                                                                                                                                                                                     |

| Section 8.0 Power-Saving<br>Features                   | Added the following two registers:<br>PMD1: Peripheral Module Disable Control Register 1<br>PMD2: Peripheral Module Disable Control Register 2                                                                                                                                                                                                                                                            |

| Section 9.0 I/O Ports                                  | Added paragraph and Table 9-1 Spection 9.1.1 Open-Drain Configuration , which provides details on IpOns and their functionality.                                                                                                                                                                                                                                                                          |

|                                                        | Removed the following sections, which are now available in the related section of<br>the <i>"PIC24H Family Reference Manual"</i> :<br>9.4.2 Available Peripherals<br>9.4.3.3 Mapping<br>9.4.5 Considerations for Peripheral Pin Selection                                                                                                                                                                 |

| Section 13.0 Output<br>Compare                         | Replaced sections 13.1, 13.2, and 13.3 and related figures and tables with entirely new content.                                                                                                                                                                                                                                                                                                          |

### TABLE 23-1: MAJOR SECTION UPDATES

| Section Name                          | Update Description                                             |

|---------------------------------------|----------------------------------------------------------------|

| Section 22.0 Packaging<br>Information | Added 28-lead SSOP package marking information.                |

| Product Identification<br>System      | Added Plastic Shrink Small Outline (SSOP) package information. |