Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 12KB (4K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                |                                                                               |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

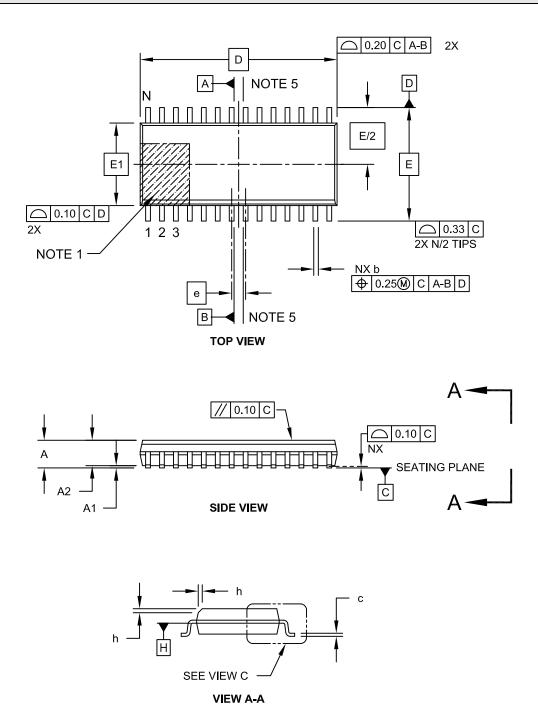

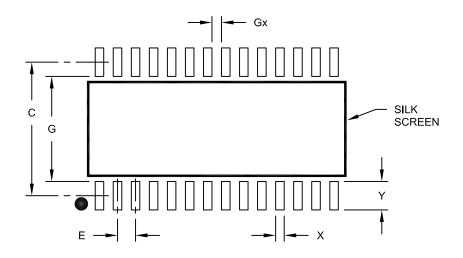

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj12gp202-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2009

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007-2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-61341-373-9

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **High-Performance**, 16-bit Microcontrollers

### **Operating Range:**

- Up to 40 MIPS operation (@ 3.0-3.6V):

- Industrial temperature range (-40°C to +85°C)

- Extended temperature range (-40°C to +125°C)

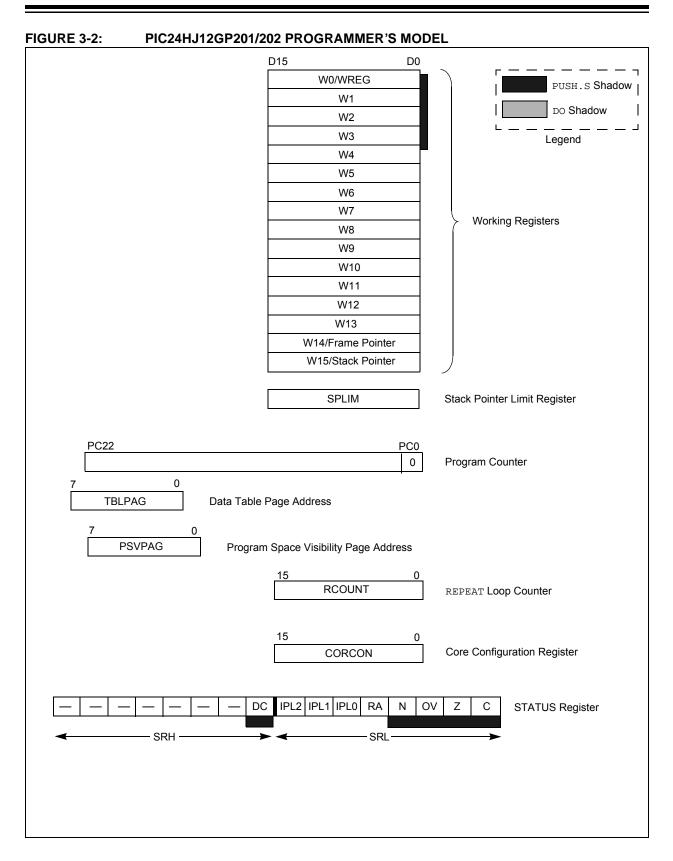

### **High-Performance CPU:**

- · Modified Harvard architecture

- · C compiler optimized instruction set

- · 16-bit-wide data path

- · 24-bit-wide instructions

- Linear program memory addressing up to 4M instruction words

- · Linear data memory addressing up to 64 Kbytes

- 71 base instructions, mostly one word/one cycle

- Sixteen 16-bit general purpose registers

- · Flexible and powerful addressing modes

- · Software stack

- · 16 x 16 multiply operations

- 32/16 and 16/16 divide operations

- Up to ±16-bit shifts for up to 40-bit data

#### **Interrupt Controller:**

- 5-cycle latency

- Up to 21 available interrupt sources

- · Up to three external interrupts

- · Seven programmable priority levels

- Four processor exceptions

#### **On-Chip Flash and SRAM:**

- Flash program memory (12 Kbytes)

- Data SRAM (1024 bytes)

- · Boot and General Security for Program Flash

#### **Digital I/O:**

- · Peripheral Pin Select Functionality

- Up to 21 programmable digital I/O pins

- Wake-up/Interrupt-on-Change for up to 21 pins

- · Output pins can drive from 3.0V to 3.6V

- Up to 5V output with open drain configurations on 5V tolerant pins

- 4 mA sink on all I/O pins

#### System Management:

- · Flexible clock options:

- External, crystal, resonator, internal RC

- Fully integrated Phase-Locked Loop (PLL)

- Extremely low-jitter PLL

- Power-up Timer

- Oscillator Start-up Timer/Stabilizer

- · Watchdog Timer with its own RC oscillator

- Fail-Safe Clock Monitor (FSCM)

- · Reset by multiple sources

#### **Power Management:**

- · On-chip 2.5V voltage regulator

- · Switch between clock sources in real time

- · Idle, Sleep, and Doze modes with fast wake-up

#### Timers/Capture/Compare:

- Timer/Counters, up to three 16-bit timers:

- Can pair up to make one 32-bit timer

- One timer runs as Real-Time Clock with external 32.768 kHz oscillator

- Programmable prescaler

- Input Capture (up to four channels):

- Capture on up, down, or both edges

- 16-bit capture input functions

- 4-deep FIFO on each capture

- Output Compare (up to two channels):

- Single or Dual 16-bit Compare mode

- 16-bit Glitchless PWM Mode

# 3.4 Arithmetic Logic Unit (ALU)

The PIC24HJ12GP201/202 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts, and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV), and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The PIC24HJ12GP201/202 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.4.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

### 3.4.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.4.3 MULTI-BIT DATA SHIFTER

The multi-bit data shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either a working register or a memory location.

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

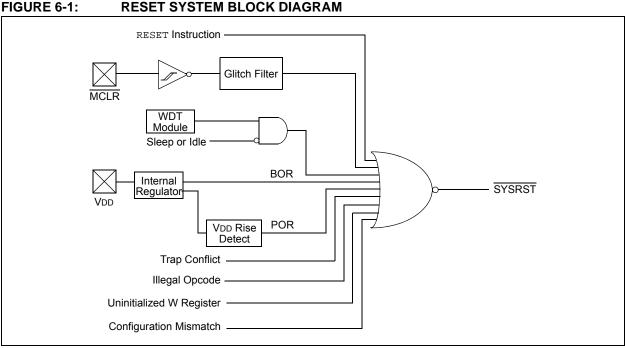

#### 6.0 RESETS

- **Note 1:** This data sheet summarizes the features of the PIC24HJ12GP201/202 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 8. Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state, and some are unaffected.

Refer to the specific peripheral section or Note: Section 3.0 "CPU" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

All bits that are set, with the exception of the POR bit (RCON<0>), are cleared during a POR event. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

### REGISTER 7-16: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

|                    | R/W-1                                                                 | R/W-0                                                    | R/W-0                 | U-0               | R/W-1         | R/W-0            | R/W-0 |  |  |  |

|--------------------|-----------------------------------------------------------------------|----------------------------------------------------------|-----------------------|-------------------|---------------|------------------|-------|--|--|--|

|                    |                                                                       | IC8IP<2:0>                                               |                       | —                 |               | IC7IP<2:0>       |       |  |  |  |

| bit 15             |                                                                       |                                                          |                       |                   |               |                  | bit   |  |  |  |

| U-0                | U-0                                                                   | U-0                                                      | U-0                   | U-0               | R/W-1         | R/W-0            | R/W-0 |  |  |  |

| _                  | _                                                                     | _                                                        | _                     | _                 |               | INT1IP<2:0>      |       |  |  |  |

| bit 7              |                                                                       |                                                          |                       |                   |               |                  | bit   |  |  |  |

| Legend:            |                                                                       |                                                          |                       |                   |               |                  |       |  |  |  |

| R = Readabl        | le hit                                                                | W = Writable                                             | bit                   | U = Unimplen      | nented hit re | n, as ,0,        |       |  |  |  |

| -n = Value at      |                                                                       | '1' = Bit is set                                         |                       | '0' = Bit is cle  |               | x = Bit is unkno | -w/n  |  |  |  |

|                    |                                                                       |                                                          |                       |                   | urcu          |                  | 00011 |  |  |  |

| bit 15             | Unimplemer                                                            | nted: Read as '                                          | 0'                    |                   |               |                  |       |  |  |  |

| bit 14-12          | IC8IP<2:0>:                                                           | Input Capture                                            | Channel 8 Inte        | rrupt Priority bi | ts            |                  |       |  |  |  |

|                    |                                                                       | pt is priority 7 (                                       |                       |                   |               |                  |       |  |  |  |

|                    | •                                                                     |                                                          | <b>3</b>              | ,                 |               |                  |       |  |  |  |

|                    | •                                                                     |                                                          |                       |                   |               |                  |       |  |  |  |

|                    | •                                                                     |                                                          |                       |                   |               |                  |       |  |  |  |

|                    | 001 = Interru                                                         | pt is priority 1                                         | ablad                 |                   |               |                  |       |  |  |  |

| bit 11             |                                                                       | nted: Read as '                                          |                       |                   |               |                  |       |  |  |  |

|                    | -                                                                     |                                                          |                       |                   |               |                  |       |  |  |  |

| bit 10-8           | IC7IP<2:0>: Input Capture Channel 7 Interrupt Priority bits           |                                                          |                       |                   |               |                  |       |  |  |  |

|                    | 111 = Interrupt is priority 7 (highest priority interrupt)            |                                                          |                       |                   |               |                  |       |  |  |  |

|                    | •                                                                     |                                                          |                       |                   |               |                  |       |  |  |  |

|                    |                                                                       |                                                          |                       |                   |               |                  |       |  |  |  |

|                    | •                                                                     |                                                          |                       |                   |               |                  |       |  |  |  |

|                    |                                                                       | pt is priority 1                                         |                       |                   |               |                  |       |  |  |  |

|                    |                                                                       | ipt is priority 1<br>ipt source is dis                   | sabled                |                   |               |                  |       |  |  |  |

| bit 7-3            | 000 = Interru                                                         |                                                          |                       |                   |               |                  |       |  |  |  |

|                    | 000 = Interru<br>Unimplemer                                           | pt source is dis                                         | 0'                    | bits              |               |                  |       |  |  |  |

|                    | 000 = Interru<br>Unimplemer<br>INT1IP<2:0>                            | ipt source is dis<br>nted: Read as '                     | 0'<br>rupt 1 Priority |                   |               |                  |       |  |  |  |

|                    | 000 = Interru<br>Unimplemer<br>INT1IP<2:0>                            | ipt source is dis<br>nted: Read as '<br>: External Inter | 0'<br>rupt 1 Priority |                   |               |                  |       |  |  |  |

| bit 7-3<br>bit 2-0 | 000 = Interru<br>Unimplemer<br>INT1IP<2:0>                            | ipt source is dis<br>nted: Read as '<br>: External Inter | 0'<br>rupt 1 Priority |                   |               |                  |       |  |  |  |

|                    | 000 = Interru<br>Unimplemen<br>INT1IP<2:0><br>111 = Interru<br>•<br>• | ipt source is dis<br>nted: Read as '<br>: External Inter | 0'<br>rupt 1 Priority |                   |               |                  |       |  |  |  |

NOTES:

# 9.0 POWER-SAVING FEATURES

- Note 1: This data sheet summarizes the features of the PIC24HJ12GP201/202 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 9. Watchdog Timer and Power-Saving Modes" (DS70196) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ12GP201/202 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. PIC24HJ12GP201/202 devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

### 9.1 Clock Frequency and Clock Switching

PIC24HJ12GP201/202 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in Section 8.0 "Oscillator Configuration".

#### 9.2 Instruction-Based Power-Saving Modes

PIC24HJ12GP201/202 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The Assembler syntax of the PWRSAV instruction is shown in Example 9-1.

Note: SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to wake-up.

#### 9.2.1 SLEEP MODE

The following events occur in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled

- The LPRC clock continues to run if the WDT is enabled

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode

- Some device features or peripherals may continue to operate. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled

The device will wake-up from Sleep mode on any of the these events:

- · Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

### EXAMPLE 9-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE ; Put the device into Sleep mode

PWRSAV #IDLE\_MODE ; Put the device into Idle mode

### 10.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See **"Pin Diagrams"** for the available pins and their functionality.

### 10.2 Configuring Analog Port Pins

The AD1PCFG and TRIS registers control the operation of the Analog-to-Digital (A/D) port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The AD1PCFGL register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 10.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP. An example is shown in Example 10-1.

### 10.3 Input Change Notification

The input change notification function of the I/O ports allows the PIC24HJ12GP201/202 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 21 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a change-of-state.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

| MOV<br>MOV | 0xFF00, W0<br>W0, TRISBB | ; Configure PORTB<15:8> as inputs<br>; and PORTB<7:0> as outputs |

|------------|--------------------------|------------------------------------------------------------------|

| NOP        |                          | ; Delay 1 cycle                                                  |

| btss       | PORTB, #13               | ; Next Instruction                                               |

#### EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| U-0                | U-0                               | U-0                             | R/W-1        | R/W-1            | R/W-1           | R/W-1            | R/W-1 |

|--------------------|-----------------------------------|---------------------------------|--------------|------------------|-----------------|------------------|-------|

| —                  | —                                 | —                               |              |                  | T3CKR<4:0>      | >                |       |

| bit 15             |                                   |                                 |              |                  |                 |                  | bit 8 |

|                    |                                   |                                 |              |                  |                 |                  |       |

| U-0                | U-0                               | U-0                             | R/W-1        | R/W-1            | R/W-1           | R/W-1            | R/W-1 |

| —                  | _                                 | —                               |              |                  | T2CKR<4:0>      | >                |       |

| bit 7              |                                   |                                 |              |                  |                 |                  | bit C |

|                    |                                   |                                 |              |                  |                 |                  |       |

| Legend:            |                                   |                                 |              |                  |                 |                  |       |

| R = Readab         | le bit                            | W = Writable                    | bit          | U = Unimpler     | nented bit, rea | d as '0'         |       |

| -n = Value a       | t POR                             | '1' = Bit is se                 | t            | '0' = Bit is cle | ared            | x = Bit is unkr  | nown  |

|                    | 11111 = Inpu<br>01111 = Inpu<br>• | ut tied to RP15                 |              |                  |                 |                  |       |

| hit 7-5            | •<br>00001 = Inpu<br>00000 = Inpu | ut tied to RP0                  | ۰ <b>۰</b> , |                  |                 |                  |       |

| bit 7-5<br>bit 4-0 | 00000 = Inpu<br>Unimplemen        | ut tied to RP0<br>Ited: Read as |              |                  |                 | ing RPn pin bits | _     |

#### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0          | U-0                | U-0                               | R/W-1          | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|--------------|--------------------|-----------------------------------|----------------|------------------|-----------------|-----------------|-------|

| —            |                    |                                   |                |                  | IC8R<4:0>       |                 |       |

| bit 15       |                    |                                   |                |                  |                 |                 | bit 8 |

|              |                    |                                   |                |                  |                 |                 |       |

| U-0          | U-0                | U-0                               | R/W-1          | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|              |                    | —                                 |                |                  | IC7R<4:0>       |                 |       |

| bit 7        |                    |                                   |                |                  |                 |                 | bit C |

|              |                    |                                   |                |                  |                 |                 |       |

| Legend:      |                    |                                   |                |                  |                 |                 |       |

| R = Readab   | le bit             | W = Writable                      | bit            | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value a | t POR              | '1' = Bit is set                  | t              | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

|              |                    |                                   |                |                  |                 |                 |       |

| oit 15-13    | Unimpleme          | nted: Read as '                   | 0'             |                  |                 |                 |       |

| oit 12-8     | IC8R<4:0>:         | Assign Input Ca                   | apture 8 (IC8) | to the correspo  | onding pin RPr  | n pin bits      |       |

|              |                    | ut tied to Vss                    |                |                  |                 |                 |       |

|              | 01111 <b>= Inp</b> | ut tied to RP15                   |                |                  |                 |                 |       |

|              | •                  |                                   |                |                  |                 |                 |       |

|              | •                  |                                   |                |                  |                 |                 |       |

|              | •                  |                                   |                |                  |                 |                 |       |

|              |                    | ut tied to RP1                    |                |                  |                 |                 |       |

| bit 7-5      |                    | ut tied to RP0                    | 0'             |                  |                 |                 |       |

|              | -                  | nted: Read as '                   |                |                  | anding sin DD   | a min hita      |       |

| bit 4-0      |                    | Assign Input Ca                   | apture / (IC/) | to the correspo  | onding pin RPr  | n pin dits      |       |

|              |                    | ut tied to Vss<br>ut tied to RP15 |                |                  |                 |                 |       |

|              | •                  |                                   |                |                  |                 |                 |       |

|              | •                  |                                   |                |                  |                 |                 |       |

|              | •                  |                                   |                |                  |                 |                 |       |

|              | 00001 <b>= Inn</b> | ut tied to RP1                    |                |                  |                 |                 |       |

|              |                    | ut tied to RP0                    |                |                  |                 |                 |       |

|              |                    |                                   |                |                  |                 |                 |       |

#### REGISTER 10-5: RPINR10: PERIPHERAL PIN SELECT INPUT REGISTERS 10

| U-0          | U-0                          | U-0                      | R/W-1          | R/W-1                                   | R/W-1           | R/W-1            | R/W-1 |

|--------------|------------------------------|--------------------------|----------------|-----------------------------------------|-----------------|------------------|-------|

| _            | —                            | —                        |                |                                         | U1CTSR<4:0      | )>               |       |

| bit 15       |                              |                          |                |                                         |                 |                  | bit 8 |

|              |                              |                          |                |                                         |                 |                  |       |

| U-0          | U-0                          | U-0                      | R/W-1          | R/W-1                                   | R/W-1           | R/W-1            | R/W-1 |

| _            | —                            | —                        |                |                                         | U1RXR<4:0       | >                |       |

| bit 7        |                              |                          |                |                                         |                 |                  | bit 0 |

|              |                              |                          |                |                                         |                 |                  |       |

| Legend:      |                              |                          |                |                                         |                 |                  |       |

| R = Readab   | le bit                       | W = Writable             | bit            | U = Unimpler                            | mented bit, rea | ad as '0'        |       |

| -n = Value a | t POR                        | '1' = Bit is se          | t              | '0' = Bit is cle                        | ared            | x = Bit is unkr  | nown  |

|              |                              |                          |                |                                         |                 |                  |       |

| bit 15-13    | Unimplemer                   | nted: Read as            | '0'            |                                         |                 |                  |       |

| bit 12-8     | U1CTSR<4:0                   | <b>)&gt;:</b> Assign UAF | RT1 Clear to S | end (U1CTS) t                           | to the correspo | onding RPn pin b | oits  |

|              | 11111 <b>= I</b> npu         |                          |                |                                         |                 |                  |       |

|              | 01111 <b>= Inp</b> i         | ut tied to RP15          |                |                                         |                 |                  |       |

|              | •                            |                          |                |                                         |                 |                  |       |

|              | •                            |                          |                |                                         |                 |                  |       |

|              | •                            | it find to DD1           |                |                                         |                 |                  |       |

|              | 00001 = Inpu<br>00000 = Inpu | ut tied to RP1           |                |                                         |                 |                  |       |

| bit 7-5      |                              | nted: Read as            | ʻ0'            |                                         |                 |                  |       |

| bit 4-0      | -                            | . Assign UAR             |                | 1RX) to the co                          | rrespondina R   | Pn pin bits      |       |

|              | 11111 = Inpu                 | -                        |                | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                 |                  |       |

|              |                              | ut tied to RP15          |                |                                         |                 |                  |       |

|              | •                            |                          |                |                                         |                 |                  |       |

|              | •                            |                          |                |                                         |                 |                  |       |

|              | •                            |                          |                |                                         |                 |                  |       |

|              | 00001 = Inpu                 |                          |                |                                         |                 |                  |       |

|              | 00000 <b>= Inp</b> i         | ut tied to RP0           |                |                                         |                 |                  |       |

|              |                              |                          |                |                                         |                 |                  |       |

#### REGISTER 10-7: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

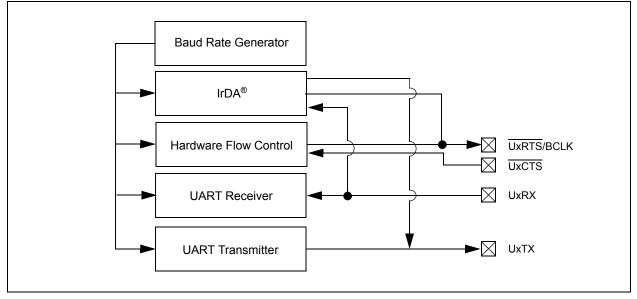

# 17.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the PIC24HJ12GP201/202 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 17. UART" (DS70188) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24HJ12GP201/202 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, and RS-232, and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-bit, or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, Odd, or No Parity options (for 8-bit data)

- · One or two stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-bit prescaler

- Baud rates ranging from 10 Mbps to 38 bps at 40 MIPS

- 4-deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, framing and buffer overrun error detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive interrupts

- · A separate interrupt for all UART error conditions

- · Loopback mode for diagnostic support

- · Support for Sync and Break characters

- · Support for automatic baud rate detection

- IrDA<sup>®</sup> encoder and decoder logic

- 16x baud clock output for IrDA<sup>®</sup> support

A simplified block diagram of the UART module is shown in Figure 17-1. The UART module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

### FIGURE 17-1: UART SIMPLIFIED BLOCK DIAGRAM

NOTES:

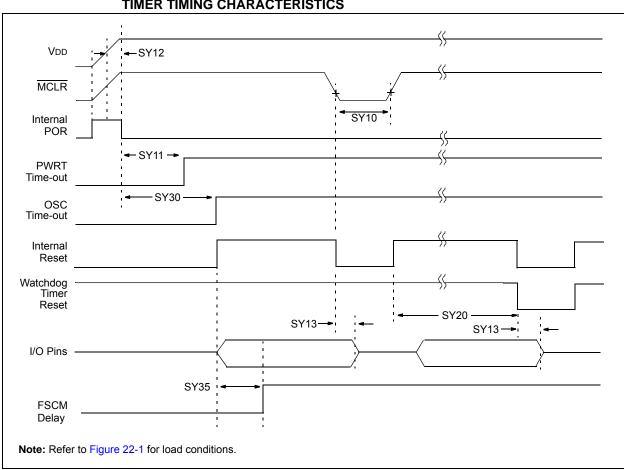

# FIGURE 22-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

|       | RACTERI               | I                           | (2)                          | (unless other<br>Operating terr | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Indus         -40°C ≤TA ≤+125°C for Ext         Min       Max |       |                                                     |  |  |  |

|-------|-----------------------|-----------------------------|------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------|--|--|--|

| Param | Param Symbol Characte |                             | eristic <sup>(2)</sup>       | Min                             | Max                                                                                                                                                                                                  | Units | Conditions                                          |  |  |  |

| IS10  | TLO:SCL               | Clock Low Time              | 100 kHz mode                 | 4.7                             | —                                                                                                                                                                                                    | μs    | Device must operate at a minimum of 1.5 MHz         |  |  |  |

|       |                       |                             | 400 kHz mode                 | 1.3                             | —                                                                                                                                                                                                    | μs    | Device must operate at a minimum of 10 MHz          |  |  |  |

|       |                       |                             | 1 MHz mode <sup>(1)</sup>    | 0.5                             |                                                                                                                                                                                                      | μs    | —                                                   |  |  |  |

| IS11  | THI:SCL               | Clock High Time             | 100 kHz mode                 | 4.0                             | —                                                                                                                                                                                                    | μs    | Device must operate at a minimum of 1.5 MHz         |  |  |  |

|       |                       |                             | 400 kHz mode                 | 0.6                             | _                                                                                                                                                                                                    | μs    | Device must operate at a minimum of 10 MHz          |  |  |  |

|       |                       |                             | 1 MHz mode <sup>(1)</sup>    | 0.5                             |                                                                                                                                                                                                      | μs    | _                                                   |  |  |  |

| IS20  | TF:SCL                | SDAx and SCLx               | 100 kHz mode                 | _                               | 300                                                                                                                                                                                                  | ns    | CB is specified to be from                          |  |  |  |

|       |                       | Fall Time                   | 400 kHz mode                 | 20 + 0.1 Св                     | 300                                                                                                                                                                                                  | ns    | 10 to 400 pF                                        |  |  |  |

|       |                       |                             | 1 MHz mode <sup>(1)</sup>    |                                 | 100                                                                                                                                                                                                  | ns    |                                                     |  |  |  |

| IS21  | TR:SCL                | SDAx and SCLx               | 100 kHz mode                 |                                 | 1000                                                                                                                                                                                                 | ns    | CB is specified to be from                          |  |  |  |

|       |                       | Rise Time                   | 400 kHz mode                 | 20 + 0.1 Св                     | 300                                                                                                                                                                                                  | ns    | 10 to 400 pF                                        |  |  |  |

|       |                       |                             | 1 MHz mode <sup>(1)</sup>    | —                               | 300                                                                                                                                                                                                  | ns    |                                                     |  |  |  |

| IS25  | TSU:DAT               | Data Input                  | 100 kHz mode                 | 250                             | —                                                                                                                                                                                                    | ns    | _                                                   |  |  |  |

|       |                       | Setup Time                  | 400 kHz mode                 | 100                             | —                                                                                                                                                                                                    | ns    |                                                     |  |  |  |

|       |                       |                             | 1 MHz mode <sup>(1)</sup>    | 100                             | —                                                                                                                                                                                                    | ns    |                                                     |  |  |  |

| IS26  | THD:DAT               |                             | 100 kHz mode                 | 0                               | —                                                                                                                                                                                                    | μs    | _                                                   |  |  |  |

|       |                       | Hold Time                   | 400 kHz mode                 | 0                               | 0.9                                                                                                                                                                                                  | μs    |                                                     |  |  |  |

|       |                       |                             | 1 MHz mode <sup>(1)</sup>    | 0                               | 0.3                                                                                                                                                                                                  | μs    |                                                     |  |  |  |

| IS30  | TSU:STA               | Start Condition             | 100 kHz mode                 | 4.7                             | —                                                                                                                                                                                                    | μs    | Only relevant for Repeated                          |  |  |  |

|       |                       | Setup Time                  | 400 kHz mode                 | 0.6                             |                                                                                                                                                                                                      | μs    | Start condition                                     |  |  |  |

|       |                       |                             | 1 MHz mode <sup>(1)</sup>    | 0.25                            |                                                                                                                                                                                                      | μs    |                                                     |  |  |  |

| IS31  | THD:STA               | Start Condition             | 100 kHz mode                 | 4.0                             |                                                                                                                                                                                                      | μs    | After this period, the first                        |  |  |  |

|       |                       | Hold Time                   | 400 kHz mode                 | 0.6                             |                                                                                                                                                                                                      | μs    | clock pulse is generated                            |  |  |  |

|       |                       |                             | 1 MHz mode <sup>(1)</sup>    | 0.25                            |                                                                                                                                                                                                      | μs    |                                                     |  |  |  |

| IS33  | Tsu:sto               | Stop Condition              | 100 kHz mode                 | 4.7                             |                                                                                                                                                                                                      | μs    | _                                                   |  |  |  |

|       |                       | Setup Time                  | 400 kHz mode                 | 0.6                             |                                                                                                                                                                                                      | μs    |                                                     |  |  |  |

|       |                       |                             | 1 MHz mode <sup>(1)</sup>    | 0.6                             |                                                                                                                                                                                                      | μs    |                                                     |  |  |  |

| IS34  | THD:ST                | Stop Condition<br>Hold Time | 100 kHz mode                 | 4000                            | —                                                                                                                                                                                                    | ns    | —                                                   |  |  |  |

|       | 0                     |                             | 400 kHz mode                 | 600                             |                                                                                                                                                                                                      | ns    |                                                     |  |  |  |

| 10.46 | <b>.</b>              |                             | 1 MHz mode <sup>(1)</sup>    | 250                             | 0500                                                                                                                                                                                                 | ns    |                                                     |  |  |  |

| IS40  | TAA:SCL               | Output Valid<br>From Clock  | 100 kHz mode                 | 0                               | 3500                                                                                                                                                                                                 | ns    | _                                                   |  |  |  |

|       |                       |                             | 400 kHz mode                 | 0                               | 1000                                                                                                                                                                                                 | ns    |                                                     |  |  |  |

| 10.45 | <b>T</b> = -          |                             | 1 MHz mode <sup>(1)</sup>    | 0                               | 350                                                                                                                                                                                                  | ns    | Time the base of the f                              |  |  |  |

| IS45  | TBF:SDA               | Bus Free Time               | 100 kHz mode                 | 4.7                             | —                                                                                                                                                                                                    | μs    | Time the bus must be free before a new transmission |  |  |  |

|       |                       |                             | 400 kHz mode                 | 1.3                             | —                                                                                                                                                                                                    | μs    | can start                                           |  |  |  |

| 1050  | 0-                    |                             | 1 MHz mode <sup>(1)</sup>    | 0.5                             |                                                                                                                                                                                                      | μs    |                                                     |  |  |  |

| IS50  | Св                    | Bus Capacitive Lo           | ading<br>= 10 pF for all I2C | <u> </u>                        | 400                                                                                                                                                                                                  | pF    | —                                                   |  |  |  |

| TABLE 22-37: I <sup>2</sup> Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) |

|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------|

Note 1: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

2: These parameters are characterized by similarity, but are not tested in manufacturing.

| AC CHA       |        | STICS                          | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |           |                      |        |                                                  |  |

|--------------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|--------|--------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                 | Min.                                                                                                                                                                                     | Тур       | Max.                 | Units  | Conditions                                       |  |

|              |        | ADC Accuracy (12-bit Mode      | ) – Measure                                                                                                                                                                              | ements w  | vith external        | VREF+/ | VREF- <sup>(3)</sup>                             |  |

| AD20a        | Nr     | Resolution <sup>(4)</sup>      | 1                                                                                                                                                                                        | 2 data bi | ts                   | bits   | —                                                |  |

| AD21a        | INL    | Integral Nonlinearity          | -2                                                                                                                                                                                       | —         | +2                   | LSb    | VINL = AVSS = VREFL =<br>0V, AVDD = VREFH = 3.6V |  |

| AD22a        | DNL    | Differential Nonlinearity      | >-1                                                                                                                                                                                      | —         | <1                   | LSb    | VINL = AVSS = VREFL =<br>0V, AVDD = VREFH = 3.6V |  |

| AD23a        | Gerr   | Gain Error                     | —                                                                                                                                                                                        | 3.4       | 10                   | LSb    | VINL = AVSS = VREFL =<br>0V, AVDD = VREFH = 3.6V |  |

| AD24a        | EOFF   | Offset Error                   | —                                                                                                                                                                                        | 0.9       | 5.0                  | LSb    | VINL = AVSS = VREFL =<br>0V, AVDD = VREFH = 3.6V |  |

| AD25a        | _      | Monotonicity                   |                                                                                                                                                                                          | _         | _                    | _      | Guaranteed <sup>(1)</sup>                        |  |

|              |        | ADC Accuracy (12-bit Mode      | e) – Measure                                                                                                                                                                             | ements v  | vith internal        | VREF+/ | VREF- <sup>(3)</sup>                             |  |

| AD20a        | Nr     | Resolution <sup>(4)</sup>      | 1                                                                                                                                                                                        | 2 data bi | ts                   | bits   | _                                                |  |

| AD21a        | INL    | Integral Nonlinearity          | -2                                                                                                                                                                                       | —         | +2                   | LSb    | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD22a        | DNL    | Differential Nonlinearity      | >-1                                                                                                                                                                                      | —         | <1                   | LSb    | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD23a        | Gerr   | Gain Error                     | —                                                                                                                                                                                        | 10.5      | 20                   | LSb    | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD24a        | EOFF   | Offset Error                   | —                                                                                                                                                                                        | 3.8       | 10                   | LSb    | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD25a        | _      | Monotonicity                   | _                                                                                                                                                                                        | _         |                      | _      | Guaranteed <sup>(1)</sup>                        |  |

|              |        | Dynamic                        | Performance                                                                                                                                                                              | e (12-bit | Mode) <sup>(2)</sup> |        |                                                  |  |

| AD30a        | THD    | Total Harmonic Distortion      |                                                                                                                                                                                          | —         | -75                  | dB     | _                                                |  |

| AD31a        | SINAD  | Signal to Noise and Distortion | 68.5                                                                                                                                                                                     | 69.5      | _                    | dB     | —                                                |  |

| AD32a        | SFDR   | Spurious Free Dynamic<br>Range | 80                                                                                                                                                                                       | —         | _                    | dB     | —                                                |  |

| AD33a        | Fnyq   | Input Signal Bandwidth         |                                                                                                                                                                                          | —         | 250                  | kHz    | —                                                |  |

| AD34a        | ENOB   | Effective Number of Bits       | 11.09                                                                                                                                                                                    | 11.3      | _                    | bits   | —                                                |  |

# TABLE 22-39: ADC MODULE SPECIFICATIONS (12-BIT MODE)

**Note 1:** The A/D conversion result never decreases with an increase in the input voltage, and has no missing codes.

**2:** These parameters are characterized by similarity, but are not tested in manufacturing.

3: These parameters are characterized, but are tested at 20 ksps only.

4: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

| TABLE 22-40: | ADC MODULE SPECIFICATIONS (10-BIT MODE) |  |

|--------------|-----------------------------------------|--|

|--------------|-----------------------------------------|--|

| Param | Symbol |                                | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |            |           |                  |                                                  |  |

|-------|--------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|------------------|--------------------------------------------------|--|

| No.   |        | Characteristic                 | Min.                                                                                                                                                                                     | Тур        | Max.      | Units            | Conditions                                       |  |

|       | •      | ADC Accuracy (10-bit Mode      | ) – Meası                                                                                                                                                                                | urements   | s with ex | ternal V         | REF+/VREF- <sup>(3)</sup>                        |  |

| AD20b | Nr     | Resolution <sup>(4)</sup>      | 1                                                                                                                                                                                        | 0 data bit | ts        | bits             | _                                                |  |

| AD21b | INL    | Integral Nonlinearity          | -1.5                                                                                                                                                                                     | _          | +1.5      | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD22b | DNL    | Differential Nonlinearity      | >-1                                                                                                                                                                                      | —          | <1        | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD23b | Gerr   | Gain Error                     | —                                                                                                                                                                                        | 3          | 6         | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD24b | EOFF   | Offset Error                   | —                                                                                                                                                                                        | 2          | 5         | LSb              | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD25b |        | Monotonicity                   | _                                                                                                                                                                                        |            |           | _                | Guaranteed <sup>(1)</sup>                        |  |

|       |        | ADC Accuracy (10-bit Mode      | e) – Meas                                                                                                                                                                                | urement    | s with in | ternal VF        | REF+/VREF- <sup>(3)</sup>                        |  |

| AD20b | Nr     | Resolution <sup>(4)</sup>      | 1                                                                                                                                                                                        | 0 data bit | ts        | bits             | _                                                |  |

| AD21b | INL    | Integral Nonlinearity          | -1                                                                                                                                                                                       | —          | +1        | LSb              | VINL = AVSS = 0V,<br>AVDD = 3.6V                 |  |

| AD22b | DNL    | Differential Nonlinearity      | >-1                                                                                                                                                                                      | —          | <1        | LSb              | VINL = AVSS = 0V,<br>AVDD = 3.6V                 |  |

| AD23b | Gerr   | Gain Error                     | —                                                                                                                                                                                        | 7          | 15        | LSb              | VINL = AVSS = 0V,<br>AVDD = 3.6V                 |  |

| AD24b | EOFF   | Offset Error                   | —                                                                                                                                                                                        | 3          | 7         | LSb              | VINL = AVSS = 0V,<br>AVDD = 3.6V                 |  |

| AD25b | —      | Monotonicity                   | —                                                                                                                                                                                        | —          | —         | —                | Guaranteed <sup>(1)</sup>                        |  |

|       |        | Dynamic I                      | Performa                                                                                                                                                                                 | nce (10-l  | oit Mode  | ) <sup>(2)</sup> |                                                  |  |

| AD30b | THD    | Total Harmonic Distortion      | _                                                                                                                                                                                        |            | -64       | dB               |                                                  |  |

| AD31b | SINAD  | Signal to Noise and Distortion | 57                                                                                                                                                                                       | 58.5       | —         | dB               | _                                                |  |