#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 12KB (4K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 28-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj12gp202-e-ss |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

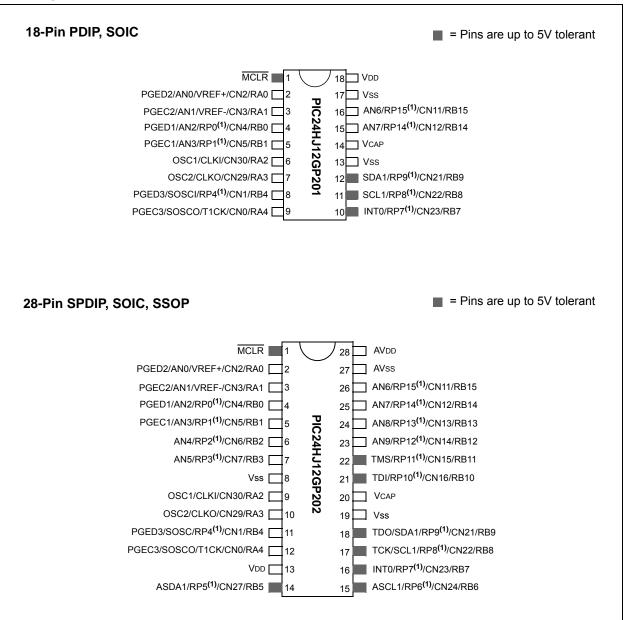

### PIC24HJ12GP201/202 Product Families

The device names, pin counts, memory sizes and peripheral availability of each family are listed below, followed by their pinout diagrams.

|                |      | ory                             |             |                 | Re               | mappa         | ble Pe                     | ripher | als                                |     |                   |       |                |                              |

|----------------|------|---------------------------------|-------------|-----------------|------------------|---------------|----------------------------|--------|------------------------------------|-----|-------------------|-------|----------------|------------------------------|

| Device         | Pins | Program Flash Memory<br>(Kbyte) | RAM (Kbyte) | Remappable Pins | 16-bit Timer     | Input Capture | Output Compare<br>Std. PWM | UART   | External Interrupts <sup>(2)</sup> | IdS | 10-Bit/12-Bit ADC | Ι²Οτω | I/O Pins (Max) | Packages                     |

| PIC24HJ12GP201 | 18   | 12                              | 1           | 8               | 3(1)             | 4             | 2                          | 1      | 3                                  | 1   | 1 ADC, 6 ch       | 1     | 13             | PDIP<br>SOIC                 |

| PIC24HJ12GP202 | 28   | 12                              | 1           | 16              | 3 <sup>(1)</sup> | 4             | 2                          | 1      | 3                                  | 1   | 1 ADC, 10 ch      | 1     | 21             | SPDIP<br>SOIC<br>SSOP<br>QFN |

### TABLE 1: PIC24HJ12GP201/202 CONTROLLER FAMILIES

**Note 1:** Only two out of three timers are remappable.

**2:** Only two out of three interrupts are remappable.

#### **Pin Diagrams**

**Note 1:** The RPn pins can be used by any remappable peripheral. See Table 1 for the list of available peripherals.

#### TABLE 4-16: PORTA REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA     | 02C0 | —      | —      | —      | —      | —      | —      |       | —     |       | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA     | 02C2 | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | XXXX          |

| LATA      | 02C4 | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | XXXX          |

| ODCA      | 02C6 | —      | _      | —      | —      | —      | —      |       | -     |       | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-17: PORTB REGISTER MAP FOR PIC24HJ12GP202

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02CA | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB      | 02CE | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-18: PORTB REGISTER MAP FOR PIC24HJ12GP201

| File Name | Addr | Bit 15  | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|---------------|

| TRISB     | 02C8 | TRISB15 | TRISB14 | _      | _      |        |        | TRISB9 | TRISB8 | TRISB7 |       |       | TRISB4 |       |       | TRISB1 | TRISB0 | C393          |

| PORTB     | 02CA | RB15    | RB14    | _      | _      |        |        | RB9    | RB8    | RB7    | _     | _     | RB4    | _     |       | RB1    | RB0    | xxxx          |

| LATB      | 02CC | LATB15  | LATB14  | _      | _      |        |        | LATB9  | LATB8  | LATB7  | _     |       | LATB4  | _     |       | LATB1  | LATB0  | xxxx          |

| ODCB      | 02CE | ODCB15  | ODCB14  | _      | _      |        |        | ODCB9  | ODCB8  | ODCB7  | _     |       | ODCB4  | _     |       | ODCB1  | ODCB0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

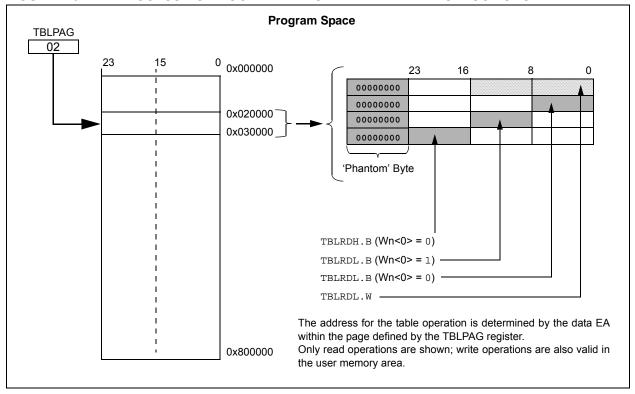

#### 4.4.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte- or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

• TBLRDL (Table Read Low): In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

• TBLRDH (Table Read High): In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, as in the TBLRDL instruction. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

### FIGURE 4-6: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

## **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred 0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | _   | —   |     | —   | —   | —   | DC    |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | C     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| Legend:            |                      |                                    |

|--------------------|----------------------|------------------------------------|

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(1)</sup> 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8)

- Note 1: For complete register details, see Register 3-1: "SR: CPU Status Register".

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

| REGISTER 8-2: | CLKDIV: CLOCK DIVISOR REGISTER <sup>(2)</sup> |

|---------------|-----------------------------------------------|

|---------------|-----------------------------------------------|

| R/W-0         | R/W-0                        | R/W-1                                    | R/W-1         | R/W-0                | R/W-0           | R/W-0              | R/W-0      |

|---------------|------------------------------|------------------------------------------|---------------|----------------------|-----------------|--------------------|------------|

| ROI           |                              | DOZE<2:0>                                |               | DOZEN <sup>(1)</sup> |                 | FRCDIV<2:0>        |            |

| bit 15        |                              |                                          |               |                      |                 |                    | bit 8      |

| R/W-0         | R/W-1                        | U-0                                      | R/W-0         | R/W-0                | R/W-0           | R/W-0              | R/W-0      |

|               | DST<1:0>                     |                                          | 10000         | 1000 0               | PLLPRE<4:0>     |                    | 10000      |

| bit 7         | 501 (1.0)                    |                                          |               |                      |                 |                    | bit        |

|               |                              |                                          |               |                      |                 |                    |            |

| Legend:       |                              | y = Value set f                          | rom Configu   | ration bits on PC    | )R              |                    |            |

| R = Readabl   | e bit                        | W = Writable I                           | oit           | U = Unimplem         | ented bit, read | l as '0'           |            |

| -n = Value at | POR                          | '1' = Bit is set                         |               | '0' = Bit is clea    | ared            | x = Bit is unkr    | nown       |

| bit 15        | ROI: Recove                  | er on Interrupt bi                       | t             |                      |                 |                    |            |

|               | 1 = Interrupt                | ts will clear the I<br>ts have no effect | OZEN bit a    |                      | clock/periphe   | ral clock ratio is | set to 1:1 |

| bit 14-12     | •                            | : Processor Cloc                         |               |                      |                 |                    |            |

|               | 111 = Fcy/1                  | 28                                       |               |                      |                 |                    |            |

|               | 110 = FCY/6                  |                                          |               |                      |                 |                    |            |

|               | 101 = FCY/3                  |                                          |               |                      |                 |                    |            |

|               | 100 = Fcy/1<br>011 = Fcy/8   |                                          |               |                      |                 |                    |            |

|               | 010 = FCY/4                  |                                          |               |                      |                 |                    |            |

|               | 001 = Fcy/2                  |                                          |               |                      |                 |                    |            |

|               | 000 = Fcy/1                  |                                          |               |                      |                 |                    |            |

| bit 11        |                              | ZE Mode Enable                           |               |                      |                 |                    |            |

|               |                              | 2:0> field specifi<br>or clock/periphe   |               |                      | pheral clocks a | and the process    | or clocks  |

| bit 10-8      | FRCDIV<2:0                   | >: Internal Fast                         | RC Oscillato  | or Postscaler bits   | ;               |                    |            |

|               | 111 <b>= FRC c</b>           |                                          |               |                      |                 |                    |            |

|               | 110 = FRC c                  |                                          |               |                      |                 |                    |            |

|               | 101 = FRC o<br>100 = FRC o   |                                          |               |                      |                 |                    |            |

|               | 011 <b>= FRC</b> o           |                                          |               |                      |                 |                    |            |

|               | 010 <b>= FRC c</b>           |                                          |               |                      |                 |                    |            |

|               | 001 <b>= FRC c</b>           |                                          |               |                      |                 |                    |            |

|               |                              | divide by 1 (defa                        | ,             |                      |                 |                    |            |

| bit 7-6       |                              | I: <b>0&gt;:</b> PLL VCO (               | Dutput Divide | er Select bits (als  | so denoted as   | 'N2', PLL posts    | caler)     |

|               | 00 = Output/<br>01 = Output/ |                                          |               |                      |                 |                    |            |

|               | 10 = Reserv                  | • •                                      |               |                      |                 |                    |            |

|               | 11 = Output/                 |                                          |               |                      |                 |                    |            |

| bit 5         | Unimpleme                    | nted: Read as 'd                         | )'            |                      |                 |                    |            |

| bit 4-0       | PLLPRE<4:                    | 0>: PLL Phase [                          | Detector Inpu | it Divider bits (al  | so denoted as   | 'N1', PLL prese    | caler)     |

|               | 00000 <b>= Inp</b>           | ut/2 (default)                           |               |                      |                 |                    |            |

|               |                              |                                          |               |                      |                 |                    |            |

|               | 00001 <b>= Inp</b>           | ut/3                                     |               |                      |                 |                    |            |

|               | 00001 = Inp                  | ut/3                                     |               |                      |                 |                    |            |

|               | 00001 = Inp<br>•<br>•        | ut/3                                     |               |                      |                 |                    |            |

Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

**2:** This register is reset only on a Power-on Reset (POR).

NOTES:

| U-0                        | U-0                             | R/W-0                               | R/W-0                   | R/W-0                            | U-0             | U-0            | U-0                  |

|----------------------------|---------------------------------|-------------------------------------|-------------------------|----------------------------------|-----------------|----------------|----------------------|

| _                          | —                               | T3MD                                | T2MD                    | T1MD                             | —               | —              | —                    |

| bit 15                     | ·                               | ·                                   |                         |                                  |                 | -              | bit                  |

|                            |                                 |                                     |                         |                                  |                 |                |                      |

| R/W-0                      | U-0                             | R/W-0                               | U-0                     | R/W-0                            | U-0             | U-0            | R/W-0                |

| I2C1MD                     |                                 | U1MD                                | —                       | SPI1MD                           | —               | _              | AD1MD <sup>(1)</sup> |

| bit 7                      |                                 |                                     |                         |                                  |                 |                | bit                  |

| <u> </u>                   |                                 |                                     |                         |                                  |                 |                |                      |

| Legend:                    |                                 |                                     | L:4                     |                                  | nanted bit was  | d ee (0)       |                      |

| R = Readab<br>-n = Value a |                                 | W = Writable<br>'1' = Bit is set    |                         | 0 = Unimpler<br>'0' = Bit is cle | nented bit, rea | x = Bit is unk | (20)1/2              |

|                            | IL FOR                          |                                     |                         |                                  | aleu            |                |                      |

| bit 15-14                  | Unimpleme                       | nted: Read as '                     | ٥'                      |                                  |                 |                |                      |

| bit 13                     | -                               | r3 Module Disal                     |                         |                                  |                 |                |                      |

|                            |                                 | nodule is disable                   |                         |                                  |                 |                |                      |

|                            | 0 = Timer3 n                    | nodule is enable                    | ed                      |                                  |                 |                |                      |

| bit 12                     | T2MD: Time                      | r2 Module Disa                      | ole bit                 |                                  |                 |                |                      |

|                            | -                               | nodule is disable                   |                         |                                  |                 |                |                      |

| bit 11                     |                                 | nodule is enable<br>r1 Module Disal |                         |                                  |                 |                |                      |

|                            | -                               | nodule is disabl                    |                         |                                  |                 |                |                      |

|                            | -                               | nodule is enable                    |                         |                                  |                 |                |                      |

| bit 10-8                   | Unimpleme                       | nted: Read as '                     | 0'                      |                                  |                 |                |                      |

| bit 7                      | <b>12C1MD:</b> 1 <sup>2</sup> C | 1 Module Disat                      | ole bit                 |                                  |                 |                |                      |

|                            |                                 | dule is disabled                    |                         |                                  |                 |                |                      |

|                            |                                 | dule is enabled                     |                         |                                  |                 |                |                      |

| bit 6                      | -                               | nted: Read as '                     |                         |                                  |                 |                |                      |

| bit 5                      |                                 | T1 Module Disa                      |                         |                                  |                 |                |                      |

|                            | -                               | nodule is disabl<br>nodule is enabl |                         |                                  |                 |                |                      |

| bit 4                      |                                 | nted: Read as '                     |                         |                                  |                 |                |                      |

| bit 3                      | -                               | PI1 Module Disa                     |                         |                                  |                 |                |                      |

|                            | 1 = SPI1 mo                     | dule is disabled                    |                         |                                  |                 |                |                      |

|                            |                                 | dule is enabled                     |                         |                                  |                 |                |                      |

| bit 2-1                    | •                               | nted: Read as '                     |                         |                                  |                 |                |                      |

| bit 0                      | AD1MD: AD                       | C1 Module Disa                      | able bit <sup>(1)</sup> |                                  |                 |                |                      |

|                            |                                 | odule is disable                    |                         |                                  |                 |                |                      |

**Note 1:** PCFGx bits have no effect if the ADC module is disabled by setting this bit. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

| U-0                | U-0                               | U-0                             | R/W-1        | R/W-1            | R/W-1           | R/W-1            | R/W-1 |

|--------------------|-----------------------------------|---------------------------------|--------------|------------------|-----------------|------------------|-------|

| —                  | —                                 | —                               |              |                  | T3CKR<4:0>      | >                |       |

| bit 15             |                                   |                                 |              |                  |                 |                  | bit 8 |

|                    |                                   |                                 |              |                  |                 |                  |       |

| U-0                | U-0                               | U-0                             | R/W-1        | R/W-1            | R/W-1           | R/W-1            | R/W-1 |

| —                  | _                                 | —                               |              |                  | T2CKR<4:0>      | >                |       |

| bit 7              |                                   |                                 |              |                  |                 |                  | bit C |

|                    |                                   |                                 |              |                  |                 |                  |       |

| Legend:            |                                   |                                 |              |                  |                 |                  |       |

| R = Readab         | le bit                            | W = Writable                    | bit          | U = Unimpler     | nented bit, rea | d as '0'         |       |

| -n = Value a       | t POR                             | '1' = Bit is se                 | t            | '0' = Bit is cle | ared            | x = Bit is unkr  | nown  |

|                    | 11111 = Inpu<br>01111 = Inpu<br>• | ut tied to RP15                 |              |                  |                 |                  |       |

| hit 7-5            | •<br>00001 = Inpu<br>00000 = Inpu | ut tied to RP0                  | ۰ <b>۰</b> , |                  |                 |                  |       |

| bit 7-5<br>bit 4-0 | 00000 = Inpu<br>Unimplemen        | ut tied to RP0<br>Ited: Read as |              |                  |                 | ing RPn pin bits | _     |

#### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

#### REGISTER 10-12: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

| U-0                               | U-0 | U-0 | R/W-0     | R/W-0                              | R/W-0     | R/W-0 | R/W-0 |  |  |

|-----------------------------------|-----|-----|-----------|------------------------------------|-----------|-------|-------|--|--|

| —                                 | _   | —   | RP5R<4:0> |                                    |           |       |       |  |  |

| bit 15                            |     |     |           |                                    |           |       | bit 8 |  |  |

|                                   |     |     |           |                                    |           |       |       |  |  |

| U-0                               | U-0 | U-0 | R/W-0     | R/W-0                              | R/W-0     | R/W-0 | R/W-0 |  |  |

| —                                 | _   | —   |           |                                    | RP4R<4:0> |       |       |  |  |

| bit 7                             | ·   |     |           |                                    |           |       | bit 0 |  |  |

|                                   |     |     |           |                                    |           |       |       |  |  |

| Legend:                           |     |     |           |                                    |           |       |       |  |  |

| R = Readable bit W = Writable bit |     |     |           | U = Unimplemented bit, read as '0' |           |       |       |  |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

- bit 12-8 **RP5R<4:0>:** Peripheral Output Function is Assigned to RP5 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP4R<4:0>:** Peripheral Output Function is Assigned to RP4 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-13: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP7R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP6R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP7R<4:0>:** Peripheral Output Function is Assigned to RP7 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP6R<4:0>:** Peripheral Output Function is Assigned to RP6 Output Pin bits (see Table 10-2 for peripheral function numbers)

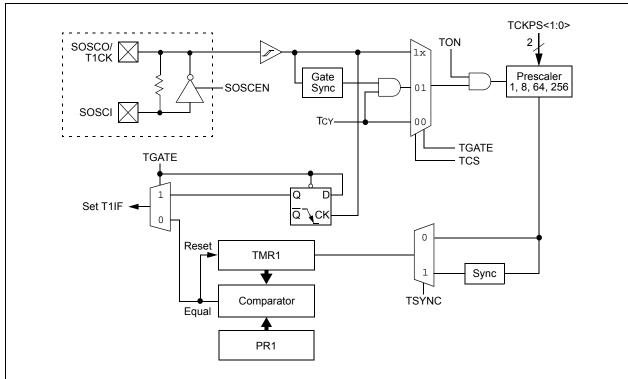

### 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the PIC24HJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 11. Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

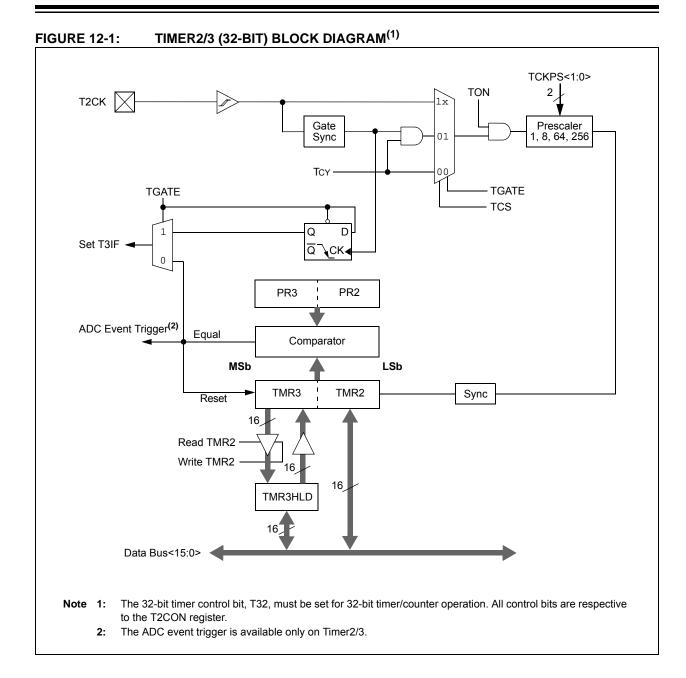

Figure 11-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

#### FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

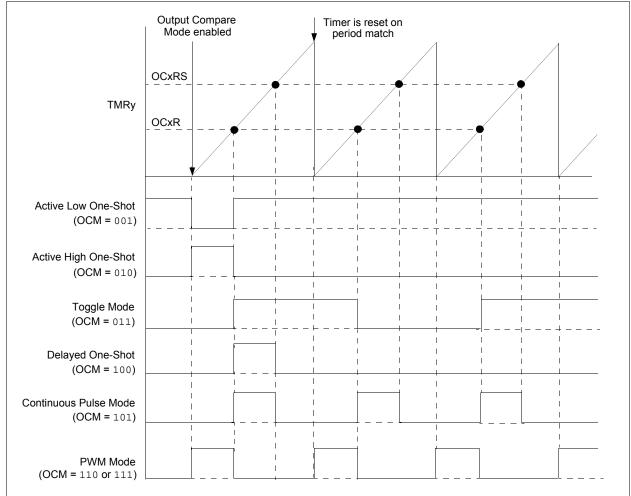

### 14.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode (OCM<2:0>) bits in the Output Compare Control (OCxCON<2:0>) register. Table 14-1 lists the different bit settings for the Output Compare modes. Figure 14-2 illustrates the output compare operation for various modes. The user

TABLE 14-1: OUTPUT COMPARE MODES

application must disable the associated timer when writing to the output compare control registers to avoid malfunctions.

| Note: | See Section 13. "Output Compare" i    | n |

|-------|---------------------------------------|---|

|       | the "dsPIC33F/PIC24H Family Reference | е |

|       | Manual" (DS70209) for OCxR an         | d |

|       | OCxRS register restrictions.          |   |

| OCM<2:0> | Mode                                 | OCx Pin Initial State                        | OCx Interrupt Generation         |  |  |

|----------|--------------------------------------|----------------------------------------------|----------------------------------|--|--|

| 000      | Module Disabled                      | Controlled by GPIO register                  | —                                |  |  |

| 001      | Active-Low One-Shot                  | 0                                            | OCx Rising edge                  |  |  |

| 010      | Active-High One-Shot                 | 1                                            | OCx Falling edge                 |  |  |

| 011      | Toggle Mode                          | Current output is maintained                 | OCx Rising and Falling edge      |  |  |

| 100      | Delayed One-Shot                     | 0                                            | OCx Falling edge                 |  |  |

| 101      | Continuous Pulse mode                | 0                                            | OCx Falling edge                 |  |  |

| 110      | PWM mode without fault<br>protection | 0, if OCxR is zero<br>1, if OCxR is non-zero | No interrupt                     |  |  |

| 111      | PWM mode with fault protection       | 0, if OCxR is zero<br>1, if OCxR is non-zero | OCFA Falling edge for OC1 to OC4 |  |  |

#### FIGURE 14-2: OUTPUT COMPARE OPERATION

| REGISTER      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 150: ADCT IN                                             |                        |                  |                  |                 |       |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------|------------------|------------------|-----------------|-------|--|--|

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                      | R/W-0                  | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

| CHONB         | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                                                        |                        |                  | CH0SB<4:0>       |                 |       |  |  |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                        |                  |                  |                 | bit   |  |  |

| R/W-0         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                      | R/W-0                  | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

| CH0NA         | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                                                        |                        |                  | CH0SA<4:0>       |                 |       |  |  |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                        |                  |                  |                 | bit   |  |  |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                        |                  |                  |                 |       |  |  |

| R = Readable  | e bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | W = Writable b                                           | oit                    | U = Unimpler     | mented bit, read | d as '0'        |       |  |  |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | '1' = Bit is set                                         |                        | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                        |                  |                  |                 |       |  |  |

|               | 1 = Channel (<br>0 = Channel (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | nnel 0 Negative<br>) negative input<br>) negative input  | is AN1<br>is VREF-     |                  |                  |                 |       |  |  |

| bit 14-13     | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                          |                        |                  |                  |                 |       |  |  |

|               | CH0SB<4:0>: Channel 0 Positive Input Select for Sample B bits<br>PIC24HJ12GP201 devices only:<br>00111 = Channel 0 positive input is AN7<br>00100 = Channel 0 positive input is AN6<br>00101 = Reserved<br>00011 = Channel 0 positive input is AN3<br>00010 = Channel 0 positive input is AN2<br>00001 = Channel 0 positive input is AN1<br>00000 = Channel 0 positive input is AN0<br>PIC24HJ12GP202 devices only:<br>01001 = Channel 0 positive input is AN9<br>•<br>•<br>•<br>00010 = Channel 0 positive input is AN2 |                                                          |                        |                  |                  |                 |       |  |  |

| bit 7         | <b>CH0NA:</b> Char<br>1 = Channel (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | nnel 0 positive i<br>nnel 0 Negative<br>) negative input | Input Select<br>is AN1 | for Sample A b   | it               |                 |       |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ) negative input                                         |                        |                  |                  |                 |       |  |  |

| bit 6-5       | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ted: Read as '0                                          | ,                      |                  |                  |                 |       |  |  |

#### REGISTER 18-5: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

NOTES:

#### TABLE 22-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARAC        | TERISTICS              |                  | (unless oth | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |       |                                                |  |  |  |  |

|------------------|------------------------|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------|--|--|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup> | Max              | Units       | Conditions                                                                                                                                                                               |       |                                                |  |  |  |  |

| Power-Down       | Current (IPD)          | ) <sup>(2)</sup> |             |                                                                                                                                                                                          |       |                                                |  |  |  |  |

| DC60d            | 55                     | 500              | μA          | -40°C                                                                                                                                                                                    |       |                                                |  |  |  |  |

| DC60a            | 63                     | 500              | μA          | +25°C                                                                                                                                                                                    | 3.3V  | Base Power-Down Current <sup>(3,4)</sup>       |  |  |  |  |

| DC60b            | 85                     | 500              | μA          | +85°C                                                                                                                                                                                    | 3.3V  | Base Power-Down Current                        |  |  |  |  |

| DC60c            | 146                    | 1000             | μA          | +125°C                                                                                                                                                                                   |       |                                                |  |  |  |  |

| DC61d            | 8                      | 13               | μA          | -40°C                                                                                                                                                                                    |       |                                                |  |  |  |  |

| DC61a            | 10                     | 15               | μA          | +25°C                                                                                                                                                                                    | 2 2)/ | Watchdog Timer Current: ∆IwDT <sup>(3,5)</sup> |  |  |  |  |

| DC61b            | 12                     | 20               | μA          | +85°C                                                                                                                                                                                    | 3.3V  |                                                |  |  |  |  |

| DC61c            | 13                     | 25               | μA          | +125°C                                                                                                                                                                                   |       |                                                |  |  |  |  |

Note 1: Data in the Typical column is at 3.3V, 25°C unless otherwise stated.

2: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss, WDT, etc., are all switched off, and VREGS (RCON<8>) = 1.

**3:** The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

4: These currents are measured on the device containing the most memory in this family.

5: These parameters are characterized, but are not tested in manufacturing.

#### TABLE 22-8: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTERI | STICS                        | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |       |     |         |      |         |

|---------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|---------|------|---------|

| Parameter No. | Doze<br>Ratio <sup>(2)</sup> | Units                                                                                                                                                                                    |       | Con | ditions |      |         |

| DC73a         | 11                           | 35                                                                                                                                                                                       | 1:2   | mA  |         |      |         |

| DC73f         | 11                           | 30                                                                                                                                                                                       | 1:64  | mA  | -40°C   | 3.3V | 40 MIPS |

| DC73g         | 11                           | 30                                                                                                                                                                                       | 1:128 | mA  |         |      |         |

| DC70a         | 11                           | 50                                                                                                                                                                                       | 1:2   | mA  |         |      | 40 MIPS |

| DC70f         | 11                           | 30                                                                                                                                                                                       | 1:64  | mA  | +25°C   | 3.3V |         |

| DC70g         | 11                           | 30                                                                                                                                                                                       | 1:128 | mA  |         |      |         |

| DC71a         | 12                           | 50                                                                                                                                                                                       | 1:2   | mA  |         |      |         |

| DC71f         | 12                           | 30                                                                                                                                                                                       | 1:64  | mA  | +85°C   | 3.3V | 40 MIPS |

| DC71g         | 12                           | 30                                                                                                                                                                                       | 1:128 | mA  | ]       |      |         |

| DC72a         | 12                           | 50                                                                                                                                                                                       | 1:2   | mA  |         |      |         |

| DC72f         | 12                           | 30                                                                                                                                                                                       | 1:64  | mA  | +125°C  | 3.3V | 40 MIPS |

| DC72g         | 12                           | 30                                                                                                                                                                                       | 1:128 | mA  |         |      |         |

Note 1: Data in the Typical column is at 3.3V, 25°C unless otherwise stated.

2: Parameters with DOZE ratios of 1:2 and 1:64 are characterized, but are not tested in manufacturing.

#### TABLE 22-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |        |                     | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |   |     |   |                           |  |

|--------------------|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|---------------------------|--|

| Param<br>No.       | Symbol | Characteristic      | Min Typ Max Units Conditions                                                                                                                                                             |   |     |   |                           |  |

|                    | Vol    | Output Low Voltage  |                                                                                                                                                                                          |   |     |   |                           |  |

| DO10               |        | I/O ports           | —                                                                                                                                                                                        |   | 0.4 | V | Iol = 2mA, Vdd = 3.3V     |  |

| DO16               |        | OSC2/CLKO           | —                                                                                                                                                                                        | — | 0.4 | V | IOL = 2mA, VDD = 3.3V     |  |

|                    | Vон    | Output High Voltage |                                                                                                                                                                                          |   |     |   |                           |  |

| DO20               |        | I/O ports           | 2.40 — V IOH = -2.3 mA, VDD = 3.3V                                                                                                                                                       |   |     |   |                           |  |

| DO26               |        | OSC2/CLKO           | 2.41                                                                                                                                                                                     |   | —   | V | Iон = -1.3 mA, Vdd = 3.3V |  |

#### TABLE 22-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHAR      | ACTERIST | ACTERISTICS Operating tem               |       |      |     |      |       |            |  |

|--------------|----------|-----------------------------------------|-------|------|-----|------|-------|------------|--|

| Param<br>No. | Symbol   | Character                               | istic | Min  | Тур | Max  | Units | Conditions |  |

| BO10         | VBOR     | BOR Event on VDD transition high-to-low |       | 2.40 |     | 2.55 | V     | Vdd        |  |

**Note 1:** Parameters are for design guidance only and are not tested in manufacturing.

#### 22.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC24HJ12GP201/202 AC characteristics and timing parameters.

#### TABLE 22-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)                                                                                                                    |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AC CHARACTERISTICS | Operating temperature -40°C ≤TA ≤+85°C for Industrial<br>-40°C ≤TA ≤+125°C for Extended<br>Operating voltage VDD range as described in <b>Section 22.1 "DC</b><br><b>Characteristics</b> ". |  |  |  |

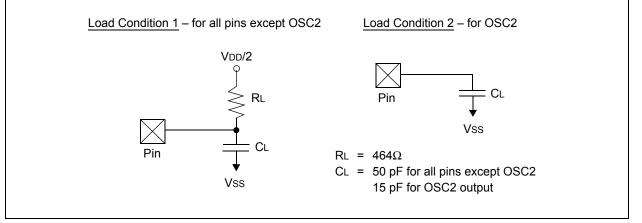

#### FIGURE 22-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 22-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Тур | Max | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|-----|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosc2  | OSC2/SOSC2 pin        | _   | —   | 15  |       | In XT and HS modes when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O pins and OSC2 | —   | —   | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            | _   |     | 400 | pF    | In l <sup>2</sup> C™ mode                                          |

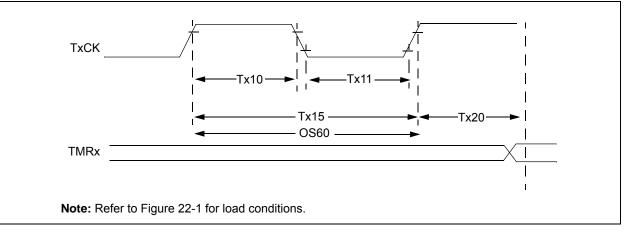

#### FIGURE 22-5: TIMER1, 2, 3 AND 4 EXTERNAL CLOCK TIMING CHARACTERISTICS

| AC CHARACTERISTICS |           |                                                                                                         |                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                               |     |                  |       |                                                                               |  |

|--------------------|-----------|---------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------|-----------------------------------------------|-----|------------------|-------|-------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol    | Characteristic                                                                                          |                                |                                                      | Min                                           | Тур | Мах              | Units | Conditions                                                                    |  |

| TA10               | ТтхН      | TxCK High Time                                                                                          | Synchronous, no prescaler      |                                                      | Тсү + 20                                      |     | _                | ns    | Must also meet<br>parameter TA15.<br>N = prescale<br>value<br>(1, 8, 64, 256) |  |

|                    |           |                                                                                                         | Synchronous, with prescaler    |                                                      | (Tcy + 20)/N                                  |     | _                | ns    |                                                                               |  |

|                    |           |                                                                                                         | Asynchronous                   |                                                      | 20                                            | _   | —                | ns    |                                                                               |  |

| TA11               | ΤτχL      | TxCK Low Time                                                                                           | Synchronous, no prescaler      |                                                      | (Tcy + 20)                                    | _   | —                | ns    | Must also meet<br>parameter TA15.<br>N = prescale<br>value<br>(1, 8, 64, 256) |  |

|                    |           |                                                                                                         | Synchronous, with prescaler    |                                                      | (Tcy + 20)/N                                  | _   | —                | ns    |                                                                               |  |

|                    |           |                                                                                                         | Asynchronous                   |                                                      | 20                                            |     | _                | ns    |                                                                               |  |

| TA15               | ΤτχΡ      | TxCK Input<br>Period                                                                                    | Synchronous, no prescaler      |                                                      | 2 Tcy + 40                                    | _   | —                | ns    | —                                                                             |  |

|                    |           |                                                                                                         | Synchronous,<br>with prescaler |                                                      | Greater of:<br>40 ns or<br>(2 TCY + 40)/<br>N | _   | _                | _     | N = prescale<br>value<br>(1, 8, 64, 256)                                      |  |

|                    |           |                                                                                                         | Asynchronous                   |                                                      | 40                                            | _   | _                | ns    | —                                                                             |  |

| OS60               | Ft1       | SOSCI/T1CK Oscillator Input<br>frequency Range (oscillator<br>enabled by setting bit TCS<br>(T1CON<1>)) |                                |                                                      | DC                                            |     | 50               | kHz   | —                                                                             |  |

| TA20               | TCKEXTMRL | Delay from External TxCK Clock<br>Edge to Timer Increment                                               |                                |                                                      | 0.75 Tcy +<br>40                              |     | 1.75 Tcy +<br>40 |       | _                                                                             |  |

### TABLE 22-22: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

Note 1: Timer1 is a Type A.