# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 12KB (4K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj12gp202-i-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                        | 9     |

|-------|------------------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-bit Microcontrollers            | 13    |

| 3.0   | CPU                                                                    |       |

| 4.0   | Memory Organization                                                    | 25    |

| 5.0   | Flash Program Memory                                                   | 45    |

| 6.0   | Resets                                                                 | 51    |

| 7.0   | Interrupt Controller                                                   | 59    |

| 8.0   | Oscillator Configuration                                               | 87    |

| 9.0   | Power-Saving Features                                                  | 97    |

| 10.0  | I/O Ports                                                              | . 101 |

| 11.0  | Timer1                                                                 | . 119 |

| 12.0  | Timer2/3 Feature                                                       | . 121 |

| 13.0  | Input Capture                                                          | . 127 |

| 14.0  | Output Compare                                                         | . 129 |

| 15.0  | Serial Peripheral Interface (SPI)                                      |       |

| 16.0  | Inter-Integrated Circuit <sup>™</sup> (I <sup>2</sup> C <sup>™</sup> ) | . 139 |

| 17.0  | Universal Asynchronous Receiver Transmitter (UART)                     | . 147 |

| 18.0  | 10-bit/12-bit Analog-to-Digital Converter (ADC)                        | . 153 |

| 19.0  | Special Features                                                       | . 167 |

| 20.0  | Instruction Set Summary                                                | . 175 |

| 21.0  | Development Support                                                    | . 183 |

|       | Electrical Characteristics                                             |       |

| 23.0  | Packaging Information                                                  | . 231 |

| Appe  | ndix A: Revision History                                               | . 245 |

| Index |                                                                        | 255   |

|       | ficrochip Web Site                                                     |       |

| Custo | mer Change Notification Service                                        | . 259 |

| Custo | mer Support                                                            | . 259 |

| Read  | er Response                                                            | . 260 |

| Produ | Ict Identification System                                              | . 261 |

|       |                                                                        |       |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

· Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 1.1 Referenced Sources

This device data sheet is based on the following individual chapters of the *"dsPlC33F/PlC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the PIC24HJ12GP202 product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory (DS70202)

- Section 4. "Program Memory" (DS70202)

- Section 5. "Flash Programming" (DS70191)

- Section 6. "Interrupts" (DS70184)

- Section 7. "Oscillator" (DS70186)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-saving Modes" (DS70196)

- Section 10. "I/O Ports" (DS70193)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 16. "Analog-to-Digital Converter (ADC) with DMA" (DS70183)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Section 23. "CodeGuard Security" (DS70199)

- Section 25. "Device Configuration" (DS70194)

| <b>TABLE 4-14</b> : | ADC1 REGISTER MAP FOR PIC24HJ12GP201 |

|---------------------|--------------------------------------|

|---------------------|--------------------------------------|

| IADLE 4-  | 14. / | ADCIN  | LOIST                 |        | FURFIC | 5241151 | 26720     | 1       |          |           |           |       |       |        |           |         |         |               |

|-----------|-------|--------|-----------------------|--------|--------|---------|-----------|---------|----------|-----------|-----------|-------|-------|--------|-----------|---------|---------|---------------|

| File Name | Addr  | Bit 15 | Bit 14                | Bit 13 | Bit 12 | Bit 11  | Bit 10    | Bit 9   | Bit 8    | Bit 7     | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300  |        | ADC Data Buffer 0 x   |        |        |         |           |         |          |           |           |       |       |        | xxxx      |         |         |               |

| ADC1BUF1  | 0302  |        | ADC Data Buffer 1 xx  |        |        |         |           |         |          |           |           |       |       |        | xxxx      |         |         |               |

| ADC1BUF2  | 0304  |        | ADC Data Buffer 2 xxx |        |        |         |           |         |          |           |           |       |       |        | xxxx      |         |         |               |

| ADC1BUF3  | 0306  |        | ADC Data Buffer 3 xxx |        |        |         |           |         |          |           |           |       |       |        | xxxx      |         |         |               |

| ADC1BUF4  | 0308  |        | ADC Data Buffer 4     |        |        |         |           |         |          |           |           |       |       |        | xxxx      |         |         |               |

| ADC1BUF5  | 030A  |        |                       |        |        |         |           |         | ADC Data | Buffer 5  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF6  | 030C  |        |                       |        |        |         |           |         | ADC Data | Buffer 6  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF7  | 030E  |        |                       |        |        |         |           |         | ADC Data | Buffer 7  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF8  | 0310  |        |                       |        |        |         |           |         | ADC Data | Buffer 8  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF9  | 0312  |        |                       |        |        |         |           |         | ADC Data | Buffer 9  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFA  | 0314  |        |                       |        |        |         |           |         | ADC Data | Buffer 10 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFB  | 0316  |        |                       |        |        |         |           |         | ADC Data | Buffer 11 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFC  | 0318  |        |                       |        |        |         |           |         | ADC Data | Buffer 12 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFD  | 031A  |        |                       |        |        |         |           |         | ADC Data | Buffer 13 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFE  | 031C  |        |                       |        |        |         |           |         | ADC Data | Buffer 14 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFF  | 031E  |        |                       |        |        |         |           |         | ADC Data | Buffer 15 |           |       |       |        |           |         |         | xxxx          |

| AD1CON1   | 0320  | ADON   |                       | ADSIDL | _      | —       | AD12B     | FOR     | M<1:0>   | Ś         | SSRC<2:0> |       | -     | SIMSAM | ASAM      | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322  |        | VCFG<2:0>             | >      | —      | —       | CSCNA     | CHF     | PS<1:0>  | BUFS      | —         |       | SMPI  | <3:0>  |           | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324  | ADRC   | _                     | —      |        | S       | SAMC<4:0> | >       | 1        |           |           |       | ADCS  | <7:0>  | r         |         | I       | 0000          |

| AD1CHS123 | 0326  | —      | _                     | —      | —      | —       |           | NB<1:0> | CH123SB  | —         | _         | _     | —     | —      |           | NA<1:0> | CH123SA | 0000          |

| AD1CHS0   | 0328  | CH0NB  |                       | —      |        | С       | H0SB<4:0  | >       |          | CH0NA     | _         |       |       | -      | CH0SA<4:0 |         |         | 0000          |

| AD1PCFGL  | 032C  | _      |                       | —      | _      | _       | —         |         | —        | PCGG7     | PCGF6     |       |       | PCFG3  | PCFG2     | PCFG1   | PCFG0   | 0000          |

| AD1CSSL   | 0330  | —      | —                     | —      | _      | —       | —         | —       | —        | CSS7      | CSS6      | —     | —     | CSS3   | CSS2      | CSS1    | CSS0    | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the PIC24HJ12GP201/202 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 4. Program Memory" (DS70202) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ12GP201/202 devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a PIC24HJ12GP201/202 device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows users to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user application can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) or a single program memory word, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes).

### 5.1 Table Instructions and Flash Programming

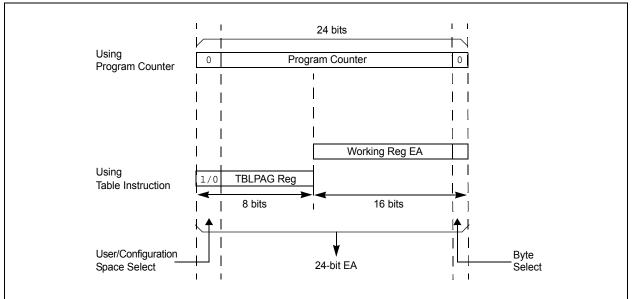

Regardless of the method used, all programming of Flash memory is done with the table-read and tablewrite instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits <7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

|   |                          | -                           |     |                                         |

|---|--------------------------|-----------------------------|-----|-----------------------------------------|

| ; | -                        | N for row programming opera | ati | zions                                   |

|   | MOV                      | #0x4001, W0                 | ;   | ;                                       |

|   | MOV                      | W0, NVMCON                  | ;   | ; Initialize NVMCON                     |

|   |                          |                             |     | emory location to be written            |

| ; | program memo:            | ry selected, and writes ena | ab] | pled                                    |

|   |                          | #0x0000, W0                 | ;   | ;                                       |

|   | MOV                      | W0, TBLPAG                  | ;   | ; Initialize PM Page Boundary SFR       |

|   | MOV                      | #0x6000, W0                 | ;   | ; An example program memory address     |

| ; | Perform the              | TBLWT instructions to write | e t | the latches                             |

| ; | 0th_program_             | word                        |     |                                         |

|   | MOV                      | #LOW_WORD_0, W2             | ;   | ;                                       |

|   | MOV                      | <pre>#HIGH_BYTE_0, W3</pre> | ;   | ;                                       |

|   | TBLWTL                   | W2, [W0]                    | ;   | ; Write PM low word into program latch  |

|   | TBLWTH                   | W3, [W0++]                  | ;   | ; Write PM high byte into program latch |

| ; | <pre>lst_program_v</pre> | word                        |     |                                         |

|   |                          | #LOW_WORD_1, W2             | ;   | ;                                       |

|   |                          | #HIGH_BYTE_1, W3            | ;   | ;                                       |

|   | TBLWTL                   | W2, [W0]                    | ;   | ; Write PM low word into program latch  |

|   | TBLWTH                   | W3, [W0++]                  | ;   | ; Write PM high byte into program latch |

| ; | 2nd_program              | —                           |     |                                         |

|   | MOV                      | #LOW_WORD_2, W2             | ;   | ;                                       |

|   | MOV                      | <pre>#HIGH_BYTE_2, W3</pre> | ;   | ;                                       |

|   |                          | W2, [W0]                    |     | ; Write PM low word into program latch  |

|   | TBLWTH                   | W3, [W0++]                  | ;   | ; Write PM high byte into program latch |

|   | •                        |                             |     |                                         |

|   | •                        |                             |     |                                         |

|   | •                        |                             |     |                                         |

| ; | 63rd_program             |                             |     |                                         |

|   |                          | #LOW_WORD_31, W2            | ;   | ;                                       |

|   |                          | #HIGH_BYTE_31, W3           | ;   | ;                                       |

|   |                          | W2, [W0]                    |     | ; Write PM low word into program latch  |

|   | TBLWTH                   | W3, [W0++]                  | ;   | ; Write PM high byte into program latch |

|   |                          |                             |     |                                         |

### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI |               | Block all interrupts with priority <7 |

|------|---------------|---------------------------------------|

|      | i             | for next 5 instructions               |

| MOV  | #0x55, W0     |                                       |

| MOV  | W0, NVMKEY ;  | Write the 55 key                      |

| MOV  | #0xAA, W1 ;   |                                       |

| MOV  | W1, NVMKEY ;  | Write the AA key                      |

| BSET | NVMCON, #WR ; | Start the erase sequence              |

| NOP  | ;             | Insert two NOPs after the             |

| NOP  | ;             | erase command is asserted             |

|      |               |                                       |

| REGISTER 7-2: C | ORCON: CORE CONTROL REGISTER <sup>(1)</sup> |

|-----------------|---------------------------------------------|

|-----------------|---------------------------------------------|

| U-0                | U-0 | U-0              | U-0   | U-0                                | U-0   | U-0 | U-0   |  |

|--------------------|-----|------------------|-------|------------------------------------|-------|-----|-------|--|

| —                  | _   | —                | _     | —                                  | —     | —   | —     |  |

| bit 15             |     |                  |       |                                    |       |     | bit 8 |  |

|                    |     |                  |       |                                    |       |     |       |  |

| U-0                | U-0 | U-0              | U-0   | R/C-0                              | R/W-0 | U-0 | U-0   |  |

| —                  | _   | —                | _     | IPL3 <sup>(2)</sup>                | PSV   | —   | —     |  |

| bit 7              |     |                  |       |                                    |       |     | bit 0 |  |

|                    |     |                  | 1.11  |                                    |       |     |       |  |

| Legend:            |     | C = Clear only   | / bit |                                    |       |     |       |  |

| R = Readable b     | bit | W = Writable     | bit   | -n = Value at                      |       |     |       |  |

| 0' = Bit is cleare | ed  | ʻx = Bit is unkr | nown  | U = Unimplemented bit, read as '0' |       |     |       |  |

bit 3 IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

1 = CPU interrupt priority level is greater than 7

0 = CPU interrupt priority level is 7 or less

Note 1: For complete register details, see Register 3-2: "CORCON: Core Control Register".

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| REGISTER     | 7-9: IECI:                                                                                                         | INTERRUPT                          |                  |                  | GISTERI         |                 |         |  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|------------------|-----------------|-----------------|---------|--|--|--|--|--|--|

| U-0          | U-0                                                                                                                | R/W-0                              | U-0              | U-0              | U-0             | U-0             | U-0     |  |  |  |  |  |  |

| _            | _                                                                                                                  | INT2IE                             | _                | —                | —               | —               | —       |  |  |  |  |  |  |

| bit 15       |                                                                                                                    |                                    |                  |                  |                 |                 | bit 8   |  |  |  |  |  |  |

|              |                                                                                                                    |                                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

| R/W-0        | R/W-0                                                                                                              | U-0                                | R/W-0            | R/W-0            | U-0             | R/W-0           | R/W-0   |  |  |  |  |  |  |

| IC8IE        | IC7IE                                                                                                              | —                                  | INT1IE           | CNIE             | —               | MI2C1IE         | SI2C1IE |  |  |  |  |  |  |

| bit 7        |                                                                                                                    |                                    |                  |                  |                 |                 | bit C   |  |  |  |  |  |  |

| Legend:      |                                                                                                                    |                                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

| R = Readab   | le bit                                                                                                             | W = Writable I                     | bit              | U = Unimpler     | mented bit, rea | d as '0'        |         |  |  |  |  |  |  |

| -n = Value a |                                                                                                                    | '1' = Bit is set                   | 5 N              | '0' = Bit is cle |                 | x = Bit is unkr | nown    |  |  |  |  |  |  |

|              |                                                                                                                    |                                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

| bit 15-14    | Unimplemen                                                                                                         | ted: Read as '0                    | כי               |                  |                 |                 |         |  |  |  |  |  |  |

| bit 13       | INT2IE: Exter                                                                                                      | nal Interrupt 2                    | Enable bit       |                  |                 |                 |         |  |  |  |  |  |  |

|              |                                                                                                                    | request enabled                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

|              | 0 = Interrupt r                                                                                                    | request not ena                    | bled             |                  |                 |                 |         |  |  |  |  |  |  |

| bit 12-8     | Unimplemen                                                                                                         | ted: Read as 'd                    | כ'               |                  |                 |                 |         |  |  |  |  |  |  |

| bit 7        | IC8IE: Input (                                                                                                     | Capture Channe                     | el 8 Interrupt I | Enable bit       |                 |                 |         |  |  |  |  |  |  |

|              |                                                                                                                    | request enabled<br>request not ena |                  |                  |                 |                 |         |  |  |  |  |  |  |

| bit 6        | <ul> <li>0 = Interrupt request not enabled</li> <li>IC7IE: Input Capture Channel 7 Interrupt Enable bit</li> </ul> |                                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

|              | -                                                                                                                  | request enabled                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                  | request not ena                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

| bit 5        | Unimplemen                                                                                                         | ted: Read as 'd                    | כי               |                  |                 |                 |         |  |  |  |  |  |  |

| bit 4        | INT1IE: Exter                                                                                                      | nal Interrupt 1                    | Enable bit       |                  |                 |                 |         |  |  |  |  |  |  |

|              |                                                                                                                    | request enabled                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

|              | •                                                                                                                  | request not ena                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

| bit 3        |                                                                                                                    | Change Notifica                    |                  | Enable bit       |                 |                 |         |  |  |  |  |  |  |

|              |                                                                                                                    | request enabled                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

| <b>h</b> # 0 | •                                                                                                                  | request not ena                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

| bit 2        | -                                                                                                                  | ted: Read as '(                    |                  | aabla bit        |                 |                 |         |  |  |  |  |  |  |

| bit 1        |                                                                                                                    | 1 Master Event                     | •                | Table bit        |                 |                 |         |  |  |  |  |  |  |

|              |                                                                                                                    | request enableo<br>request not ena |                  |                  |                 |                 |         |  |  |  |  |  |  |

| bit 0        | •                                                                                                                  | 1 Slave Events                     |                  | able bit         |                 |                 |         |  |  |  |  |  |  |

|              |                                                                                                                    |                                    |                  |                  |                 |                 |         |  |  |  |  |  |  |

|              | 1 = Interrupt r                                                                                                    | request enabled                    | d                |                  |                 |                 |         |  |  |  |  |  |  |

### REGISTER 7-9: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| U-0          | U-0            | U-0                 | U-0             | U-0                                | U-0  | U-0                | U-0   |  |

|--------------|----------------|---------------------|-----------------|------------------------------------|------|--------------------|-------|--|

|              | —              |                     | _               |                                    | _    |                    | _     |  |

| bit 15       |                |                     |                 |                                    |      | bit 8              |       |  |

|              |                |                     |                 |                                    |      |                    |       |  |

| U-0          | R/W-1          | R/W-0               | R/W-0           | U-0                                | U-0  | U-0                | U-0   |  |

| —            |                | INT2IP<2:0>         |                 |                                    | _    |                    | —     |  |

| bit 7        |                |                     |                 |                                    |      |                    | bit 0 |  |

|              |                |                     |                 |                                    |      |                    |       |  |

| Legend:      |                |                     |                 |                                    |      |                    |       |  |

| R = Readab   | le bit         | W = Writable I      | bit             | U = Unimplemented bit, read as '0' |      |                    |       |  |

| -n = Value a | t POR          | '1' = Bit is set    |                 | '0' = Bit is cle                   | ared | x = Bit is unknown |       |  |

|              |                |                     |                 |                                    |      |                    |       |  |

| bit 15-7     | Unimplemen     | ted: Read as 'o     | )'              |                                    |      |                    |       |  |

| bit 6-4      | INT2IP<2:0>:   | External Interr     | upt 2 Priority  | bits                               |      |                    |       |  |

|              | 111 = Interrup | ot is priority 7 (ł | nighest priorit | ty interrupt)                      |      |                    |       |  |

|              | •              |                     |                 |                                    |      |                    |       |  |

|              | •              |                     |                 |                                    |      |                    |       |  |

|              | •              | at ia muiamite d    |                 |                                    |      |                    |       |  |

|              | 001 = Interrup | ot is priority 1    | abled           |                                    |      |                    |       |  |

| bit 3-0      | -              | ted: Read as '(     |                 |                                    |      |                    |       |  |

|              |                | icu. I cau as (     |                 |                                    |      |                    |       |  |

### REGISTER 7-17: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

### 7.4 Interrupt Setup Procedures

### 7.4.1 INITIALIZATION

To configure an interrupt source at initialization:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits into the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources can be programmed to the same non-zero value.

Note: At a device Reset, the IPCx registers are initialized such that all user interrupt sources are assigned to priority level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

## 7.4.2 INTERRUPT SERVICE ROUTINE (ISR)

The method used to declare an Interrupt Service Routine (ISR) and initialize the IVT with the correct vector address depends on the programming language (C or Assembler) and the language development toolsuite used to develop the application.

In general, the user application must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the program will re-enter the ISR immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

### 7.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using this procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value OEh with SRL.

To enable user interrupts, the POP instruction can be used to restore the previous SR value.

| Note: | Only user interrupts with a priority level of |

|-------|-----------------------------------------------|

|       | 7 or lower can be disabled. Trap sources      |

|       | (level 8-level 15) cannot be disabled.        |

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

## 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the PIC24HJ12GP201/202 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 7. Oscillator" (DS70186) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

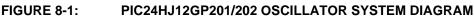

The PIC24HJ12GP201/202 oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- A Clock Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection.

A simplified diagram of the oscillator system is shown in Figure 8-1.

### 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the PIC24HJ12GP201/202 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 10. I/O Ports" (DS70193) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

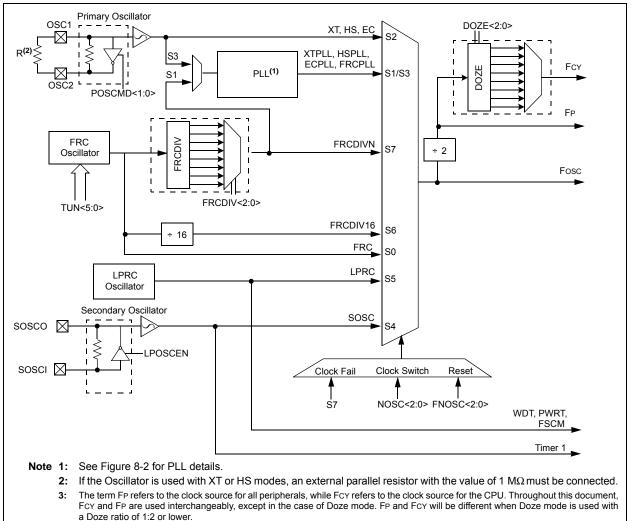

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

#### Parallel I/O (PIO) Ports 10.1

A parallel I/O port that shares a pin with a peripheral is generally subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in

which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch, write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. This means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

© 2007-2011 Microchip Technology Inc.

### REGISTER 10-8: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| U-0                               | U-0                               | U-0                               | R/W-1 | R/W-1            | R/W-1           | R/W-1          | R/W-1 |

|-----------------------------------|-----------------------------------|-----------------------------------|-------|------------------|-----------------|----------------|-------|

| —                                 | —                                 | _                                 |       |                  | SCK1R<4:0       | >              |       |

| bit 15                            |                                   |                                   |       |                  |                 |                | bit 8 |

|                                   |                                   |                                   |       |                  |                 |                |       |

| U-0                               | U-0                               | U-0                               | R/W-1 | R/W-1            | R/W-1           | R/W-1          | R/W-1 |

|                                   |                                   |                                   |       |                  | SDI1R<4:0       | >              |       |

| bit 7                             |                                   |                                   |       |                  |                 |                | bit ( |

|                                   |                                   |                                   |       |                  |                 |                |       |

| Legend:                           | - 6:4                             |                                   | L 11  |                  |                 |                |       |

| R = Readable bit W = Writable bit |                                   |                                   |       |                  | nented bit, rea |                |       |

| -n = Value at                     | POR                               | '1' = Bit is set                  |       | '0' = Bit is cle | ared            | x = Bit is unk | nown  |

|                                   | •<br>•<br>00001 = Inpu            |                                   |       |                  |                 |                |       |

| bit 7-5                           | 00000 = Inpu                      | it tied to RP0<br>ited: Read as ' | 0'    |                  |                 |                |       |

| bit 4-0                           | •                                 | Assign SPI1                       |       | 11) to the corre | sponding RPr    | nin hits       |       |

|                                   | 11111 <b>= I</b> npu              | -                                 |       |                  |                 |                |       |

|                                   | •                                 |                                   |       |                  |                 |                |       |

|                                   | •<br>00001 = Inpu<br>00000 = Inpu |                                   |       |                  |                 |                |       |

| R/W-0           | U-0                                                                                                                                                                                        | R/W-0                                                | R/W-1 HC                        | R/W-0            | R/W-0           | R/W-0             | R/W-0       |  |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|------------------|-----------------|-------------------|-------------|--|--|--|--|

| I2CEN           | _                                                                                                                                                                                          | I2CSIDL                                              | SCLREL                          | IPMIEN           | A10M            | DISSLW            | SMEN        |  |  |  |  |

| bit 15          |                                                                                                                                                                                            |                                                      |                                 |                  |                 |                   | bit 8       |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                                                                      | R/W-0                                                | R/W-0 HC                        | R/W-0 HC         | R/W-0 HC        | R/W-0 HC          | R/W-0 HC    |  |  |  |  |

| GCEN            | STREN                                                                                                                                                                                      | ACKDT                                                | ACKEN                           | RCEN             | PEN             | RSEN              | SEN         |  |  |  |  |

| bit 7           | onten                                                                                                                                                                                      | , long i                                             | , lonent                        | ROLI             |                 | noen              | bit 0       |  |  |  |  |

| Legend:         |                                                                                                                                                                                            | U = Unimpler                                         | nented bit, rea                 | d as '0'         |                 |                   |             |  |  |  |  |

| R = Readable    | bit                                                                                                                                                                                        | W = Writable                                         |                                 | HS = Set in h    | ardware         | HC = Cleared      | in hardware |  |  |  |  |

| -n = Value at F | POR                                                                                                                                                                                        | '1' = Bit is set                                     |                                 | '0' = Bit is cle |                 | x = Bit is unkr   |             |  |  |  |  |

| in value at i   | ÖN                                                                                                                                                                                         |                                                      |                                 | o Biclo dio      |                 |                   |             |  |  |  |  |

| bit 15          | <b>12CEN:</b> 12Cx                                                                                                                                                                         | Enable bit                                           |                                 |                  |                 |                   |             |  |  |  |  |

|                 |                                                                                                                                                                                            |                                                      |                                 |                  |                 | as serial port pi | าร          |  |  |  |  |

|                 |                                                                                                                                                                                            |                                                      |                                 | are controlled   | by port functio | ns                |             |  |  |  |  |

| bit 14          | Unimplemen                                                                                                                                                                                 | ted: Read as '                                       | 0'                              |                  |                 |                   |             |  |  |  |  |

| bit 13          |                                                                                                                                                                                            | p in Idle Mode                                       |                                 |                  |                 |                   |             |  |  |  |  |

|                 |                                                                                                                                                                                            |                                                      | eration when de                 |                  | n Idle mode     |                   |             |  |  |  |  |

| bit 12          | SCLREL: SCLx Release Control bit (when operating as I <sup>2</sup> C slave)                                                                                                                |                                                      |                                 |                  |                 |                   |             |  |  |  |  |

|                 | 1 = Release SCLx clock<br>0 = Hold SCLx clock low (clock stretch)                                                                                                                          |                                                      |                                 |                  |                 |                   |             |  |  |  |  |

|                 | If STREN = 1:                                                                                                                                                                              |                                                      |                                 |                  |                 |                   |             |  |  |  |  |

|                 | Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception. |                                                      |                                 |                  |                 |                   |             |  |  |  |  |

|                 | If STREN = 0                                                                                                                                                                               | :                                                    |                                 |                  |                 |                   |             |  |  |  |  |

|                 | Bit is R/S (i.e. transmission.                                                                                                                                                             |                                                      | only write '1' t                | o release cloc   | k). Hardware cl | ear at beginnin   | g of slave  |  |  |  |  |

| bit 11          |                                                                                                                                                                                            | le is enabled; a                                     | al Managemer<br>all addresses A | •                | MI) Enable bit  |                   |             |  |  |  |  |

| bit 10          | A10M: 10-bit Slave Address bit                                                                                                                                                             |                                                      |                                 |                  |                 |                   |             |  |  |  |  |

|                 |                                                                                                                                                                                            | is a 10-bit slav<br>is a 7-bit slave                 |                                 |                  |                 |                   |             |  |  |  |  |

| bit 9           | DISSLW: Disa                                                                                                                                                                               | able Slew Rate                                       | e Control bit                   |                  |                 |                   |             |  |  |  |  |

|                 |                                                                                                                                                                                            | control disable                                      |                                 |                  |                 |                   |             |  |  |  |  |

| bit 8           | SMEN: SMBL                                                                                                                                                                                 | us Input Levels                                      | bit                             |                  |                 |                   |             |  |  |  |  |

|                 |                                                                                                                                                                                            | O pin threshold<br>MBus input the                    | ls compliant wi<br>resholds     | ith SMBus spe    | cification      |                   |             |  |  |  |  |

| bit 7           | <b>GCEN:</b> General Call Enable bit (when operating as I <sup>2</sup> C slave)                                                                                                            |                                                      |                                 |                  |                 |                   |             |  |  |  |  |

|                 | (module i                                                                                                                                                                                  | nterrupt when a<br>is enabled for<br>call address di | reception)                      | iddress is rece  | ived in the I2C | xRSR              |             |  |  |  |  |

| hit 6           |                                                                                                                                                                                            |                                                      |                                 | hon onoration    | $a_{12}$        |                   |             |  |  |  |  |

| bit 6           |                                                                                                                                                                                            | x Clock Stretcr                                      | n Enable bit (w<br>LREL bit.    | nen operating    | as i⁻u siave)   |                   |             |  |  |  |  |

### REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0         | U-0                            | U-0                                                   | R/W-0                  | R/W-0                  | R/W-0           | R/W-0           | R/W-0  |

|---------------|--------------------------------|-------------------------------------------------------|------------------------|------------------------|-----------------|-----------------|--------|

| ADRC          |                                |                                                       |                        |                        | SAMC<4:0>(      | 1)              |        |

| bit 15        |                                |                                                       |                        |                        |                 |                 | bit    |

| U-0           | U-0                            | R/W-0                                                 | R/W-0                  | R/W-0                  | R/W-0           | R/W-0           | R/W-0  |

| 0-0           | 0-0                            | N/VV-0                                                | ADCS<                  | -                      | N/W-U           | FV/VV-0         | N/ W-U |

| bit 7         |                                |                                                       | 7.200                  |                        |                 |                 | bit    |

| Legend:       |                                |                                                       |                        |                        |                 |                 |        |

| R = Readable  | e bit                          | W = Writable bi                                       | t                      | U = Unimpler           | nented bit, rea | ad as '0'       |        |

| -n = Value at |                                | '1' = Bit is set                                      | •                      | '0' = Bit is cle       |                 | x = Bit is unkr | nown   |

|               |                                |                                                       |                        |                        |                 |                 | -      |

| bit 15        | 1 = ADC inte                   | Conversion Cloc<br>rnal RC clock<br>rived from system |                        |                        |                 |                 |        |

| bit 14-13     |                                | ted: Read as '0'                                      |                        |                        |                 |                 |        |

| bit 12-8      | SAMC<4:0>                      | Auto Sample Tir                                       | ne bits <sup>(1)</sup> |                        |                 |                 |        |

|               | 11111 <b>= 31</b> <sup>-</sup> | TAD                                                   |                        |                        |                 |                 |        |

|               | •                              |                                                       |                        |                        |                 |                 |        |

|               | •                              |                                                       |                        |                        |                 |                 |        |

|               | 00001 = 1 TA<br>00000 = 0 TA   |                                                       |                        |                        |                 |                 |        |

| bit 7-0       | ADCS<7:0>:                     | ADC Conversion                                        | n Clock Seled          | ct bits <sup>(2)</sup> |                 |                 |        |

|               | 11111111 =                     | Reserved                                              |                        |                        |                 |                 |        |

|               | •                              |                                                       |                        |                        |                 |                 |        |

|               | •                              |                                                       |                        |                        |                 |                 |        |

|               | •                              |                                                       |                        |                        |                 |                 |        |

|               | •                              | <b>_</b>                                              |                        |                        |                 |                 |        |

|               | 01000000 =                     | TCY · (ADCS<7:                                        | 0> + 1) = 64           | . Toy = Tad            |                 |                 |        |

|               | •                              |                                                       | 0, 1) – 04             |                        |                 |                 |        |

|               | •                              |                                                       |                        |                        |                 |                 |        |

|               | •                              |                                                       |                        |                        |                 |                 |        |

|               | 00000010 =                     | TCY · (ADCS<7:                                        | 0> + 1) = 3 ·          | Tcy = Tad              |                 |                 |        |

|               | 00000001 =                     | TCY · (ADCS<7:                                        | 0> + 1) = 2 ·          | TCY = TAD              |                 |                 |        |

|               | 00000000 =                     |                                                       |                        |                        |                 |                 |        |

### REGISTER 18-3: AD1CON3: ADC1 CONTROL REGISTER 3

- **Note 1:** These bits are used only if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- 2: These bits are not used if the ADRC bit (AD1CON3<15>) = 1.

| REGISTER      |                                                                                                                                                | 150: ADCT IN                                                |                                                                         |                  |                 |                 |       |  |  |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|--|--|

| R/W-0         | U-0                                                                                                                                            | U-0                                                         | R/W-0                                                                   | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |  |  |

| CHONB         |                                                                                                                                                | —                                                           |                                                                         |                  | CH0SB<4:0>      |                 |       |  |  |  |  |  |  |  |

| bit 15        |                                                                                                                                                |                                                             |                                                                         |                  |                 |                 | bit   |  |  |  |  |  |  |  |

| R/W-0         | U-0                                                                                                                                            | U-0                                                         | R/W-0                                                                   | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |  |  |

| CH0NA         | —                                                                                                                                              | —                                                           |                                                                         |                  | CH0SA<4:0>      |                 |       |  |  |  |  |  |  |  |

| bit 7         |                                                                                                                                                |                                                             |                                                                         |                  |                 |                 | bit   |  |  |  |  |  |  |  |

| Legend:       |                                                                                                                                                |                                                             |                                                                         |                  |                 |                 |       |  |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                                          | W = Writable b                                              | it                                                                      | U = Unimpler     | mented bit, rea | d as '0'        |       |  |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                            | '1' = Bit is set                                            |                                                                         | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |  |  |  |  |

|               |                                                                                                                                                |                                                             |                                                                         |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 1 = Channel (<br>0 = Channel (                                                                                                                 | nnel 0 Negative<br>) negative input<br>) negative input     | is AN1<br>is VREF-                                                      |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 14-13     | Unimplemen                                                                                                                                     | ted: Read as '0                                             | 3                                                                       |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 12-8      | CH0SB<4:0>: Channel 0 Positive Input Select for Sample B bits                                                                                  |                                                             |                                                                         |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 00111 = Cha<br>00110 = Cha<br>00101 = Res<br>00100 = Res<br>00011 = Cha<br>00010 = Cha<br>00001 = Cha                                          |                                                             | nput is AN7<br>nput is AN6<br>nput is AN3<br>nput is AN2<br>nput is AN1 |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | PIC24HJ12GP202 devices only:<br>01001 = Channel 0 positive input is AN9                                                                        |                                                             |                                                                         |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | •                                                                                                                                              |                                                             |                                                                         |                  |                 |                 |       |  |  |  |  |  |  |  |

|               | 00001 <b>= Cha</b>                                                                                                                             | nnel 0 positive i<br>nnel 0 positive i<br>nnel 0 positive i | nput is AN1                                                             |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 7         | <b>CHONA:</b> Channel 0 Negative Input Select for Sample A bit<br>1 = Channel 0 negative input is AN1<br>0 = Channel 0 negative input is VREF- |                                                             |                                                                         |                  |                 |                 |       |  |  |  |  |  |  |  |

| bit 6-5       |                                                                                                                                                | ted: Read as '0                                             |                                                                         |                  |                 |                 |       |  |  |  |  |  |  |  |

|               |                                                                                                                                                |                                                             |                                                                         |                  |                 |                 |       |  |  |  |  |  |  |  |

### REGISTER 18-5: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

| IADE               | L 20-2.              |        |             |                              |               |                |                          |  |  |  |  |  |

|--------------------|----------------------|--------|-------------|------------------------------|---------------|----------------|--------------------------|--|--|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |        |             | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |  |  |  |  |

| 66                 | TBLRDL               | TBLRDL | Ws,Wd       | Read Prog<15:0> to Wd        | 1             | 2              | None                     |  |  |  |  |  |

| 67                 | TBLWTH               | TBLWTH | Ws,Wd       | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |  |  |  |  |  |

| 68                 | TBLWTL               | TBLWTL | Ws,Wd       | Write Ws to Prog<15:0>       | 1             | 2              | None                     |  |  |  |  |  |

| 69                 | ULNK                 | ULNK   |             | Unlink Frame Pointer         | 1             | 1              | None                     |  |  |  |  |  |

| 70                 | XOR                  | XOR    | f           | f = f .XOR. WREG             | 1             | 1              | N,Z                      |  |  |  |  |  |

|                    |                      | XOR    | f,WREG      | WREG = f .XOR. WREG          | 1             | 1              | N,Z                      |  |  |  |  |  |