Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 12KB (4K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

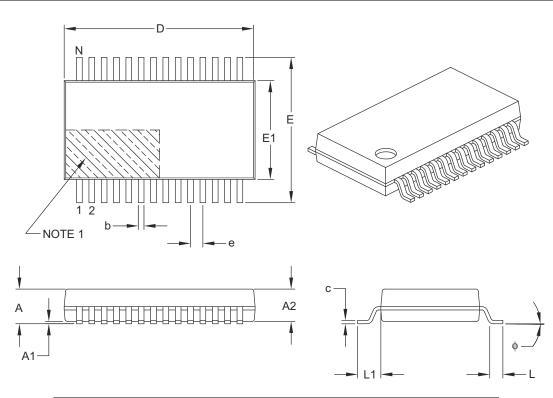

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-VQFN Exposed Pad                                                            |

| Supplier Device Package    | 28-QFN (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj12gp202t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC24HJ12GP201/202 Product Families

The device names, pin counts, memory sizes and peripheral availability of each family are listed below, followed by their pinout diagrams.

|                |      | ory                             |             |                 | Re               | mappa         | ble Pe                     | ripher | als                                |     |                   |       |                |                              |

|----------------|------|---------------------------------|-------------|-----------------|------------------|---------------|----------------------------|--------|------------------------------------|-----|-------------------|-------|----------------|------------------------------|

| Device         | Pins | Program Flash Memory<br>(Kbyte) | RAM (Kbyte) | Remappable Pins | 16-bit Timer     | Input Capture | Output Compare<br>Std. PWM | UART   | External Interrupts <sup>(2)</sup> | IdS | 10-Bit/12-Bit ADC | Ι²Οτω | I/O Pins (Max) | Packages                     |

| PIC24HJ12GP201 | 18   | 12                              | 1           | 8               | 3(1)             | 4             | 2                          | 1      | 3                                  | 1   | 1 ADC, 6 ch       | 1     | 13             | PDIP<br>SOIC                 |

| PIC24HJ12GP202 | 28   | 12                              | 1           | 16              | 3 <sup>(1)</sup> | 4             | 2                          | 1      | 3                                  | 1   | 1 ADC, 10 ch      | 1     | 21             | SPDIP<br>SOIC<br>SSOP<br>QFN |

## TABLE 1: PIC24HJ12GP201/202 CONTROLLER FAMILIES

**Note 1:** Only two out of three timers are remappable.

**2:** Only two out of three interrupts are remappable.

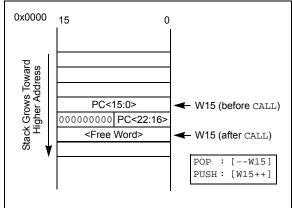

## 4.2.5 SOFTWARE STACK

In addition to its use as a working register, the W15 register in the PIC24HJ12GP201/202 devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-4. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | concatenates the SRL register to the MSB |

|       | of the PC prior to the push.             |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned.

When an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. However, the stack error trap will occur on a subsequent push operation. For example, to cause a stack error trap when the stack grows beyond address 0x0C00 in RAM, initialize the SPLIM with the value 0x0BFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the SFR space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### FIGURE 4-4: CALL STACK FRAME

## 4.2.6 DATA RAM PROTECTION FEATURE

The PIC24H product family supports Data RAM protection features that enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code, when it is enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code, when it is enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

## 4.3 Instruction Addressing Modes

The addressing modes shown in Table 4-22 form the basis of the addressing modes that are optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those provided by other instruction types.

### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

## 4.3.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 < function > Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be register direct), which is referred to as Wb. Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

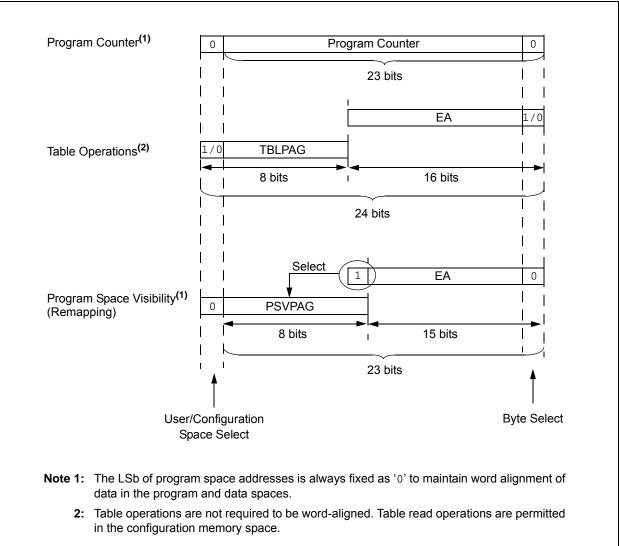

## FIGURE 4-5: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

|                                                                    | R/W-0                                                                                                                            | U-0                                         | U-0           | U-0                          | U-0              | R/W-0           | R/W-0        |  |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------|------------------------------|------------------|-----------------|--------------|--|

| TRAPR                                                              | IOPUWR                                                                                                                           |                                             |               |                              |                  | СМ              | VREGS        |  |

| bit 15                                                             | •                                                                                                                                |                                             |               | ·                            |                  |                 | bit          |  |

| 5.444                                                              | <b>D</b> # 4 4 A                                                                                                                 | 5444.0                                      | 5444.0        |                              | 5444.6           | <b>-</b>        |              |  |

| R/W-0                                                              | R/W-0                                                                                                                            | R/W-0                                       | R/W-0         | R/W-0                        | R/W-0            | R/W-1           | R/W-1        |  |

| EXTR                                                               | SWR SWDTEN <sup>(2)</sup> WDTO SLEEP IDLE BOR PO                                                                                 |                                             |               |                              |                  |                 |              |  |

| bit 7                                                              |                                                                                                                                  |                                             |               |                              |                  |                 | bit          |  |

| Legend:                                                            |                                                                                                                                  |                                             |               |                              |                  |                 |              |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                                                                                                                  |                                             |               |                              |                  |                 |              |  |

| -n = Value at F                                                    | POR                                                                                                                              | '1' = Bit is set                            |               | '0' = Bit is cle             | ared             | x = Bit is unki | nown         |  |

| bit 15                                                             | TRAPR. Tran                                                                                                                      | Reset Flag bit                              |               |                              |                  |                 |              |  |

|                                                                    |                                                                                                                                  | onflict Reset ha                            |               |                              |                  |                 |              |  |

|                                                                    |                                                                                                                                  | onflict Reset ha                            |               | d                            |                  |                 |              |  |

| bit 14                                                             | IOPUWR: Ille                                                                                                                     | egal Opcode or                              | Uninitialized | W Access Rese                | et Flag bit      |                 |              |  |

|                                                                    |                                                                                                                                  | al opcode dete                              |               | gal address mo               | ode or uninitial | ized W registe  | er used as a |  |

|                                                                    | ,                                                                                                                                | Pointer caused                              |               | locat has not a              | oourrod          |                 |              |  |

| bit 13-10                                                          | -                                                                                                                                | I opcode or unin<br><b>ited:</b> Read as '0 |               | leset has not o              | ccurreu          |                 |              |  |

|                                                                    | -                                                                                                                                |                                             |               |                              |                  |                 |              |  |

| bit 9                                                              |                                                                                                                                  | ration Mismatch                             |               | occurred                     |                  |                 |              |  |

|                                                                    | <ul> <li>1 = A configuration mismatch Reset has occurred</li> <li>0 = A configuration mismatch Reset has not occurred</li> </ul> |                                             |               |                              |                  |                 |              |  |

| bit 8                                                              | VREGS: Volta                                                                                                                     | age Regulator S                             | Standby Durir | ng Sleep bit                 |                  |                 |              |  |

|                                                                    |                                                                                                                                  | egulator is activ                           |               |                              |                  |                 |              |  |

| =                                                                  | -                                                                                                                                | regulator goes i                            |               | node during Sl               | еер              |                 |              |  |

| bit 7                                                              |                                                                                                                                  | nal Reset (MCL                              | ,             | no d                         |                  |                 |              |  |

|                                                                    |                                                                                                                                  | Clear (pin) Res<br>Clear (pin) Res          |               |                              |                  |                 |              |  |

| bit 6                                                              |                                                                                                                                  | are Reset (Instru                           |               |                              |                  |                 |              |  |

|                                                                    |                                                                                                                                  | instruction has                             |               |                              |                  |                 |              |  |

|                                                                    | 0 = A  RESET instruction has not been executed                                                                                   |                                             |               |                              |                  |                 |              |  |

| bit 5                                                              | SWDTEN: So                                                                                                                       | oftware Enable/                             | Disable of W  | DT bit <b><sup>(2)</sup></b> |                  |                 |              |  |

|                                                                    | 1 = WDT is e                                                                                                                     |                                             |               |                              |                  |                 |              |  |

| L:1 4                                                              | 0 = WDT is d                                                                                                                     |                                             |               | 1                            |                  |                 |              |  |

| bit 4                                                              |                                                                                                                                  | hdog Timer Tim<br>e-out has occur           | -             | t                            |                  |                 |              |  |

|                                                                    |                                                                                                                                  | e-out has occur                             |               |                              |                  |                 |              |  |

| bit 3                                                              | SLEEP: Wak                                                                                                                       | e-up from Sleep                             | Flag bit      |                              |                  |                 |              |  |

|                                                                    |                                                                                                                                  | as been in Slee                             |               |                              |                  |                 |              |  |

|                                                                    |                                                                                                                                  | as not been in S                            |               |                              |                  |                 |              |  |

| bit 2                                                              |                                                                                                                                  | up from Idle Fla                            | g bit         |                              |                  |                 |              |  |

|                                                                    | 1 = Device wa                                                                                                                    |                                             |               |                              |                  |                 |              |  |

## REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

cause a device Reset. 2: If the EWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the

2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| FIGURE 7-1: | PIC24HJ12GP201/202 INTERRUPT VECTOR TABLE |

|-------------|-------------------------------------------|

|             |                                           |

| I                                 |                                                          | 7                 |                                                        |

|-----------------------------------|----------------------------------------------------------|-------------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction                                 | 0x000000          |                                                        |

|                                   | Reset – GOTO Address                                     | 0x000002          |                                                        |

|                                   | Reserved                                                 | 0x000004          |                                                        |

|                                   | Oscillator Fail Trap Vector                              |                   |                                                        |

|                                   | Address Error Trap Vector                                |                   |                                                        |

|                                   | Stack Error Trap Vector                                  |                   |                                                        |

|                                   | Math Error Trap Vector                                   |                   |                                                        |

|                                   | Reserved                                                 |                   |                                                        |

|                                   | Reserved                                                 |                   |                                                        |

|                                   | Reserved                                                 |                   |                                                        |

|                                   | Interrupt Vector 0                                       | 0x000014          |                                                        |

|                                   | Interrupt Vector 1                                       |                   |                                                        |

|                                   | ~                                                        |                   |                                                        |

|                                   | ~                                                        |                   |                                                        |

|                                   | ~                                                        |                   |                                                        |

|                                   | Interrupt Vector 52                                      | 0x00007C          | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

|                                   | Interrupt Vector 53                                      | 0x00007E          |                                                        |

| Drity                             | Interrupt Vector 54                                      | 0x000080          |                                                        |

| Pric                              | ~                                                        |                   |                                                        |

| er H                              | ~                                                        | _                 |                                                        |

| Drd                               | ~                                                        | 0.000050          |                                                        |

|                                   | Interrupt Vector 116                                     | 0x0000FC          |                                                        |

| tura                              | Interrupt Vector 117                                     | 0x0000FE          |                                                        |

| Nat                               | Reserved                                                 | 0x000100          |                                                        |

| Decreasing Natural Order Priority | Reserved                                                 | 0x000102          | 1                                                      |

| asir                              | Reserved                                                 | _                 |                                                        |

| Cre                               | Oscillator Fail Trap Vector<br>Address Error Trap Vector | -                 |                                                        |

| )ec                               | Stack Error Trap Vector                                  | -                 |                                                        |

|                                   | Math Error Trap Vector                                   | -                 |                                                        |

|                                   | Reserved                                                 |                   |                                                        |

|                                   | Reserved                                                 | -                 |                                                        |

|                                   | Reserved                                                 | -                 |                                                        |

|                                   | Interrupt Vector 0                                       | 0x000114          |                                                        |

|                                   | Interrupt Vector 1                                       |                   |                                                        |

|                                   | ~                                                        |                   |                                                        |

|                                   | ~                                                        |                   |                                                        |

|                                   | ~                                                        |                   | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52                                      | 0x00017C          | ,                                                      |

|                                   | Interrupt Vector 53                                      | 0x00017E          |                                                        |

|                                   | Interrupt Vector 54                                      | 0x000180          |                                                        |

|                                   | ~                                                        |                   |                                                        |

|                                   | ~                                                        |                   |                                                        |

|                                   | ~                                                        |                   |                                                        |

|                                   | Interrupt Vector 116                                     |                   |                                                        |

| 4                                 | Interrupt Vector 117                                     | 0x0001FE          |                                                        |

| <b>V</b>                          | Start of Code                                            | 0x000200          |                                                        |

| Note 1: See                       | e Table 7-1 for the list of impleme                      | ented interrupt v | vectors.                                               |

## REGISTER 7-16: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

|                                              | R/W-1                                                                 | R/W-0                                                               | R/W-0                 | U-0               | R/W-1     | R/W-0            | R/W-0 |  |  |  |  |

|----------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------|-------------------|-----------|------------------|-------|--|--|--|--|

|                                              |                                                                       | IC8IP<2:0>                                                          |                       | —                 |           | IC7IP<2:0>       |       |  |  |  |  |

| bit 15                                       |                                                                       |                                                                     |                       |                   |           |                  | bit   |  |  |  |  |

| U-0                                          | U-0                                                                   | U-0                                                                 | U-0                   | U-0               | R/W-1     | R/W-0            | R/W-0 |  |  |  |  |

| _                                            | _                                                                     | _                                                                   | _                     | _                 |           | INT1IP<2:0>      |       |  |  |  |  |

| bit 7                                        |                                                                       |                                                                     | bit                   |                   |           |                  |       |  |  |  |  |

| l agend:                                     |                                                                       |                                                                     |                       |                   |           |                  |       |  |  |  |  |

| Legend:<br>R = Readable bit W = Writable bit |                                                                       |                                                                     | U = Unimplen          | nented hit re     | n, as ,0, |                  |       |  |  |  |  |

| -n = Value at                                |                                                                       | '1' = Bit is set                                                    |                       | '0' = Bit is cle  |           | x = Bit is unkno | -w/n  |  |  |  |  |

|                                              |                                                                       |                                                                     |                       |                   | urcu      |                  | 00011 |  |  |  |  |

| bit 15                                       | Unimplemer                                                            | nted: Read as '                                                     | 0'                    |                   |           |                  |       |  |  |  |  |

| bit 14-12                                    | IC8IP<2:0>:                                                           | Input Capture                                                       | Channel 8 Inte        | rrupt Priority bi | ts        |                  |       |  |  |  |  |

|                                              |                                                                       | pt is priority 7 (                                                  |                       |                   |           |                  |       |  |  |  |  |

|                                              | •                                                                     |                                                                     | <b>3</b>              | ,                 |           |                  |       |  |  |  |  |

|                                              | •                                                                     |                                                                     |                       |                   |           |                  |       |  |  |  |  |

|                                              | •                                                                     | •                                                                   |                       |                   |           |                  |       |  |  |  |  |

|                                              | 001 = Interru                                                         | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |                       |                   |           |                  |       |  |  |  |  |

| bit 11                                       |                                                                       | nted: Read as '                                                     |                       |                   |           |                  |       |  |  |  |  |

|                                              | -                                                                     |                                                                     |                       |                   |           |                  |       |  |  |  |  |

| bit 10-8                                     |                                                                       | Input Capture                                                       |                       |                   | ts        |                  |       |  |  |  |  |

|                                              | 111 = Interru                                                         | pt is priority 7 (                                                  | nignest priorit       | y interrupt)      |           |                  |       |  |  |  |  |

|                                              | •                                                                     |                                                                     |                       |                   |           |                  |       |  |  |  |  |

|                                              |                                                                       |                                                                     |                       |                   |           |                  |       |  |  |  |  |

|                                              | •                                                                     |                                                                     |                       |                   |           |                  |       |  |  |  |  |

|                                              |                                                                       | pt is priority 1                                                    |                       |                   |           |                  |       |  |  |  |  |

|                                              |                                                                       | ipt is priority 1<br>ipt source is dis                              | sabled                |                   |           |                  |       |  |  |  |  |

| bit 7-3                                      | 000 = Interru                                                         |                                                                     |                       |                   |           |                  |       |  |  |  |  |

|                                              | 000 = Interru<br>Unimplemer                                           | pt source is dis                                                    | 0'                    | bits              |           |                  |       |  |  |  |  |

|                                              | 000 = Interru<br>Unimplemer<br>INT1IP<2:0>                            | ipt source is dis<br>nted: Read as '                                | 0'<br>rupt 1 Priority |                   |           |                  |       |  |  |  |  |

|                                              | 000 = Interru<br>Unimplemer<br>INT1IP<2:0>                            | ipt source is dis<br>nted: Read as '<br>: External Inter            | 0'<br>rupt 1 Priority |                   |           |                  |       |  |  |  |  |

| bit 7-3<br>bit 2-0                           | 000 = Interru<br>Unimplemer<br>INT1IP<2:0>                            | ipt source is dis<br>nted: Read as '<br>: External Inter            | 0'<br>rupt 1 Priority |                   |           |                  |       |  |  |  |  |

|                                              | 000 = Interru<br>Unimplemen<br>INT1IP<2:0><br>111 = Interru<br>•<br>• | ipt source is dis<br>nted: Read as '<br>: External Inter            | 0'<br>rupt 1 Priority |                   |           |                  |       |  |  |  |  |

NOTES:

| REGISTER 15-2: SPIxCON1: SPIx CONTROL REGISTER |

|------------------------------------------------|

|------------------------------------------------|

| U-0                                                                         | U-0                                                                    | U-0                                                                 | R/W-0                               | R/W-0              | R/W-0                                   | R/W-0         | R/W-0              |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------|--------------------|-----------------------------------------|---------------|--------------------|

| _                                                                           | _                                                                      | _                                                                   | DISSCK                              | DISSDO             | MODE16                                  | SMP           | CKE <sup>(1)</sup> |

| bit 15                                                                      |                                                                        |                                                                     |                                     |                    |                                         |               | bit                |

| R/W-0                                                                       | 0 R/W-0                                                                | R/W-0                                                               | R/W-0                               | R/W-0              | R/W-0                                   | R/W-0         | R/W-0              |

| SSEN                                                                        | <sup>(2)</sup> CKP                                                     | MSTEN SPRE<2:0> <sup>(3)</sup> PPR                                  |                                     |                    |                                         |               |                    |

| bit 7                                                                       |                                                                        |                                                                     |                                     |                    |                                         | 1             | bit                |

| Legend:                                                                     |                                                                        |                                                                     |                                     |                    |                                         |               |                    |

| R = Read                                                                    | able bit                                                               | W = Writable                                                        | bit                                 | U = Unimpler       | mented bit, read                        | l as '0'      |                    |

| -n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown) |                                                                        |                                                                     |                                     |                    |                                         |               |                    |

| bit 15-13                                                                   | Unimplemen                                                             | ted: Read as '                                                      | 0'                                  |                    |                                         |               |                    |

| bit 12                                                                      | 1 = Internal S                                                         | able SCKx pin<br>PI clock is disa<br>PI clock is ena                | abled, pin func                     |                    |                                         |               |                    |

| bit 11                                                                      | 1 = SDOx pin                                                           | able SDOx pin<br>is not used by<br>is controlled b                  | v module; pin f                     | unctions as I/C    | )                                       |               |                    |

| bit 10                                                                      | 1 = Communi                                                            | ord/Byte Comm<br>ication is word-<br>ication is byte-               | wide (16 bits)                      | ect bit            |                                         |               |                    |

| bit 9                                                                       | Master mode:<br>1 = Input data<br>0 = Input data<br><u>Slave mode:</u> | ata Input Samp<br>a sampled at en<br>a sampled at m<br>cleared when | nd of data outr<br>iiddle of data c | output time        |                                         |               |                    |

| bit 8                                                                       | 1 = Serial out                                                         |                                                                     | ges on transitio                    |                    | clock state to Id<br>ock state to activ |               |                    |

| bit 7                                                                       | <b>SSEN:</b> Slave<br>1 = <u>SSx</u> pin u                             | Select Enable<br>sed for Slave i<br>ot used by mo                   | bit (Slave mo<br>mode               | de) <sup>(2)</sup> |                                         |               | ·                  |

| bit 6                                                                       | 1 = Idle state                                                         | Polarity Select I<br>for clock is a h<br>for clock is a lo          | igh level; activ                    |                    |                                         |               |                    |

| oit 5                                                                       |                                                                        | ter Mode Enat<br>ode                                                |                                     | C                  |                                         |               |                    |

| Note 1:                                                                     | The CKE bit is not<br>(FRMEN = 1).                                     | used in the Fr                                                      | amed SPI mod                        | des. Program t     | his bit to '0' for                      | the Framed SP | 'l modes           |

| 2:                                                                          | This bit must be cl                                                    |                                                                     |                                     |                    |                                         |               |                    |

| 3.                                                                          | Do not set both Pr                                                     | imary and Sec                                                       | ondary presca                       | lers to a value    | of 1.1                                  |               |                    |

**3:** Do not set both Primary and Secondary prescalers to a value of 1:1.

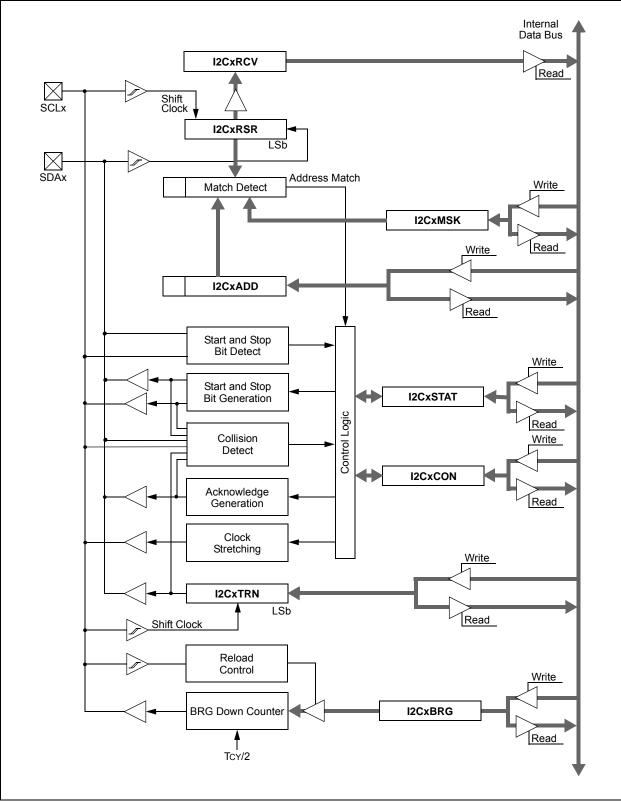

## 16.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the PIC24HJ12GP201/202 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 19. Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

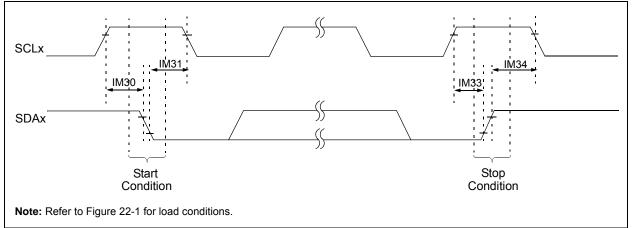

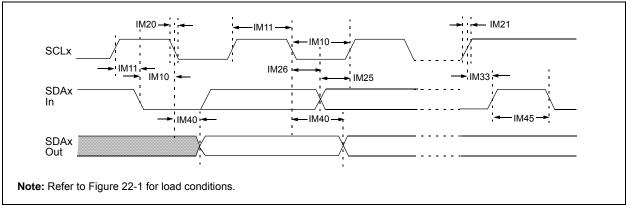

The Inter-Integrated Circuit <sup>TM</sup> (I<sup>2</sup>C<sup>TM</sup>) module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard, with a 16-bit interface.

The I<sup>2</sup>C module has a 2-pin interface:

- The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addresses

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addresses

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

## 16.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7-bit and 10-bit addressing.

The  $l^2C$  module can operate either as a slave or a master on an  $l^2C$  bus.

The following types of  $I^2C$  operation are supported:

- I<sup>2</sup>C slave operation with 7-bit address

- I<sup>2</sup>C slave operation with 10-bit address

- I<sup>2</sup>C master operation with 7-bit or 10-bit address

For details about the communication sequence in each of these modes, refer to the Microchip web site (www.microchip.com) for the latest *"dsPIC33F/PIC24H Family Reference Manual"* sections.

## 16.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

- · I2CxRSR is the shift register used for shifting data

- I2CxRCV is the receive buffer and the register to which data bytes are written, or from which data bytes are read

- I2CxTRN is the transmit register to which bytes are written during a transmit operation

- · I2CxADD register holds the slave address

- · ADD10 status bit indicates 10-bit Address mode

- I2CxBRG acts as the Baud Rate Generator (BRG) reload value

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV, and an interrupt pulse is generated.

### REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <ul> <li>BRGH: High Baud Rate Enable bit</li> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                       |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                               |

- **Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

## REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect.</li> <li>0 = Address Detect mode disabled</li> </ul>                                                                        |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                            |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                           |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                       |

|       | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>                                                        |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                      |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                        |

|       | 0 = Framing error has not been detected                                                                                                                                                                                         |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read-only/clear-only)                                                                                                                                                            |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 →0 transition) will reset<br/>the receiver buffer and the UxRSR to the empty state.</li> </ul> |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                            |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                   |

**Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

| TABLE 19-2: | PICZ4HJ1Z |                                                                                                                 | 2 CONFIGURATION BITS DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Field   | Register  | RTSP<br>Effect                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                         |

| BWRP        | FBS       | Immediate                                                                                                       | Boot Segment Program Flash Write Protection<br>1 = Boot segment may be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                               |

| BSS<2:0>    | FBS       | Immediate                                                                                                       | Boot Segment Program Flash Code Protection Size<br>x11 = No Boot program Flash segment                                                                                                                                                                                                                                                                                                              |

|             |           |                                                                                                                 | Boot space is 256 Instruction Words (except interrupt vectors)<br>110 = Standard security; boot program Flash segment ends at 0x0003FE<br>010 = High security; boot program Flash segment ends at 0x0003FE                                                                                                                                                                                          |

|             |           |                                                                                                                 | Boot space is 768 Instruction Words (except interrupt vectors)<br>101 = Standard security; boot program Flash segment, ends at 0x0007FE<br>001 = High security; boot program Flash segment ends at 0x0007FE                                                                                                                                                                                         |

|             |           |                                                                                                                 | Boot space is 1792 Instruction Words (except interrupt vectors)<br>100 = Standard security; boot program Flash segment ends at 0x000FFE<br>000 = High security; boot program Flash segment ends at 0x000FFE                                                                                                                                                                                         |

| GSS<1:0>    | FGS       | Immediate                                                                                                       | General Segment Code-Protect bit<br>11 = User program memory is not code-protected<br>10 = Standard security<br>0x = High security                                                                                                                                                                                                                                                                  |

| GWRP        | FGS       | Immediate                                                                                                       | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                   |

| IESO        | FOSCSEL   | Immediate                                                                                                       | <ul> <li>Two-speed Oscillator Start-up Enable bit</li> <li>1 = Start-up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start-up device with user-selected oscillator source</li> </ul>                                                                                                                                                   |

| FNOSC<2:0>  | FOSCSEL   | If clock<br>switch is<br>enabled,<br>RTSP<br>effect is<br>on any<br>device<br>Reset;<br>otherwise,<br>Immediate | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) oscillator with postscaler<br>110 = Internal Fast RC (FRC) oscillator with divide-by-16<br>101 = LPRC oscillator<br>100 = Secondary (LP) oscillator<br>011 = Primary (XT, HS, EC) oscillator with PLL<br>010 = Primary (XT, HS, EC) oscillator<br>001 = Internal Fast RC (FRC) oscillator with PLL<br>000 = FRC oscillator |

| FCKSM<1:0>  | FOSC      | Immediate                                                                                                       | Clock Switching Mode bits<br>1x = Clock switching is disabled, fail-safe clock monitor is disabled<br>01 = Clock switching is enabled, fail-safe clock monitor is disabled<br>00 = Clock switching is enabled, fail-safe clock monitor is enabled                                                                                                                                                   |

| IOL1WAY     | FOSC      | Immediate                                                                                                       | Peripheral Pin Select Configuration<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                    |

| OSCIOFNC    | FOSC      | Immediate                                                                                                       | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is clock output<br>0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                                                                                        |

| POSCMD<1:0> | FOSC      | Immediate                                                                                                       | Primary Oscillator Mode Select bits<br>11 = Primary oscillator disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                      |

### TABLE 19-2: PIC24HJ12GP201/202 CONFIGURATION BITS DESCRIPTION

### TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># Assembly<br>Mnemonic |        | Assembly Syntax |              | Description                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|-----------------------------------------|--------|-----------------|--------------|-----------------------------------------|---------------|----------------|--------------------------|

| 47                                      | RCALL  | RCALL           | Expr         | Relative Call                           | 1             | 2              | None                     |

|                                         |        | RCALL           | Wn           | Computed Call                           | 1             | 2              | None                     |

| 48                                      | REPEAT | REPEAT          | #lit14       | Repeat Next Instruction lit14 + 1 times | 1             | 1              | None                     |

|                                         |        | REPEAT          | Wn           | Repeat Next Instruction (Wn) + 1 times  | 1             | 1              | None                     |

| 49                                      | RESET  | RESET           |              | Software device Reset                   | 1             | 1              | None                     |

| 50                                      | RETFIE | RETFIE          |              | Return from interrupt                   | 1             | 3 (2)          | None                     |

| 51                                      | RETLW  | RETLW           | #lit10,Wn    | Return with literal in Wn               | 1             | 3 (2)          | None                     |

| 52                                      | RETURN | RETURN          |              | Return from Subroutine                  | 1             | 3 (2)          | None                     |

| 53                                      | RLC    | RLC             | f            | f = Rotate Left through Carry f         | 1             | 1              | C,N,Z                    |

|                                         |        | RLC             | f,WREG       | WREG = Rotate Left through Carry f      | 1             | 1              | C,N,Z                    |

|                                         |        | RLC             | Ws,Wd        | Wd = Rotate Left through Carry Ws       | 1             | 1              | C,N,Z                    |

| 54                                      | RLNC   | RLNC            | f            | f = Rotate Left (No Carry) f            | 1             | 1              | N,Z                      |

|                                         |        | RLNC            | f,WREG       | WREG = Rotate Left (No Carry) f         | 1             | 1              | N,Z                      |

|                                         |        | RLNC            | Ws,Wd        | Wd = Rotate Left (No Carry) Ws          | 1             | 1              | N,Z                      |

| 55                                      | RRC    | RRC             | f            | f = Rotate Right through Carry f        | 1             | 1              | C,N,Z                    |

|                                         |        | RRC             | f,WREG       | WREG = Rotate Right through Carry f     | 1             | 1              | C,N,Z                    |

|                                         |        | RRC             | Ws,Wd        | Wd = Rotate Right through Carry Ws      | 1             | 1              | C,N,Z                    |

| 56                                      | RRNC   | RRNC            | f            | f = Rotate Right (No Carry) f           | 1             | 1              | N,Z                      |

|                                         |        | RRNC            | f,WREG       | WREG = Rotate Right (No Carry) f        | 1             | 1              | N,Z                      |

|                                         |        | RRNC            | Ws,Wd        | Wd = Rotate Right (No Carry) Ws         | 1             | 1              | N,Z                      |

| 57                                      | SE     | SE              | Ws,Wnd       | Wnd = sign-extended Ws                  | 1             | 1              | C,N,Z                    |

| 58                                      | SETM   | SETM            | f            | f = 0xFFFF                              | 1             | 1              | None                     |

|                                         |        | SETM            | WREG         | WREG = 0xFFFF                           | 1             | 1              | None                     |

|                                         |        | SETM            | Ws           | Ws = 0xFFFF                             | 1             | 1              | None                     |

| 59                                      | SL     | SL              | f            | f = Left Shift f                        | 1             | 1              | C,N,OV,Z                 |

|                                         |        | SL              | f,WREG       | WREG = Left Shift f                     | 1             | 1              | C,N,OV,Z                 |

|                                         |        | SL              | Ws,Wd        | Wd = Left Shift Ws                      | 1             | 1              | C,N,OV,Z                 |

|                                         |        | SL              | Wb,Wns,Wnd   | Wnd = Left Shift Wb by Wns              | 1             | 1              | N,Z                      |

|                                         |        | SL              | Wb,#lit5,Wnd | Wnd = Left Shift Wb by lit5             | 1             | 1              | N,Z                      |

| 60                                      | SUB    | SUB             | f            | f = f – WREG                            | 1             | 1              | C,DC,N,OV,Z              |

|                                         |        | SUB             | f,WREG       | WREG = f – WREG                         | 1             | 1              | C,DC,N,OV,Z              |

|                                         |        | SUB             | #lit10,Wn    | Wn = Wn - lit10                         | 1             | 1              | C,DC,N,OV,Z              |

|                                         |        | SUB             | Wb,Ws,Wd     | Wd = Wb – Ws                            | 1             | 1              | C,DC,N,OV,               |

|                                         |        | SUB             | Wb,#lit5,Wd  | Wd = Wb – lit5                          | 1             | 1              | C,DC,N,OV,               |

| 61                                      | SUBB   | SUBB            | f            | $f = f - WREG - (\overline{C})$         | 1             | 1              | C,DC,N,OV,2              |

|                                         |        | SUBB            | f,WREG       | WREG = f – WREG – $(\overline{C})$      | 1             | 1              | C,DC,N,OV,2              |

|                                         |        | SUBB            | #lit10,Wn    | $Wn = Wn - lit10 - (\overline{C})$      | 1             | 1              | C,DC,N,OV,2              |

|                                         |        | SUBB            | Wb,Ws,Wd     | $Wd = Wb - Ws - (\overline{C})$         | 1             | 1              | C,DC,N,OV,2              |

|                                         |        | SUBB            | Wb,#lit5,Wd  | $Wd = Wb - lit5 - (\overline{C})$       | 1             | 1              | C,DC,N,OV,2              |

| 62                                      | SUBR   | SUBR            | f            | f = WREG – f                            | 1             | 1              | C,DC,N,OV,Z              |

| 02                                      | JUBR   | SUBR            | f,WREG       | WREG = WREG – f                         | 1             | 1              | C,DC,N,OV,Z              |

|                                         |        | SUBR            | Wb,Ws,Wd     | Wite - Wite - T                         | 1             | 1              | C,DC,N,OV,               |

|                                         |        | SUBR            |              | Wd = 105 - Wb                           | 1             | 1              | C,DC,N,OV,Z              |

| 63                                      | CUIDDD |                 | Wb,#lit5,Wd  | _                                       |               | 1              |                          |

| 63                                      | SUBBR  | SUBBR           | f            | f = WREG - f - (C)                      | 1             |                | C,DC,N,OV,Z              |

|                                         |        | SUBBR           | f,WREG       | WREG = WREG - f - $(\overline{C})$      | 1             | 1              | C,DC,N,OV,Z              |

|                                         |        | SUBBR           | Wb,Ws,Wd     | Wd = Ws - Wb - (C)                      | 1             | 1              | C,DC,N,OV,2              |

|                                         | ļ      | SUBBR           | Wb,#lit5,Wd  | $Wd = lit5 - Wb - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |

| 64                                      | SWAP   | SWAP.b          | Wn           | Wn = nibble swap Wn                     | 1             | 1              | None                     |

|                                         |        | SWAP            | Wn           | Wn = byte swap Wn                       | 1             | 1              | None                     |

| 65                                      | TBLRDH | TBLRDH          | Ws,Wd        | Read Prog<23:16> to Wd<7:0>             | 1             | 2              | None                     |

| DC CHARACTERISTICS |        |                                                                       | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |                    |                       |       |                                                                                                                                    |  |

|--------------------|--------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-------|------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                        | Min                                                                                                                                                                                                      | Typ <sup>(1)</sup> | Max                   | Units | Conditions                                                                                                                         |  |

| DI60a              | licl   | Input Low Injection Current                                           | 0                                                                                                                                                                                                        | _                  | <sub>-5</sub> (5,8)   | mA    | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>and SOSCO                                                           |  |