#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 12KB (4K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | <u>.</u>                                                                       |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj12gp202t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.1 Referenced Sources

This device data sheet is based on the following individual chapters of the *"dsPlC33F/PlC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the PIC24HJ12GP202 product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory (DS70202)

- Section 4. "Program Memory" (DS70202)

- Section 5. "Flash Programming" (DS70191)

- Section 6. "Interrupts" (DS70184)

- Section 7. "Oscillator" (DS70186)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-saving Modes" (DS70196)

- Section 10. "I/O Ports" (DS70193)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 16. "Analog-to-Digital Converter (ADC) with DMA" (DS70183)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Section 23. "CodeGuard Security" (DS70199)

- Section 25. "Device Configuration" (DS70194)

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

- bit 1 IC1IF: Input Capture Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

### REGISTER 10-10: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| R = Readable | bit | W = Writable I | oit         | U = Unimpler | nented bit, rea | ad as '0' |       |

|--------------|-----|----------------|-------------|--------------|-----------------|-----------|-------|

| Legend:      |     |                |             |              |                 |           |       |

| bit 7        |     |                |             |              |                 |           | bit 0 |

| bit 7        |     |                |             |              |                 |           | hit 0 |

|              |     |                | — RP0R<4:0> |              |                 |           |       |

| U-0          | U-0 | U-0            | R/W-0       | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|              |     |                |             |              |                 |           |       |

| bit 15       |     | •              |             |              |                 |           | bit 8 |

| _            | _   |                |             |              | RP1R<4:0>       | >         |       |

| U-0          | U-0 | U-0            | R/W-0       | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

- bit 15-13 **Unimplemented:** Read as '0'

- bit 12-8 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 10-2 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 10-2 for peripheral function numbers)

### REGISTER 10-11: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | U-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|-----|-----|-----------|-------|-------|-------|-------|--|

| —      | —   | —   | RP3R<4:0> |       |       |       |       |  |

| bit 15 |     |     |           |       |       |       | bit 8 |  |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP2R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-2 for peripheral function numbers)

# 12.0 TIMER2/3 FEATURE

- Note 1: This data sheet summarizes the features of the PIC24HJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 11. Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 feature has 32-bit timers that can also be configured as two independent 16-bit timers with selectable operating modes.

As a 32-bit timer, the Timer2/3 feature permits operation in three modes:

- Two Independent 16-bit timers (Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer (Timer2/3)

- Single 32-bit synchronous counter (Timer2/3)

The Timer2/3 feature also supports:

- Timer gate operation

- Selectable Prescaler Settings

- · Timer operation during Idle and Sleep modes

- Interrupt on a 32-bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (Timer2/3 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON and T3CON registers. T2CON registers are shown in generic form in Register 12-1. T3CON registers are shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 is the lsw, and Timer3 is the msw of the 32-bit timers.

Note: For 32-bit operation, T3CON control bits are ignored. Only T2CON control bit is used for setup and control. Timer2 clock and gate inputs are used for the 32-bit timer modules, but an interrupt is generated with the Timer3 interrupt flags.

## 12.1 32-bit Operation

To configure the Timer2/3 feature for 32-bit operation:

- 1. Set the corresponding T32 control bit.

- 2. Select the prescaler ratio for Timer2 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3 contains the msw of the value, while PR2 contains the lsw.

- 5. If interrupts are required, set the interrupt enable bit, T3IE. Use the priority bits T3IP<2:0> to set the interrupt priority. While Timer2 controls the timer, the interrupt appears as a Timer3 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair TMR3:TMR2. TMR3 always contains the msw of the count, while TMR2 contains the lsw.

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

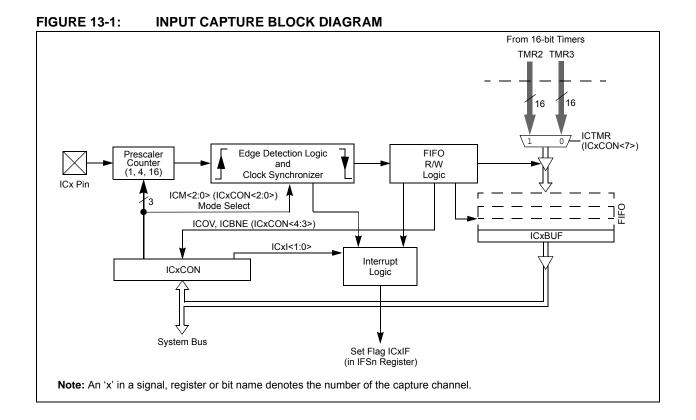

## 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the PIC24HJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 12. Input Capture" (DS70198) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement. The PIC24HJ12GP201/202 devices support up to eight input capture channels.

The Input Capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each Input Capture channel can select one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on Input Capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Use of Input Capture to provide additional sources of external interrupts

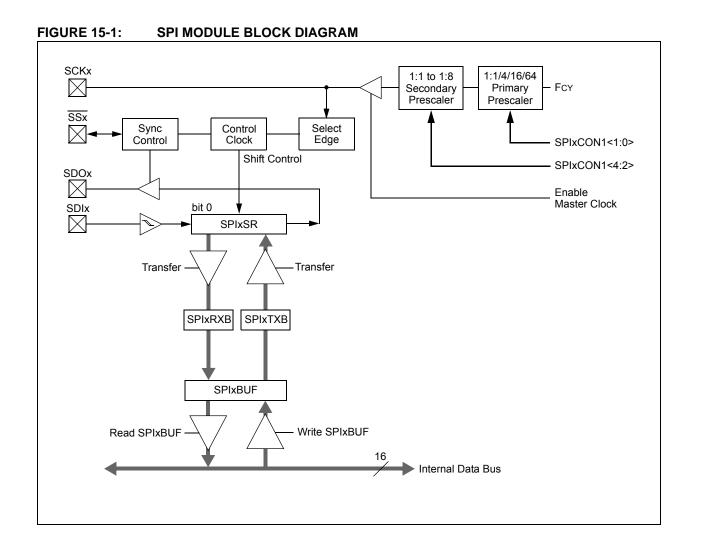

## 15.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC24HJ12GP201/202 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Section 18. Serial Peripheral Interface (SPI)" (DS70206) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, analog-to-digital (A/D) converters, etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates status conditions.

The serial interface consists of 4 pins:

- · SDIx (serial data input)

- · SDOx (serial data output)

- SCKx (shift clock input or output)

- · SSx (active low slave select).

In Master mode operation, SCK is a clock output. In Slave mode, it is a clock input.

| R/W-0          | R/W-0                                        | R/W-0                                                                             | U-0                                    | R/W-0 HC         | R/W-0                                 | R-0                | R-1           |  |  |  |

|----------------|----------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------|------------------|---------------------------------------|--------------------|---------------|--|--|--|

| UTXISEL1       | UTXINV                                       | UTXISEL0                                                                          |                                        | UTXBRK           | UTXEN <sup>(1)</sup>                  | UTXBF              | TRMT          |  |  |  |

| pit 15         |                                              |                                                                                   |                                        |                  |                                       |                    | bit           |  |  |  |

| R/W-0          | R/W-0                                        | R/W-0                                                                             | R-1                                    | R-0              | R-0                                   | R/C-0              | R-0           |  |  |  |

|                |                                              | ADDEN                                                                             | RIDLE                                  | PERR             | FERR                                  | OERR               | 1             |  |  |  |

| URXISE         | L<1.0>                                       | ADDEN                                                                             | RIDLE                                  | PERK             | FERR                                  | UERR               | URXDA         |  |  |  |

|                |                                              |                                                                                   |                                        |                  |                                       |                    |               |  |  |  |

| _egend:        |                                              | HC = Hardwar                                                                      | e cleared                              |                  |                                       |                    |               |  |  |  |

| R = Readable   | bit                                          | W = Writable b                                                                    | pit                                    | U = Unimpler     | nented bit, read                      | as '0'             |               |  |  |  |

| n = Value at F | POR                                          | '1' = Bit is set                                                                  |                                        | '0' = Bit is cle | ared                                  | x = Bit is unkr    | nown          |  |  |  |

| bit 15,13      | 11 = Reserve<br>10 = Interrupt               | <b>0&gt;:</b> Transmissio<br>ed; do not use<br>t when a charac<br>t buffer become | ter is transfe                         |                  | bits<br>nsmit Shift Regi              | ster, and as a r   | esult, the    |  |  |  |

|                | 01 = Interrupt<br>operatio<br>00 = Interrupt | t when the last ons are complete                                                  | character is s<br>ed<br>ter is transfe | rred to the Trar | e Transmit Shift<br>nsmit Shift Regi  | -                  |               |  |  |  |

| pit 14         |                                              |                                                                                   | •                                      |                  |                                       |                    |               |  |  |  |

| JIL 14         | If IREN = $0$ :                              | nsmit Polarity In                                                                 |                                        |                  |                                       |                    |               |  |  |  |

|                | 1 = UxTX Idl                                 | e state is '0'                                                                    |                                        |                  |                                       |                    |               |  |  |  |

|                | 0 = UxTX Idl                                 |                                                                                   |                                        |                  |                                       |                    |               |  |  |  |

|                | If IREN = 1:                                 |                                                                                   |                                        |                  |                                       |                    |               |  |  |  |

|                |                                              | oded UxTX Idle                                                                    | state is '1'                           |                  |                                       |                    |               |  |  |  |

|                | 0 = IrDA enc                                 | oded UxTX Idle                                                                    | state is '0'                           |                  |                                       |                    |               |  |  |  |

| bit 12         | Unimplemen                                   | ted: Read as '0                                                                   | )'                                     |                  |                                       |                    |               |  |  |  |

| pit 11         | UTXBRK: Transmit Break bit                   |                                                                                   |                                        |                  |                                       |                    |               |  |  |  |

|                | cleared b                                    | nc Break on nex<br>by hardware upo<br>eak transmissior                            | on completion                          | า                | llowed by twelve                      | e '0' bits, follow | ed by Stop b  |  |  |  |

| bit 10         | •                                            | smit Enable bit                                                                   |                                        | · · · · · ·      |                                       |                    |               |  |  |  |

|                | 1 = Transmit                                 | enabled, UxTX                                                                     | pin controlle                          |                  | rted and buffer                       | is reset. UxTX     | pin controlle |  |  |  |

| oit 9          | • •                                          | smit Buffer Full                                                                  | Status bit (re                         | ead-only)        |                                       |                    |               |  |  |  |

|                | 1 = Transmit                                 |                                                                                   | ·                                      | •                |                                       |                    |               |  |  |  |

|                | 0 = Transmit                                 | buffer is not ful                                                                 | l, at least one                        | e more characte  | er can be writter                     | ו                  |               |  |  |  |

| oit 8          | TRMT: Trans                                  | mit Shift Registe                                                                 | er Empty bit                           | (read-only)      |                                       |                    |               |  |  |  |

|                |                                              |                                                                                   |                                        |                  | s empty (the last<br>is in progress o |                    | as completed  |  |  |  |

| oit 7-6        | URXISEL<1:                                   | 0>: Receive Inte                                                                  | errupt Mode                            | Selection bits   |                                       |                    |               |  |  |  |

| JIL 7-0        |                                              |                                                                                   | -                                      |                  |                                       |                    |               |  |  |  |

### REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

**Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

### REGISTER 18-4: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

|            | Legend:<br>R = Readable bit W = Writable bit |     |     | U = Unimpler | nented bit read | 1 as '0' |         |

|------------|----------------------------------------------|-----|-----|--------------|-----------------|----------|---------|

|            |                                              |     |     |              |                 |          | bit 0   |

|            | _                                            | —   | —   | —            | CH123N          | IA<1:0>  | CH123SA |

| <br>bit 15 | U-0                                          | U-0 | U-0 | U-0          | R/W-0           | R/W-0    | R/W-0   |

|            |                                              |     |     |              |                 |          | DILO    |

| —          |                                              |     |     |              |                 |          | bit 8   |

|            | _                                            | —   | _   | —            | CH123NB<1:0>    |          | CH123SB |

| U-0        | U-0                                          | U-0 | U-0 | U-0          | R/W-0           | R/W-0    | R/W-0   |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9 CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample B bits PIC24HJ12GP201 devices only: If AD12B = 1:

11 = Reserved

10 = Reserved

01 = Reserved

00 = Reserved

If AD12B = 0:

11 = Reserved

10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is not connected

01 = CH1, CH2, CH3 negative input is VREF-

00 = CH1, CH2, CH3 negative input is VREF-

### PIC24HJ12GP202 devices only:

<u>If AD12B = 1:</u> 11 = Reserved 10 = Reserved

01 = Reserved

01 - Reserved

00 = Reserved

If AD12B = 0:

11 = CH1 negative input is AN9, CH2 and CH3 negative inputs are not connected

10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8

01 = CH1, CH2, CH3 negative input is VREF-

00 = CH1, CH2, CH3 negative input is VREF-

### REGISTER 18-5: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

bit 4-0 CH0SA<4:0>: Channel 0 Positive Input Select for Sample A bits

#### PIC24HJ12GP201 devices only:

- 00111 = Channel 0 positive input is AN7

- 00110 = Channel 0 positive input is AN6

- 00101 = Reserved

- 00100 = Reserved

- 00011 = Channel 0 positive input is AN3

- 00010 = Channel 0 positive input is AN2

- 00001 = Channel 0 positive input is AN1

- 00000 = Channel 0 positive input is AN0

### PIC24HJ12GP202 devices only:

01001 = Channel 0 positive input is AN9

- •

- 00010 = Channel 0 positive input is AN2 00001 = Channel 0 positive input is AN1 00000 = Channel 0 positive input is AN0

# PIC24HJ12GP201/202

### TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic Assembly Syntax Description |         | Assembly Syntax | Description                                                | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|--------------------------------------------------|---------|-----------------|------------------------------------------------------------|---------------|----------------|--------------------------|

| 12                 | BTST                                             | BTST    | f,#bit4         | Bit Test f                                                 | 1             | 1              | Z                        |

|                    |                                                  | BTST.C  | Ws,#bit4        | Bit Test Ws to C                                           | 1             | 1              | С                        |

|                    |                                                  | BTST.Z  | Ws,#bit4        | Bit Test Ws to Z                                           | 1             | 1              | Z                        |

|                    |                                                  | BTST.C  | Ws,Wb           | Bit Test Ws <wb> to C</wb>                                 | 1             | 1              | С                        |

|                    |                                                  | BTST.Z  | Ws,Wb           | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1              | Z                        |

| 13                 | BTSTS                                            | BTSTS   | f,#bit4         | Bit Test then Set f                                        | 1             | 1              | Z                        |

|                    |                                                  | BTSTS.C | Ws,#bit4        | Bit Test Ws to C, then Set                                 | 1             | 1              | С                        |

|                    |                                                  | BTSTS.Z | Ws,#bit4        | Bit Test Ws to Z, then Set                                 | 1             | 1              | Z                        |

| 14                 | CALL                                             | CALL    | lit23           | Call subroutine                                            | 2             | 2              | None                     |

|                    |                                                  | CALL    | Wn              | Call indirect subroutine                                   | 1             | 2              | None                     |

| 15                 | CLR                                              | CLR     | f               | f = 0x0000                                                 | 1             | 1              | None                     |

|                    |                                                  | CLR     | WREG            | WREG = 0x0000                                              | 1             | 1              | None                     |

|                    |                                                  | CLR     | Ws              | Ws = 0x0000                                                | 1             | 1              | None                     |

| 16                 | CLRWDT                                           | CLRWDT  |                 | Clear Watchdog Timer                                       | 1             | 1              | WDTO,Sleep               |

| 17                 | COM                                              | СОМ     | f               | $f = \overline{f}$                                         | 1             | 1              | N,Z                      |

|                    |                                                  | СОМ     | f,WREG          | WREG = $\overline{f}$                                      | 1             | 1              | N,Z                      |

|                    |                                                  |         |                 | $Wd = \overline{Ws}$                                       | 1             | 1              | N,Z                      |

| 18                 | CP                                               | COM     | Ws,Wd<br>f      |                                                            | 1             | 1              | ,                        |

| 10                 | CP                                               | CP      |                 | Compare f with WREG                                        |               |                | C,DC,N,OV,Z              |

|                    |                                                  | CP      | Wb,#lit5        | Compare Wb with lit5                                       | 1             | 1              | C,DC,N,OV,Z              |

| 10                 |                                                  | CP      | Wb,Ws           | Compare Wb with Ws (Wb – Ws)                               | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CPO                                              | CP0     | f               | Compare f with 0x0000                                      | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                  | CP0     | Ws              | Compare Ws with 0x0000                                     | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                                              | CPB     | f               | Compare f with WREG, with Borrow                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                  | CPB     | Wb,#lit5        | Compare Wb with lit5, with Borrow                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                  | CPB     | Wb,Ws           | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1              | C,DC,N,OV,Z              |

| 21                 | CPSEQ                                            | CPSEQ   | Wb, Wn          | Compare Wb with Wn, skip if =                              | 1             | 1<br>(2 or 3)  | None                     |

| 22                 | CPSGT                                            | CPSGT   | Wb, Wn          | Compare Wb with Wn, skip if >                              | 1             | 1<br>(2 or 3)  | None                     |

| 23                 | CPSLT                                            | CPSLT   | Wb, Wn          | Compare Wb with Wn, skip if <                              | 1             | 1<br>(2 or 3)  | None                     |

| 24                 | CPSNE                                            | CPSNE   | Wb, Wn          | Compare Wb with Wn, skip if $\neq$                         | 1             | 1<br>(2 or 3)  | None                     |

| 25                 | DAW                                              | DAW     | Wn              | Wn = decimal adjust Wn                                     | 1             | 1              | С                        |

| 26                 | DEC                                              | DEC     | f               | f = f - 1                                                  | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                  | DEC     | f,WREG          | WREG = f – 1                                               | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                  | DEC     | Ws,Wd           | Wd = Ws - 1                                                | 1             | 1              | C,DC,N,OV,Z              |

| 27                 | DEC2                                             | DEC2    | f               | f = f - 2                                                  | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                  | DEC2    | f,WREG          | WREG = f – 2                                               | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                  | DEC2    | Ws,Wd           | Wd = Ws - 2                                                | 1             | 1              | C,DC,N,OV,Z              |

| 28                 | DISI                                             | DISI    | #lit14          | Disable Interrupts for k instruction cycles                | 1             | 1              | None                     |

| 29                 | DIV                                              | DIV.S   | Wm,Wn           | Signed 16/16-bit Integer Divide                            | 1             | 18             | N,Z,C,OV                 |

|                    |                                                  | DIV.SD  | Wm,Wn           | Signed 32/16-bit Integer Divide                            | 1             | 18             | N,Z,C,OV                 |

|                    |                                                  | DIV.U   | Wm,Wn           | Unsigned 16/16-bit Integer Divide                          | 1             | 18             | N,Z,C,OV                 |

|                    |                                                  | DIV.UD  | Wm,Wn           | Unsigned 32/16-bit Integer Divide                          | 1             | 18             | N,Z,C,OV                 |

| 30                 | EXCH                                             | EXCH    | Wns,Wnd         | Swap Wns with Wnd                                          | 1             | 1              | None                     |

| 31                 | FBCL                                             | FBCL    | Ws,Wnd          | Find Bit Change from Left (MSb) Side                       | 1             | 1              | C                        |

| 32                 | FF1L                                             | FF1L    | Ws,Wnd          | Find First One from Left (MSb) Side                        | 1             | 1              | C                        |

| 33                 | FF1R                                             | FF1R    | Ws,Wnd          | Find First One from Right (LSb) Side                       | 1             | 1              | C                        |

| 34                 | GOTO                                             | GOTO    | Expr            | Go to address                                              | 2             | 2              | None                     |

| • •                |                                                  | GOTO    | Wn              | Go to indirect                                             | 1             | 2              | None                     |

| IABL               | E 20-2:              | INSTRUCTION SET OVERVIEW (CONTINUED) |                 |                                                   |               |                |                          |  |  |  |  |

|--------------------|----------------------|--------------------------------------|-----------------|---------------------------------------------------|---------------|----------------|--------------------------|--|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                      | Assembly Syntax | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |  |  |  |

| 35                 | INC                  | INC                                  | f               | f = f + 1                                         | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC                                  | f,WREG          | WREG = f + 1                                      | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC                                  | Ws,Wd           | Wd = Ws + 1                                       | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

| 36                 | INC2                 | INC2                                 | f               | f = f + 2                                         | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC2                                 | f,WREG          | WREG = f + 2                                      | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC2                                 | Ws,Wd           | Wd = Ws + 2                                       | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

| 37                 | IOR                  | IOR                                  | f               | f = f .IOR. WREG                                  | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | IOR                                  | f,WREG          | WREG = f .IOR. WREG                               | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | IOR                                  | #lit10,Wn       | Wd = lit10 .IOR. Wd                               | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | IOR                                  | Wb,Ws,Wd        | Wd = Wb .IOR. Ws                                  | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | IOR                                  | Wb,#lit5,Wd     | Wd = Wb .IOR. lit5                                | 1             | 1              | N,Z                      |  |  |  |  |

| 38                 | LNK                  | LNK                                  | #lit14          | Link Frame Pointer                                | 1             | 1              | None                     |  |  |  |  |

| 39                 | LSR                  | LSR                                  | f               | f = Logical Right Shift f                         | 1             | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |                      | LSR                                  | f,WREG          | WREG = Logical Right Shift f                      | 1             | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |                      | LSR                                  | Ws,Wd           | Wd = Logical Right Shift Ws                       | 1             | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |                      | LSR                                  | Wb,Wns,Wnd      | Wnd = Logical Right Shift Wb by Wns               | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | LSR                                  | Wb,#lit5,Wnd    | Wnd = Logical Right Shift Wb by lit5              | 1             | 1              | N,Z                      |  |  |  |  |

| 40                 | MOV                  | MOV                                  | f,Wn            | Move f to Wn                                      | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV                                  | f               | Move f to f                                       | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | MOV                                  | f,WREG          | Move f to WREG                                    | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV                                  | #lit16,Wn       | Move 16-bit literal to Wn                         | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV.b                                | #lit8,Wn        | Move 8-bit literal to Wn                          | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV                                  | Wn,f            | Move Wn to f                                      | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV                                  | Wso,Wdo         | Move Ws to Wd                                     | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV                                  | WREG, f         | Move WREG to f                                    | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV.D                                | Wns,Wd          | Move Double from W(ns):W(ns + 1) to Wd            | 1             | 2              | None                     |  |  |  |  |

|                    |                      | MOV.D                                | Ws,Wnd          | Move Double from Ws to W(nd + 1):W(nd)            | 1             | 2              | None                     |  |  |  |  |

| 41                 | MUL                  | MUL.SS                               | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)          | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MUL.SU                               | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MUL.US                               | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MUL.UU                               | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MUL.SU                               | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)      | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MUL.UU                               | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MUL                                  | f               | W3:W2 = f * WREG                                  | 1             | 1              | None                     |  |  |  |  |

| 42                 | NEG                  | NEG                                  | f               | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | NEG                                  | f,WREG          | WREG = $\overline{f}$ + 1                         | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | NEG                                  | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

| 43                 | NOP                  | NOP                                  |                 | No Operation                                      | 1             | 1              | None                     |  |  |  |  |

|                    |                      | NOPR                                 |                 | No Operation                                      | 1             | 1              | None                     |  |  |  |  |

| 44                 | POP                  | POP                                  | f               | Pop f from Top-of-Stack (TOS)                     | 1             | 1              | None                     |  |  |  |  |

|                    |                      | POP                                  | Wdo             | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1              | None                     |  |  |  |  |

|                    |                      | POP.D                                | Wnd             | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2              | None                     |  |  |  |  |

|                    |                      | POP.S                                |                 | Pop Shadow Registers                              | 1             | 1              | All                      |  |  |  |  |

| 45                 | PUSH                 | PUSH                                 | f               | Push f to Top-of-Stack (TOS)                      | 1             | 1              | None                     |  |  |  |  |

|                    |                      | PUSH                                 | Wso             | Push Wso to Top-of-Stack (TOS)                    | 1             | 1              | None                     |  |  |  |  |

|                    |                      | PUSH.D                               | Wns             | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)        | 1             | 2              | None                     |  |  |  |  |

|                    |                      | PUSH.S                               |                 | Push Shadow Registers                             | 1             | 1              | None                     |  |  |  |  |

| 46                 | PWRSAV               | PWRSAV                               | #lit1           | Go into Sleep or Idle mode                        | 1             | 1              | WDTO,Sleep               |  |  |  |  |

### TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

# PIC24HJ12GP201/202

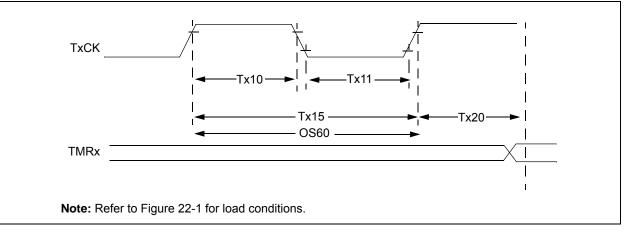

### FIGURE 22-5: TIMER1, 2, 3 AND 4 EXTERNAL CLOCK TIMING CHARACTERISTICS

| АС СНА       | ARACTERIS | TICS                                                                                                    |                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                               |     |                  |                       |                                          |

|--------------|-----------|---------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------|-----------------------------------------------|-----|------------------|-----------------------|------------------------------------------|

| Param<br>No. | Symbol    | Charact                                                                                                 | eristic               |                                                      | Min                                           | Тур | Мах              | Units                 | Conditions                               |

| TA10         | ТтхН      | TxCK High Time                                                                                          | Synchron<br>no presc  |                                                      | Тсү + 20                                      |     | _                | ns                    | Must also meet parameter TA15.           |

|              |           |                                                                                                         | Synchron with pres    |                                                      | (Tcy + 20)/N                                  |     | _                | ns                    | N = prescale<br>value                    |

|              |           |                                                                                                         | Asynchro              | onous                                                | 20                                            | _   | —                | ns                    | (1, 8, 64, 256)                          |

| TA11         |           |                                                                                                         | Synchroi<br>no presc  |                                                      | (Tcy + 20)                                    | _   | —                | ns                    | Must also meet parameter TA15.           |

|              |           | Synchronous, with prescaler                                                                             |                       | (Tcy + 20)/N                                         | _                                             | —   | ns               | N = prescale<br>value |                                          |

|              |           |                                                                                                         | Asynchro              | onous                                                | 20                                            |     | _                | ns                    | (1, 8, 64, 256)                          |

| TA15         | ΤτχΡ      | TxCK Input<br>Period                                                                                    | Synchroi<br>no presc  |                                                      | 2 Tcy + 40                                    | _   | —                | ns                    | —                                        |

|              |           |                                                                                                         | Synchroi<br>with pres |                                                      | Greater of:<br>40 ns or<br>(2 TCY + 40)/<br>N | _   | _                | _                     | N = prescale<br>value<br>(1, 8, 64, 256) |

|              |           |                                                                                                         | Asynchro              | onous                                                | 40                                            | _   | _                | ns                    | —                                        |

| OS60         | Ft1       | SOSCI/T1CK Oscillator Input<br>frequency Range (oscillator<br>enabled by setting bit TCS<br>(T1CON<1>)) |                       |                                                      | DC                                            |     | 50               | kHz                   | —                                        |

| TA20         | TCKEXTMRL | Delay from Extern<br>Edge to Timer Inc                                                                  |                       | Clock                                                | 0.75 Tcy +<br>40                              |     | 1.75 Tcy +<br>40 |                       | _                                        |

# TABLE 22-22: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

Note 1: Timer1 is a Type A.

# TABLE 22-34:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       | AC CHARACTERISTICS    |                                                            |              | erating<br>erwise st<br>mperatur | <b>ated)</b><br>e -40° | C ≤TA ≤+ | V to 3.6V<br>85°C for Industrial<br>125°C for Extended |

|--------------|-----------------------|------------------------------------------------------------|--------------|----------------------------------|------------------------|----------|--------------------------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                              | Min          | Тур <sup>(2)</sup>               | Max                    | Units    | Conditions                                             |

| SP70         | TscP                  | Maximum SCK Input Frequency                                | —            | —                                | 15                     | MHz      | See Note 3                                             |

| SP72         | TscF                  | SCKx Input Fall Time                                       | —            | —                                |                        | ns       | See parameter DO32 and <b>Note 4</b>                   |

| SP73         | TscR                  | SCKx Input Rise Time                                       | —            | _                                | _                      | ns       | See parameter DO31 and <b>Note 4</b>                   |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                 | —            | _                                | _                      | ns       | See parameter DO32 and <b>Note 4</b>                   |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                 | —            | _                                | _                      | ns       | See parameter DO31 and <b>Note 4</b>                   |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                  | —            | 6                                | 20                     | ns       | —                                                      |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge               | 30           | —                                |                        | ns       | —                                                      |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                 | 30           | —                                |                        | ns       | —                                                      |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                  | 30           | _                                |                        | ns       | —                                                      |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow to SCKx \uparrow or SCKx Input$ | 120          | _                                | —                      | ns       | —                                                      |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup>      | 10           | _                                | 50                     | ns       | —                                                      |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                        | 1.5 TCY + 40 | —                                |                        | ns       | See Note 4                                             |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the SCK clock generated by the Master must not violate this specification.

**4:** Assumes 50 pF load on all SPIx pins.

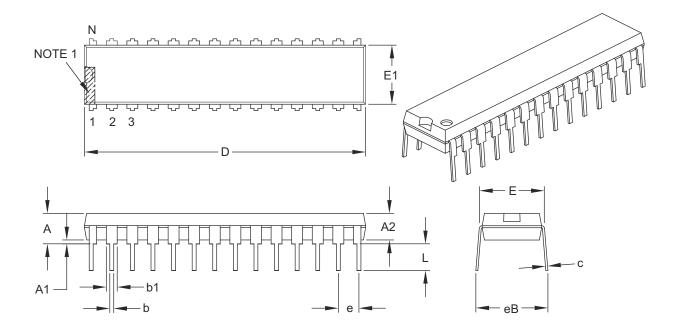

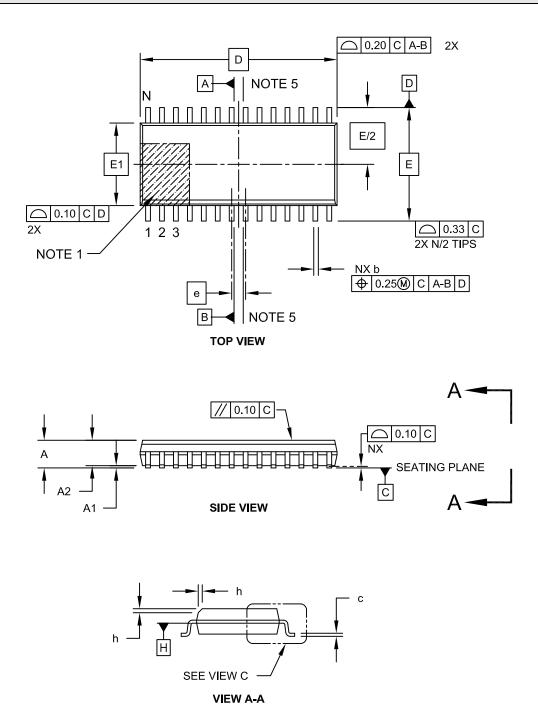

### 28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | INCHES   |       |       |

|----------------------------|----|----------|-------|-------|

| Dimension Limits           |    | MIN      | NOM   | MAX   |

| Number of Pins             | Ν  | 28       |       |       |

| Pitch                      | е  | .100 BSC |       |       |

| Top to Seating Plane       | Α  | -        | _     | .200  |

| Molded Package Thickness   | A2 | .120     | .135  | .150  |

| Base to Seating Plane      | A1 | .015     | -     | -     |

| Shoulder to Shoulder Width | Е  | .290     | .310  | .335  |

| Molded Package Width       | E1 | .240     | .285  | .295  |

| Overall Length             | D  | 1.345    | 1.365 | 1.400 |

| Tip to Seating Plane       | L  | .110     | .130  | .150  |

| Lead Thickness             | С  | .008     | .010  | .015  |

| Upper Lead Width           | b1 | .040     | .050  | .070  |

| Lower Lead Width           | b  | .014     | .018  | .022  |

| Overall Row Spacing §      | eB | -        | -     | .430  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

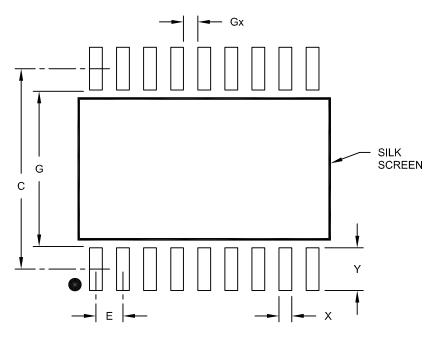

## RECOMMENDED LAND PATTERN

|                       | Units | Units MILLIMETERS |      |      |

|-----------------------|-------|-------------------|------|------|

| Dimension Limits      |       | MIN               | NOM  | MAX  |

| Contact Pitch         | E     | 1.27 BSC          |      |      |

| Contact Pad Spacing   | С     |                   | 9.40 |      |

| Contact Pad Width     | X     |                   |      | 0.60 |

| Contact Pad Length    | Y     |                   |      | 2.00 |

| Distance Between Pads | Gx    | 0.67              |      |      |

| Distance Between Pads | G     | 7.40              |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

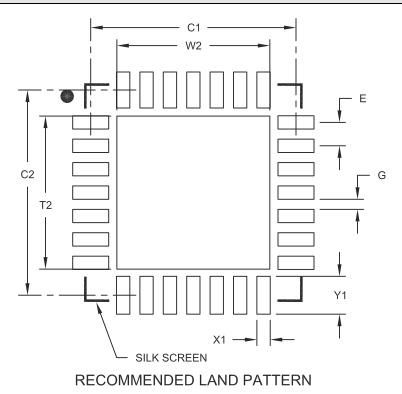

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |      |      |  |

|----------------------------|----|-------------|------|------|--|

| Dimension Limits           |    | MIN         | NOM  | MAX  |  |

| Contact Pitch              | E  | 0.65 BSC    |      |      |  |

| Optional Center Pad Width  | W2 |             |      | 4.25 |  |

| Optional Center Pad Length | T2 |             |      | 4.25 |  |

| Contact Pad Spacing        | C1 |             | 5.70 |      |  |

| Contact Pad Spacing        | C2 |             | 5.70 |      |  |

| Contact Pad Width (X28)    | X1 |             |      | 0.37 |  |

| Contact Pad Length (X28)   | Y1 |             |      | 1.00 |  |

| Distance Between Pads      | G  | 0.20        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

# PIC24HJ12GP201/202

NOTES:

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3180 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-213-7830 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

05/02/11