Welcome to E-XFL.COM

#### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

#### Details

| Product Status                  | Obsolete                                                                      |

|---------------------------------|-------------------------------------------------------------------------------|

| Programmable Type               | In System Programmable                                                        |

| Delay Time tpd(1) Max           | 7.5 ns                                                                        |

| Voltage Supply - Internal       | 3V ~ 3.6V                                                                     |

| Number of Logic Elements/Blocks | 32                                                                            |

| Number of Macrocells            | 1024                                                                          |

| Number of Gates                 |                                                                               |

| Number of I/O                   | 317                                                                           |

| Operating Temperature           | 0°C ~ 90°C (TJ)                                                               |

| Mounting Type                   | Surface Mount                                                                 |

| Package / Case                  | 484-BBGA                                                                      |

| Supplier Device Package         | 484-FPBGA (23x23)                                                             |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lc51024mv-75fn484c |

|                                 |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Introduction

The ispXPLD 5000MX family represents a new class of device, referred to as the eXpanded Programmable Logic Devices (XPLDs). These devices extend the capability of Lattice's popular SuperWIDE ispMACH 5000 architecture by providing flexible memory capability. The family supports single- or dual-port SRAM, FIFO, and ternary CAM operation. Extra logic has also been included to allow efficient implementation of arithmetic functions. In addition, sysCLOCK PLLs and sysIO interfaces provide support for the system-level needs of designers.

The devices provide designers with a convenient one-chip solution that provides logic availability at boot-up, design security, and extreme reconfigurability. The use of advanced process technology provides industry-leading performance with combinatorial propagation delay as low as 4.0ns, 2.8ns clock-to-out delay, 2.2ns set-up time, and operating frequency up to 300MHz. This performance is coupled with low static and dynamic power consumption. The ispXPLD 5000MX architecture provides predictable deterministic timing.

The availability of 3.3, 2.5 and 1.8V versions of these devices along with the flexibility of the sysIO interface helps users meet the challenge of today's mixed voltage designs. Inputs can be safely driven up to 5.5V when an I/O bank is configured for 3.3V operation, making this family 5V tolerant. Boundary scan testability further eases integration into today's complex systems. A variety of density and package options increase the likelihood of a good fit for a particular application. Table 1 shows the members of the ispXPLD 5000MX family.

### Architecture

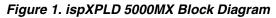

The ispXPLD 5000MX devices consist of Multi-Function Blocks (MFBs) interconnected with a Global Routing Pool. Signals enter and leave the device via one of four sysIO banks. Figure 1 shows the block diagram of the ispXPLD

#### Lattice Semiconductor

5000MX. Incoming signals may connect to the global routing pool or the registers in the MFBs. An Output Sharing Array (OSA) increases the number of I/O available to each MFB, allowing a complete function high-performance access to the I/O. There are four clock pins that drive four global clock nets within the device. Two sysCLOCK PLLs are provided to allow the synthesis of new clocks and control of clock skews.

### **Multi-Function Block (MFB)**

Each MFB in the ispXPLD 5000MX architecture can be configured in one of the six following modes. This provides a flexible approach to implementing logic and memory that allows the designer to achieve the mix of functions that are required for a particular design, maximizing resource utilization. The six modes supported by the MFB are:

- SuperWIDE Logic Mode

- True Dual-port SRAM Mode

- Pseudo Dual-port SRAM Mode

- Single-port SRAM Mode

- FIFO Mode

- Ternary CAM Mode

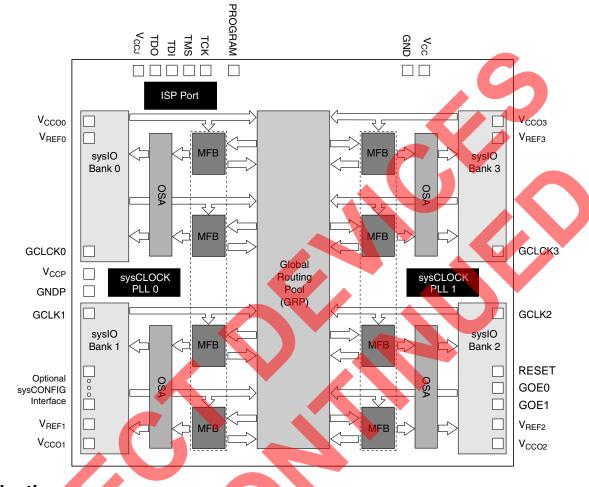

The MFB consists of a multi-function array and associated routing. Depending on the chosen functions the multifunction array uses up to 68 inputs from the GRP and the four global clock and reset signals. The array outputs data along with certain control functions to the macrocells. Output signals can be routed internally for use elsewhere in the device and to the sysIO banks for output. Figure 2 shows the block diagram of the MFB. The various configurations are described in more detail in the following sections.

#### Figure 2. MFB Block Diagram

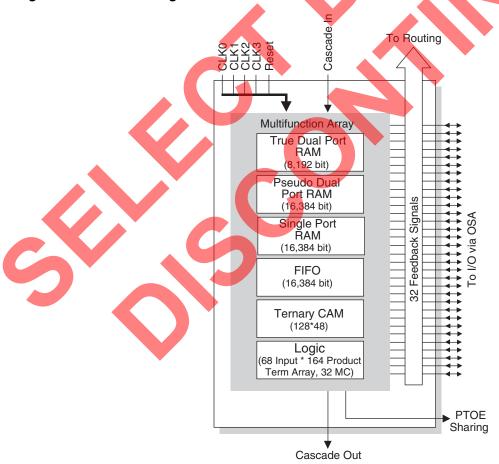

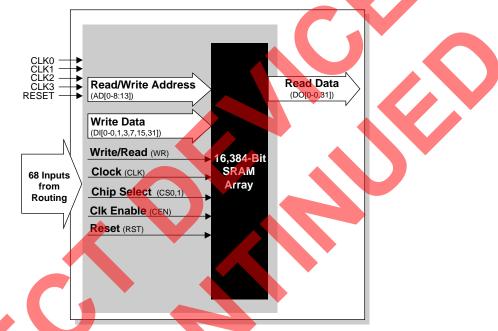

#### Single-Port SRAM Mode

In Single-Port SRAM Mode the multi-function array is configured as a single-port SRAM. In this mode one ports accesses 16,384-bits of memory. Data widths of 1, 2, 4, 8, 16 and 32 are supported by the MFB. Figure 11 shows the block diagram of the single-port SRAM.

Write data, address, chip select and read/write signals are always synchronous (registered.) The output data signals can be synchronous or asynchronous. Reset is asynchronous. All signals share a common clock, clock enable, and reset. Table 7 shows the possible sources for the clock, clock enable and reset signals.

Table 7. Register Clock, Clock Enable, and Reset in Single-Port SRAM Mode

| Register                            | Input        | Source                                                                                                                                      |

|-------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Address, Write Data,                | Clock        | CLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                           |

| Read Data, Read/<br>Write, and Chip | Clock Enable | CEN or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                          |

| Select                              | Reset        | Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction array from GRP, with inversion if desired. |

|                                     |              |                                                                                                                                             |

#### **FIFO Mode**

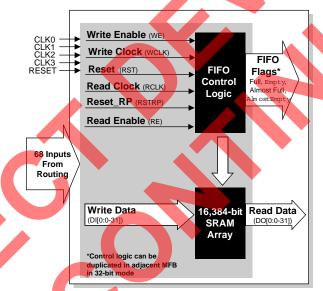

In FIFO Mode the multi-function array is configured as a FIFO (First In First Out) buffer with built in control. The read and write clocks can be different or the same dependent on the application. Four flags show the status of the FIFO; Full, Empty, Almost Full, and Almost Empty. The thresholds for Full, Almost full and Almost empty are programmable by the user. It is possible to reset the read pointer, allowing support of frame retransmit in communications applications. If desired, the block can be used in show ahead mode allowing the early reading of the next read address.

In this mode one ports accesses 16,384-bits of memory. Data widths of 1, 2, 4, 8, 16 and 32 are supported by the MFB. Figure 12 shows the block diagram of the FIFO.

Write data, write enable, flag outputs and read enable are synchronous. The Write Data, Almost Full and Full share the same clock and clock enables. Read outputs are synchronous although these can be configured in look ahead mode. The Read Data, Empty and Almost Empty signals share the same clock and clock enables. Reset is shared by all signals. Table 8 shows the possible sources for the clock, clock enable and reset signals for the various registers.

#### Figure 12. FIFO Block Diagram

#### Table 8. Register Clocks, Clock Enables, and Initialization in FIFO Mode

| Register                           | Input           | Source                                                                                                                                      |

|------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | Clock           | WCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                          |

| Write Enable                       | Clock<br>Enable | WE or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                           |

|                                    | Reset           | N/A                                                                                                                                         |

| Full and                           | Clock           | WCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                          |

| Almost Full<br>Flags               | Clock<br>Enable | WE or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                           |

|                                    | Reset           | Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction array from GRP, with inversion if desired. |

| ,                                  | Clock           | RCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                          |

| Empty and<br>Almost Empty<br>Flags | Clock<br>Enable | RE or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                           |

|                                    | Reset           | Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction array from GRP, with inversion if desired. |

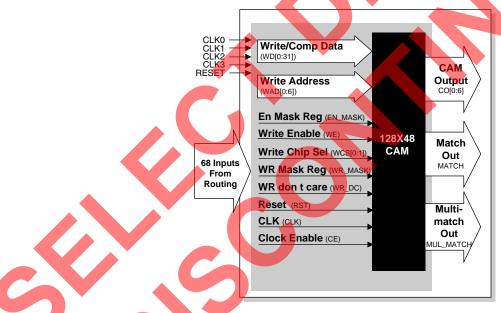

#### CAM Mode

In CAM Mode the multi-function array is configured as a Ternary Content Addressable Memory (CAM). CAM behaves like a reverse memory where the input is data and the output is an address. It can be used to perform a variety of high-performance look-up functions. As such, CAM has two modes of operation. In write or update mode the CAM behaves as a RAM and data is written to the supplied address. In read or compare operations data is supplied to the CAM and if this matches any of the data in the array the Match and Multiple Match (if there is more than one match) flags are set to true and the lowest address with matching data is output. The CAM contains 128 entries of 48 bits. Figure 13 shows the block diagram of the CAM.

To further enhance the flexibility of the CAM a mask register is available. If enabled during updates, bits corresponding with those set to 1 in the mask register are not updated. If enabled during compare operations, bits corresponding to those set to 1 in the mask register are not included in the compare. A write don't care signal allows don't cares to be programmed into the CAM if desired. Like other write operations the mask register controls this.

The write/comp data, write address, write enable, write chip select, and write don't care signals are synchronous. The CAM Output signals, match flag, and multimatch flag can be synchronous or asynchronous. The Enable mask register input is not latched but must meet setup and hold times relative to the write clock. All inputs must use the same clock and clock enable signals. All outputs must use the same clock and clock enable signals. Reset is common for both inputs and outputs. Table 9 shows the allowable sources for clock, clock enable, and reset for the various CAM registers.

#### Figure 13. CAM Mode

#### Table 9. Register Clocks, Clock Enables, and Initialization in CAM Mode

| Register                                                                                       | Input        | Source                                                                                                                                     |

|------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Write data, Write address,                                                                     | Clock        | CLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                          |

| Enable mask register, Write<br>enable, write chip select, and<br>write don't care, CAM Output, | Clock Enable | WE or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                          |

| Match, and Multimatch                                                                          | Reset        | Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction array from GRP, with inversion if desired |

### **Clock Distribution**

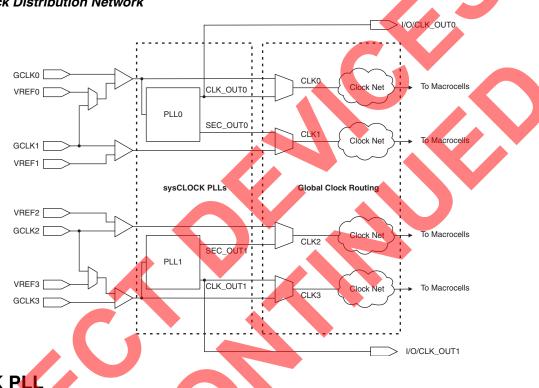

The ispXPLD 5000MX family has four dedicated clock input pins: GCLK0-GCLK3. GLCK0 and GCLK3 can be routed through a PLL circuit or routed directly to the internal clock nets. The internal clock nets (CLK0-CLK3) are directly related to the dedicated clock pins (see Secondary Clock Divider exception when using the sysCLOCK circuit). These feed the registers in the MFBs. Note at each register there is the option of inverting the clock if required. Figure 14 shows the clock distribution network.

#### Figure 14. Clock Distribution Network

### sysCLOCK PLL

The sysCLOCK PLL circuitry consists of Phase-Lock Loops (PLLs) and the various dividers, reset and feedback signals associated with the PLLs. This feature gives the user the ability to synthesize clock frequencies and generate multiple clock signals for routing within the device. Furthermore, it can generate clock signals that are deskewed either at the board level or the device level.

The ispXPLD 5000MX devices provide two PLL circuits. PLL0 receives its clock inputs from GCLK 0 and provides outputs to CLK 0 (CLK 1 when using the secondary clock). PLL1 operates with signals from GCLK 3 and CLK 3 (CLK 2 when using the secondary clock). The optional outputs CLK\_OUT can be routed to an I/O pin. The optional PLL\_LOCK output is routed into the GRP. The optional input PLL\_RST can be routed either from the GRP or directly from an I/O pin. The optional PLL\_FBK into can be routed directly from a pin. Figure 15 shows the ispXPLD 5000MX PLL block diagram. Figure 16 shows the connection of optional inputs and outputs.

#### Lattice Semiconductor

Figure 17. I/O Cell

#### Table 10. Shared PTOE Segments

| -               | Device    | MFBs Associated With Segments                                                                                          |

|-----------------|-----------|------------------------------------------------------------------------------------------------------------------------|

| ispXPL          | ) 5256MX  | (A, B, C, D) (E, F, G, H)                                                                                              |

| ispXPLE         | 0 5512MX  | (A, B, C, D) (E, F, G, H)<br>(I, J, K, L) (M, N, O, P)                                                                 |

| ispXPLE         | 0 5768MX  | (A, B, C, D) (E, F, G, H)<br>(I, J, K, L) (M, N, O, P)<br>(Q, R, S, T) (U, V, W, Z)                                    |

| <u>íspXPL</u> [ | D 51024MX | (A, B, C, D) (E, F, G, H)<br>(I, J, K, L) (M, N, O, P)<br>(Q, R, S, T) (U, V, W, Z)<br>(Y, Z, AA, AB) (AC, AD, AE, AF) |

|                 |           |                                                                                                                        |

#### sysIO Standards

Each I/O within a bank is individually configurable based on the  $V_{CCO}$  and  $V_{REF}$  settings. Some standards also require the use of an external termination voltage. Table 12 lists the sysIO standards with the typical values for  $V_{CCO}$ ,  $V_{REF}$  and  $V_{TT}$ . For more information on the sysIO capability, refer to TN1000, sysIO Usage Guidelines for Lattice Devices.

#### Table 11. Number of I/Os per Bank

| ſ | Device          | Maximum Number of I/Os per Bank (n) |

|---|-----------------|-------------------------------------|

| Ī | ispXPLD 5256MX  | 36                                  |

| Ī | ispXPLD 5512MX  | 68                                  |

| Ī | ispXPLD 5768MX  | 96                                  |

|   | ispXPLD 51024MX | 96                                  |

### Supply Current

| Symbol                                                           | Parameter                                       | Condition                                     | Min.     | Typ. <sup>3</sup> | Max. | Units |

|------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------|----------|-------------------|------|-------|

| ispXPLD                                                          | 5256                                            | 1                                             |          | 1                 | 1    |       |

|                                                                  |                                                 | V <sub>CC</sub> = 3.3V, f = 1.0MHz            |          | 26                | —    | mA    |

| I <sub>CC</sub> <sup>1,2</sup>                                   | Operating Power Supply Current                  | V <sub>CC</sub> = 2.5V, f = 1.0MHz            | _        | 26                | _    | mA    |

|                                                                  |                                                 | V <sub>CC</sub> = 1.8V, f = 1.0MHz            | _        | 16                |      | mA    |

|                                                                  |                                                 | V <sub>CCO</sub> = 3.3V, f = 1.0MHz, unloaded | —        | 4                 |      | mA    |

| I <sub>CCO</sub>                                                 | Standby Power Supply Current (per I/O Bank)     | V <sub>CCO</sub> = 2.5V, f = 1.0MHz, unloaded |          | 4                 | -    | mA    |

| 000                                                              |                                                 | $V_{CCO} = 1.8V$ , f = 1.0MHz, unloaded       |          | 3                 |      | mA    |

|                                                                  |                                                 | V <sub>CCP</sub> = 3.3V, f = 10MHz            | <b>—</b> | 11                |      | mA    |

| I <sub>CCP</sub>                                                 | PLL Power Supply Current<br>(per PLL Bank)      | V <sub>CCP</sub> = 2.5V, f = 10MHz            | - 1      | 11                |      | mA    |

|                                                                  |                                                 | V <sub>CCP</sub> = 1.8V, f = 10MHz            |          | 3                 |      | mA    |

|                                                                  |                                                 | V <sub>CCJ</sub> = 3.3V                       | —        | 1                 |      | mA    |

| I <sub>CCJ</sub> Standby IEEE 1149.1 TAP Power<br>Supply Current |                                                 | V <sub>CCJ</sub> = 2.5V                       | <b>-</b> | 1                 |      | mA    |

|                                                                  |                                                 | V <sub>CCJ</sub> = 1.8V                       | —        | 1                 |      | mA    |

| ispXPLD                                                          | 5512                                            |                                               |          |                   |      |       |

|                                                                  |                                                 | V <sub>CC</sub> = 3.3V, f = 1.0MHz            |          | 33                | -    | mA    |

| I <sub>CC</sub> <sup>1,2</sup>                                   | Operating Power Supply Current                  | V <sub>CC</sub> = 2.5V, f = 1.0MHz            |          | 33                | —    | mA    |

|                                                                  |                                                 | V <sub>CC</sub> = 1.8V, f = 1.0MHz            |          | 22                | —    | mA    |

|                                                                  |                                                 | V <sub>CCO</sub> = 3.3V, f = 1.0MHz, unloaded |          | 4                 | —    | mA    |

| I <sub>CCO</sub>                                                 | Standby Power Supply Current<br>(per I/O Bank)  | V <sub>CCO</sub> = 2.5V, f = 1.0MHz, unloaded | —        | 4                 | —    | mA    |

|                                                                  |                                                 | V <sub>CCO</sub> = 1.8V, f = 1.0MHz, unloaded | -        | 3                 | —    | mA    |

|                                                                  |                                                 | V <sub>CCP</sub> = 3.3V, f = 10MHz            | —        | 11                | —    | mA    |

| I <sub>CCP</sub>                                                 | PLL Power Supply Current<br>(per PLL Bank)      | V <sub>CCP</sub> = 2.5V, f = 10MHz            | —        | 11                | —    | mA    |

|                                                                  |                                                 | V <sub>CCP</sub> = 1.8V, f = 10MHz            | —        | 3                 | —    | mA    |

|                                                                  |                                                 | V <sub>CCJ</sub> = 3.3V                       | —        | 1                 | —    | mA    |

| I <sub>CCJ</sub>                                                 | Standby IEEE 1149.1 TAP Power<br>Supply Current | V <sub>CCJ</sub> = 2.5V                       | —        | 1                 | —    | mA    |

|                                                                  | Supply Sulform                                  | V <sub>CCJ</sub> = 1.8V                       | —        | 1                 | —    | mA    |

| ispXPLD                                                          | 5768                                            |                                               |          |                   |      |       |

|                                                                  |                                                 | V <sub>CC</sub> = 3.3V, f = 1.0MHz            | —        | 40                | —    | mA    |

| I <sub>CC</sub> <sup>1,2</sup>                                   | Operating Power Supply Current                  | V <sub>CC</sub> = 2.5V, f = 1.0MHz            | —        | 40                | —    | mA    |

|                                                                  |                                                 | V <sub>CC</sub> = 1.8V, f = 1.0MHz            | —        | 30                | —    | mA    |

|                                                                  |                                                 | $V_{CCO} = 3.3V$ , f = 1.0MHz, unloaded       | —        | 4                 | —    | mA    |

| Icco                                                             | Standby Power Supply Current (per I/O Bank)     | $V_{CCO} = 2.5V$ , f = 1.0MHz, unloaded       | —        | 4                 | —    | mA    |

|                                                                  |                                                 | V <sub>CCO</sub> = 1.8V, f = 1.0MHz, unloaded | —        | 3                 | —    | mA    |

|                                                                  |                                                 | V <sub>CCP</sub> = 3.3V, f = 10MHz            | —        | 11                | —    | mA    |

| I <sub>CCP</sub>                                                 | PLL Power Supply Current<br>(per PLL Bank)      | V <sub>CCP</sub> = 2.5V, f = 10MHz            | —        | 11                | —    | mA    |

|                                                                  |                                                 | V <sub>CCP</sub> = 1.8V, f = 10MHz            |          | 3                 |      | mA    |

|                                                                  |                                                 | $V_{CCJ} = 3.3V$                              |          | 1                 |      | mA    |

| I <sub>CCJ</sub>                                                 | Standby IEEE 1149.1 TAP Power<br>Supply Current | $V_{CCJ} = 2.5V$                              | —        | 1                 | —    | mA    |

|                                                                  |                                                 | V <sub>CCJ</sub> = 1.8V                       | _        | 1                 | —    | mA    |

### Supply Current (Continued)

| Symbol                         | Parameter                                       | Condition                               | Min.     | Typ. <sup>3</sup> | Max.     | Units |

|--------------------------------|-------------------------------------------------|-----------------------------------------|----------|-------------------|----------|-------|

| ispXPLD                        | 51024                                           | •                                       |          |                   |          |       |

|                                |                                                 | V <sub>CC</sub> = 3.3V, f = 1.0MHz      | —        | 75                | —        | mA    |

| I <sub>CC</sub> <sup>1,2</sup> | Operating Power Supply Current                  | V <sub>CC</sub> = 2.5V, f = 1.0MHz      | _        | 75                | -        | mA    |

|                                |                                                 | V <sub>CC</sub> = 1.8V, f = 1.0MHz      | _        | 55                |          | mA    |

|                                |                                                 | $V_{CCO} = 3.3V$ , f = 1.0MHz, unloaded | —        | 4                 |          | mA    |

| I <sub>CCO</sub>               | Standby Power Supply Current (per I/O Bank)     | $V_{CCO}$ = 2.5V, f = 1.0MHz, unloaded  |          | 4                 | _        | mA    |

|                                |                                                 | $V_{CCO} = 1.8V$ , f = 1.0MHz, unloaded |          | 3                 | _        | mA    |

|                                | Did Davies Oversky Overset                      | V <sub>CCP</sub> = 3.3V, f = 10MHz      |          | 11                |          | mA    |

| I <sub>CCP</sub>               | PLL Power Supply Current<br>(per PLL Bank)      | V <sub>CCP</sub> = 2.5V, f = 10MHz      | —        | 11                |          | mA    |

|                                |                                                 | V <sub>CCP</sub> = 1.8V, f = 10MHz      |          | 3                 | <b>~</b> | mA    |

|                                |                                                 | V <sub>CCJ</sub> = 3.3V                 | —        | 1                 |          | mA    |

| I <sub>CCJ</sub>               | Standby IEEE 1149.1 TAP Power<br>Supply Current | V <sub>CCJ</sub> = 2.5V                 | <b>—</b> | 1                 |          | mA    |

|                                |                                                 | V <sub>CCJ</sub> = 1.8V                 | —        |                   |          | mA    |

Device configured with 16-bit counters.

ICC varies with specific device configuration and operating frequency.

3.  $T_A = 25^{\circ}C$

# ispXPLD 5000MX Family Internal Switching Characteristics (Continued)

|                            | Base -4 -45 -5 -52 -75                                    |                                                                                                                     |       |      |       |         |         |         | ′5       |      |       |      |       |

|----------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|------|-------|---------|---------|---------|----------|------|-------|------|-------|

| Parameter                  | Description                                               | Parameter                                                                                                           | Min.  | Max. | Min.  | Max.    | Min.    | Max.    | Min.     | Max. | Min.  | Max. | Units |

| t <sub>CASC</sub>          | Additional Delay for<br>PT Cascading<br>between MFBs      |                                                                                                                     |       | 0.71 | _     | 0.80    | _       | 0.89    | _        | 0.92 | 7     | 1.33 | ns    |

| <sup>t</sup> сісомғв       | Carry Chain Delay,<br>MFB to MFB                          | _                                                                                                                   |       | 0.35 | _     | 0.39    | _       | 0.44    | -        | 0.46 | _     | 0.66 | ns    |

| tсісомс                    | Carry Chain Delay,<br>Macro-Cell to<br>Macro-Cell         | _                                                                                                                   |       | 0.10 | _     | 0.11    |         | 0.13    | -        | 0.13 | _     | 0.19 | ns    |

| t <sub>FLAG</sub>          | Routing Delay for<br>Extended Function<br>Flags           | _                                                                                                                   | _     | 2.62 | _     | 2.94    | -       | 3.27    | _        | 3.40 |       | 4.91 | ns    |

| t <sub>FLAGEXP</sub>       | Additional Flag<br>Delay when<br>Expanding Data<br>Widths | <sup>t</sup> FLAGFULL <sup>,</sup><br><sup>t</sup> FLAGAFULL,<br><sup>t</sup> FLAGEMPTY,<br><sup>t</sup> FLAGAEMPTY | _     | 2.57 |       | 2.89    | -       | 3.21    |          | 3.34 |       | 4.82 | ns    |

| t <sub>SUM</sub>           | Counter Sum Delay                                         | t <sub>PTSA</sub>                                                                                                   |       | 0.80 | -     | 0.90    | —       | 1.00    | —        | 1.04 | —     | 1.50 | ns    |

| Optional Adjus             | sters                                                     |                                                                                                                     |       |      |       |         |         |         |          |      |       |      |       |

| t <sub>BLA</sub>           | Block Loading<br>Adder                                    | t <sub>ROUTE</sub>                                                                                                  |       | 0.04 | _     | 0.04    | J       | 0.05    | -        | 0.05 | _     | 0.07 | ns    |

| t <sub>EXP</sub>           | PT Expander Adder                                         | t <sub>ROUTE</sub>                                                                                                  | 1     | 0.53 | —     | 0.60    | -       | 0.66    | —        | 0.69 | —     | 0.99 | ns    |

| t <sub>INDIO</sub>         | Additional Delay for the Input Register                   | tinneg                                                                                                              | _     | 0.50 |       | 0.56    |         | 0.63    | _        | 0.65 | _     | 0.94 | ns    |

| t <sub>PLL_SEC_DELAY</sub> | Secondary PLL<br>Output Delay                             | t <sub>PLL_DELAY</sub>                                                                                              | _     | 0.91 |       | 0.91    | -       | 0.91    | —        | 0.91 | _     | 0.91 | ns    |

| t <sub>INEXP</sub>         | MFB Input Extender                                        | t <mark>ro</mark> ute                                                                                               | _     | 0.62 |       | 0.70    | —       | 0.78    | —        | 0.81 | —     | 1.16 | ns    |

| Input and Outp             | out Buffer Delays                                         |                                                                                                                     |       |      |       |         |         |         |          |      |       |      |       |

| t <sub>IOI</sub>           | Input Buffer Selec-<br>tion Adder                         | t <sub>GCLK_IN</sub> , t <sub>IN</sub> ,<br>t <sub>GOE</sub> , t <sub>RST</sub>                                     |       |      |       | efer to | sysIO   | Adjuste | er Table | 26   |       |      | ns    |

| t <sub>IOO</sub>           | Output Buffer<br>Selection Adder                          | t <sub>BUF</sub>                                                                                                    |       |      |       |         | eyere : | rajuon  |          |      |       |      | ns    |

| FIFO                       |                                                           |                                                                                                                     |       | -    |       | -       |         | -       | -        | -    |       | -    |       |

| t <sub>FIFOWCLKS</sub>     | Write Data Setup<br>before Write Clock<br>Time            |                                                                                                                     | -0.27 | _    | -0.27 | _       | -0.22   | _       | -0.22    | _    | -0.21 | _    | ns    |

| t <sub>FIFOWCLKH</sub>     | Write Data Hold<br>after Write Clock<br>Time              |                                                                                                                     | -0.01 | _    | -0.01 | _       | -0.01   | _       | -0.01    | _    | -0.01 | _    | ns    |

| t <sub>FIFOCLKSKEW</sub>   | Opposite Clock<br>Cycle Delay                             | _                                                                                                                   |       | 1.40 | —     | 1.40    | —       | 1.76    | —        | 1.76 | —     | 1.83 | ns    |

|                            | Write Clock to Full<br>Flag Delay                         | _                                                                                                                   | _     | 3.08 | —     | 3.08    | —       | 3.85    | —        | 3.85 | —     | 4.00 | ns    |

| <sup>t</sup> FIFOAFULL     | Write Clock to<br>Almost Full Flag<br>Delay               | _                                                                                                                   |       | 3.08 | _     | 3.08    | _       | 3.86    | _        | 3.86 | _     | 4.01 | ns    |

| t <sub>FIFOEMPTY</sub>     | Read Clock to<br>Empty Flag Delay                         | _                                                                                                                   |       | 3.08 | _     | 3.08    | _       | 3.86    |          | 3.86 | _     | 4.01 | ns    |

| t <sub>FIFOAEMPTY</sub>    | Read Clock to<br>Almost Empty Flag<br>Delay               | _                                                                                                                   |       | 3.08 |       | 3.08    |         | 3.86    |          | 3.86 |       | 4.01 | ns    |

**Over Recommended Operating Conditions**

# ispXPLD 5000MX Family Internal Switching Characteristics (Continued)

| Base -4 -45 -5 -52 -75  |                                                   |           |       |      |       |      |       |      |       |      | -7    | 75   |       |

|-------------------------|---------------------------------------------------|-----------|-------|------|-------|------|-------|------|-------|------|-------|------|-------|

| Parameter               | Description                                       | Parameter | Min.  | Max. | Units |

| t <sub>PDPRWH</sub>     | R/W Hold time after<br>Clock Time                 | _         | -0.01 | —    | -0.01 | —    | -0.01 | —    | -0.01 | 6    | -0.01 | —    | ns    |

| t <sub>PDPDATAS</sub>   | Data Setup before<br>Clock Time                   | _         | -0.27 | _    | -0.27 | _    | -0.22 | —    | -0.22 | -    | -0.21 | _    | ns    |

| t <sub>PDPDATAH</sub>   | Data Hold time after<br>Clock Time                | _         | -0.01 | _    | -0.01 | _    | -0.01 |      | -0.01 |      | -0.01 | _    | ns    |

| t <sub>PDPRCLKO</sub>   | Read Clock to<br>Output Delay                     | _         | _     | 5.08 | _     | 5.02 |       | 5.66 |       | 5.45 |       | 8.54 | ns    |

| t <sub>PDPCLKSKEW</sub> | Opposite Clock<br>Cycle Delay                     | _         | 1.40  | _    | 1.40  |      | 1.76  |      | 1.76  |      | 1.83  | —    | ns    |

| t <sub>PDPRSTO</sub>    | Reset to RAM<br>Output Delay                      | _         | _     | 3.30 |       | 3.30 | _     | 4.13 |       | 4.13 | -     | 4.29 | ns    |

| t <sub>PDPRSTR</sub>    | Reset Recovery<br>Time                            | _         | 1.20  |      | 1.20  | _    | 1.50  | _    | 1.50  | -    | 1.56  | —    | ns    |

| t <sub>PDPRSTPW</sub>   | Reset Pulse Width                                 | _         | 0.14  | -    | 0.14  |      | 0.18  | -    | 0.18  |      | 0.19  | —    | ns    |

| Dual Port RAM           | 1                                                 |           |       |      |       |      |       |      |       |      |       |      |       |

| t <sub>DPMSAS</sub>     | Memory Select A<br>Setup Before R/W A<br>Time     | _         | -0.27 |      | -0.27 | _    | -0.27 | -    | -0.27 | _    | -0.21 | _    | ns    |

| t <sub>DPMSAH</sub>     | Memory Select<br>Hold time after R/W<br>A Time    |           | -0.01 | —    | -0.01 | -    | -0.01 | _    | -0.01 | _    | -0.01 | _    | ns    |

| t <sub>DPCEAS</sub>     | Clock Enable A<br>Setup before Clock<br>A Time    | <b>_</b>  | 3.72  | Ē    | 3.72  | _    | 3.72  | _    | 3.72  | _    | 4.84  | _    | ns    |

| t <sub>DPCEAH</sub>     | Clock Enable A<br>Hold time after<br>Clock A Time | _         | -2.95 | -    | -2.95 | _    | -2.95 | _    | -2.95 | _    | -2.27 | _    | ns    |

| t <sub>DPADDAS</sub>    | Address A Setup<br>before Clock A Time            |           | -0.27 |      | -0.27 | _    | -0.27 | _    | -0.27 | _    | -0.21 | _    | ns    |

| t <sub>DPADDAH</sub>    | Address A Hold<br>time after Clock A<br>Time      |           | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | ns    |

| t <sub>DPRWAS</sub>     | R/W A Setup before<br>Clock A Time                |           | -0.27 | _    | -0.27 | _    | -0.27 | —    | -0.27 | _    | -0.21 | —    | ns    |

| t <sub>DPRWAH</sub>     | R/W A Hold time<br>after Clock A Time             |           | -0.01 | —    | -0.01 | —    | -0.01 | —    | -0.01 | _    | -0.01 | —    | ns    |

| t <sub>DPDATAAS</sub>   | Write Data A Setup<br>before Clock A Time         | _         | -0.27 | _    | -0.27 | _    | -0.27 | _    | -0.27 | _    | -0.21 | _    | ns    |

| t <sub>dpdataah</sub>   | Write Data A Hold<br>time after Clock A<br>Time   | _         | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | ns    |

| t <sub>DPMSBS</sub>     | Memory Select B<br>Setup Before R/W B<br>Time     |           | -0.27 | _    | -0.27 | _    | -0.27 | _    | -0.27 | _    | -0.21 | _    | ns    |

| t <sub>DPMSBH</sub>     | Memory Select<br>Hold time after R/W<br>B Time    | _         | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | ns    |

**Over Recommended Operating Conditions**

# ispXPLD 5000MX Power Supply and NC Connections<sup>1</sup>

#### ispXPLD 5000MX Family Data Sheet

| Signals         | <b>208 PQFP</b> <sup>4</sup>                                                                                | 256 fpBGA <sup>3, 5</sup>                                                                                         | 484 fpBGA, 5 <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 672 fpBGA <sup>3, 5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC             | 10, 49, 76, 114,<br>153, 180                                                                                | D4, D13, F6, F11, L6,<br>L11, N4, N13                                                                             | A17, A6, AA2, AA21, AB17,<br>AB6, B2, B21, D19, D4, F1,<br>F22, G10, G11, G12, G13, K16,<br>K7, L16, L7, M16, M7, T10,<br>T11, T12, T13, T14, T9, U1,<br>U22, W19, W4                                                                                                                                                                                                                                                                                                                      | AA21, AA6, F21, F6, G20, G7, J13,<br>J14, K13, K14, L13, L14, M13, M14,<br>N10, N11, N12, N15, N16, N17, N18,<br>N9, P10, P11, P12, P15, P16, P17,<br>P18, P9, R13, R14, T13, T14, U13,<br>U14, V13, V14, Y20, Y7                                                                                                                                                                                                                                                                                                                                                                                           |

| VCCO0           | 5, 17, 189, 204                                                                                             | A1, F7, G6                                                                                                        | B9, C3, G8, G9, H7, J2, J7, P4                                                                                                                                                                                                                                                                                                                                                                                                                                                             | H10, H11, H8, H9, J8, J9, K8, L8, M8,<br>N8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VCCO1           | 42, 57, 72                                                                                                  | K6, L7, T1                                                                                                        | AA9, R7, T3, T8, Y3                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P8, R8, T8, U8, V8, V9, W10, W11,<br>W8, W9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VCCO2           | 85, 100, 107,<br>121                                                                                        | K11, L10, T16                                                                                                     | AA14, R16, T15, T20, Y20                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P19, R19, T19, U19, V18, V19, W12,<br>W13, W14, W15, W16, W17, W18,<br>W19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VCCO3           | 146, 161, 176                                                                                               | A16, F10, G11                                                                                                     | B14, C20, G14, G15, H16, J16,<br>J21, P19                                                                                                                                                                                                                                                                                                                                                                                                                                                  | H12, H13, H14, H15, H16, H17, H18,<br>H19, J18, J19, K19, L19, M19, N19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCCP            | 136                                                                                                         | J16                                                                                                               | M22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | N25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VCCJ            | 27                                                                                                          | J1                                                                                                                | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | N4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GND             | 15, 29, 44, 81,<br>119, 148, 185,<br>7, 19, 191, 205,<br>40, 56, 70, 87,<br>101, 109, 123,<br>144, 160, 174 | K1, C3, C14, E5, E12,<br>G7, G8, G9, G10, H7,<br>H8, H9, H10, J7, J8, J9,<br>J10, K7, K8, K9, K10,<br>M5, M12, P3 | N1, A1, A2, A21, A22, AA1,<br>AA22, AB1, AB22, B1, B22,<br>C15, C8, D11, D12, E18, E5,<br>F17, F6, G16, G7, H10, H11,<br>H12, H13, H14, H15, H20, H3,<br>H8, H9, J10, J11, J12, J13, J14,<br>J15, J8, J9, K10, K11, K12,<br>K13, K14, K15, K8, K9, L10,<br>L11, L12, L13, L14, L15, L19,<br>L4, L8, L9, M10, M11, M12,<br>M13, M14, M19, M4, M9, N10,<br>N11, N12, N13, N14, N9, P10,<br>P11, P12, P13, P14, P9, R10,<br>R11, R12, R13, R14, R15, R8,<br>R9, T16, T7, W11, W12, Y15,<br>Y8 | A11, A16, A2, A25, AE1, AE2, AE25,<br>AE26, AF11, AF16, AF2, AF25, B1,<br>B2, B25, B26, J10, J11, J12, J15, J16,<br>J17, K10, K11, K12, K15, K16, K17,<br>K18, K9, L1, L10, L11, L12, L15, L16,<br>L17, L18, L26, L9, M10, M11, M12,<br>M15, M16, M17, M18, M9, N13, N14,<br>P13, P14, R10, R11, R12, R15, R16,<br>R17, R18, R9, T1, T10, T11, T12,<br>T15, T16, T17, T18, T26, T9, U10,<br>U11, U12, U15, U16, U17, U18, U9,<br>V10, V11, V12, V15, V16, V17                                                                                                                                               |

| GNDP            | 134                                                                                                         | K16                                                                                                               | N22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NC <sup>2</sup> |                                                                                                             | A15, B2, B12, B15,<br>B16, C4, C12, C15,<br>C16, D1, D11, D14,                                                    | J17, J6, K1, K17, K18, K19, K2,<br>K20, K21, K22, K3, K4, K5, K6,<br>L1, L17, L18, L2, L20, L21, L22,                                                                                                                                                                                                                                                                                                                                                                                      | A12, A13, A14, A15, AA10, AA11,<br>AA12, AA13, AA14, AA15, AA16,<br>AA17, AA7, AB10, AB11, AB12,<br>AB13, AB14, AB15, AB16, AB17,<br>AC10, AC11, AC12, AC13, AC14,<br>AC15, AC16, AC17, AD11, AD12,<br>AD13, AD14, AD15, AD16, AE11,<br>AE12, AE13, AE14, AE15, AE16,<br>AF12, AF13, AF14, AF15, B11, B12,<br>B13, B14, B15, B16, C11, C12, C13,<br>C14, C15, C16, C3, D10, D11, D12,<br>D13, D14, D15, D16, D17, E10, E11,<br>E12, E13, E14, E15, E16, E17, E6,<br>E7, E8, F10, F11, F12, F13, F14, F15,<br>F16, F17, G10, G11, G12, G13, G14,<br>G15, G16, G17, Y10, Y11, Y12, Y13,<br>Y14, Y15, Y16, Y17 |

1. All grounds must be electrically connected at the board level.

2. NC pins should not be connected to any active signals,  $V_{CC}\, \text{or GND}.$

3. Balls for GND, V<sub>CC</sub> and V<sub>CCOX</sub> are connected within the substrate to their respective common signals. Pin orientation A1 starts from the upper left corner of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

4. Pin orientation follows the conventional counter-clockwise order from pin 1 marking of the topside view.

5. Internal GNDs and I/O GNDs (Bank 0 - Bank 3) pare connected inside package. V<sub>CCO</sub> balls connect to four power planes within the package, one each for V<sub>CCOX</sub>.

## ispXPLD 5512MX Logic Signal Connections (Continued)

| syslO | LVDS | Primary Macrocell/ | Alternate         | Outputs     | Alternate | 208 PQFP   | 256 fpBGA         | 484 fpBGA         |

|-------|------|--------------------|-------------------|-------------|-----------|------------|-------------------|-------------------|

| Bank  | Pair | Function           | Macrocell 1       | Macrocell 2 | Input     | Pin Number | Ball Number       | Ball Number       |

| 0     | 96N  | M12                | M23               | O23         | M13       | 196        | B5                | A10               |

| 0     | 96P  | M10                | M22               | O22         | M11       | 197        | A3                | A9                |

| 0     | 97N  | M8                 | M21               | O21         | M9        | 198        | B4                | C9                |

| 0     | 97P  | M6                 | M20               | O20         | M7        | 199        | B3                | D9                |

| 0     | 98N  | M5                 | M19               | O19         | —         | 200        | C5                | F9                |

| 0     | 98P  | M4                 | M18               | O18         | —         | 201        | C6                | E9                |

| 0     | 99N  | M2                 | M1                | 01          | M3        | 202        | D5                | A8                |

| —     | _    | V <sub>CCO0</sub>  | —                 |             | _         | —          | V <sub>CCO0</sub> | V <sub>CCO0</sub> |

| 0     | 99P  | MO                 | MO                | O0          | M1        | 203        | D6                | <b>B8</b>         |

|       | _    | GND (Bank 0)       | —                 | _           |           | -          | GND (Bank 0)      | GND (Bank 0)      |

| 0     | 100N | N30                | O29               | -           | N31       | <b>—</b> — |                   | A7                |

| 0     | 100P | N28                | O28               |             | N29       | —          |                   | B7                |

| 0     | 101N | N26                | 027               |             | N27       | —          |                   | A5                |

| 0     | 101P | N24                | O26               |             | N25       |            |                   | B5                |

| 0     | 102N | N22                | O25               |             | N23       |            |                   | B6                |

| 0     | 102P | N21                | O24               |             | —         | ł          | l                 | C7                |

| 0     | 103N | N20                | O23               |             |           |            |                   | E8                |

| 0     | 103P | N18                | O22               |             | N19       | —          |                   | E7                |

| 0     | 104N | N16                | O21               |             | N17       | -          |                   | E6                |

| 0     | 104P | N14                | O20               |             | N15       | <b>—</b>   | _                 | D6                |

| 0     | 105N | N12                | 019               | -           | N13       | —          | _                 | D8                |

| —     | —    | V <sub>CCO0</sub>  | —                 |             | —         | 204        | V <sub>CCO0</sub> | V <sub>CCO0</sub> |

| 0     | 105P | N10                | O18               | -           | N11       | —          | —                 | F8                |

| —     | _    | GND (Bank 0)       | —                 | -           | —         | 205        | GND (Bank 0)      | GND (Bank 0)      |

| 0     | 106N | N8                 | 0 <mark>17</mark> | _           | N9        | —          | —                 | F7                |

| 0     | 106P | N6                 | 016               |             | N7        | —          | —                 | D7                |

| 0     | 107N | N5                 | 015               | -           | —         | 206        | A2                | C6                |

| 0     | 107P | N4                 | 014               | _           | —         | 207        | B2                | C5                |

| 0     | 108N | N2                 | 013               | _           | N3        | —          | _                 | C4                |

| 0     | 108P | NO                 | 012               | —           | N1        | —          | —                 | D5                |

1. Not available for differential pair.

Global Clock LVDS pair options: GCLK0 and GCLK1, as well as GCLK2 and GCLK3, can be paired together to receive differential clocks; where GCLK0 and GCLK3 are the positive LVDS inputs.

# ispXPLD 5768MX Logic Signal Connections

|            |           | Primary Macrocell/ | Alternate   | Outputs     | Alternate | 256 fpBGA    | 484 fpBGA   |

|------------|-----------|--------------------|-------------|-------------|-----------|--------------|-------------|

| syslO Bank | LVDS Pair | Function           | Macrocell 1 | Macrocell 2 | Inputs    | Ball Number  | Ball Number |

| 0          | 127N      | S22                | S11         | T18         | S23       | C4           | B4          |

| 0          | 127P      | S20                | S10         | T16         | S21       | E4           | A4          |

| 0          | 128N      | S18                | Q17         | S17         | S19       | B1           | B3          |

| 0          | 128P      | S16                | Q16         | S16         | S17       | C1           | A3          |

| 0          | 129N      | S14                | Q15         | S15         | S15       | D3           | F5          |

| -          | -         | VCCO0              | -           | -           |           | VCCO0        | VCCO0       |

| 0          | 129P      | S12                | Q14         | S14         | S13       | C2           | G6          |

| -          | -         | GND (Bank 0)       | -           | -           | -         | GND (Bank 0) | GND (Bank 0 |

| 0          | 130N      | S10                | Q13         | S13         | S11       | E3           | H6          |

| 0          | 130P      | S8                 | Q12         | S12         | S9        | D2           | G5          |

| 0          | 131N      | S6                 | S9          | T14         | \$7       |              | D3          |

| 0          | 131P      | S4                 | S8          | T12         | S5        |              | D2          |

| 0          | 132N      | S2                 | S7          | <b>T</b> 10 | S3        |              | E4          |

| -          | -         | VCC                | -           | -           | -         | VCC          | VCC         |

| 0          | 132P      | S0                 | S6          | Т8          | S1        | —            | E3          |

| -          | -         | GND                | -           | -           |           | GND          | GND         |

| 0          | 133N      | T30                | S5          | T6          | T31       | —            | F4          |

| 0          | 133P      | T28                | S4          | T4          | T29       | —            | G4          |

| 0          | 134N      | T26                | S3          | Т2          | T27       | —            | C2          |

| -          | -         | VCCO0              | -           |             | -         | VCCO0        | VCCO0       |

| 0          | 134P      | T24                | S2          | то          | T25       | —            | C1          |

| -          | -         | GND (Bank 0)       | -           |             | -         | GND (Bank 0) | GND (Bank 0 |

| 0          | 135N      | T22                | S1          | -           | T23       | D1           | F3          |

| 0          | 135P      | T20                | S0          | -           | T21       | E1           | G3          |

| 0          | 136N      | 718                | S31         | -           | T19       | F4           | H4          |

| -          | -         | VCC                | -           | -           | -         | VCC          | VCC         |

| 0          | 136P      | T16                | S30         | -           | T17       | F5           | J4          |

| 0          | 137N      | T14                | Q11         | S11         | T15       | E2           | H5          |

| 0          | 137P      | T12/CLK_OUT0       | Q10         | S10         | T13       | F2           | J5          |

| 0          | 138N      | T10                | Q9          | S9          | T11       | F1           | E2          |

| 0          | 138P      | T8                 | Q8          | S8          | Т9        | G1           | F2          |

|            | -         | GND                | -           | -           | -         | GND          | GND         |

| 0          | 139N      | T6                 | Q7          | S7          | T7        | F3           | D1          |

| -          | -         | VCCO0              | -           | -           | -         | VCCO0        | VCCO0       |

| 0          | 139P      | T4                 | Q6          | S6          | T5        | G5           | E1          |

| -          | -         | GND (Bank 0)       | -           | -           | -         | GND (Bank 0) | GND (Bank 0 |

| 0          | 140N      | T2                 | Q5          | S5          | Т3        | H5           | J3          |

| 0          | 140P      | T0/PLL_RST0        | Q4          | S4          | T1        | G4           | H2          |

| 0          | 141N      | U30                | U31         | W31         | U31       | G3           | G2          |

| 0          | 141P      | U28/PLL_FBK0       | U30         | W30         | U29       | H3           | G1          |

| 0          | 142N      | U26                | U29         | W29         | U27       |              | J6          |

| 0          | 142P      | U24                | U28         | W28         | U25       | —            | K4          |

# ispXPLD 5768MX Logic Signal Connections (Continued)

|            |           | Primary Macrocell/ | Alternate           | Outputs     | Alternate | 256 fpBGA              | 484 fpBGA                 |

|------------|-----------|--------------------|---------------------|-------------|-----------|------------------------|---------------------------|

| syslO Bank | LVDS Pair | Function           | Macrocell 1         | Macrocell 2 | Inputs    | Ball Number            | Ball Number               |

| 0          | 143N      | U22                | U27                 | W27         | U23       |                        | K6                        |

| -          | -         | VCCO0              | -                   | -           | -         | VCCO0                  | VCCO0                     |

| 0          | 143P      | U20                | U26                 | W26         | U21       |                        | К3                        |

| -          | -         | GND (Bank 0)       | -                   | -           | -         | GND (Bank 0)           | GND (Bank 0)              |

| 0          | 144N      | U18                | U25                 | W25         | U19       | -                      | K5                        |

| 0          | 144P      | U16                | U24                 | W24         | U17       | -                      | K2                        |

| 0          | 145N      | U14                | U23                 | W23         | U15       | —                      | L5                        |

| 0          | 145P      | U12                | U22                 | W22         | U13       | —                      | K1                        |

| 0          | 146N      | U10                | U21                 | W21         | U11       | <                      | L6                        |

| 0          | 146P      | U8                 | U20                 | W20         | U9        |                        | L1                        |

| 0          | 147N      | U6                 | U19                 | W19         | U7        |                        | M5                        |

| 0          | 147P      | U4                 | U18                 | W18         | U5        | Ľ,                     | L2                        |

| 0          | 148N      | U2                 | U17                 | W17         | U3        |                        | N5                        |

| -          | -         | VCCO0              | -                   | -           | -         | VCC00                  | VCCO0                     |

| 0          | 148P      | U0                 | U16                 | W16         | U1        | -                      | L3                        |

| -          | -         | GND (Bank 0)       | <b>K</b> - <b>T</b> | -           | -         | GND (Bank 0)           | GND (Bank 0)              |

| 0          | 149N      | W30                | U15                 | W15         | W31       | —                      | M6                        |

| 0          | 149P      | W28                | U14                 | W14         | W29       | —                      | M2                        |

| 0          | 150N      | W26                | U13                 | W13         | W27       | —                      | P5                        |

| -          | -         | VCC                | -                   |             | -         | VCC                    | VCC                       |

| 0          | 150P      | W24                | U12                 | W12         | W25       | —                      | P6                        |

| 0          | 151N      | W22                | U11                 | W11         | W23       | —                      | M3                        |

| 0          | 151P      | W20                | U10                 | W10         | W21       | —                      | N6                        |

| 0          | 152N      | W18                | U9                  | W9          | W19       | —                      | N2                        |

| 0          | 152P      | W16                | U8                  | W8          | W17       |                        | P1                        |

| -          | -         | GND                | -                   | -           | -         | GND                    | GND                       |

| 0          | 153N      | W14                | U7                  | W7          | W15       | —                      | N3                        |

| -          |           | VCCOO              | -                   | -           | -         | VCCO0                  | VCCO0                     |

| 0          | 153P      | W12                | U6                  | W6          | W13       |                        | M8                        |

|            | -         | GND (Bank 0)       | -                   | -           | -         | GND (Bank 0)           | GND (Bank 0)              |

| 0          | 154N      | W10                | U5                  | W5          | W11       |                        | N8                        |

| 0          | 154P      | W8                 | U4                  | W4          | -         | —                      | P2                        |

| 0          | 155N      | W6                 | U3                  | W3          | W7        | —                      | P8                        |

| 0          | 155P      | W4                 | U2                  | W2          | W5        | —                      | N4                        |

| 0          | 156N      | W2                 | U1                  | W1          | W3        | G2                     | H1                        |

| 0          | 156P      | W0                 | U0                  | W0          | W1        | H1                     | J1                        |

| -          | GCLK0P    | GCLK0              | -                   | -           | -         | H2                     | N7                        |

| -          | -         | VCCJ               | -                   | -           | -         | See Power<br>NC Connec | Supply and<br>tions Table |

| -          | GCLK0N    | GCLK1              | -                   | -           | -         | J2                     | P7                        |

| -          | -         | GND                | -                   | -           | -         | GND                    | GND                       |

| -          | -         | TDI                | -                   | -           | -         | H6                     | R1                        |

| -          | -         | TMS                | -                   | -           | -         | H4                     | R2                        |

# ispXPLD 5768MX Logic Signal Connections (Continued)

|            |           | Primary Macrocell/ | Alternate   | Outputs     | Alternate | 256 fpBGA    | 484 fpBGA    |

|------------|-----------|--------------------|-------------|-------------|-----------|--------------|--------------|

| syslO Bank | LVDS Pair | Function           | Macrocell 1 | Macrocell 2 | Inputs    | Ball Number  | Ball Number  |

| 2          | 29N       | E2                 | F1          | H1          | E3        | T12          | AA12         |

| -          | -         | GND                | -           | -           | -         | GND          | GND          |

| 2          | 30P       | E4                 | F2          | H2          | E5        | P10          | Y12          |

| 2          | 30N       | E6                 | F3          | H3          | E7        | R10          | AA13         |

| 2          | 31P       | E8                 | F4          | H4          | E9        | R11          | V12          |

| -          | -         | VCCO2              | -           | -           |           | VCCO2        | VCCO2        |

| 2          | 31N       | E10                | F5          | H5          | E11       | M10          | U12          |

| -          | -         | GND (Bank 2)       | -           | -           | -         | GND (Bank 2) | GND (Bank 2) |

| 2          | 32P       | E12                | F6          | H6          | E13       | M11          | AB13         |

| 2          | 32N       | E14                | F7          | H7          | E15       | T13          | Y13          |

| 2          | 33P       | E16                | H0          | -           | E17       | P11          | V13          |

| 2          | 33N       | E18/VREF2          | H1          |             | E19       | T14          | W13          |

| 2          | 34P       | E20                | F8          | H8          | E21       | R12          | V14          |

| 2          | 34N       | E22                | F9          | H9          | E23       | R13          | W14          |

| 2          | 35P       | E24                | F10         | H10         | E25       | N11          | Y14          |

| 2          | 35N       | E26                | F11         | H11         | E27       | T15          | AB14         |

| 2          | 36P       | E28                | F12         | H12         | E29       | R14          | AB15         |