Welcome to E-XFL.COM

#### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### Applications of Embedded - CPLDs

#### Details

| Product Status                  | Obsolete                                                                     |

|---------------------------------|------------------------------------------------------------------------------|

| Programmable Type               | In System Programmable                                                       |

| Delay Time tpd(1) Max           | 7.5 ns                                                                       |

| Voltage Supply - Internal       | 3V ~ 3.6V                                                                    |

| Number of Logic Elements/Blocks | 24                                                                           |

| Number of Macrocells            | 768                                                                          |

| Number of Gates                 | ·                                                                            |

| Number of I/O                   | 193                                                                          |

| Operating Temperature           | 0°C ~ 90°C (TJ)                                                              |

| Mounting Type                   | Surface Mount                                                                |

| Package / Case                  | 256-BGA                                                                      |

| Supplier Device Package         | 256-FPBGA (17x17)                                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lc5768mv-75fn256c |

|                                 |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ispXPLD<sup>™</sup> 5000MX Family

3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD™ Family

#### February 2010

### Features

- Flexible Multi-Function Block (MFB) Architecture

- SuperWIDE<sup>™</sup> logic (up to 136 inputs)

- Arithmetic capability

- Single- or Dual-port SRAM

- FIFO

- Ternary CAM

### ■ sysCLOCK<sup>TM</sup> PLL Timing Control

- Multiply and divide between 1 and 32

- Clock shifting capability

- External feedback capability

### ■ sysIO<sup>™</sup> Interfaces

- LVCMOS 1.8, 2.5, 3.3V

- Programmable impedance

- Hot-socketing

- Flexible bus-maintenance (Pull-up, pulldown, bus-keeper, or none)

- Open drain operation

- SSTL 2, 3 (I & II)

- HSTL (I, III, IV)

- PCI 3.3

- GTL+

- LVDS

- LVPECL

- LVTTL

### Table 1. ispXPLD 5000MX Family Selection Guide

### ■ Expanded In-System Programmability (ispXP<sup>™</sup>)

**Data Sheet**

- Instant-on capability

- Single chip convenience

- In-System Programmable via IEEE 1532

Interface

- Infinitely reconfigurable via IEEE 1532 or sys-CONFIG<sup>™</sup> microprocessor interface

- Design security

### High Speed Operation

- 4.0ns pin-to-pin delays, 300MHz f<sub>MAX</sub>

- Deterministic timing

### Low Power Consumption

- Typical static power: 20 to 50mA (1.8V),

- 30 to 60mA (2.5/3.3V) • 1.8V core for low dynamic power

### **Easy System Integration**

- 3.3V (5000MV), 2.5V (5000MB) and 1.8V (5000MC) power supply operation

- 5V tolerant I/O for LVCMOS 3.3 and LVTTL interfaces

- IEEE 1149.1 interface for boundary scan testing

- sysIQ quick configuration

- Density migration

- Multiple density and package options

- PQFP and fine pitch BGA packaging

- · Lead-free package options

|                                                | ispXPLD 5256MX | ispXPLD 5512MX                     | ispXPLD 5768MX         | ispXPLD 51024MX        |

|------------------------------------------------|----------------|------------------------------------|------------------------|------------------------|

| Macrocells                                     | 256            | 512                                | 768                    | 1,024                  |

| Multi-Function Blocks                          | 8              | 16                                 | 24                     | 32                     |

| Maximum RAM Bits                               | 128K           | 256K                               | 384K                   | 512K                   |

| Maximum CAM Bits                               | 48K            | 96K                                | 144K                   | 192K                   |

| SySCLOCK PLLS                                  | 2              | 2                                  | 2                      | 2                      |

| t <sub>PD</sub> (Propagation Delay)            | 4.0ns          | 4.5ns                              | 5.0ns                  | 5.2ns                  |

| t <sub>S</sub> (Register Set-up Time)          | 2.2ns          | 2.8ns                              | 2.8ns                  | 3.0ns                  |

| t <sub>CO</sub> (Register Clock to Out Time)   | 2.8ns          | 3.0ns                              | 3.2ns                  | 3.7ns                  |

| f <sub>MAX</sub> (Maximum Operating Frequency) | 300MHz         | 275MHz                             | 250MHz                 | 250MHz                 |

| Functional Gates                               | 75K            | 150K                               | 225K                   | 300K                   |

| I/Os                                           | 141            | 149/193/253                        | 193/317                | 317/381                |

| Packages                                       | 256 fpBGA      | 208 PQFP<br>256 fpBGA<br>484 fpBGA | 256 fpBGA<br>484 fpBGA | 484 fpBGA<br>672 fpBGA |

<sup>© 2010</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

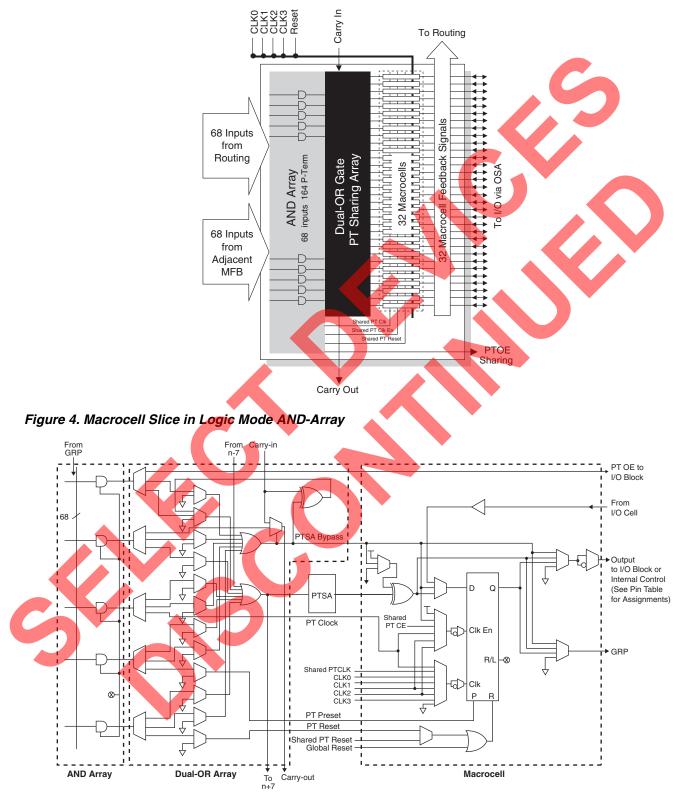

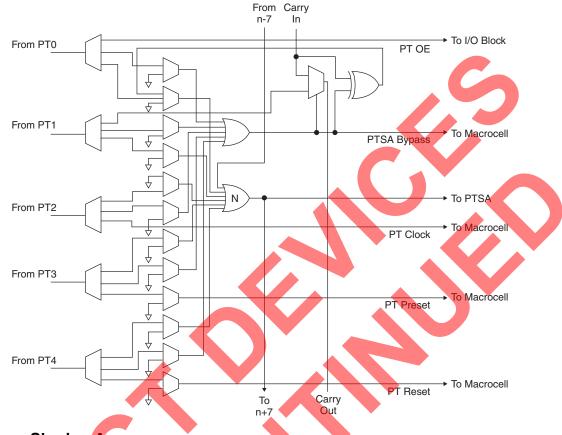

#### Figure 6. Dual-OR PT Sharing Array

### Product Term Sharing Array

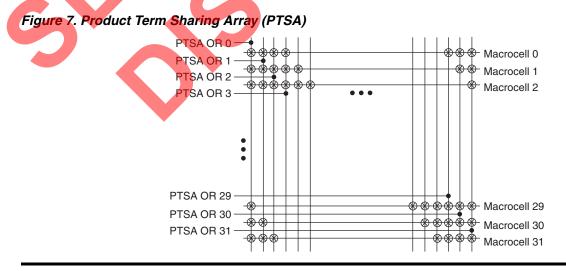

The Product Term Sharing Array (PTSA) consists of 32 inputs from the Dual-OR Array (Expandable PTSA OR) and 32 outputs directly to the macrocells. Each output is the OR term of any combination of the seven Expandable PTSA OR terms connected to that output. Every Nth macrocell is connected to N-3, N-2, N-1, N, N+1, N+2 and N+3 PTSA OR terms via a programmable connection. This wraps around the logic, for example, Macrocell 0 gets its logic from 29, 30, 31, 0, 1, 2, 3. The Expandable PTSA OR used in conjunction with the PTSA allows wide functions to be implemented easily and efficiently. Without using the Expandable PTSA OR capability, the greatest number of product terms that can be included in a single function with one pass of delay is 35. Up to 160 product terms can be included in a single function through the use of the expandable PTSA OR capability. Figure 7 shows the graphical representation of the PTSA.

### Lattice Semiconductor

### Macrocell

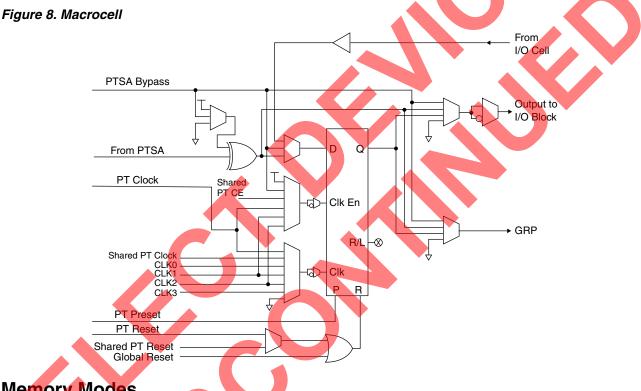

The 32 registered macrocells in the MFB are driven by the 32 outputs from the PTSA or the PTSA bypass. Each macrocell contains a programmable XOR gate, a programmable register/latch flip-flop and the necessary clocks and control logic to allow combinatorial or registered operation. All macrocells have an output that feeds the GRP. Selected macrocells have an additional output that feeds the OSA and hence I/Os. This dual or concurrent output capability from the macrocell gives efficient use of the hardware resources. One output can be a registered function for example, while the other output can be an unrelated combinatorial function. A direct register input from the I/O cell facilitates efficient use of the macrocell to construct high-speed input registers. Macrocell registers can be clocked from one of several global or product term clocks available on the device. A global and product term clock enable is also provided, eliminating the need to gate the clock to the macrocell registers directly. Reset and preset for the macrocell register is provided from both global and product term signals. The macrocell register can be programmed to operate as a D-type register or a D-type latch. Figure 8 is a graphical representation of the macrocell.

### **Memory Modes**

The ispXPLD 5000MX architecture allows the MFB to be configured as a variety of memory blocks as detailed in Table 4. The remainder of this section details operation of each of the memory modes. Additional information regarding the memory modes can also be found in TN1030, <u>Using Memory in ispXPLD 5000MX Devices</u>.

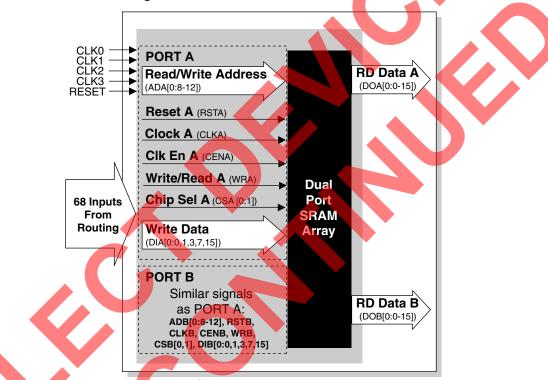

### True Dual-Port SRAM Mode

In Dual-Port SRAM Mode the multi-function array is configured as a dual port SRAM. In this mode two independent read/write ports access the same 8,192-bits of memory. Data widths of 1, 2, 4, 8, and 16 are supported by the MFB. Figure 9 shows the block diagram of the dual port SRAM.

Write data, address, chip select and read/write signals are always synchronous (registered.) The output data signals can be synchronous or asynchronous. Resets are asynchronous. All inputs on the same port share the same clock, clock enable, and reset selections. All outputs on the same port share the same clock, clock enable, and reset selections. Selections may be made independently between both inputs and outputs and ports. Table 5 shows the possible sources for the clock, clock enable and initialization signals for the various registers.

#### Figure 9. Dual-Port SRAM Block Diagram

### Table 5. Register Clock, Clock Enable, and Reset in Dual-Port SRAM Mode

| Register             | Input | Source                                                                                                           |

|----------------------|-------|------------------------------------------------------------------------------------------------------------------|

| Address, Write Data, |       | CLKA (CLKB) or one of the global clocks (CLK0 - CLK3). The selected sig-<br>nal can be inverted if desired.      |

| write, and Chip      |       | CENA (CENB) or one of the global clocks (CLK1 - CLK 2). The selected sig-<br>nal can be inverted if required.    |

| Select               | Reset | Created by the logical OR of the global reset signal and RSTA (RSTB).<br>RSTA (RSTB) can be inverted is desired. |

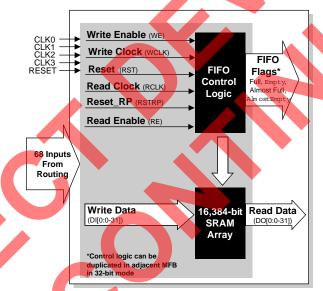

### **FIFO Mode**

In FIFO Mode the multi-function array is configured as a FIFO (First In First Out) buffer with built in control. The read and write clocks can be different or the same dependent on the application. Four flags show the status of the FIFO; Full, Empty, Almost Full, and Almost Empty. The thresholds for Full, Almost full and Almost empty are programmable by the user. It is possible to reset the read pointer, allowing support of frame retransmit in communications applications. If desired, the block can be used in show ahead mode allowing the early reading of the next read address.

In this mode one ports accesses 16,384-bits of memory. Data widths of 1, 2, 4, 8, 16 and 32 are supported by the MFB. Figure 12 shows the block diagram of the FIFO.

Write data, write enable, flag outputs and read enable are synchronous. The Write Data, Almost Full and Full share the same clock and clock enables. Read outputs are synchronous although these can be configured in look ahead mode. The Read Data, Empty and Almost Empty signals share the same clock and clock enables. Reset is shared by all signals. Table 8 shows the possible sources for the clock, clock enable and reset signals for the various registers.

### Figure 12. FIFO Block Diagram

### Table 8. Register Clocks, Clock Enables, and Initialization in FIFO Mode

| Register                           | Input           | Source                                                                                                                                      |

|------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | Clock           | WCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                          |

| Write Enable                       | Clock<br>Enable | WE or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                           |

|                                    | Reset           | N/A                                                                                                                                         |

| Full and                           | Clock           | WCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                          |

| Almost Full<br>Flags               | Clock<br>Enable | WE or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                           |

|                                    | Reset           | Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction array from GRP, with inversion if desired. |

| ,                                  | Clock           | RCLK or one of the global clocks (CLK0 - CLK3). Each of these signals can be inverted if required.                                          |

| Empty and<br>Almost Empty<br>Flags | Clock<br>Enable | RE or one of the global clocks (CLK1 - CLK 2). Each of these signals can be inverted if required.                                           |

|                                    | Reset           | Created by the logical OR of the global reset signal and RST. RST is routed by the multifunction array from GRP, with inversion if desired. |

### **Programmable Slew Rate**

The slew rate of outputs is carefully controlled. When outputs are configured as LVCMOS the devices support two slew rates. This allows system noise and performance to be balanced in a design.

### Programmable Bus-Maintenance

All general-purpose inputs have programmable bus maintenance circuitry. These are intended to maintain a valid logic level into a device when driving devices go into the tri-state mode. Four options are available for users: pull-up, pull-down, bus-keeper, or nothing.

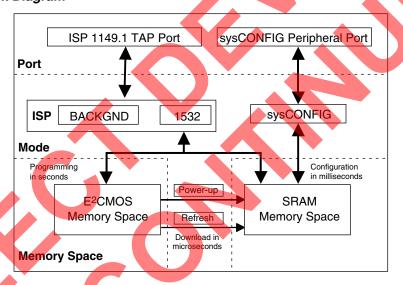

### Expanded In-System Programmability (ispXP)

The ispXPLD 5000MX family utilizes a combination of EEPROM non-volatile cells and SRAM technology to deliver a logic solution that provides "instant-on" at power-up, a convenient single chip solution, and the capability for infinite reconfiguration. A non-volatile array distributed within the device stores the device configuration. At power-up this information is transferred in a massively parallel fashion into SRAM bits that control the operation of the device. Figure 18 shows the different ports and modes that are used in the configuration and programming of the ispXPLD 5000MX devices.

### Figure 18. ispXP Block Diagram

### **IEEE 1532 ISP**

In-system programming of devices provides a number of significant benefits including rapid prototyping, lower inventory levels, higher quality and the ability to make in-field modifications. All ispXPLD 5000MX devices provide in-system programmability through their Boundary Scan Test Access Port. This capability has been implemented in a manner that ensures that the port remains compliant to the IEEE 1532 standard. By using IEEE 1532 as the communication interface through which ISP is achieved, customers get the benefit of a standard, well-defined interface.

The IEEE1532 programming interface allows programming of either the non-volatile array or reconfiguration of the SRAM bits.

The ispXPLD 5000MX devices can be programmed across the commercial temperature and voltage range. The PC-based Lattice software facilitates in-system programming of ispXPLD 5000MX devices. The software takes the JEDEC file output produced by the design implementation software, along with information about the scan chain, and creates a set of vectors used to drive the scan chain. The software can use these vectors to drive a scan chain via the parallel port of a PC. Alternatively, the software can output files in formats understood by common automated test equipment. This equipment can then be used to program ispXPLD 5000MX devices during the testing of a circuit board.

### sysCONFIG Interface

In addition to being able to program the device through the IEEE 1532 interface a microprocessor style interface (sysCONFIG interface) allows reconfiguration of the SRAM bits within the device. For more information on the sys-CONFIG capability, refer to TN1026, <u>ispXP Configuration Usage Guidelines</u>.

### **Security Scheme**

A programmable security scheme is provided on the ispXPLD 5000MX devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit prevents readback of the programmed pattern by a device programmer, securing proprietary designs from competitors. The security bit also prevents programming and verification. The entire device must be erased in order to erase the security bit.

### Low Power Consumption

The ispXPLD 5000MX devices use zero power non-volatile cells along with full CMOS design to provide low static power consumption. The 1.8V core reduces dynamic power consumption compared with devices with higher core voltages. For information on estimating power consumption, refer to TN1031 Power Estimation in ispXPLD 5000MX Devices.

### **Density Migration**

The ispXPLD 5000MX family has been designed to ensure that different density devices in the same package have compatible pin-outs. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is possible to shift a lower utilization design targeted for a high-density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

### IEEE 1149.1-Compliant Boundary Scan Testability

All ispXPLD 5000MX devices have boundary scan cells and are compliant to the IEEE 1149.1 standard. This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic notes. Internal boundary scan registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test node data to be captured and shifted out for verification. In addition, these devices can be linked into a board-level serial scan path for board-level testing. The test access port has its own supply voltage and can operate with LVCMOS3.3, 2.5 and 1.8V standards.

### sysIO Quick Configuration

To facilitate the most efficient board test, the physical nature of the I/O cells must be set before running any continuity tests. As these tests are fast, by nature, the overhead and time that is required for configuration of the I/Os' physical nature should be minimal so that board test time is minimized. The ispXPLD 5000MX family of devices allows this by offering the user the ability to quickly configure the physical nature of the sysIO cells. This quick configuration takes milliseconds to complete, whereas it takes seconds for the entire device to be programmed. Lattice's ispVM<sup>™</sup> System programming software can either perform the quick configuration through the PC parallel port, or can generate the ATE or test vectors necessary for a third-party test system.

# **DC Electrical Characteristics**

| Symbol                       | Parameter                             | Condition                                                           | Min.                    | Тур. | Max.                    | Units |

|------------------------------|---------------------------------------|---------------------------------------------------------------------|-------------------------|------|-------------------------|-------|

| I I 1                        | Input or I/O Leakage                  | 0 ð V <sub>IN</sub> ð (V <sub>CCO</sub> - 0.2V)                     | —                       |      | 10                      | μΑ    |

| $I_{IL}$ , $I_{IH}^{1}$      | Input of I/O Leakage                  | (V <sub>CCO</sub> - 0.2V) < V <sub>IN</sub> ð 3.6V                  | —                       |      | 40                      | μΑ    |

| I <sub>IH</sub> <sup>4</sup> | Input High Leakage Current            | 3.6V < V <sub>IN</sub> ð 5.5V and<br>3.0V ð V <sub>CCO</sub> ð 3.6V | -                       |      | 3                       | mA    |

| I <sub>PU</sub> <sup>3</sup> | I/O Active Pullup Current             | 0 ð V <sub>IN</sub> ð 0.7 V <sub>CCO</sub>                          | -30                     |      | -150                    | μΑ    |

| I <sub>PD</sub>              | I/O Active Pulldown Current           | V <sub>IL</sub> (MAX) ð V <sub>IN</sub> ð V <sub>IH</sub> (MAX)     | 30                      | -    | 150                     | μΑ    |

| I <sub>BHLS</sub>            | Bus Hold Low Sustaining Current       | $V_{IN} = V_{IL}$ (MAX)                                             | 30                      | -    | _                       | μΑ    |

| I <sub>BHHS</sub>            | Bus Hold High Sustaining Current      | $V_{IN} = 0.7 V_{CCO}$                                              | 30                      | _    |                         | μA    |

| I <sub>BHLO</sub>            | Bus Hold Low Overdrive Current        | 0 ð V <sub>IN</sub> ð V <sub>IH</sub> (MAX)                         |                         | —    | 150                     | μA    |

| I <sub>BHHO</sub>            | Bus Hold High Overdrive Current       | 0 ð V <sub>IN</sub> ð V <sub>IH</sub> (MAX)                         | —                       | _    | 150                     | μA    |

| V <sub>BHT</sub>             | Bus Hold Trip Points                  | 0 ð V <sub>IN</sub> ð V <sub>IH</sub> (MAX)                         | V <sub>CCO</sub> * 0.35 |      | V <sub>CCO</sub> * 0.65 | μΑ    |

| C1                           | I/O Capacitance <sup>2</sup>          | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V                                 | —                       | 8    |                         | pf    |

| 01                           |                                       | $V_{CC} = 1.8V, V_{IO} = 0 \text{ to } V_{IH} \text{ (MAX)}$        | —                       | 8    | —                       | pf    |

| C2                           | Clock Capacitance <sup>2</sup>        | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V                                 |                         | 8    | _                       | pf    |

| 02                           | Clock Capacitance                     | $V_{CC} = 1.8V, V_{IO} = 0$ to $V_{IH}$ (MAX)                       |                         | 8    | —                       | pf    |

| C3                           | Global Input Capacitance <sup>2</sup> | V <sub>CCO</sub> = 3.3V, 2.5V, 1.8V                                 | —                       | 8    | —                       | pf    |

| 00                           | Ciobal input Capacitance              | $V_{CC} = 1.8V, V_{IO} = 0$ to $V_{IH}$ (MAX)                       |                         | 8    | —                       | pf    |

#### **Over Recommended Operating Conditions**

1. Input or I/O leakage current is measured with the pin configured as an input or as an I/O with the output driver tristated. It is not measured with the output driver active. Bus maintenance circuits are disabled.

2. T<sub>A</sub> 25°C, f=1.0MHz

I<sub>PU</sub> on JTAG pins has a maximum of -175μA for 5512MX devices.

5V tolerant inputs and I/Os should be placed in banks where 3.0V δ V<sub>CCO</sub> δ 3.6V. The JTAG and sysCONFIG ports are not included for the 5V tolerant interface.

# ispXPLD 5000MX Family Internal Switching Characteristics (Continued)

|                        |                                                  | Base      |       | 4    |       | 19 00 |       | 5    | -5    | 52   | -7    | <b>'</b> 5 |       |

|------------------------|--------------------------------------------------|-----------|-------|------|-------|-------|-------|------|-------|------|-------|------------|-------|

| Parameter              | Description                                      | Parameter | Min.  | Max. | Min.  | Max.  | Min.  | Max. | Min.  | Max. | Min.  | Max.       | Units |

| t <sub>FIFOWES</sub>   | Write-Enable setup<br>before Write Clock         | _         | 2.33  |      | 2.33  | —     | 2.91  | _    | 2.91  | C    | 3.03  | —          | ns    |

| t <sub>FIFOWEH</sub>   | Write-Enable hold<br>after Write Clock           | _         | -2.95 |      | -2.95 | —     | -2.36 | _    | -2.36 | -    | -2.27 | _          | ns    |

| t <sub>FIFORES</sub>   | Read-Enable setup<br>before Read Clock           | _         | 2.69  |      | 2.35  | —     | 2.79  |      | 2.38  |      | 4.14  | _          | ns    |

| t <sub>FIFOREH</sub>   | Read-Enable hold<br>after Read Clock             | _         | -3.17 | _    | -3.17 | _     | -2.53 | —    | -2.53 | —    | -2.44 |            | ns    |

| t <sub>FIFORSTO</sub>  | Reset to Output<br>Delay                         | _         | _     | 3.30 | _     | 3.30  |       | 4.13 | _     | 4.13 |       | 4.29       | ns    |

| t <sub>FIFORSTR</sub>  | Reset Recovery<br>Time                           | _         | 1.20  | _    | 1.20  | -     | 1.50  | _    | 1.50  | -    | 1.56  |            | ns    |

| t <sub>FIFORSTPW</sub> | Reset Pulse Width                                | _         | 0.14  | -    | 0.14  |       | 0.18  | —    | 0.18  | -    | 0.19  | _          | ns    |

| t <sub>FIFORCLKO</sub> | Read Clock to FIFO<br>Out Delay                  | _         |       | 3.73 | -     | 3.73  | _     | 4.66 | -     | 4.66 | _     | 4.84       | ns    |

| CAM – Update           | Mode                                             |           |       |      |       |       |       |      |       | 7    |       |            |       |

| t <sub>CAMMSS</sub>    | Memory Select<br>Setup before CLK                | _         | 1.40  |      | 0.70  |       | 1.50  |      | 1.40  | —    | 1.44  | _          | ns    |

| t <sub>CAMMSH</sub>    | Memory Select<br>Hold after CLK                  |           | -0.01 |      | -0.01 |       | -0.01 |      | -0.01 | _    | -0.01 | _          | ns    |

| <sup>t</sup> CAMENMSKS | Enable Mask<br>Register Setup<br>Time before CLK | -         | -0.27 |      | -0.27 |       | -0.22 | _    | -0.22 | _    | -0.21 | _          | ns    |

| <sup>t</sup> CAMENMSKH | Enable Mask<br>Register Setup<br>Time after CLK  |           | -0.01 | Í    | -0.01 | -     | -0.01 | _    | -0.01 | _    | -0.01 | _          | ns    |

| t <sub>CAMADDS</sub>   | Address Setup<br>Time before Clock               | —         | -0.27 |      | -0.27 | _     | -0.22 | _    | -0.22 | _    | -0.21 | _          | ns    |

| t <sub>CAMADDH</sub>   | Address Hold Time<br>after Clock                 |           | -0.01 |      | -0.01 | —     | -0.01 | _    | -0.01 | _    | -0.01 | _          | ns    |

| <sup>t</sup> CAMDATAS  | Data Setup Time<br>before Clock                  | -         | -0.41 |      | -0.41 | —     | -0.33 | —    | -0.33 | _    | -0.31 | _          | ns    |

| <sup>t</sup> CAMDATAH  | Data Hold Time<br>after Clock                    |           | -0.01 |      | -0.01 | _     | -0.01 | —    | -0.01 | _    | -0.01 | _          | ns    |

| <sup>t</sup> CAMDCS    | "Don't Care" Setup<br>Time before Clock          |           | -0.27 |      | -0.27 | —     | -0.22 | —    | -0.22 | _    | -0.21 | _          | ns    |

| t <sub>CAMDCH</sub>    | "Don't Care" Hold<br>Time after Clock            | _         | -0.01 |      | -0.01 | —     | -0.01 | _    | -0.01 | _    | -0.01 | _          | ns    |

| t <sub>CAMRWS</sub>    | R/W Setup Time<br>before Clock                   |           | -0.27 |      | -0.27 | _     | -0.22 | _    | -0.22 | _    | -0.21 | _          | ns    |

| t <sub>CAMRWH</sub>    | R/W Enable Hold<br>Time after Clock              | _         | -0.01 |      | -0.01 | —     | -0.01 | —    | -0.01 | —    | -0.01 | —          | ns    |

| t <sub>CAMCES</sub>    | Clock Enable Setup<br>Time before Clock          | _         | 1.55  |      | 1.55  | —     | 1.94  | —    | 1.94  | —    | 2.02  | —          | ns    |

| t <sub>CAMCEH</sub>    | Clock Enable Hold<br>Time after Clock            | —         | -2.95 | —    | -2.95 | —     | -2.36 | —    | -2.36 | —    | -2.27 | —          | ns    |

**Over Recommended Operating Conditions**

# ispXPLD 5000MX Family Internal Switching Characteristics (Continued)

|                         |                                                   | Base      | -     | 4    | -4    | 15   | -     | 5    | -5    | 52   | -7    | 75   |       |

|-------------------------|---------------------------------------------------|-----------|-------|------|-------|------|-------|------|-------|------|-------|------|-------|

| Parameter               | Description                                       | Parameter | Min.  | Max. | Units |

| t <sub>PDPRWH</sub>     | R/W Hold time after<br>Clock Time                 | _         | -0.01 | —    | -0.01 | —    | -0.01 | —    | -0.01 | 6    | -0.01 | —    | ns    |

| t <sub>PDPDATAS</sub>   | Data Setup before<br>Clock Time                   | _         | -0.27 | _    | -0.27 | _    | -0.22 | —    | -0.22 | -    | -0.21 | _    | ns    |

| t <sub>PDPDATAH</sub>   | Data Hold time after<br>Clock Time                | _         | -0.01 | _    | -0.01 | _    | -0.01 |      | -0.01 |      | -0.01 | _    | ns    |

| t <sub>PDPRCLKO</sub>   | Read Clock to<br>Output Delay                     | _         | _     | 5.08 | _     | 5.02 |       | 5.66 |       | 5.45 |       | 8.54 | ns    |

| t <sub>PDPCLKSKEW</sub> | Opposite Clock<br>Cycle Delay                     | _         | 1.40  | _    | 1.40  |      | 1.76  |      | 1.76  |      | 1.83  | —    | ns    |

| t <sub>PDPRSTO</sub>    | Reset to RAM<br>Output Delay                      | _         | _     | 3.30 |       | 3.30 | _     | 4.13 |       | 4.13 | -     | 4.29 | ns    |

| t <sub>PDPRSTR</sub>    | Reset Recovery<br>Time                            | _         | 1.20  |      | 1.20  | _    | 1.50  | _    | 1.50  | -    | 1.56  | —    | ns    |

| t <sub>PDPRSTPW</sub>   | Reset Pulse Width                                 | _         | 0.14  | -    | 0.14  |      | 0.18  | -    | 0.18  |      | 0.19  | —    | ns    |

| Dual Port RAM           | 1                                                 |           |       |      |       |      |       |      |       |      |       |      |       |

| t <sub>DPMSAS</sub>     | Memory Select A<br>Setup Before R/W A<br>Time     | _         | -0.27 |      | -0.27 | _    | -0.27 | -    | -0.27 | _    | -0.21 | _    | ns    |

| t <sub>DPMSAH</sub>     | Memory Select<br>Hold time after R/W<br>A Time    |           | -0.01 | —    | -0.01 | -    | -0.01 | _    | -0.01 | _    | -0.01 | _    | ns    |

| t <sub>DPCEAS</sub>     | Clock Enable A<br>Setup before Clock<br>A Time    | <b>_</b>  | 3.72  | Ē    | 3.72  | _    | 3.72  | _    | 3.72  | _    | 4.84  | _    | ns    |

| t <sub>DPCEAH</sub>     | Clock Enable A<br>Hold time after<br>Clock A Time | _         | -2.95 | -    | -2.95 | _    | -2.95 | _    | -2.95 | _    | -2.27 | _    | ns    |

| t <sub>DPADDAS</sub>    | Address A Setup<br>before Clock A Time            |           | -0.27 |      | -0.27 | _    | -0.27 | _    | -0.27 | _    | -0.21 | _    | ns    |

| t <sub>DPADDAH</sub>    | Address A Hold<br>time after Clock A<br>Time      |           | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | ns    |

| t <sub>DPRWAS</sub>     | R/W A Setup before<br>Clock A Time                |           | -0.27 | —    | -0.27 | _    | -0.27 | —    | -0.27 | _    | -0.21 | —    | ns    |

| t <sub>DPRWAH</sub>     | R/W A Hold time<br>after Clock A Time             |           | -0.01 | —    | -0.01 | —    | -0.01 | —    | -0.01 | _    | -0.01 | —    | ns    |

| t <sub>DPDATAAS</sub>   | Write Data A Setup<br>before Clock A Time         | _         | -0.27 | _    | -0.27 | _    | -0.27 | _    | -0.27 | _    | -0.21 | _    | ns    |

| t <sub>dpdataah</sub>   | Write Data A Hold<br>time after Clock A<br>Time   | _         | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | ns    |

| t <sub>DPMSBS</sub>     | Memory Select B<br>Setup Before R/W B<br>Time     |           | -0.27 | _    | -0.27 | _    | -0.27 | _    | -0.27 | _    | -0.21 | _    | ns    |

| t <sub>DPMSBH</sub>     | Memory Select<br>Hold time after R/W<br>B Time    | _         | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | -0.01 | _    | ns    |

**Over Recommended Operating Conditions**

# sysCLOCK PLL Timing

| Symbol                                | Parameter                                            | Conditions                                                                                                             | Min      | Max      | Units |

|---------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------|----------|-------|

| t <sub>PWH</sub>                      | Input clock, high time                               | 80% to 80%                                                                                                             | 1.2      | —        | ns    |

| t <sub>PWL</sub>                      | Input clock, low time                                | 20% to 20%                                                                                                             | 1.2      | —        | ns    |

| t <sub>R</sub> , t <sub>F</sub>       | Input Clock, rise and fall time                      | 20% to 80%                                                                                                             |          | 3.0      | ns    |

| t <sub>INSTB</sub>                    | Input clock stability, cycle to cycle (peak)         |                                                                                                                        |          | +/- 250  | ps    |

| f <sub>MDIVIN</sub>                   | M Divider input, frequency range                     |                                                                                                                        | 10       | 320      | MHz   |

| f <sub>MDIVOUT</sub>                  | M Divider output, frequency range                    |                                                                                                                        | 10       | 320      | MHz   |

| f <sub>NDIVIN</sub>                   | N Divider input, frequency range                     |                                                                                                                        | 10       | 320      | MHz   |

| f <sub>NDIVOUT</sub>                  | N Divider output, frequency range                    |                                                                                                                        | 10       | 320      | MHz   |

| f <sub>VDIVIN</sub>                   | V Divider input, frequency range                     |                                                                                                                        | 100      | 400      | MHz   |

| f <sub>VDIVOUT</sub>                  | V Divider output, frequency range                    |                                                                                                                        | 10       | 320      | MHz   |

| t <sub>OUTDUTY</sub>                  | Output clock, duty cycle                             |                                                                                                                        | 40       | 60       | %     |

|                                       |                                                      | Clean reference.<br>10 MHz < f <sub>MDIVOUT</sub> < 20 MHz or<br>100MHz < f <sub>VDIVIN</sub> < 160 MHz <sup>1</sup>   | K        | +/- 250  | ps    |

| tJIT(CC)                              |                                                      | Clean reference.<br>20 MHz < f <sub>MDIVOUT</sub> < 320 MHz and<br>160MHz < f <sub>VDIVIN</sub> < 320 MHz <sup>1</sup> | -        | +/- 150  | ps    |

| <b>T</b> 2                            | Output clock, period jitter (peak)                   | Clean reference.<br>10 MHz < f <sub>MDIVOUT</sub> < 20 MHz or<br>100MHz < f <sub>VDIVIN</sub> < 160 MHz <sup>1</sup>   | _        | +/- 300  | ps    |

| T <sub>JIT(PERIOD)</sub> <sup>2</sup> | Culput clock, period jitter (peak)                   | Clean reference.<br>20 MHz < f <sub>MDIVOUT</sub> < 320 MHz and<br>160MHz < f <sub>VDIVIN</sub> < 320 MHz <sup>1</sup> | _        | +/- 150  | ps    |

| t <sub>CLK_OUT_DLY</sub>              | Input clock to CLK_OUT delay                         | Internal feedback                                                                                                      | —        | 3.0      | ns    |

| t <sub>PHASE</sub>                    | Input clock to external feedback delta               | External feedback                                                                                                      |          | 600      | ps    |

| t <sub>LOCK</sub>                     | Time to acquire phase lock after input stable        |                                                                                                                        |          | 25       | us    |

| t <sub>PLL_DELAY</sub>                | Delay increment (Lead/Lag)                           | Typical = +/- 250ps                                                                                                    | +/- 120  | +/- 550  | ps    |

| t <sub>RANGE</sub>                    | Total output delay range (lead/lag)                  |                                                                                                                        | +/- 0.84 | +/- 3.85 | ns    |

| t <sub>PLL_RSTW</sub>                 | Minimum reset pulse width                            |                                                                                                                        | —        | 1.8      | ns    |

| t <sub>CLK_IN</sub> <sup>3</sup>      | Global clock input delay                             |                                                                                                                        | —        | 1.0      | ns    |

| PLL_SEC_DELAY                         | Secondary PLL output delay (t <sub>PLL_DELAY</sub> ) |                                                                                                                        | —        | 1.5      | ns    |

Over Recommended Operating Conditions

This condition assures that the output phase jitter will remain within specification.

Accumulated jitter measured over 10,000 waveform samples.

3. Internal timing for reference only.

# ispXP sysCONFIG Port Timing Specifications

| Symbol                    | Timing Parameter                            | Min. | Max. | Units |

|---------------------------|---------------------------------------------|------|------|-------|

| sysCONFIG Write Cycle Tim | ing                                         | •    |      |       |

| t <sub>SUCS</sub>         | Input setup time of CS to CCLK rise         | 10   | —    | ns    |

| t <sub>HCS</sub>          | Hold time of CS to CCLK rise                |      |      | ns    |

| t <sub>SUWD</sub>         | Input setup time of write data to CCLK rise | 10   |      | ns    |

| t <sub>HWD</sub>          | Hold time of write data to CCLK rise        | 0    | -    | ns    |

| t <sub>PRGM</sub>         | Low time to reset device SRAM               | 5    | 50   | ns    |

| t <sub>DINIT</sub>        | INIT delay time                             | -    | 5    | ms    |

| t <sub>IODISS</sub>       | User I/O disable                            | -    | _    | ns    |

| t <sub>IOENSS</sub>       | User I/O enable                             | —    |      | ns    |

| t <sub>WH</sub>           | Write clock High pulse width                | 18   |      | ns    |

| t <sub>WL</sub>           | Write clock Low pulse width                 | 18   |      | ns    |

| f <sub>MAXW</sub>         | Write f <sub>MAX</sub>                      |      | 27   | MHz   |

| sysCONFIG Read Cycle Tim  | ing                                         |      |      |       |

| t <sub>HREAD</sub>        | Hold time of READ to CCLK rise              | 1    |      | ns    |

| t <sub>SUREAD</sub>       | Input setup time of READ High to CCLK rise  | 15   | _    | ns    |

| t <sub>RH</sub>           | READ clock high pulse width                 | 18   | —    | ns    |

| t <sub>RL</sub>           | READ clock low pulse width                  | 18   | —    | ns    |

| f <sub>MAXR</sub>         | Read f <sub>MAX</sub>                       | —    | 27   | MHz   |

| t <sub>CORD</sub>         | Clock to out for read data                  | —    | 25   | ns    |

### **Switching Test Conditions**

Figure 21 shows the output test load that is used for AC testing. The specific values for resistance, capacitance, voltage, and other test conditions are shown in Table 14.

### Figure 21. Output Test Load, LVTTL and LVCMOS Standards

Table 14. Test Fixture Required Components

| Test Condition                          | R <sub>1</sub> | R <sub>2</sub> | CL   | Timing Ref.             | V <sub>cco</sub>  |

|-----------------------------------------|----------------|----------------|------|-------------------------|-------------------|

| Default LVCMOS 1.8 I/O (L -> H, H -> L) | 106            | 106            | 35pF | V <sub>CCO</sub> /2     | 1.8V              |

|                                         |                |                |      | LVCMOS3.3 = 1.5V        | LVCMOS3.3 = 3.0V  |

| LVCMOS I/O (L -> H, H -> L)             | <b>—</b>       | _              | 35pF | $LVCMOS2.5 = V_{CCO}/2$ | LVCMOS2.5 = 2.3V  |

|                                         |                |                |      | LVCMOS1.8 = $V_{CCO}/2$ | LVCMOS1.8 = 1.65V |

| Default LVCMOS 1.8 I/O (Z -> H)         | _              | 106            | 35pF | V <sub>CCO</sub> /2     | 1.65V             |

| Default LVCMOS 1.8 I/O (Z -> L)         | 106            | —              | 35pF | V <sub>CCO</sub> /2     | 1.65V             |

| Default LVCMOS 1.8 I/O (H -> Z)         |                | 106            | 5pF  | V <sub>OH</sub> - 0.15  | 1.65V             |

| Default LVCMOS 1.8 I/O (L -> Z)         | 106            |                | 5pF  | V <sub>OL</sub> + 0.15  | 1.65V             |

Note: Output test conditions for all other interfaces are determined by the respective standards.

### ispXPLD 5000MX Family Data Sheet

| Signals         | <b>208 PQFP</b> <sup>4</sup>                                                                                | 256 fpBGA <sup>3, 5</sup>                                                                                         | 484 fpBGA, 5 <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 672 fpBGA <sup>3, 5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC             | 10, 49, 76, 114,<br>153, 180                                                                                | D4, D13, F6, F11, L6,<br>L11, N4, N13                                                                             | A17, A6, AA2, AA21, AB17,<br>AB6, B2, B21, D19, D4, F1,<br>F22, G10, G11, G12, G13, K16,<br>K7, L16, L7, M16, M7, T10,<br>T11, T12, T13, T14, T9, U1,<br>U22, W19, W4                                                                                                                                                                                                                                                                                                                      | AA21, AA6, F21, F6, G20, G7, J13,<br>J14, K13, K14, L13, L14, M13, M14,<br>N10, N11, N12, N15, N16, N17, N18,<br>N9, P10, P11, P12, P15, P16, P17,<br>P18, P9, R13, R14, T13, T14, U13,<br>U14, V13, V14, Y20, Y7                                                                                                                                                                                                                                                                                                                                                                                           |

| VCCO0           | 5, 17, 189, 204                                                                                             | A1, F7, G6                                                                                                        | B9, C3, G8, G9, H7, J2, J7, P4                                                                                                                                                                                                                                                                                                                                                                                                                                                             | H10, H11, H8, H9, J8, J9, K8, L8, M8,<br>N8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VCCO1           | 42, 57, 72                                                                                                  | K6, L7, T1                                                                                                        | AA9, R7, T3, T8, Y3                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P8, R8, T8, U8, V8, V9, W10, W11,<br>W8, W9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VCCO2           | 85, 100, 107,<br>121                                                                                        | K11, L10, T16                                                                                                     | AA14, R16, T15, T20, Y20                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P19, R19, T19, U19, V18, V19, W12,<br>W13, W14, W15, W16, W17, W18,<br>W19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VCCO3           | 146, 161, 176                                                                                               | A16, F10, G11                                                                                                     | B14, C20, G14, G15, H16, J16,<br>J21, P19                                                                                                                                                                                                                                                                                                                                                                                                                                                  | H12, H13, H14, H15, H16, H17, H18,<br>H19, J18, J19, K19, L19, M19, N19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCCP            | 136                                                                                                         | J16                                                                                                               | M22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | N25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VCCJ            | 27                                                                                                          | J1                                                                                                                | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | N4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| GND             | 15, 29, 44, 81,<br>119, 148, 185,<br>7, 19, 191, 205,<br>40, 56, 70, 87,<br>101, 109, 123,<br>144, 160, 174 | K1, C3, C14, E5, E12,<br>G7, G8, G9, G10, H7,<br>H8, H9, H10, J7, J8, J9,<br>J10, K7, K8, K9, K10,<br>M5, M12, P3 | N1, A1, A2, A21, A22, AA1,<br>AA22, AB1, AB22, B1, B22,<br>C15, C8, D11, D12, E18, E5,<br>F17, F6, G16, G7, H10, H11,<br>H12, H13, H14, H15, H20, H3,<br>H8, H9, J10, J11, J12, J13, J14,<br>J15, J8, J9, K10, K11, K12,<br>K13, K14, K15, K8, K9, L10,<br>L11, L12, L13, L14, L15, L19,<br>L4, L8, L9, M10, M11, M12,<br>M13, M14, M19, M4, M9, N10,<br>N11, N12, N13, N14, N9, P10,<br>P11, P12, P13, P14, P9, R10,<br>R11, R12, R13, R14, R15, R8,<br>R9, T16, T7, W11, W12, Y15,<br>Y8 | A11, A16, A2, A25, AE1, AE2, AE25,<br>AE26, AF11, AF16, AF2, AF25, B1,<br>B2, B25, B26, J10, J11, J12, J15, J16,<br>J17, K10, K11, K12, K15, K16, K17,<br>K18, K9, L1, L10, L11, L12, L15, L16,<br>L17, L18, L26, L9, M10, M11, M12,<br>M15, M16, M17, M18, M9, N13, N14,<br>P13, P14, R10, R11, R12, R15, R16,<br>R17, R18, R9, T1, T10, T11, T12,<br>T15, T16, T17, T18, T26, T9, U10,<br>U11, U12, U15, U16, U17, U18, U9,<br>V10, V11, V12, V15, V16, V17                                                                                                                                               |

| GNDP            | 134                                                                                                         | K16                                                                                                               | N22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NC <sup>2</sup> |                                                                                                             | A15, B2, B12, B15,<br>B16, C4, C12, C15,<br>C16, D1, D11, D14,                                                    | J17, J6, K1, K17, K18, K19, K2,<br>K20, K21, K22, K3, K4, K5, K6,<br>L1, L17, L18, L2, L20, L21, L22,                                                                                                                                                                                                                                                                                                                                                                                      | A12, A13, A14, A15, AA10, AA11,<br>AA12, AA13, AA14, AA15, AA16,<br>AA17, AA7, AB10, AB11, AB12,<br>AB13, AB14, AB15, AB16, AB17,<br>AC10, AC11, AC12, AC13, AC14,<br>AC15, AC16, AC17, AD11, AD12,<br>AD13, AD14, AD15, AD16, AE11,<br>AE12, AE13, AE14, AE15, AE16,<br>AF12, AF13, AF14, AF15, B11, B12,<br>B13, B14, B15, B16, C11, C12, C13,<br>C14, C15, C16, C3, D10, D11, D12,<br>D13, D14, D15, D16, D17, E10, E11,<br>E12, E13, E14, E15, E16, E17, E6,<br>E7, E8, F10, F11, F12, F13, F14, F15,<br>F16, F17, G10, G11, G12, G13, G14,<br>G15, G16, G17, Y10, Y11, Y12, Y13,<br>Y14, Y15, Y16, Y17 |

1. All grounds must be electrically connected at the board level.

2. NC pins should not be connected to any active signals,  $V_{CC}\, \text{or GND}.$

3. Balls for GND, V<sub>CC</sub> and V<sub>CCOX</sub> are connected within the substrate to their respective common signals. Pin orientation A1 starts from the upper left corner of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

4. Pin orientation follows the conventional counter-clockwise order from pin 1 marking of the topside view.

5. Internal GNDs and I/O GNDs (Bank 0 - Bank 3) pare connected inside package. V<sub>CCO</sub> balls connect to four power planes within the package, one each for V<sub>CCOX</sub>.

# ispXPLD 5256MX Logic Signal Connections (Continued)

|            |           | Primary Macrocell/ | Alternate   | Outputs           |                 | 256 fpBGA    |

|------------|-----------|--------------------|-------------|-------------------|-----------------|--------------|

| syslO Bank | LVDS Pair | Function           | Macrocell 1 | Macrocell 2       | Alternate Input | Ball Number  |

| 3          | 51N       | F2                 | E1          | F1                | F3              | B8           |

| 3          | 51P       | F0                 | E0          | F0                | F1              | C8           |

| 0          | 52N       | G30                | G31         | H31               | G31             | B7           |

| 0          | 52P       | G28                | G30         | H30               | G29             | A7           |

| -          | -         | GND                | -           | - •               |                 | NC           |

| 0          | 53N       | G26                | G29         | H29               | G27             | D7           |

| 0          | 53P       | G24                | G28         | H28               | G25             | C7           |

| 0          | 54N       | G22                | G27         | H2 <mark>7</mark> | G23             | B6           |

| -          | -         | VCCO0              | -           |                   | -               | VCCO0        |

| 0          | 54P       | G21                | G26         | H26               | -               | E7           |

| -          | -         | GND (Bank 0)       | -           | -                 | -               | GND (Bank 0) |

| 0          | 55N       | G20                | G25         | H25               |                 | E6           |

| 0          | 55P       | G18                | G24         | H24               | G19             | A6           |

| 0          | 56N       | G16/VREF0          | G3          | H3                | G17             | A5           |

| 0          | 56P       | G14                | G2          | H2                | G15             | A4           |

| 0          | 57N       | G12                | G23         | H23               | G13             | B5           |

| 0          | 57P       | G10                | G22         | H22               | G11             | A3           |

| 0          | 58N       | G8                 | G21         | H21               | G9              | B4           |

| 0          | 58P       | G6                 | G20         | H20               | G7              | B3           |

| 0          | 59N       | G5                 | G19         | H19               | -               | C5           |

| 0          | 59P       | G4                 | G18         | H18               | -               | C6           |

| 0          | 60N       | G2                 | G1          | H1                | G3              | D5           |

| 0          | 60P       | GO                 | GO          | H0                | G1              | D6           |

| -          | -         | VCC00              | -           | -                 | -               | VCCO0        |

| -          | -         | GND (Bank 0)       |             | -                 | -               | GND (Bank 0) |

Global Clock LVDS pair options: GCLK0 and GCLK1, as well as GCLK2 and GCLK3, can be paired together to receive differential clocks; where GCLK0 and GCLK3 are the positive LVDS inputs

# ispXPLD 5768MX Logic Signal Connections (Continued)

| syslO Bank | LVDS Pair | Primary Macrocell/<br>Function | Alternate Outputs |             | Alternate | 256 fpBGA    | 484 fpBGA    |

|------------|-----------|--------------------------------|-------------------|-------------|-----------|--------------|--------------|

|            |           |                                | Macrocell 1       | Macrocell 2 | Inputs    | Ball Number  | Ball Number  |

| -          | -         | VCC                            | -                 | -           | -         | VCC          | VCC          |

| 0          | 109P      | Q28                            | Q30               | S30         | Q29       | A7           | C11          |

| -          | -         | GND                            | -                 | -           | -         | GND          | GND          |

| 0          | 110N      | Q26                            | Q29               | S29         | Q27       | D7           | B11          |

| 0          | 110P      | Q24                            | Q28               | S28         | Q25       | C7           | A11          |

| 0          | 111N      | Q22                            | Q27               | S27         | Q23       | B6           | F11          |

| -          | -         | VCCO0                          | -                 | -           | -         | VCCO0        | VCCO0        |

| 0          | 111P      | Q20                            | Q26               | S26         | Q21       | E7           | F10          |

| -          | -         | GND (Bank 0)                   | -                 | -           |           | GND (Bank 0) | GND (Bank 0) |

| 0          | 112N      | Q18                            | Q25               | S25         | Q19       | E6           | E10          |

| 0          | 112P      | Q16                            | Q24               | S24         | Q17       | A6           | C10          |

| 0          | 113N      | Q14/VREF0                      | Q3                | S3          | Q15       | A5           | D10          |

| 0          | 113P      | Q12                            | Q2                | S2          | Q13       | A4           | B10          |

| 0          | 114N      | Q10                            | Q23               | S23         | Q11       | B5           | A10          |

| 0          | 114P      | Q8                             | Q22               | S22         | Q9        | A3           | A9           |

| 0          | 115N      | Q6                             | Q21               | S21         | Q7        | B4           | C9           |

| 0          | 115P      | Q4                             | Q20               | S20         | Q5        | B3           | D9           |

| 0          | 116N      | Q2                             | Q19               | S19         | Q3        | C5           | F9           |

| 0          | 116P      | Q0                             | Q18               | S18         | Q1        | C6           | E9           |

| 0          | 117N      | R30                            | Q1                | S1          | R31       | D5           | A8           |

| -          | -         | VCCO0                          | -                 |             | -         | VCCO0        | VCCO0        |

| 0          | 117P      | R28                            | Q0                | <b>S</b> 0  | R29       | D6           | B8           |

| -          | -         | GND (Bank 0)                   | -                 | -           | -         | GND (Bank 0) | GND (Bank 0  |

| 0          | 118N      | R26                            | S29               | -           | R27       | —            | A7           |

| 0          | 118P      | R24                            | S28               | -           | R25       | —            | B7           |

| 0          | 119N      | R22                            | S27               | -           | R23       | —            | A5           |

| 0          | 119P      | R20                            | S26               | -           | R21       | —            | B5           |

| 0          | 120N      | R18                            | S25               | -           | R19       | —            | B6           |

| 0          | 120P      | R16                            | S24               | -           | R17       | —            | C7           |

| 0          | 121N      | R14                            | S23               | -           | R15       | —            | E8           |

| 0          | 121P      | R12                            | S22               | -           | R13       | —            | E7           |

| 0          | 122N      | R10                            | S21               | -           | R11       | —            | E6           |

|            | -         | VCC                            | -                 | -           | -         | VCC          | VCC          |

| 0          | 122P      | R8                             | S20               | -           | R9        | —            | D6           |

| -          | -         | GND                            | -                 | -           | -         | GND          | GND          |

| 0          | 123N      | R6                             | S19               | -           | R7        | —            | D8           |

| -          | -         | VCCO0                          | -                 | -           | -         | VCCO0        | VCCO0        |

| 0          | 123P      | R4                             | S18               | -           | R5        | —            | F8           |

| -          | -         | GND (Bank 0)                   | -                 | -           | -         | GND (Bank 0) | GND (Bank 0) |

| 0          | 124N      | R2                             | S17               | -           | R3        |              | F7           |

| 0          | 124P      | R0                             | S16               | -           | R1        |              | D7           |

| 0          | 125N      | S30                            | S15               | -           | S31       | A2           | C6           |

| 0          | 125P      | S28                            | S14               | -           | S29       | B2           | C5           |

# ispXPLD 51024MX Logic Signal Connections (Continued)

| syslO<br>Bank | LVDS Pair | Primary<br>Macrocell/Function | Alternate Outputs |             | Alternate | 484 fpBGA    | 672 fpBGA    |

|---------------|-----------|-------------------------------|-------------------|-------------|-----------|--------------|--------------|

|               |           |                               | Macrocell 1       | Macrocell 2 | Input     | Ball Number  | Ball Number  |

| -             | GCLK3P    | GCLK3                         | -                 | -           | -         | N16          | N24          |

| 3             | 93N       | R0                            | T31               | R31         | R1        | J22          | N23          |

| 3             | 93P       | R2                            | T30               | R30         | R3        | H22          | N22          |

| 3             | 94N       | R4                            | T29               | R29         | R5        | N19          | M26          |

| 3             | 94P       | R6                            | T28               | R28         | R7        | P15          | M25          |

| 3             | 95N       | R8                            | T27               | R27         | R9        | P21          | M23          |

| 3             | 95P       | R10                           | T26               | R26         | R11       | N15          | M22          |

| -             | -         | GND (Bank 3)                  | -                 | -           | - 1       | GND (Bank 3) | GND (Bank 3) |

| 3             | 96N       | R12                           | T25               | R25         | R13       | M15          | N20          |

| -             | -         | VCCO3                         | -                 | -           | -         | VCCO3        | VCCO3        |

| 3             | 96P       | R14                           | T24               | R24         | R15       | N20          | M20          |

| -             | -         | GND                           | -                 |             | -         | GND          | GND          |

| 3             | 97N       | R16                           | T23               | R23         | R17       | P22          | N21          |

| 3             | 97P       | R18                           | T22               | R22         | R19       | N21          | M21          |

| 3             | 98N       | R20                           | T21               | R21         | R21       | N17          | M24          |

| 3             | 98P       | R22                           | T20               | R20         | R23       | M20          | L24          |

| 3             | 99N       | R24                           | T19               | R19         | R25       | P17          | L23          |

| -             | -         | VCC                           |                   | -           |           | VCC          | VCC          |

| 3             | 99P       | R26                           | T18               | R18         | R27       | P18          | L22          |

| 3             | 100N      | R28                           | T17               | R17         | R29       | M21          | L25          |

| 3             | 100P      | R30                           | T16               | R16         | R31       | M17          | K26          |

| -             | -         | GND (Bank 3)                  | -                 | -           | -         | GND (Bank 3) | GND (Bank 3) |

| 3             | 101N      | то                            | T15               | R15         | T1        | L20          | K25          |

| -             | -         | VCCO3                         |                   | -           | -         | VCCO3        | VCCO3        |

| 3             | 101P      | Т2                            | T14               | R14         | Т3        | N18          | K24          |

| 3             | 102N      | T4                            | T13               | R13         | T5        | L21          | K23          |

| 3             | 102P      | Т6                            | T12               | R12         | T7        | M18          | K22          |

| 3             | 103N      | Т8                            | T11               | R11         | Т9        | L22          | J25          |

| 3             | 103P      | T10                           | T10               | R10         | T11       | L17          | J24          |

| 3             | 104N      | T12                           | Т9                | R9          | T13       | K22          | L21          |

| 3             | 104P      | T14                           | Т8                | R8          | T15       | L18          | K21          |

| 3             | 105N      | T16                           | T7                | R7          | T17       | K21          | L20          |

| 3             | 105P      | T18                           | Т6                | R6          | T19       | K18          | K20          |

| -             | -         | GND (Bank 3)                  | -                 | -           | -         | GND (Bank 3) |              |

| 3             | 106N      | T20                           | T5                | R5          | T21       | K20          | J23          |

| -             | -         | VCCO3                         | -                 | -           | -         | VCCO3        | VCCO3        |

| 3             | 106P      | T22                           | T4                | R4          | T23       | K17          | J22          |

| 3             | 107N      | T24                           | Т3                | R3          | T25       | K19          | J26          |

| 3             | 107P      | T26                           | T2                | R2          | T27       | J17          | H26          |

| 3             | 108N      | T28                           | T1                | R1          | T29       | E22          | H25          |

| 3             | 108P      | T30/PLL_FBK1                  | T0                | R0          | T31       | E21          | H24          |

| 3             | 109N      | U0/PLL_RST1                   | X27               | V27         | U1        | G22          | H23          |

| 3             | 109P      | U2                            | X26               | V26         | U3        | F21          | H22          |

# ispXPLD 51024MX Logic Signal Connections (Continued)

|               |           | Duin                          | Alternate Outputs |             | A 11 1 .           | 404 6-004                | 670 (- 0.0.1             |

|---------------|-----------|-------------------------------|-------------------|-------------|--------------------|--------------------------|--------------------------|

| syslO<br>Bank | LVDS Pair | Primary<br>Macrocell/Function | Macrocell 1       | Macrocell 2 | Alternate<br>Input | 484 fpBGA<br>Ball Number | 672 fpBGA<br>Ball Number |