Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 8x8b; D/A 1x8b                                                         |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc782t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### **PROGRAM MEMORY READ** 4.0 (PMR)

Program memory is readable during normal operation (full VDD range). It is read by indirect addressing through the following Special Function Registers:

- PMCON1: Control

- · PMDATH: Data High

- PMDATL: Data Low

- PMADRH: Address High

- PMADRL: Address Low

When interfacing to the program memory block, the PMDATH and PMDATL registers form a 2-byte word, which holds the 14-bit data. The PMADRH and PMADRL registers form a 2-byte word, which holds the 12-bit address of the program memory location being accessed. Mid-range devices have up to 8K words of program EPROM with an address range from 0h to 3FFFh. When the device contains less memory than the full address range of the PMADRH: PMARDL registers, the Most Significant bits of the PMADRH register are ignored.

#### 4.1 PMCON1 Register

PMCON1 is the control register for program memory accesses.

Control bit RD initiates a read operation. This bit cannot be cleared, only set, in software. It is cleared in hardware at completion of the read operation.

#### 4.2 PMDATH and PMDATL Registers

The PMDATH: PMDATL registers are loaded with the contents of program memory addressed by the PMADRH and PMADRL registers upon completion of a Program Memory Read command.

#### **REGISTER 4-1:** PROGRAM MEMORY READ CONTROL REGISTER 1 (PMCON1: 18Ch)

|         | R-1                          | U-0         | U-0        | U-0          | U-0          | U-0         | U-0          | R/S-0 |

|---------|------------------------------|-------------|------------|--------------|--------------|-------------|--------------|-------|

|         | Reserved                     | —           | —          | —            | _            | —           | —            | RD    |

|         | bit7                         |             | ·          |              |              |             |              | bit0  |

| bit 7   | Reserved: F                  | Read as '1' |            |              |              |             |              |       |

| bit 6-1 | Unimplemen                   | ted: Read   | d as '0    |              |              |             |              |       |

| bit 0   | RD: Read C                   | ontrol bit  |            |              |              |             |              |       |

|         | 1 = Initiates<br>0 = Reserve | 0           | memory rea | ad (read tak | es 2 cycles, | RD is clear | ed in hardwa | are)  |

|         | Legend:                      |             |            |              |              |             |              |       |

|         | U U                          |             |            |              |              |             |              |       |

|         | S = Settable                 | bit         |            |              |              |             |              |       |

| : | S = Settable bit   |                  |                      |                    |

|---|--------------------|------------------|----------------------|--------------------|

|   | R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

|   | - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### **REGISTER 4-2:** PROGRAM MEMORY DATA HIGH (PMDATH: 10Eh)

- n = Value at POR

|         | U-0                        | U-0       | R/W-0      | R/W-0       | R/W-0      | R/W-0      | R/W-0          | R/W-0        |

|---------|----------------------------|-----------|------------|-------------|------------|------------|----------------|--------------|

|         | —                          | —         | PMD13      | PMD12       | PMD11      | PMD10      | PMD9           | PMD8         |

|         | bit7                       |           |            |             |            |            |                | bit0         |

| bit 7-6 | Unimpleme                  | nted: Rea | d as '0    |             |            |            |                |              |

| bit 5-0 | PMD<13:8>                  | : Program | Memory Dat | ta bits     |            |            |                |              |

|         | The value of<br>memory rea | 1 0       |            | word pointe | d to by PM | ADRH and F | MADRL afte     | er a program |

|         | Т                          |           |            |             |            |            |                |              |

|         | Legend:                    |           |            |             |            |            |                |              |

|         | R = Readab                 | le bit    | W = W      | ritable bit | U = Unii   | mplemented | l bit, read as | '0'          |

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

### 6.2 Control Register T1CON

Control and configuration of Timer1 is by means of the T1CON register shown in Register 6-1.

Timer1 is enabled by setting the TMR1ON bit (T1CON<0>). Clearing TMR1ON stops the timer, but does not clear the Timer1 register.

The TMR1CS bit (T1CON<1>) determines the Timer mode. When TMR1CS is set, the timer is configured as a counter and receives its clock from RA6/OSC2/ CLKOUT/T1CKI. When cleared, the timer is configured as a timer and its clock is derived from FoSC/4.

The T1SYNC bit (T1CON<2>) determines Timer1's synchronization. If cleared, the timer clock is synchronized to the system clock. If set, the timer is asynchronous.

The Timer1 clock gate function is enabled by setting the TMR1GE bit (T1CON<6>). When TMR1GE is set, the T1G input will control the clock input to the timer/ counter. A low on the T1G input will cause Timer1 to increment at the clock rate, a high will hold the timer at its present value.

The T1OSCEN bit (T1CON<3>) enables the LP oscillator as a clock source for Timer1. This mode is a replacement for the regular external oscillator. T1CKPS<1:0> determines the prescaler value for the timer. Available prescaler values are:

| T1CKP | 'S<1:0> | Prescaler Value |  |  |  |  |

|-------|---------|-----------------|--|--|--|--|

| Bit 1 | Bit 0   |                 |  |  |  |  |

| 1     | 1       | 1:8             |  |  |  |  |

| 1     | 0       | 1:4             |  |  |  |  |

| 0     | 1       | 1:2             |  |  |  |  |

| 0     | 0       | 1:1             |  |  |  |  |

Note: To use the LP oscillator as the Timer1 oscillator:

- 1. TMR1CS must be set.

- 2. T1OSCEN must be set.

- The Configuration Word must select INTRC w/o CLKOUT.

NOTES:

#### 8.2 Operation

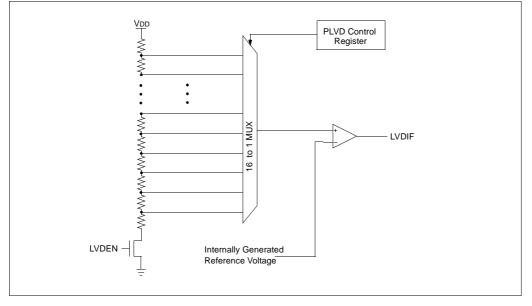

The PLVD indicates a low voltage condition by setting the LVDIF bit in the PIR1 register. Once set by the PLVD module, the LVDIF bit will remain set until cleared by software. For proper indication of a low voltage condition, the user should clear this bit prior to testing.

To test for a low voltage condition, the PLVD module compares the divided output of VDD against an internal bandgap reference. The PLVD module automatically enables this reference whenever it is enabled and provides a stability bit, BGST, to indicate when it has stabilized. The bandgap reference is also enabled by other modules within the PIC16C781/782 as part of their operation. Other modules using the bandgap include the following:

- VR module

- · BOR module

- · OPA calibration module

#### 10.3 DAC Configuration

Example 10-1 shows a sample configuration for the DAC module. The port pin is configured, AVDD is selected for the voltage reference, and the DAC output is enabled.

#### EXAMPLE 10-1: DAC CONFIGURATION

```

;* This code block will configure the DAC

```

;\* for AVDD Voltage Ref, and RB1/AN5/VDAC as

;\* output.

```

BANKSEL TRISB

; Select bank 1

TRISB,1

; Set RB1 input

BSF

BSF

ANSEL,1

; Set RB1 as analog

BANKSEL DACON0

; Select Bank 2

CLRF

DAC

; DAC to 00

MOVLW B'11000000'

; Enable DAC output

MOVWF DACON0

; Set REF = VDD

MOVLW

DAC_VALUE

MOVWF

DAC

; Set DAC output

```

#### 10.4 Effects of RESET

A device RESET forces all registers to their RESET state. This forces the following conditions:

- · DAC module is off

- · Reference input to AVDD

- · Output disabled

- · DAC register is cleared

#### 10.5 DAC Module Accuracy/Error

The accuracy/error specified for the DAC includes:

- · Integral non-linearity error

- Differential non-linearity error

- · Gain error

- Offset error

- Monotonicity

# FIGURE 10-2: DAC TRANSFER FUNCTION

03h

02h 01h

00h

2 LSb 3 LSb 4 LSb

Offset error measures the first actual transition of a code versus the first ideal transition of a code. Offset error shifts the entire transfer function. Offset error can be calibrated out of a system or introduced into a system through the interaction of the output drive capability with the load impedance.

Analog Output Voltage

256 LSb full scale)

255 LSb

Gain error measures the maximum deviation of the last actual transition and the last ideal transition adjusted for offset error. This error appears as a change in slope of the transfer function. The difference in gain error to full scale error is that full scale does not take offset error into account. Gain error can be calibrated out by adjusting the reference voltage.

Linearity error refers to the uniformity of the voltage change with code change. Linearity errors cannot be calibrated out of the system. **Integral non-linearity error** measures the actual voltage output versus the ideal voltage output adjusted by the gain error for each code.

**Differential non-linearity error** measures the maximum actual voltage step versus the ideal voltage step. This measure is unadjusted.

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on<br>All Other<br>RESETS |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------------|

| 11Fh    | DACON0 | DAON  | DAOE  |       | —     |       | _     | DARS1 | DARS0 | 0000                     | 0000                            |

| 11Eh    | DAC    | DA7   | DA6   | DA5   | DA4   | DA3   | DA2   | DA1   | DA0   | 0000 0000                | 0000 0000                       |

| 86h     | TRISB  | RB7   | RB6   | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | 1111 1111                | 1111 1111                       |

| 9Dh     | ANSEL  | AN7   | AN6   | AN5   | AN4   | AN3   | AN2   | AN1   | AN0   | 1111 1111                | 1111 1111                       |

#### TABLE 10-1: REGISTERS/BITS ASSOCIATED WITH DAC

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for DAC conversion.

#### 11.2 Configuration as OPAMP or Comparator

The following example demonstrates calibration of the OPA module as an Operational Amplifier.

#### EXAMPLE 11-1: CALIBRATION FOR OPAMP MODE

- ;\* This code block will configure the OPA

- ;\* module as an Op Amp, 2 MHz GBWP, and

- ;\* calibrated for a common mode voltage of

- ;\* 1.2V. Routine returns w=0 if

- ;\* calibration good.

| BANKSEL<br>MOVLW<br>MOVWF | B'10000001' ;                   | Select Bank 2<br>Op Amp mode &<br>2 MHz GBWP |

|---------------------------|---------------------------------|----------------------------------------------|

| BCF<br>BSF                | CALCON, CALREF;<br>CALCON, CAL; |                                              |

| CAL_LOOP<br>BTFSC         | CALCON, CAL ;                   | Test for end                                 |

| GOTO<br>MOVLW             | CAL_LOOP ;<br>ERROR_FLAG        | If not, wait                                 |

| BTFSS<br>CLRW<br>RETURN   |                                 | Test for error<br>If no, return 0            |

The following example demonstrates how to configure and calibrate the OPA module as a Voltage Comparator.

#### EXAMPLE 11-2: CALIBRATION FOR COMPARATOR MODE

- ;\* This code block will configure the OPA

- ;\* module as a voltage comparator, slow

- ;\* speed, and calibrated for a common mode

- ;\* voltage of 2.5 V (assumes VDD=5V).

- ;\* Routine returns w=0 if calibration good.

|     | BANKSEL<br>MOVLW | OPACON<br>B'10000000' | ; | Select Bank 2        |

|-----|------------------|-----------------------|---|----------------------|

|     | MOVWF            | OPACON                |   | Op Amp mode,<br>slow |

|     | BSF              | CALCON, CALREF        | ; | Common mode=DAC      |

|     | MOVLW            | H'0x80'               |   |                      |

|     | MOVWF            | DAC                   | ; | DAC at VDD/2         |

|     | MOVLW            | B'10000000'           |   |                      |

|     | MOVWF            | DACON0                | ; | enable DAC,          |

|     |                  |                       | ; | VDD ref              |

|     | BSF              | CALCON, CAL           | ; | Start                |

| CAL | LOOP             |                       |   |                      |

|     | BTFSC            | CALCON, CAL           | ; | Test for end         |

|     | GOTO             | CAL_LOOP              | ; | If not, wait         |

|     | MOVLW            | EDDOD ELAC            |   |                      |

|     |                  | ERROR_FLAG            |   |                      |

|     | BTFSS            | CALCON, CALERR        |   | Test for error       |

|     | CLRW             |                       | ; | If no, return O      |

|     | BSF              | OPACON, CMPEN         | ; | Comparator mode      |

|     | RETURN           |                       |   |                      |

|     |                  |                       |   |                      |

#### 11.3 Effects of RESET

A device RESET forces all registers to their RESET state. This disables the OPA module and clears any calibration.

#### 11.4 OPA Module Performance

Common AC and DC performance specifications for the OPA module:

- Common Mode Voltage Range

- Leakage Current

- · Input Offset Voltage

- · Open Loop Gain

- · Gain Bandwidth Product

**Common mode voltage range** is the specified voltage range for the OPA+ and OPA- inputs, for which the OPA module will perform to within its specifications. The OPA module is designed to operate with input voltages between 0 and VDD-1.4V. Behavior for Common mode voltages greater than VDD-1.4V, or below 0V, are not guaranteed.

Leakage current is a measure of the small source or sink currents on the OPA+ and OPA- inputs. To minimize the effect of leakage currents, the effective impedances connected to the OPA+ and OPA- inputs should be kept as small as possible and equal.

Input offset voltage is a measure of the voltage difference between the OPA+ and OPA- inputs in a closed loop circuit with the OPA in its linear region. The offset voltage will appear as a DC offset in the output equal to the input offset voltage, multiplied by the gain of the circuit. The input offset voltage is also affected by the Common mode voltage. The OPA has an automatic calibration module which can minimize the input offset voltage of the module.

**Open loop gain** is the ratio of the output voltage to the differential input voltage, (OPA+) - (OPA-). The gain is greatest at DC and falls off with frequency.

**Gain Bandwidth Product** or GBWP is the frequency at which the open loop gain falls off to 0 dB. The lower GBWP is optimized for systems requiring low frequency response and low power consumption.

#### 12.3 Effects of RESET

A RESET forces all registers to their RESET state. This disables both comparators.

| Address | Name    | Bit 7    | Bit 6        | Bit 5     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|---------|----------|--------------|-----------|-------|-------|-------|-------|--------|-----------------------|---------------------------------|

| 119h    | CM1CON0 | C10N     | C10UT        | C10E      | C1POL | C1SP  | C1R   | C1CH1 | C1CH0  | 0000 0000             | 0000 0000                       |

| 11Ah    | CM2CON0 | C2ON     | C2OUT        | C2OE      | C2POL | C2SP  | C2R   | C2CH1 | C2CH0  | 0000 0000             | 0000 0000                       |

| 11Bh    | CM2CON1 | MC1OUT   | MC2OUT       | _         | —     | _     |       | —     | C2SYNC | 000                   | 000                             |

| 85h     | TRISA   | PORTA Da | ata Directio | n Registe | ər    |       |       |       |        | 1111 1111             | 1111 1111                       |

| 86h     | TRISB   | PORTB Da | ata Directio | n Regist  | er    |       |       |       |        | 1111 1111             | 1111 1111                       |

| 05h     | PORTA   | RA7      | RA6          | RA5       | RA4   | RA3   | RA2   | RA1   | RA0    | xxxx 0000             | uuuu 0000                       |

| 06h     | PORTB   | RB7      | RB6          | RB5       | RB4   | RB3   | RB2   | RB1   | RB0    | xxxx 0000             | uuuu 0000                       |

| 9Dh     | ANSEL   | AN7      | AN6          | AN5       | AN4   | AN3   | AN2   | AN1   | AN0    | 1111 1111             | 1111 1111                       |

| 0Ch     | PIR1    | LVDIF    | ADIF         | C2IF      | C1IF  | _     | _     | _     | TMR1ON | 00000                 | 00000                           |

| 8Ch     | PIE1    | LVDIE    | ADIE         | C2IE      | C1IE  | _     | _     | —     | TMR1IE | 00000                 | 00000                           |

#### TABLE 12-2: REGISTERS ASSOCIATED WITH THE COMPARATOR MODULE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for comparator.

## REGISTER 14-1: CONFIGURATION WORD FOR PIC16C781/782 DEVICE (CONFIG:2007h)

| CP CP             | BORV1 BORV                                                                        | 0 <u>CP</u>                                                                                                                                                | CP       | _                    | BODEN                  | MCLRE     | PWRTE | WDTE    | F0SC2     | F0SC1 | F0SC0 |

|-------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|------------------------|-----------|-------|---------|-----------|-------|-------|

| bit13             | Bolter Bolte                                                                      | 0 0.                                                                                                                                                       | 01       |                      | BODEN                  | MOLINE    |       | IID I E | 10002     | 10001 | bit0  |

| birro             |                                                                                   |                                                                                                                                                            |          |                      |                        |           |       |         |           |       | Ditto |

| bit 13-12,<br>9-8 | <b>CP:</b> Program M<br>1 = Code Prote<br>0 = All program                         | ction off                                                                                                                                                  |          |                      |                        |           |       |         |           |       |       |

| bit 11-10         | BORV<1:0>: Bo<br>00 = PBOR set<br>01 = PBOR set<br>10 = PBOR set<br>11 = PBOR set | to 4.5V<br>to 4.2V<br>to 2.7V                                                                                                                              | Reset V  | /oltage              | e bits                 |           |       |         |           |       |       |

| bit 7             | Unimplemente                                                                      | d: Read a                                                                                                                                                  | as '1'   |                      |                        |           |       |         |           |       |       |

| bit 6             | BODEN: Brown<br>1 = Brown-out I<br>0 = Brown-out I                                | Detect Re                                                                                                                                                  | eset ena | bled                 | ble bit <sup>(1)</sup> |           |       |         |           |       |       |

| bit 5             | $1 = RA5 \overline{MCLR}$                                                         | <b>ICLRE:</b> RA5/MCLR Pin Function Select bit<br>= RA5/MCLR pin function is MCLR<br>= RA5/MCLR pin function is digital input, MCLR internally tied to VDD |          |                      |                        |           |       |         |           |       |       |

| bit 4             | <b>PWRTE</b> : Power<br>1 = PWRT disal<br>0 = PWRT enab                           | oled                                                                                                                                                       | r Enable | e bit <sup>(1)</sup> | )                      |           |       |         |           |       |       |

| bit 3             | WDTE: Watchd<br>1 = WDT enable<br>0 = WDT disabl                                  | ed                                                                                                                                                         | Enable   | bit                  |                        |           |       |         |           |       |       |

| bit 2-0           | FOSC<2:0>: 03                                                                     | scillator S                                                                                                                                                | electior | n bits               |                        |           |       |         |           |       |       |

|                   | FOSC<2:0>                                                                         | OSCIL                                                                                                                                                      | LATOR    | RA                   | S/OSC2/CI              | KOUT/T1   | ICKI  | RA7/OS  | C1/CLKIN  | 1     |       |

|                   | 000                                                                               | L                                                                                                                                                          | P        |                      | Crystal/F              | Resonator | -     | Crystal | Resonato  | or    |       |

|                   | 001                                                                               | >                                                                                                                                                          | (T       |                      | Crystal/F              | Resonator |       | Crystal | Resonate/ | or    |       |

|                   | 010                                                                               | F                                                                                                                                                          | IS       |                      | Crystal/F              | Resonator |       | Crystal | Resonate/ | or    |       |

|                   | 011                                                                               | E                                                                                                                                                          | C        |                      | Digit                  | al I/O    |       | С       | LKIN      |       |       |

|                   | 100                                                                               | IN                                                                                                                                                         | FRC      |                      | Digit                  | al I/O    |       | Dig     | ital I/O  |       |       |

|                   | 101                                                                               | IN                                                                                                                                                         | FRC      |                      | CLK                    | OUT       |       | Dig     | ital I/O  |       |       |

|                   | 110                                                                               | F                                                                                                                                                          | RC       |                      | Digit                  | al I/O    |       |         | RC        |       |       |

|                   | 111                                                                               | F                                                                                                                                                          | RC 01    |                      | CLK                    | OUT       |       |         | RC        |       |       |

|                   |                                                                                   |                                                                                                                                                            |          |                      |                        |           |       |         |           |       |       |

Note 1: All of the CP bits must be given the same value to enable code protection.

#### TABLE 14-5: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                             | Program<br>Counter | STATUS<br>Register | PCON<br>Register |

|---------------------------------------|--------------------|--------------------|------------------|

| Power-on Reset                        | 000h               | 0001 1xxx          | 0 1-01           |

| MCLR Reset during normal operation    | 000h               | 000u uuuu          | 0 1-uu           |

| MCLR Reset during SLEEP               | 000h               | 0001 0uuu          | 0 1-uu           |

| WDT Reset                             | 000h               | 0000 luuu          | 0 1-uu           |

| WDT Wake-up                           | PC + 1             | uuu0 0uuu          | 0 u-uu           |

| Brown-out Reset                       | 000h               | 0001 luuu          | 0 1-u0           |

| Interrupt wake-up from SLEEP, GIE = 0 | PC + 1             | uuul Ouuu          | u u-uu           |

| Interrupt wake-up from SLEEP, GIE = 1 | 0004h              | uuul Ouuu          | u u-uu           |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

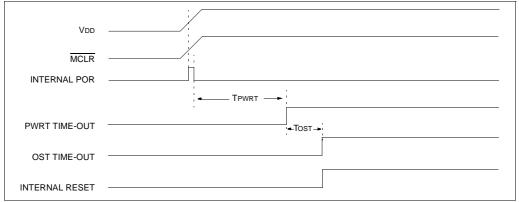

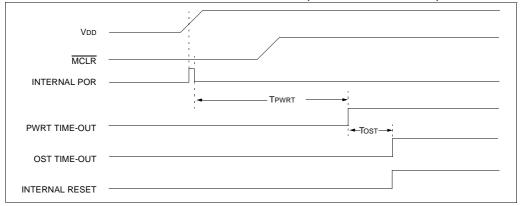

## FIGURE 14-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

#### FIGURE 14-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD)

#### FIGURE 14-12: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                                  |                   | TOST         |              | \'\        |                        |             |

|----------------------------------|-------------------|--------------|--------------|------------|------------------------|-------------|

| NT pin                           | i<br>i            |              | 1            |            | 1                      |             |

| NTF flag                         | 1                 |              | 1            |            | 1                      |             |

| NTCON<1>)                        |                   | /            | 1            |            | 1                      |             |

| GIE bit                          |                   |              |              | Interrupt  | Latency <sup>(2)</sup> |             |

| NTCON<7>)                        | 1                 | Processor in | · ·          |            |                        |             |

| 1                                | 1                 | SLEEP        | 1            |            | 1                      |             |

| NSTRUCTION FLOW                  |                   |              | i i          |            |                        |             |

| PC X P                           | C X PC+1          | χ PC+2       | X PC+2       | ( PC + 2 ) | 0004h χ                | 0005h       |

|                                  | = SLEEP Inst(PC - | + 1)         | Inst(PC + 2) |            | Inst(0004h)            | Inst(0005h) |

| nstruction<br>Fetched { Inst(PC) |                   |              |              |            | Dummy cycle            |             |

3: CLKOUT is not available in these osc modes, but shown here for timing reference.

| TABLE 13-2: FIGTOGAAA INSTRUCTION SET | TABLE 15-2: | PIC16CXXX INSTRUCTION SET |

|---------------------------------------|-------------|---------------------------|

|---------------------------------------|-------------|---------------------------|

| Mnemonic,                             |                                 | Description                           | Cycles  |        | 14-Bit | Opcod | е    | Status   | Notes |

|---------------------------------------|---------------------------------|---------------------------------------|---------|--------|--------|-------|------|----------|-------|

| Opera                                 | inds                            | Description                           | Cycles  | MSb    | )      |       | LSb  | Affected | NULES |

|                                       |                                 | BYTE-ORIENTED FILE REG                | ISTER O | PERA   | TIONS  |       |      |          |       |

| ADDWF                                 | f, d                            | Add W and f                           | 1       | 00     | 0111   | dfff  | ffff | C,DC,Z   | 1,2   |

| ANDWF                                 | f, d                            | AND W with f                          | 1       | 00     | 0101   | dfff  | ffff | Z        | 1,2   |

| CLRF                                  | f                               | Clear f                               | 1       | 00     | 0001   | lfff  | ffff | Z        | 2     |

| CLRW                                  | -                               | Clear W                               | 1       | 00     | 0001   | 0000  | 0011 | Z        |       |

| COMF                                  | f, d                            | Complement f                          | 1       | 00     | 1001   | dfff  | ffff | Z        | 1,2   |

| DECF                                  |                                 |                                       | 1       | 00     | 0011   | dfff  | ffff | Z        | 1,2   |

| DECFSZ                                | FSZ f, d Decrement f, Skip if 0 |                                       | 1(2)    | 00     | 1011   | dfff  | ffff |          | 1,2,3 |

| INCF                                  | CF f, d Increment f             |                                       | 1       | 00     | 1010   | dfff  | ffff | Z        | 1,2   |

| INCFSZ                                |                                 |                                       | 1(2)    | 00     | 1111   | dfff  | ffff |          | 1,2,3 |

| IORWF                                 | f, d                            | Inclusive OR W with f                 | 1       | 00     | 0100   | dfff  | ffff | Z        | 1,2   |

| MOVF f, d                             |                                 | Move f                                | 1       | 00     | 1000   | dfff  | ffff | Z        | 1,2   |

| MOVWF                                 | f                               | Move W to f                           | 1       | 00     | 0000   | lfff  | ffff |          |       |

| NOP                                   | -                               | No Operation                          | 1       | 00     | 0000   | 0xx0  | 0000 |          |       |

| RLF                                   | f, d                            | Rotate Left f through Carry           | 1       | 00     | 1101   | dfff  | ffff | С        | 1,2   |

| RRF                                   | f, d                            | Rotate Right f through Carry          | 1       | 00     | 1100   | dfff  | ffff | С        | 1,2   |

| SUBWF                                 | f, d                            | Subtract W from f                     | 1       | 00     | 0010   | dfff  | ffff | C,DC,Z   | 1,2   |

| SWAPF                                 | f, d                            | Swap nibbles in f                     | 1       | 00     | 1110   | dfff  | ffff |          | 1,2   |

| XORWF                                 | f, d                            | Exclusive OR W with f                 | 1       | 00     | 0110   | dfff  | ffff | Z        | 1,2   |

| BIT-ORIENTED FILE REGISTER OPERATIONS |                                 |                                       |         |        |        |       |      |          |       |

| BCF                                   | f, b                            | Bit Clear f                           | 1       | 01     | 00bb   | bfff  | ffff |          | 1,2   |

| BSF                                   | f, b                            | Bit Set f                             | 1       | 01     | 01bb   | bfff  | ffff |          | 1,2   |

| BTFSC                                 | f, b                            | Bit Test f, Skip if Clear             | 1 (2)   | 01     | 10bb   | bfff  | ffff |          | 3     |

| BTFSS                                 | f, b                            | Bit Test f, Skip if Set               | 1 (2)   | 01     | 11bb   | bfff  | ffff |          | 3     |

| LITERAL AND CONTROL OPERATIONS        |                                 |                                       |         |        |        |       |      |          |       |

| ADDLW                                 | k                               | Add literal and W 1 11 111x kkkk kkkk |         | C,DC,Z |        |       |      |          |       |

| ANDLW                                 | k                               | AND literal with W                    | 1       | 11     | 1001   | kkkk  | kkkk | Z        |       |

| CALL                                  | k                               | Call subroutine                       | 2       | 10     | 0kkk   | kkkk  | kkkk |          |       |

| CLRWDT                                | -                               | Clear Watchdog Timer                  | 1       | 00     | 0000   | 0110  | 0100 | TO,PD    |       |

| GOTO                                  | k                               | Go to address                         | 2       | 10     | 1kkk   | kkkk  | kkkk |          |       |

| IORLW                                 | k                               | Inclusive OR literal with W           | 1       | 11     | 1000   | kkkk  | kkkk | Z        |       |

| MOVLW                                 | k                               | Move literal to W                     | 1       | 11     | 00xx   | kkkk  | kkkk |          |       |

| RETFIE                                | -                               | Return from interrupt                 | 2       | 00     | 0000   | 0000  | 1001 |          |       |

| RETLW                                 | k                               | Return with literal in W              | 2       | 11     | 01xx   | kkkk  | kkkk |          |       |

| RETURN                                | -                               | Return from Subroutine                | 2       | 00     | 0000   | 0000  | 1000 |          |       |

| SLEEP                                 | -                               | Go into standby mode                  | 1       | 00     | 0000   | 0110  | 0011 | TO, PD   |       |

| SUBLW                                 | k                               | Subtract W from literal               | 1       | 11     | 110x   | kkkk  | kkkk | C,DC,Z   |       |

| XORLW                                 | k                               | Exclusive OR literal with W           | 1       | 11     | 1010   | kkkk  | kkkk | Z        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

#### 16.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

#### 16.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multiproject software development tool.

#### 16.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

## 16.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

### TABLE 16-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                                                                                                    |                                                                      | PIC120 | PIC14 | PIC160 | PIC160  | D91019 | PIC16F | PIC16C | PIC16C | PIC16C | PIC16F8 | PIC16C9 | PIC17C | 2271219 | XD81DI9 | PIC18FX | 83CXX<br>52CXX/<br>54CXX/ | ххзэн | мсвехх | MCP251 |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------|-------|--------|---------|--------|--------|--------|--------|--------|---------|---------|--------|---------|---------|---------|---------------------------|-------|--------|--------|

|                                                                                                    | MPLAB <sup>®</sup> Integrated<br>Development Environment             | >      | >     | >      | >       | >      | >      | >      | >      | >      | >       | >       | >      | >       | >       | >       |                           |       |        |        |

|                                                                                                    | MPLAB® C17 C Compiler                                                |        |       |        |         |        |        |        |        |        |         |         | >      | >       |         |         |                           |       |        |        |

|                                                                                                    | MPLAB <sup>®</sup> C18 C Compiler                                    |        |       |        |         |        |        |        |        |        |         |         |        |         | ~       | 1       |                           |       |        |        |

| NOS<br>A M                                                                                         | MPASM <sup>TM</sup> Assembler/<br>MPLINK <sup>TM</sup> Object Linker | >      | >     | >      | >       | >      | >      | >      | >      | >      | >       | >       | >      | >       | >       | >       | >                         | >     |        |        |

|                                                                                                    | MPLAB® ICE In-Circuit Emulator                                       | ~      | ~     | `      | `       | <      | <**    | ~      | ~      | <      | ~       | >       | >      | ~       | ~       | 1       |                           |       |        |        |

|                                                                                                    | ICEPIC <sup>TM</sup> In-Circuit Emulator                             | ^      |       | >      | ~       | ~      |        | >      | >      | ~      |         | ^       |        |         |         |         |                           |       |        |        |

| of ⊒<br>D ⊻<br>Depn88et                                                                            | MPL AB® ICD In-Circuit<br>Debugger                                   |        |       |        | *       |        |        | *>     |        |        | >       |         |        |         |         | >       |                           |       |        |        |

|                                                                                                    | PICSTART® Plus Entry Level<br>Development Programmer                 | `      | >     | >      | `       | `      | <**    | ~      | ~      | `      | `       | `       | `      | `       | `       | 1       |                           |       |        |        |

| Program                                                                                            | PRO MATE® II<br>Universal Device Programmer                          | ^      | ^     | >      | >       | ^      | ** ^   | ^      | ^      | ^      | ^       | ~       | >      | >       | >       | ~       | ~                         | ^     |        |        |

| PIC<br>B<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | PICDEM <sup>TM</sup> 1 Demonstration<br>Board                        |        |       | >      |         | >      |        | .≁     |        | >      |         |         | >      |         |         |         |                           |       |        |        |

| Bög                                                                                                | PICDEM <sup>TM</sup> 2 Demonstration<br>Board                        |        |       |        | <+<br>\ |        |        | ✓†     |        |        |         |         |        |         | >       | ~       |                           |       |        |        |

|                                                                                                    | PICDEM <sup>TM</sup> 3 Demonstration<br>Board                        |        |       |        |         |        |        |        |        |        |         | >       |        |         |         |         |                           |       |        |        |

|                                                                                                    | PICDEM <sup>TM</sup> 14A Demonstration<br>Board                      |        | >     |        |         |        |        |        |        |        |         |         |        |         |         |         |                           |       |        |        |

|                                                                                                    | PICDEM <sup>TM</sup> 17 Demonstration<br>Board                       |        |       |        |         |        |        |        |        |        |         |         |        | >       |         |         |                           |       |        |        |

|                                                                                                    | KEELoq® Evaluation Kit                                               |        |       |        |         |        |        |        |        |        |         |         |        |         |         |         |                           | 1     |        |        |

|                                                                                                    | KEELoa <sup>®</sup> Transponder Kit                                  |        |       |        |         |        |        |        |        |        |         |         |        |         |         |         |                           | 1     |        |        |

|                                                                                                    | microlD <sup>TM</sup> Programmer's Kit                               |        |       |        |         |        |        |        |        |        |         |         |        |         |         |         |                           |       | >      |        |

|                                                                                                    | 125 kHz microlD™<br>Developer's Kit                                  |        |       |        |         |        |        |        |        |        |         |         |        |         |         |         |                           |       | >      |        |

| 12!<br>De                                                                                          | 125 kHz Anticollision microlD™<br>Developer's Kit                    |        |       |        |         |        |        |        |        |        |         |         |        |         |         |         |                           |       | >      |        |

| 13.°<br>Mic                                                                                        | 13.56 MHz Anticollision<br>microlD™ Developer's Kit                  |        |       |        |         |        |        |        |        |        |         |         |        |         |         |         |                           |       | >      |        |

| ğ                                                                                                  | MCP2510 CAN Developer's Kit                                          |        |       |        |         |        |        |        |        |        |         |         |        |         |         |         |                           |       |        | ^      |

© 2001-2013 Microchip Technology Inc.

## 17.1 DC Characteristics: Power Supply

#### TABLE 17-1: DC CHARACTERISTICS: PIC16C781/782, DSTEMP (INDUSTRIAL)

| DC CHA        | RACTER | ISTICS                                                             | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature-40°C $\leq$ TA $\leq$ +85°C for industrial |            |            |                   |                                                                              |  |  |  |  |

|---------------|--------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------|------------|-------------------|------------------------------------------------------------------------------|--|--|--|--|

| Param<br>No.  | Sym    | Characteristic                                                     | Min                                                                                                                         | Тур†       | Max        | Units             | Conditions                                                                   |  |  |  |  |

| D001          | Vdd    | Supply Voltage                                                     | 4.0<br>4.5                                                                                                                  | _          | 5.5<br>5.5 |                   | XT, EC, RC, INTRC Oscillator<br>HS Oscillator                                |  |  |  |  |

| D001A         | Vdd    | Supply Voltage (DSTEMP)                                            | 2.7<br>4.5                                                                                                                  | _          | 5.5<br>5.5 | V<br>V            | XT, EC, RC, INTRC Oscillator<br>HS Oscillator                                |  |  |  |  |

| D002*         | Vdr    | RAM Data Retention<br>Voltage <sup>(1)</sup>                       | -                                                                                                                           | 1.5        | —          | V                 |                                                                              |  |  |  |  |

| D003          | VPOR   | VDD Start Voltage to<br>ensure internal Power-on Reset signal      | -                                                                                                                           | TBD        | —          | V                 | See section on Power-on Reset for details                                    |  |  |  |  |

| D004*         | SVDD   | VDD Rise Rate to ensure internal<br>Power-on Reset signal          | 0.05                                                                                                                        | —          | _          | V/ms              | See section on Power-on Reset for details. PWRT enabled                      |  |  |  |  |

| D010          | IDD    | Supply Current <sup>(2)</sup>                                      | _                                                                                                                           | TBD<br>TBD | TBD<br>TBD | mA<br>mA          | Fosc = 20 MHz, VDD = 5.5V*<br>HS Oscillator<br>Fosc = 20 MHz, VDD = 4.5V     |  |  |  |  |

|               |        |                                                                    | _                                                                                                                           | TBD        | TBD        | mA                | HS Oscillator<br>Fosc = 4 MHz, VDD = 4.0V*<br>XT, RC w/CLKOUT                |  |  |  |  |

|               |        |                                                                    | -                                                                                                                           | TBD        | TBD        | mA                | Fosc = 32 kHz, VDD = 4.0V<br>LP Oscillator                                   |  |  |  |  |

| D020<br>D020A | IPD    | Power-down Current <sup>(3)</sup>                                  | _                                                                                                                           | TBD<br>1.5 | TBD<br>19  | μΑ<br>μΑ          | VDD = 5.5V<br>VDD = 4.0V                                                     |  |  |  |  |

|               | Ιορά   | Operational Amplifier                                              | -                                                                                                                           | TBD<br>TBD | TBD        | mA<br>mA          | VDD = 5.0V,<br>GBWP = 0<br>VDD = 5.0V.                                       |  |  |  |  |

|               |        |                                                                    |                                                                                                                             | 100        | 100        | mA                | GBWP = 1                                                                     |  |  |  |  |

|               | Ivc*   | Voltage Comparators C1 and C2                                      | -                                                                                                                           | TBD        | TBD        | mA                | $V_{DD} = 5.0V, V_{ID} > 100 mV$<br>C1SP = 0                                 |  |  |  |  |

|               |        |                                                                    | -                                                                                                                           | TBD        | TBD        | mA                | VDD = 5.0 , VID>100 mV<br>C1SP = 1                                           |  |  |  |  |

|               | IADC*  | Digital to Analog Converter (DAC)                                  | —                                                                                                                           | TBD        | TBD        | mA                | VDD = 5.0V                                                                   |  |  |  |  |

| D021          | IWDT*  | Watchdog Timer                                                     | —                                                                                                                           | TBD        | TBD        | mA                | VDD = 4.0V                                                                   |  |  |  |  |

| D026          | IAD*   | Analog-to-Digital Converter (ADC)                                  | —                                                                                                                           | TBD        | TBD        | mA                | VDD = 5.5V, ADC not converting                                               |  |  |  |  |

|               | IPLVD* | Programmable Low Voltage Detect                                    |                                                                                                                             | TBD        | TBD        | mA                | VDD = 4.0V                                                                   |  |  |  |  |

|               | IPBOR* | Programmable Brown-out Reset                                       |                                                                                                                             | TBD        | TBD        | mA                | VDD = 5.0V                                                                   |  |  |  |  |

| 1A            | Fosc   | LP Oscillator, Operating Freq.<br>INTRC Oscillator Operating Freq. | 9                                                                                                                           |            | 200<br>    | kHz<br>MHz<br>kHz | All temperatures<br>All temperatures, OSCF = 1<br>All temperatures, OSCF = 0 |  |  |  |  |

|               |        | XT Oscillator Operating Freq.<br>HS Oscillator Operating Freq.     | 0<br>0                                                                                                                      | _          | 4<br>20    | MHz<br>MHz        | All temperatures<br>All temperatures                                         |  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins configured as inputs, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins configured as iputs and tied to VDD or VSS.

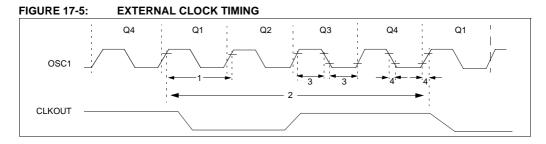

#### TABLE 17-4: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                          | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|-----------------------------------------|-----|------|--------|-------|--------------------|

| 1A               | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC  |      | 4      | MHz   | XT osc mode        |

|                  |       |                                         | DC  | _    | 20     | MHz   | EC osc mode        |

|                  |       |                                         | DC  | _    | 20     | MHz   | HS osc mode        |

|                  |       |                                         | DC  | _    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency <sup>(1)</sup>     | 0.1 |      | 4      | MHz   | XT osc mode        |

|                  |       |                                         | 4   | _    | 20     | MHz   | HS osc mode        |

|                  |       |                                         | 5   | _    | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period <sup>(1)</sup>    | 250 | _    | —      | ns    | XT and RC osc mode |

|                  |       |                                         | 50  | _    | —      | ns    | EC osc mode        |

|                  |       |                                         | 50  | _    | —      | ns    | HS osc mode        |

|                  |       |                                         | 5   | —    | —      | μs    | LP osc mode        |

|                  |       | Oscillator Period <sup>(1)</sup>        | 250 | _    | 10,000 | ns    | XT osc mode        |

|                  |       |                                         | 50  | _    | 250    | ns    | HS osc mode        |

|                  |       |                                         | 5   | _    | —      | μS    | LP osc mode        |

| 2                | TCY   | Instruction Cycle Time <sup>(1)</sup>   | 200 | TCY  | DC     | ns    | TCY = 4/FOSC       |

| 3*               | TOSL, | External Clock in (OSC1) High or        | 100 | _    | _      | ns    | XT oscillator      |

|                  | Tosh  | Low Time                                | 2.5 | —    | —      | μs    | LP oscillator      |

|                  |       |                                         | 15  | _    | —      | ns    | HS oscillator      |

|                  |       |                                         |     |      |        |       | EC oscillator      |

| 4*               | TOSR, | External Clock in (OSC1) Rise or        | —   | _    | 25     | ns    | XT oscillator      |

|                  | TOSF  | Fall Time                               | —   | —    | 50     | ns    | LP oscillator      |

|                  |       |                                         | —   | _    | 15     | ns    | HS oscillator      |

|                  |       |                                         |     |      |        |       | EC oscillator      |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: Instruction cycle period (TcY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

NOTES:

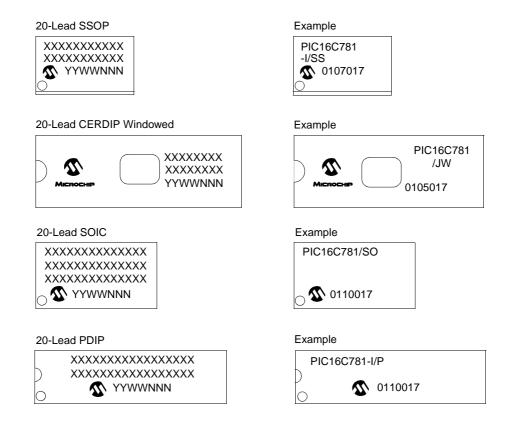

## **19.0 PACKAGING INFORMATION**

## 19.1 Package Marking Information

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((a))<br>can be found on the outer packaging for this package. |

|---------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I       | be carried                             | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                   |

© 2001-2013 Microchip Technology Inc.