Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

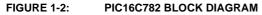

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 8x8b; D/A 1x8b                                                         |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc782t-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                           | Function | Input<br>Type | Output<br>Type | Description                             |  |  |

|------------------------------------------------|----------|---------------|----------------|-----------------------------------------|--|--|

|                                                | RB7      | TTL           | CMOS           | Bi-directional I/O                      |  |  |

| RB7/C2/PSMC1B/T1G                              | C2       | —             | CMOS           | Comparator 2 Output                     |  |  |

|                                                | PSMC1B   | -             | CMOS           | PSMC Output 1B                          |  |  |

|                                                | T1G      | ST            | -              | Timer 1 Gate Input                      |  |  |

| AVdd                                           | AVdd     | Power         |                | Positive Supply for Analog              |  |  |

| AVss                                           | AVss     | Power         |                | Ground Reference for Analog             |  |  |

| VDD                                            | Vdd      | Power         | _              | Positive Supply for Logic and I/O pins  |  |  |

| Vss                                            | Vss      | Power         |                | Ground Reference for Logic and I/O pins |  |  |

| Legend: ST = Schmitt Trigger<br>XTAL = Crystal |          |               |                |                                         |  |  |

## TABLE 1-1: PIC16C781/782 PINOUT DESCRIPTION (CONTINUED)

NOTES:

## 2.8 PCON Register

The Power Control (PCON) register contains two flag bits to allow determination of the source of the most recent RESET:

- Power-on Reset (POR)

- External MCLR Reset

- Power Supply Brown-out (BOR) Reset

The Power Control register also contains frequency select bits for the INTRC oscillator and the WDT software enable bit.

| Note: | BOR is unknown on Power-on Reset. It         |

|-------|----------------------------------------------|

|       | must then be set by the user and checked     |

|       | on subsequent RESETS to see if BOR is        |

|       | clear, indicating a brown-out has occurred.  |

|       | The BOR status bit is a don't care and is    |

|       | not necessarily predictable if the brown-out |

|       | circuit is disabled (by clearing the BODEN   |

|       | bit in the Configuration word).              |

| Directi   | on of Change                                                                  | Typical Time Inactive |         |  |  |  |  |

|-----------|-------------------------------------------------------------------------------|-----------------------|---------|--|--|--|--|

| Direction | on of Change                                                                  | Minimum               | Maximum |  |  |  |  |

| 4 MHz –   | → 37 kHz                                                                      | 100 μs                | 300 μs  |  |  |  |  |

| 37 kHz⇒   | →4 MHz                                                                        | 1.25 μs               | 3.25 μs |  |  |  |  |

| Note:     | When changing the internal oscillator speed (i.e., the OSCF bit, INTRC mode), |                       |         |  |  |  |  |

oscillator frequency change.

the processor will be inactive during the

|               | 0      | ,              |                  |  |

|---------------|--------|----------------|------------------|--|

|               |        |                |                  |  |

|               |        |                |                  |  |

|               |        |                |                  |  |

|               |        | CONTROL DECK   | TED (DOONL OFL)  |  |

| REGISTER 2-6: | POWERU | JUNI KUL KEGIS | STER (PCON: 8Eh) |  |

|               |        |                |                  |  |

|         |               | ••••••                                                                                                                                            |             | (        | ,            |             |               |       |  |  |  |  |  |

|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|--------------|-------------|---------------|-------|--|--|--|--|--|

|         | U-0           | U-0                                                                                                                                               | U-0         | R/W-q    | R/W-1        | U-0         | R/W-q         | R/W-q |  |  |  |  |  |

|         | —             |                                                                                                                                                   | _           | WDTON    | OSCF         | —           | POR           | BOR   |  |  |  |  |  |

|         | bit 7         |                                                                                                                                                   |             |          |              |             |               | bit 0 |  |  |  |  |  |

| bit 7-5 | Unimpleme     | Unimplemented: Read as '0'                                                                                                                        |             |          |              |             |               |       |  |  |  |  |  |

| bit 4   | WDTON: WI     | WDTON: WDT Software Enable bit                                                                                                                    |             |          |              |             |               |       |  |  |  |  |  |

|         |               | If WDTE bit (Configuration Word <3>) = 1:<br>This bit is not writable, always reads '1'                                                           |             |          |              |             |               |       |  |  |  |  |  |

|         | 1 = WDT is e  | If WDTE bit (Configuration Word <3>) = 0:<br>1 = WDT is enabled<br>0 = WDT is disabled                                                            |             |          |              |             |               |       |  |  |  |  |  |

| bit 3   | OSCF: Oscil   | OSCF: Oscillator Speed INTRC Mode bit                                                                                                             |             |          |              |             |               |       |  |  |  |  |  |

|         | 0 = 37 kHz t  | 1 = 4 MHz typical<br>0 = 37 kHz typical<br>All other oscillator modes (X = Ignored)                                                               |             |          |              |             |               |       |  |  |  |  |  |

| bit 2   | Unimpleme     | nted: Read                                                                                                                                        | as '0'      |          |              |             |               |       |  |  |  |  |  |

| bit 1   | POR: Power    | -on Reset S                                                                                                                                       | tatus bit   |          |              |             |               |       |  |  |  |  |  |

|         |               | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul> |             |          |              |             |               |       |  |  |  |  |  |

| bit 0   | BOR: Brown    | -out Reset S                                                                                                                                      | Status bit  |          |              |             |               |       |  |  |  |  |  |

|         |               | 1 = No Brown-out Reset occurred<br>0 = A Brown-out Reset occurred                                                                                 |             |          |              |             |               |       |  |  |  |  |  |

|         | Legend:       |                                                                                                                                                   |             |          |              |             |               |       |  |  |  |  |  |

|         | q = Value de  | pends on co                                                                                                                                       | onditions   |          |              |             |               |       |  |  |  |  |  |

|         | R = Readab    | le bit                                                                                                                                            | W = Writ    | able bit | U = Unimp    | lemented bi | t, read as '0 | )'    |  |  |  |  |  |

|         | - n = Value a | at POR                                                                                                                                            | '1' = Bit i | s set    | '0' = Bit is | cleared     | x = Bit is ur | known |  |  |  |  |  |

|         |               |                                                                                                                                                   |             |          |              |             |               |       |  |  |  |  |  |

#### REGISTER 3-2: WEAK PULL-UP PORTB REGISTER (WPUB: 95h)

| R/W-1                                      | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |  |  |

|--------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| WPUB7                                      | WPUB6 | WPUB5 | WPUB4 | WPUB3 | WPUB2 | WPUB1 | WPUB0 |  |  |

| bit7 b                                     |       |       |       |       |       |       |       |  |  |

| WPUB<7:0>: PORTB Weak Pull-Up Control bits |       |       |       |       |       |       |       |  |  |

bit 7-0 WPUB<7:0>: PORTB Weak Pull-Up C

1 = Weak pull-up enabled for corresponding pin

0 = Weak pull-up disabled for corresponding pin

- Note 1: For the WPUB register setting to take effect, the RBPU bit in the OPTION\_REG register must be cleared.

- 2: The weak pull-up device is automatically disabled if the pin is in output mode, i.e., (TRISB = 0) for corresponding pin.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 3-3: INTERRUPT-ON-CHANGE PORTB REGISTER (IOCB: 96h)

| R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOCB7 | IOCB6 | IOCB5 | IOCB4 | IOCB3 | IOCB2 | IOCB1 | IOCB0 |

| bit7  |       |       |       |       |       |       | bit0  |

bit 7-0

7-0 **IOCB<7:0>:** Interrupt-on-Change PORTB Control bits

1 = Interrupt-on-change enabled for corresponding pin

0 = Interrupt-on-change disabled for corresponding pin

**Note 1:** The interrupt enable bits, GIE and RBIE in the INTCON register, must be set for individual interrupts to be recognized.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 3.3.3 TRISB, ANSEL, AND CONTROL PRECEDENCE

The ANSEL and TRISB registers are the primary controls for the configuration of PORTB pins. TRISB tristates the output drivers of PORTB, and the ANSEL register disables the input buffers. It is important to program both registers when configuring a port pin, since most peripherals do not have precedence over the TRISB and ANSEL registers' control of the pin. Even if a peripheral has the ability to override the control of the TRISB and ANSEL registers, it is good practice to program both registers appropriately.

| Note 1: Upon RESET, the ANSEL register config- |  |

|------------------------------------------------|--|

| ures the RB<3:0> pins as analog inputs.        |  |

- 2: When programmed as analog inputs, RB<3:0> pins will read as '0'.

- 3: There are specific cases in which the functions of the TRISB and ANSEL registers can be overridden by a peripheral or configuration word (see Figure 3-9 through Figure 3-16 for details).

## 4.4 Program Memory Read With Code Protect Set

When the device is code protected, the CPU can still perform the program memory read function.

| Address | Name   | Bit 7    | Bit 6 | Bit 5 | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|----------|-------|-------|----------|----------|-------|-------|-------|-----------------------|---------------------------------|

| 10Ch    | PMDATL | PMD7     | PMD6  | PMD5  | PMD4     | PMD3     | PMD2  | PMD1  | PMD0  | 0000 0000             | 0000 0000                       |

| 10Dh    | PMADRL | PMA7     | PMA6  | PMA5  | PMA4     | PMA3     | PMA2  | PMA1  | PMA0  | xxxx xxxx             | uuuu uuuu                       |

| 10Eh    | PMDATH | _        | _     | PMD13 | PMD12    | PMD11    | PMD10 | PMD9  | PMD8  | 00 0000               | 00 0000                         |

| 10Fh    | PMADRH |          | _     | —     | Reserved | Reserved | PMA10 | PMA9  | PMA8  | x xxxx                | u uuuu                          |

| 18Ch    | PMCON1 | Reserved | -     |       | —        | —        |       | _     | RD    | 10                    | 10                              |

### TABLE 4-1: SUMMARY OF REGISTERS ASSOCIATED WITH PMR

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PMR.

#### FIGURE 4-1: PROGRAM MEMORY READ CYCLE EXECUTION

|                              | C+5                 |

|------------------------------|---------------------|

|                              | R(PC+4)<br>ted here |

| RD bit                       | <br>                |

| PMDATH<br>PMDATL<br>Register | <br>+<br>           |

## 8.2 Operation

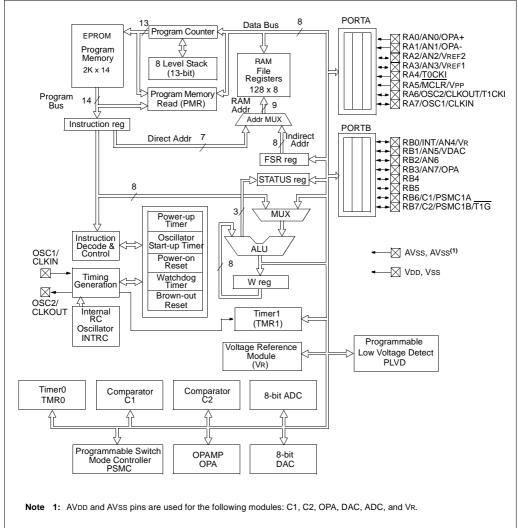

The PLVD indicates a low voltage condition by setting the LVDIF bit in the PIR1 register. Once set by the PLVD module, the LVDIF bit will remain set until cleared by software. For proper indication of a low voltage condition, the user should clear this bit prior to testing.

To test for a low voltage condition, the PLVD module compares the divided output of VDD against an internal bandgap reference. The PLVD module automatically

enables this reference whenever it is enabled and provides a stability bit, BGST, to indicate when it has stabilized. The bandgap reference is also enabled by other modules within the PIC16C781/782 as part of their operation. Other modules using the bandgap include the following:

- VR module

- · BOR module

- · OPA calibration module

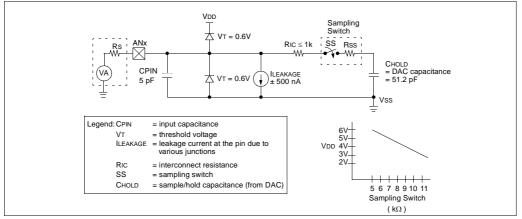

## 9.4 ADC Configuration and Conversion

Example 9-2 demonstrates an ADC conversion. The RA0/AN0 pin is configured as the analog input. The reference voltage selected is the device AVDD. The ADC interrupt is enabled, and the ADC conversion clock is ADRC.

Clearing the GO/DONE bit during a conversion aborts the current conversion. The ADRES register is NOT updated with the partially completed ADC conversion sample. That is, the ADRES register continues to contain the value of the last completed conversion (or the last value written to the ADRES register). After the ADC conversion is aborted, a 2TAD wait period is required before the next acquisition is started. After this 2TAD wait period, an acquisition is automatically started on the selected channel.

## EXAMPLE 9-2: ADC CONVERSION

- ;\* for polling, AVDD as reference, RC clock

- ;\* and RAO input.

- ;\*

- ;\* Conversion start & wait for complete

- ;\* polling code included.

| ;* |         |             |   |                   |

|----|---------|-------------|---|-------------------|

|    | BANKSEL | ADCON1      | ; | Select Bank 1     |

|    | CLRF    | ADCON1      | ; | AVDD as VREF      |

|    | BSF     | TRISA,0     | ; | Set RA0 as input  |

|    | BSF     | ANSEL,0     | ; | Set RA0 as analog |

|    |         |             |   |                   |

|    | BANKSEL | ADCON0      | ; | Select Bank0      |

|    | MOVLW   | B'11000001' |   |                   |

|    | MOVWF   | ADCON0      | ; | RC, Ch 0, ADC on  |

|    |         |             |   |                   |

- ;\* Start & Wait for ADC complete, assumes

- ;\* minimum acquisition delay from

- ;\* configuration.

| ADC_CNVRT   |             |   |               |

|-------------|-------------|---|---------------|

| BANKSEL     | ADCON0      | ; | Select Bank 0 |

| BSF         | ADCON0,GO   | ; | Start convert |

| ADC_CN_LOOP |             |   |               |

| BTFSC       | ADCON0,GO   | ; | Test for end  |

| GOTO        | ADC_CN_LOOP | ; | If not, wait  |

| MOVF        | ADRES,W     | ; | Get result    |

| Address | Name   | Bit 7   | Bit 6        | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>RESETS |

|---------|--------|---------|--------------|------------|-------|-------|-------|-------|-------|-----------------------|---------------------------------|

| 11Ch    | OPACON | OPAON   | CMPEN        | —          |       | —     | —     | —     | GBWP  | 000                   | 000                             |

| 110h    | CALCON | CAL     | CALERR       | CALREF     | _     | —     | _     | —     |       | 000                   | 000                             |

| 9Dh     | ANSEL  | AN7     | AN6          | AN5        | AN4   | AN3   | AN2   | AN1   | AN0   | 1111 1111             | 1111 1111                       |

| 86h     | TRISB  | PORTB I | Data Directi | on Registe | r     |       |       |       |       | 1111 1111             | 1111 1111                       |

| 85h     | TRISA  | PORTA D | Data Directi | on Registe | r     |       |       |       |       | 1111 1111             | 1111 1111                       |

| 11Eh    | DAC    | DA7     | DA6          | DA5        | DA4   | DA3   | DA1   | DA1   | DA0   | 0000 0000             | 0000 0000                       |

| 11Fh    | DACON0 | DAON    | DAOE         | —          | -     | —     | —     | DARS1 | DARS0 | 0000                  | 0000                            |

TABLE 11-1: REGISTERS ASSOCIATED WITH THE OPA MODULE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for the OPA module.

## 12.0 COMPARATOR MODULE

The comparator module has two separate voltage comparators: Comparator C1 and Comparator C2 (see Figure 12-1).

Each comparator offers the following list of features:

- · Control and configuration register

- · Comparator output available externally

- Programmable output polarity

- Interrupt-on-change flags

- Wake-up from SLEEP

- · Configurable as feedback input to the PSMC

- Programmable four input multiplexer

- Programmable reference selections

- · Programmable speed

- Output synchronization to Timer1 clock input (Comparator C2 only)

### 12.1 Control Registers

Both comparators have separate control and configuration registers: CM1CON0 for C1 and CM2CON0 for C2. In addition, Comparator C2 has a second control register, CM2CON1, for synchronization control and simultaneous reading of both comparator outputs.

#### 12.1.1 COMPARATOR C1 CONTROL REGISTER

The CM1CON0 register (shown in Register 12-1) contains the control and status bits for the following:

- · Comparator enable

- · Comparator input selection

- Comparator reference selection

- Output mode

- Comparator speed

Setting C1ON (CM1CON0<7>) enables Comparator C1 for operation.

Bits C1CH<1:0> (CM1CON0<1:0>) select the comparator input from the four analog pins AN<7:4>.

| Note: | To use AN<7:4> as analog inputs, the   |

|-------|----------------------------------------|

|       | appropriate bits must be programmed in |

|       | the ANSEL register.                    |

Setting C1R (CM1CON0<2>) selects the output of the DAC module as the reference voltage for the comparator. Clearing C1R selects the VREF1 input on the RA3/ AN3/VREF1 pin.

The output of the comparator is available internally via the C1OUT flag (CM1CON0<6>). To make the output available for an external connection, the C1OE flag (CM1CON0<5>) must be set. If the module is disabled with C1OE set, the output will be driven as shown in Table 12-2:

The polarity of the comparator output can be inverted by setting the C1POL flag (CM1CON0<4>). Clearing C1POL results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 12-2.

## TABLE 12-1: OUTPUT STATE VERSUS INPUT CONDITIONS

| Input Condition | C1POL | C1OUT |

|-----------------|-------|-------|

| C1VN > C1VP     | 0     | 0     |

| C1VN < C1VP     | 0     | 1     |

| C1VN > C1VP     | 1     | 1     |

| C1VN < C1VP     | 1     | 0     |

Note 1: The internal output of the comparator is latched at the end of each instruction cycle. External outputs are not latched.

- **2:** The C1 interrupt will operate correctly with C1OE set or cleared.

- For the output of C1 on RB6/C1/ PSMC1A, the PSMC must be disabled and TRISB<6> must be '0'.

C1SP (CM1CON0<3>) configures the speed of the comparator. When C1SP is set, the comparator operates at its normal speed. Clearing C1SP operates the comparator in a slower, low power mode.

|         | R/W-0           | R-0                          | R/W-0        | R/W-0              | R/W-0                 | R/W-0         | R/W-0          | R/W-0 |

|---------|-----------------|------------------------------|--------------|--------------------|-----------------------|---------------|----------------|-------|

|         | C10N            | C10UT                        | C10E         | C1POL              | C1SP                  | C1R           | C1CH1          | C1CH0 |

|         | bit 7           |                              |              |                    |                       |               |                | bit 0 |

|         |                 |                              |              |                    |                       |               |                |       |

| bit 7   | C1ON: Co        | mparator C1                  | Enable bit   | t                  |                       |               |                |       |

|         |                 | mparator is o                |              |                    |                       |               |                |       |

|         | 0 = C1 Co       | mparator is o                | disabled     |                    |                       |               |                |       |

| bit 6   | <b>C1OUT:</b> C | omparator C                  | 1 Output b   | it                 |                       |               |                |       |

|         |                 | <u>= 1 (inverted</u>         |              |                    |                       |               |                |       |

|         |                 | Γ = 1, C1VF<br>Γ = 0, C1VF   |              |                    |                       |               |                |       |

|         | If C1POL =      | <u>= 0 (non-inve</u>         | erted polari | t <u>v):</u>       |                       |               |                |       |

|         | C10U            | T = 1, C1VP                  | > C1VN       |                    |                       |               |                |       |

|         | C10U            | Γ = 0, C1VP                  | < C1VN       |                    |                       |               |                |       |

| bit 5   | C10E: Co        | mparator C1                  | Output En    | able bit           |                       |               |                |       |

|         |                 | T is present                 |              | S/C1/PSMC1         | IA pin <sup>(1)</sup> |               |                |       |

|         | 0 = C1OU        | T is internal                | only         |                    |                       |               |                |       |

| bit 4   | <b>C1POL:</b> C | omparator C                  | C1 Output F  | olarity Sele       | ct bit                |               |                |       |

|         |                 | T logic is inv               |              |                    |                       |               |                |       |

|         | 0 = C1OU        | T logic is not               | t inverted   |                    |                       |               |                |       |

| bit 3   | C1SP: Co        | mparator C1                  | Speed Sel    | ect bit            |                       |               |                |       |

|         |                 | erates in nor                |              |                    |                       |               |                |       |

|         | 0 = C1 ope      | erates in low                | power, slo   | w speed mo         | de                    |               |                |       |

| bit 2   | C1R: Com        | parator C1 I                 | Reference    | Select bits (r     | non-inverting         | g input)      |                |       |

|         |                 | connects to                  |              | ut                 |                       |               |                |       |

|         |                 | connects to                  |              |                    |                       |               |                |       |

| bit 1-0 | C1CH<1:0        | I>: Compara                  | tor C1 Cha   | nnel Select        | bits                  |               |                |       |

|         |                 | V of C1 conn                 |              |                    |                       |               |                |       |

|         |                 | N of C1 conn<br>N of C1 conn |              |                    |                       |               |                |       |

|         |                 | V of C1 conn                 |              |                    |                       |               |                |       |

|         | 11 - 0111       |                              |              | ,                  |                       |               |                |       |

|         |                 | C1OUT will o                 |              |                    |                       |               |                |       |

|         |                 | · /                          |              | , ,                | 8<7> = 0) &           | ((SMCON = 0)) |                |       |

|         | (               | or ((SMCOM                   | i = 0) & (SC | $\mu \equiv 0))).$ |                       |               |                |       |

|         | Legend:         |                              |              |                    |                       |               |                |       |

|         | R = Reada       | able bit                     | W = 1        | Writable bit       | U = Un                | implemented b | it, read as 'C | ,     |

|         | 1               |                              |              |                    |                       |               |                |       |

## REGISTER 12-1: COMPARATOR C1 CONTROL REGISTER0 (CM1CON0: 119h)

© 2001-2013 Microchip Technology Inc.

- n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 12.1.2.2 Control Register CM2CON1

Comparator C2 has one additional feature: its output can be synchronized to the Timer1 clock input. Setting C2SYNC (CM2CON1<0>) synchronizes the output of Comparator 2 to the falling edge of Timer 1's clock input (see Figure 12-1 and Register 12-3). The CM2CON1 register also contains mirror copies of both comparator outputs, MC1OUT and MC2OUT (CM2CON1<7:6>). The ability to read both outputs simultaneously from a single register eliminates the timing skew of reading separate registers.

#### REGISTER 12-3: COMPARATOR C2 CONTROL REGISTER1 (CM2CON1: 11Bh)

| R-0    | R-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|--------|--------|-----|-----|-----|-----|-----|--------|

| MC10UT | MC2OUT | —   | —   | —   | —   |     | C2SYNC |

| bit 7  |        |     |     |     |     |     | bit 0  |

|        |        |     |     |     |     |     |        |

- bit 7 MC1OUT: Mirror Copy of C1OUT (CM1CON0<6>)

- bit 6 MC2OUT: Mirror Copy of C2OUT (CM2CON0<6>)

- bit 5-1 Unimplemented: Read as '0'

- bit 0 C2SYNC: C2 Output Synchronous Mode bit

- 1 = C2 output is synchronous to falling edge of TMR1 clock

- 0 = C2 output is asynchronous

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

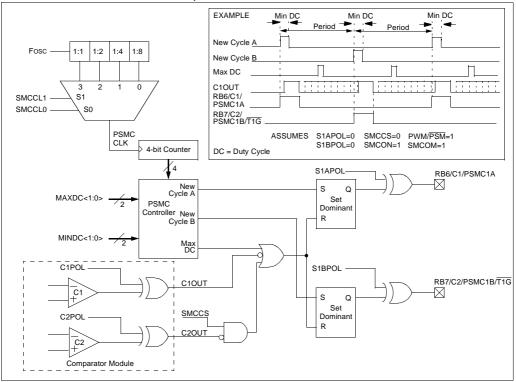

## FIGURE 13-2: PSMC MODULE IN DUAL ALTERNATING OUTPUT PWM MODE (SIMPLIFIED BLOCK DIAGRAM)

### TABLE 13-1: PSMC1A OUTPUT SEQUENCE IN PWM MODE USING C1 COMPARATOR ONLY

| Time                         | MINDC<1:0> | C1OUT             | PSMC1A Output Signal |

|------------------------------|------------|-------------------|----------------------|

| Beginning of PWM cycle       | 00         | Н                 | $0 \rightarrow 1$    |

|                              |            | L                 | 0                    |

|                              | non-zero   | х                 | $0 \rightarrow 1$    |

| During Min Duty Cycle        | non-zero   | х                 | 1                    |

| After Min Duty Cycle, Before | х          | $H \rightarrow L$ | $q \rightarrow 0$    |

| Max Duty Cycle               |            | $L \rightarrow H$ | 0                    |

| Max Duty Cycle               | х          | х                 | $q \rightarrow 0$    |

Legend: x = Don't Care q = Prior State 0 = Inactive 1 = Active H = High L = Low

NOTES:

## 14.0 SPECIAL FEATURES OF THE CPU

These devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These features include:

- · Oscillator selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Programmable Brown-out Reset (PBOR)

- Interrupts

- Watchdog Timer (WDT)

- Programmable Low Voltage Detection (PLVD)

- SLEEP

- Code protection

- · ID locations

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

Several oscillator options are available to allow the part to fit the application. The INTRC oscillator options save system cost while the LP crystal option saves power. A set of configuration bits is used to select various options.

The CPU also features a Watchdog Timer (WDT), which can be enabled either through a configuration bit during programming, or by the software. For added reliability, the WDT runs off its own internal RC oscillator instead of the main CPU clock.

In addition to the WDT, the CPU incorporates both an Oscillator Start-up Timer and a Power-up Timer. The Oscillator Start-up Timer (OST) is intended to hold the chip in RESET until the crystal oscillator has stabilized. The Power-up Timer (PWRT) holds the CPU in a fixed RESET delay of 72ms (nominal) on Power-up Resets (POR and PBOR), while the power supply stabilizes. With these two timers on-chip, most applications need no external RESET circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can awaken from SLEEP through:

- External RESET

- Watchdog Timer Wake-up

- Interrupt

Additional information on special features is available in the PIC Mid-Range Reference Manual, (DS33023).

## 14.1 Configuration Bits

The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped in program memory location 2007h.

#### Note: Address 2007h is beyond the user program memory space, which can be accessed only during programming.

Some of the core features provided may not be necessary for each application in which a device may be used. The configuration word bits allow these features to be configured/enabled/disabled as necessary. These features include:

- Code Protection

- PBOR Trip Point

- Power-up Timer

- Watchdog Timer

- Device Oscillator Mode

As can be seen in Table 14-1, some additional configuration word bits have been provided for Brown-out Reset trip point selection.

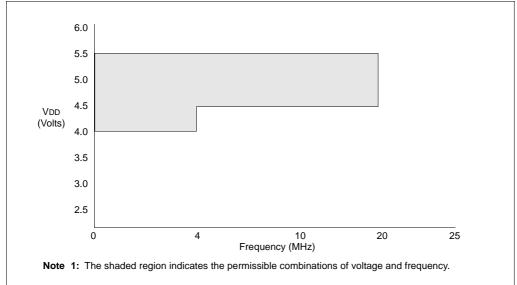

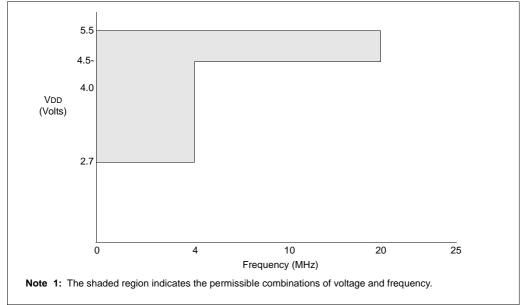

### FIGURE 17-2: PIC16LC781/782 VOLTAGE-FREQUENCY GRAPH, -40°C ≤ TA ≤ +85°C

## 17.1 DC Characteristics: Power Supply

## TABLE 17-1: DC CHARACTERISTICS: PIC16C781/782, DSTEMP (INDUSTRIAL)

| DC CHA        | DC CHARACTERISTICS |                                                                    |            | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature- $40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |            |                   |                                                                              |  |  |  |

|---------------|--------------------|--------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|------------------------------------------------------------------------------|--|--|--|

| Param<br>No.  | Sym                | Characteristic                                                     | Min        | Тур†                                                                                                                                   | Max        | Units             | Conditions                                                                   |  |  |  |

| D001          | Vdd                | Supply Voltage                                                     | 4.0<br>4.5 | _                                                                                                                                      | 5.5<br>5.5 |                   | XT, EC, RC, INTRC Oscillator<br>HS Oscillator                                |  |  |  |

| D001A         | Vdd                | Supply Voltage (DSTEMP)                                            | 2.7<br>4.5 | _                                                                                                                                      | 5.5<br>5.5 | V<br>V            | XT, EC, RC, INTRC Oscillator<br>HS Oscillator                                |  |  |  |

| D002*         | Vdr                | RAM Data Retention<br>Voltage <sup>(1)</sup>                       | -          | 1.5                                                                                                                                    | —          | V                 |                                                                              |  |  |  |

| D003          | VPOR               | VDD Start Voltage to<br>ensure internal Power-on Reset signal      | -          | TBD                                                                                                                                    | —          | V                 | See section on Power-on Reset for details                                    |  |  |  |

| D004*         | SVDD               | VDD Rise Rate to ensure internal<br>Power-on Reset signal          | 0.05       | —                                                                                                                                      | _          | V/ms              | See section on Power-on Reset for details. PWRT enabled                      |  |  |  |

| D010          | IDD                | Supply Current <sup>(2)</sup>                                      | _          | TBD<br>TBD                                                                                                                             | TBD<br>TBD | mA<br>mA          | Fosc = 20 MHz, VDD = 5.5V*<br>HS Oscillator<br>Fosc = 20 MHz, VDD = 4.5V     |  |  |  |

|               |                    |                                                                    | _          | TBD                                                                                                                                    | TBD        | mA                | HS Oscillator<br>Fosc = 4 MHz, VDD = 4.0V*<br>XT. RC w/CLKOUT                |  |  |  |

|               |                    |                                                                    | -          | TBD                                                                                                                                    | TBD        | mA                | Fosc = 32 kHz, VDD = 4.0V<br>LP Oscillator                                   |  |  |  |

| D020<br>D020A | IPD                | Power-down Current <sup>(3)</sup>                                  | _          | TBD<br>1.5                                                                                                                             | TBD<br>19  | μΑ<br>μΑ          | VDD = 5.5V<br>VDD = 4.0V                                                     |  |  |  |

|               | Ιορά               | Operational Amplifier                                              | _          | TBD<br>TBD                                                                                                                             | TBD        | mA<br>mA          | VDD = 5.0V,<br>GBWP = 0<br>VDD = 5.0V.                                       |  |  |  |

|               |                    |                                                                    |            |                                                                                                                                        |            |                   | GBWP = 1                                                                     |  |  |  |

|               | Ivc*               | Voltage Comparators C1 and C2                                      | -          | TBD                                                                                                                                    | TBD        | mA                | VDD = 5.0V, VID>100 mV<br>C1SP = 0                                           |  |  |  |

|               |                    |                                                                    | -          | TBD                                                                                                                                    | TBD        | mA                | VDD = 5.0 , VID>100 mV<br>C1SP = 1                                           |  |  |  |

|               | IADC*              | Digital to Analog Converter (DAC)                                  | —          | TBD                                                                                                                                    | TBD        | mA                | VDD = 5.0V                                                                   |  |  |  |

| D021          | IWDT*              | Watchdog Timer                                                     | —          | TBD                                                                                                                                    | TBD        | mA                | VDD = 4.0V                                                                   |  |  |  |

| D026          | IAD*               | Analog-to-Digital Converter (ADC)                                  | —          | TBD                                                                                                                                    | TBD        | mA                | VDD = 5.5V, ADC not converting                                               |  |  |  |

|               | IPLVD*             | Programmable Low Voltage Detect                                    |            | TBD                                                                                                                                    | TBD        | mA                | VDD = 4.0V                                                                   |  |  |  |

|               | IPBOR*             | Programmable Brown-out Reset                                       |            | TBD                                                                                                                                    | TBD        | mA                | VDD = 5.0V                                                                   |  |  |  |

| 1A            | Fosc               | LP Oscillator, Operating Freq.<br>INTRC Oscillator Operating Freq. | 9          |                                                                                                                                        | 200<br>    | kHz<br>MHz<br>kHz | All temperatures<br>All temperatures, OSCF = 1<br>All temperatures, OSCF = 0 |  |  |  |

|               |                    | XT Oscillator Operating Freq.<br>HS Oscillator Operating Freq.     | 0<br>0     |                                                                                                                                        | 4<br>20    | MHz<br>MHz        | All temperatures<br>All temperatures                                         |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins configured as inputs, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins configured as iputs and tied to VDD or VSS.

NOTES:

NOTES:

## Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Svdney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12