Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | PWM, WDT                                                               |

| Number of I/O              | 59                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 4K x 8                                                                 |

| RAM Size                   | 12K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                          |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 80-QFP                                                                 |

| Supplier Device Package    | 80-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12a256bcfu |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

14

| MC9S12DP256B Device User   | Egddr bold Rdl | Honnet banq+Hhb- |

|----------------------------|----------------|------------------|

| MIC33 IZDFZ30D Device USer | Guide — VUZ.14 | <b>-</b>         |

| Table A-19 | SPI Slave Mode Timing Characteristics | 118 |

|------------|---------------------------------------|-----|

| Table A-20 | Expanded Bus Timing Characteristics   | 121 |

## **Section 1 Introduction**

#### 1.1 Overview

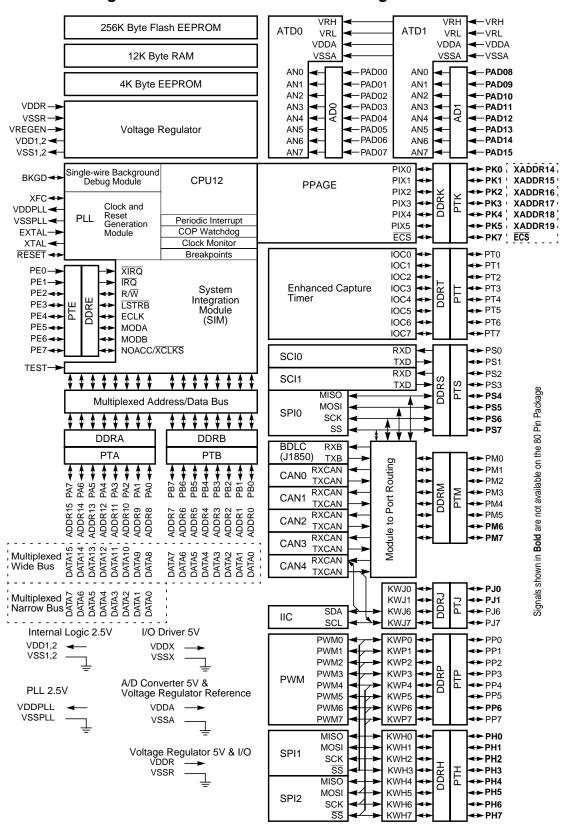

The MC9S12DP256 microcontroller unit (MCU) is a 16-bit device composed of standard on-chip peripherals including a 16-bit central processing unit (HCS12 CPU), 256K bytes of Flash EEPROM, 12K bytes of RAM, 4K bytes of EEPROM, two asynchronous serial communications interfaces (SCI), three serial peripheral interfaces (SPI), an 8-channel IC/OC enhanced capture timer, two 8-channel, 10-bit analog-to-digital converters (ADC), an 8-channel pulse-width modulator (PWM), a digital Byte Data Link Controller (BDLC), 29 discrete digital I/O channels (Port A, Port B, Port K and Port E), 20 discrete digital I/O lines with interrupt and wakeup capability, five CAN 2.0 A, B software compatible modules (MSCAN12), and an Inter-IC Bus. The MC9S12DP256 has full 16-bit data paths throughout. However, the external bus can operate in an 8-bit narrow mode so single 8-bit wide memory can be interfaced for lower cost systems. The inclusion of a PLL circuit allows power consumption and performance to be adjusted to suit operational requirements.

#### 1.2 Features

- HCS12 Core

- 16-bit HCS12 CPU

- i. Upward compatible with M68HC11 instruction set

- ii. Interrupt stacking and programmer's model identical to M68HC11

- iii. Instruction queue

- iv. Enhanced indexed addressing

- MEBI (Multiplexed External Bus Interface)

- MMC (Module Mapping Control)

- INT (Interrupt control)

- BKP (Breakpoints)

- BDM (Background Debug Mode)

- CRG (low current oscillator, PLL, reset, clocks, COP watchdog, real time interrupt, clock monitor)

- 8-bit and 4-bit ports with interrupt functionality

- Digital filtering

- Programmable rising or falling edge trigger

- Memory

- 256K Flash EEPROM

- 4K byte EEPROM

- 12K byte RAM

Figure 1-1 MC9S12DP256B Block Diagram

# MC9S12DP256B Device User Guide V02.14 RdI Honnet bsnq+ Hhb-

#### \$0010 - \$0014

#### MMC map 1 of 4 (Core User Guide)

| Address | Name   |

|---------|--------|

| \$0012  | INITEE |

| \$0013  | MISC   |

| \$0014  | MTSTO  |

|        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0 |

|--------|-------|-------|-------|-------|--------|--------|--------|-------|

| Read:  | EE15  | EE14  | EE13  | EE12  | 0      | 0      | 0      | EEON  |

| Write: | EE13  | CC14  | EEIS  | EE12  |        |        |        | EEON  |

| Read:  | 0     | 0     | 0     | 0     | EXSTR1 | EXSTR0 | ROMHM  | ROMON |

| Write: |       |       |       |       | EVOLKI | ENSIRU | KOMINI | KOWON |

| Read:  | Bit 7 | 6     | 5     | 4     | 3      | 2      | 1      | Bit 0 |

| Write: |       |       |       |       |        |        |        |       |

#### \$0015 - \$0016

## INT map 1 of 2 (Core User Guide)

| Address | Name  |

|---------|-------|

| \$0015  | ITCR  |

| \$0016  | ITEST |

|                 | Bit 7      | Bit 6 | Bit 5 | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------------|------------|-------|-------|----------|-------|-------|-------|-------|

| Read:           | 0          | 0     | 0     | WRINT    | ADR3  | ADR2  | ADR1  | ADR0  |

| Write:          |            |       |       | VVIXIINI | ADNO  | ADNZ  | ADNI  | ADRO  |

| Read:<br>Write: | 1 11/11/1- | INTC  | INTA  | INT8     | INT6  | INT4  | INT2  | INT0  |

#### \$0017 - \$0017

### MMC map 2 of 4 (Core User Guide)

| Address | Name  |

|---------|-------|

| \$0017  | MTST1 |

|        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:  | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| Write: |       |       |       |       |       |       |       |       |

#### \$0018 - \$001B

## Miscellaneous Peripherals (Device User Guide, Table 1-3)

| Address | Name     |

|---------|----------|

| \$0018  | Reserved |

| \$0019  | Reserved |

| \$001A  | PARTIDH  |

| \$001B  | PARTIDL  |

|        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Write: |       |       |       |       |       |       |       |       |

| Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Write: |       |       |       |       |       |       |       |       |

| Read:  | ID15  | ID14  | ID13  | ID12  | ID11  | ID10  | ID9   | ID8   |

| Write: |       |       |       |       |       |       |       |       |

| Read:  | ID7   | ID6   | ID5   | ID4   | ID3   | ID2   | ID1   | ID0   |

| Write: |       |       |       |       |       |       |       |       |

#### \$001C - \$001D

Address

## MMC map 3 of 4 (Core and Device User Guide, Table 1-4)

| \$001C | MEMSIZ0 |

|--------|---------|

| \$001D | MEMSIZ1 |

Name

|        | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2   | Bit 1   | Bit 0   |

|--------|---------|---------|---------|---------|-------|---------|---------|---------|

| Read:  | reg_sw0 | 0       | eep_sw1 | eep_sw0 | 0     | ram_sw2 | ram_sw1 | ram_sw0 |

| Write: |         |         |         |         |       |         |         |         |

| Read:  | rom_sw1 | rom_sw0 | 0       | 0       | 0     | 0       | pag_sw1 | pag_sw0 |

| Write: |         |         |         |         |       |         |         |         |

26

#### \$00F0 - \$00F7

#### **SPI1 (Serial Peripheral Interface)**

|                   |          | _               |       |       |       |         |         |       |         |       |

|-------------------|----------|-----------------|-------|-------|-------|---------|---------|-------|---------|-------|

| Address           | Name     |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3   | Bit 2 | Bit 1   | Bit 0 |

| \$00F0            | SPI1CR1  | Read:<br>Write: | SPIE  | SPE   | SPTIE | MSTR    | CPOL    | СРНА  | SSOE    | LSBFE |

| \$00F1            | SPI1CR2  | Read:           | 0     | 0     | 0     | MODFEN  | BIDIROE | 0     | SPISWAI | SPC0  |

| φυση              | SPITCRZ  | Write:          |       |       |       | MODELIN | BIDIKOL |       | SFISWAI | 3500  |

| \$00F2            | SPI1BR   | Read:           | 0     | SPPR2 | SPPR1 | SPPR0   | 0       | SPR2  | SPR1    | SPR0  |

| φυυΓΖ             | SPIIDK   | Write:          |       | SFFNZ | SEEKI | SFFRU   |         | SFRZ  | SEKT    | SFRU  |

| \$00F3            | SPI1SR   | Read:           | SPIF  | 0     | SPTEF | MODF    | 0       | 0     | 0       | 0     |

| φυυΓο             | SFIISK   | Write:          |       |       |       |         |         |       |         |       |

| \$00F4            | Reserved | Read:           | 0     | 0     | 0     | 0       | 0       | 0     | 0       | 0     |

| φυυΓ <del>4</del> | Reserved | Write:          |       |       |       |         |         |       |         |       |

| \$00F5            | SPI1DR   | Read:           | Bit7  | 6     | 5     | 4       | 3       | 2     | 1       | Bit0  |

| φυυΓΟ             | SPIIDR   | Write:          | Ыί    | b     | 5     | 4       | 3       | 2     | I       | ыш    |

| \$00F6            | Reserved | Read:           | 0     | 0     | 0     | 0       | 0       | 0     | 0       | 0     |

| φυσισ             | Reserved | Write:          |       |       |       |         |         |       |         |       |

| \$00F7            | Reserved | Read:           | 0     | 0     | 0     | 0       | 0       | 0     | 0       | 0     |

| φυυι-7            | Reserved | Write:          |       |       |       |         |         |       |         |       |

#### \$00F8 - \$00FF

#### **SPI2 (Serial Peripheral Interface)**

|         |          | -               |       |       |       |          |         |       |         |       |

|---------|----------|-----------------|-------|-------|-------|----------|---------|-------|---------|-------|

| Address | Name     |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3   | Bit 2 | Bit 1   | Bit 0 |

| \$00F8  | SPI2CR1  | Read:<br>Write: | SPIE  | SPE   | SPTIE | MSTR     | CPOL    | СРНА  | SSOE    | LSBFE |

| \$00F9  | SPI2CR2  | Read:           | 0     | 0     | 0     | MODFEN   | BIDIROE | 0     | SPISWAI | SPC0  |

| φυυΓ9   | SPIZURZ  | Write:          |       |       |       | INIODEEN | DIDIKUE |       | SPISWAI | 3500  |

| <b></b> | CDIODD   | Read:           | 0     | SPPR2 | CDDD4 | SPPR0    | 0       | SPR2  | SPR1    | SPR0  |

| \$00FA  | SPI2BR   | Write:          |       | SPPRZ | SPPR1 | SPPRU    |         | SPRZ  | SPRI    | SPRU  |

| ¢00ED   | CDIOCD   | Read:           | SPIF  | 0     | SPTEF | MODF     | 0       | 0     | 0       | 0     |

| \$00FB  | SPI2SR   | Write:          |       |       |       |          |         |       |         |       |

| ¢ሰባርር   | Decembed | Read:           | 0     | 0     | 0     | 0        | 0       | 0     | 0       | 0     |

| \$00FC  | Reserved | Write:          |       |       |       |          |         |       |         |       |

| \$00FD  | CDIODD   | Read:           | Bit7  | 6     | 5     | 4        | 3       | 2     | 1       | Bit0  |

| φυυΓυ   | SPI2DR   | Write:          | DILI  | O     | 5     | 4        | S       | 2     | I       | DILU  |

| \$00FE  | Decembed | Read:           | 0     | 0     | 0     | 0        | 0       | 0     | 0       | 0     |

| ₽UUFE   | Reserved | Write:          |       |       |       |          |         |       |         |       |

| ¢00EE   | Decembed | Read:           | 0     | 0     | 0     | 0        | 0       | 0     | 0       | 0     |

| \$00FF  | Reserved | Write:          |       |       |       |          |         |       |         |       |

|         |          | -               |       |       |       |          |         |       |         |       |

### \$0100 - \$010F

## Flash Control Register (fts512k4)

| Address | Name    |                 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  |

|---------|---------|-----------------|--------|--------|--------|--------|-------|-------|--------|--------|

| \$0100  | FCLKDIV | Read:<br>Write: | FDIVLD | PRDIV8 | FDIV5  | FDIV4  | FDIV3 | FDIV2 | FDIV1  | FDIV0  |

| \$0101  | FSEC    | Read:           | KEYEN  | NV6    | NV5    | NV4    | NV3   | NV2   | SEC1   | SEC0   |

| \$0101  | FSEC    | Write:          |        |        |        |        |       |       |        |        |

| \$0102  | FTSTMOD | Read:           | 0      | 0      | 0      | WRALL  | 0     | 0     | 0      | 0      |

| φ0102   | FISTNOD | Write:          | U      | O      | U      | WINALL |       |       |        | U      |

| \$0103  | FCNFG   | Read:           | CBEIE  | CCIE   | KEYACC | 0      | 0     | 0     | BKSEL1 | BKSEL0 |

| φυτυσ   | FUNEG   | Write:          | OBEIE  | COL    | RETACC |        |       |       | DNOELI | DNOELU |

# MC9S12DP256B Device User Guide b ld RdI Honnet bsnq+ Hrb-

#### \$0180 - \$01BF

## **CAN1 (Motorola Scalable CAN - MSCAN)**

|                    |           | _               |       |                                                 |         |          |          |           |       |       |  |

|--------------------|-----------|-----------------|-------|-------------------------------------------------|---------|----------|----------|-----------|-------|-------|--|

| Address            | Name      |                 | Bit 7 | Bit 6                                           | Bit 5   | Bit 4    | Bit 3    | Bit 2     | Bit 1 | Bit 0 |  |

| \$0199             | CAN1IDAR5 | Read:<br>Write: | AC7   | AC6                                             | AC5     | AC4      | AC3      | AC2       | AC1   | AC0   |  |

| \$019A             | CAN1IDAR6 | Read:<br>Write: | AC7   | AC6                                             | AC5     | AC4      | AC3      | AC2       | AC1   | AC0   |  |

| \$019B             | CAN1IDAR7 | Read:<br>Write: | AC7   | AC6                                             | AC5     | AC4      | AC3      | AC2       | AC1   | AC0   |  |

| \$019C             | CAN1IDMR4 | Read:<br>Write: | AM7   | AM6                                             | AM5     | AM4      | AM3      | AM2       | AM1   | AM0   |  |

| \$019D             | CAN1IDMR5 | Read:<br>Write: | AM7   | AM6                                             | AM5     | AM4      | AM3      | AM2       | AM1   | AM0   |  |

| \$019E             | CAN1IDMR6 | Read:<br>Write: | AM7   | AM6                                             | AM5     | AM4      | AM3      | AM2       | AM1   | AM0   |  |

| \$019F             | CAN1IDMR7 | Read:<br>Write: | AM7   | AM6                                             | AM5     | AM4      | AM3      | AM2       | AM1   | AM0   |  |

| \$01A0 -           | CANADYEC  | Read:           |       | FOF                                             | REGROUN | D RECEIV | E BUFFER | see Table | 1-2   |       |  |

| \$01AF             | CAN1RXFG  | Write:          |       |                                                 |         |          |          |           |       |       |  |

| \$01B0 -<br>\$01BF | CAN1TXFG  | Read:<br>Write: |       | FOREGROUND TRANSMIT BUFFER see <b>Table 1-2</b> |         |          |          |           |       |       |  |

### \$01C0 - \$01FF

## **CAN2 (Motorola Scalable CAN - MSCAN)**

| Address | Name      |                 | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

|---------|-----------|-----------------|-------|--------|---------|---------|---------|---------|--------|--------|

| \$01C0  | CAN2CTL0  | Read:<br>Write: | RXFRM | RXACT  | CSWAI   | SYNCH   | TIME    | WUPE    | SLPRQ  | INITRQ |

| \$01C1  | CAN2CTL1  | Read:<br>Write: | CANE  | CLKSRC | LOOPB   | LISTEN  | 0       | WUPM    | SLPAK  | INITAK |

| \$01C2  | CAN2BTR0  | Read:<br>Write: | SJW1  | SJW0   | BRP5    | BRP4    | BRP3    | BRP2    | BRP1   | BRP0   |

| \$01C3  | CAN2BTR1  | Read:<br>Write: | SAMP  | TSEG22 | TSEG21  | TSEG20  | TSEG13  | TSEG12  | TSEG11 | TSEG10 |

| \$01C4  | CAN2RFLG  | Read:<br>Write: | WUPIF | CSCIF  | RSTAT1  | RSTAT0  | TSTAT1  | TSTAT0  | OVRIF  | RXF    |

| \$01C5  | CAN2RIER  | Read:<br>Write: | WUPIE | CSCIE  | RSTATE1 | RSTATE0 | TSTATE1 | TSTATE0 | OVRIE  | RXFIE  |

| \$01C6  | CAN2TFLG  | Read:<br>Write: | 0     | 0      | 0       | 0       | 0       | TXE2    | TXE1   | TXE0   |

| \$01C7  | CAN2TIER  | Read:<br>Write: | 0     | 0      | 0       | 0       | 0       | TXEIE2  | TXEIE1 | TXEIE0 |

| \$01C8  | CAN2TARQ  | Read:<br>Write: | 0     | 0      | 0       | 0       | 0       | ABTRQ2  | ABTRQ1 | ABTRQ0 |

| \$01C9  | CAN2TAAK  | Read:<br>Write: | 0     | 0      | 0       | 0       | 0       | ABTAK2  | ABTAK1 | ABTAK0 |

| \$01CA  | CAN2TBSEL | Read:<br>Write: | 0     | 0      | 0       | 0       | 0       | TX2     | TX1    | TX0    |

| \$01CB  | CAN2IDAC  | Read:<br>Write: | 0     | 0      | IDAM1   | IDAM0   | 0       | IDHIT2  | IDHIT1 | IDHIT0 |

| \$01CC  | Reserved  | Read:<br>Write: | 0     | 0      | 0       | 0       | 0       | 0       | 0      | 0      |

## 2.3.8 PAD[14:08] / AN[14:08] — Port AD Input Pins of ATD1

PAD14 - PAD08 are general purpose input pins and analog inputs AN[6:0] of the analog to digital converter ATD1.

## 2.3.9 PAD7 / AN07 / ETRIG0 — Port AD Input Pin of ATD0

PAD7 is a general purpose input pin and analog input AN7 of the analog to digital converter ATD0. It can act as an external trigger input for the ATD0.

## 2.3.10 PAD[06:00] / AN[06:00] — Port AD Input Pins of ATD0

PAD06 - PAD00 are general purpose input pins and analog inputs AN[6:0] of the analog to digital converter ATD0.

## 2.3.11 PA[7:0] / ADDR[15:8] / DATA[15:8] — Port A I/O Pins

PA7-PA0 are general purpose input or output pins. In MCU expanded modes of operation, these pins are used for the multiplexed external address and data bus.

## 2.3.12 PB[7:0] / ADDR[7:0] / DATA[7:0] — Port B I/O Pins

PB7-PB0 are general purpose input or output pins. In MCU expanded modes of operation, these pins are used for the multiplexed external address and data bus.

## 2.3.13 PE7 / NOACC / XCLKS — Port E I/O Pin 7

PE7 is a general purpose input or output pin. During MCU expanded modes of operation, the NOACC signal, when enabled, is used to indicate that the current bus cycle is an unused or "free" cycle. This signal will assert when the CPU is not using the bus.

The  $\overline{XCLKS}$  input selects between an external clock or oscillator configuration. The state of this pin is latched at the rising edge of  $\overline{RESET}$ . If the input is a logic low the EXTAL pin is configured for an external clock drive. If input is a logic high an oscillator circuit is configured on EXTAL and XTAL. Since this pin is an input with a pull-up device, if the pin is left floating, the default configuration is an oscillator circuit on EXTAL and XTAL.

### 2.3.14 PE6 / MODB / IPIPE1 — Port E I/O Pin 6

PE6 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODB bit at the rising edge of  $\overline{RESET}$ . This pin is shared with the instruction queue tracking signal IPIPE1. This pin is an input with a pull-down device which is only active when  $\overline{RESET}$  is low.

# MC9S12DP256B Device User Guide bold RdI Honnet banq+ Hrb-

#### 2.3.30 PJ6 / KWJ6 / RXCAN4 / SDA — PORT J I/O Pin 6

PJ6 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as the receive pin RXCAN for the Motorola Scalable Controller Area Network controller 4 (CAN4) or the serial data pin SDA of the IIC module.

## 2.3.31 PJ[1:0] / KWJ[1:0] — Port J I/O Pins [1:0]

PJ1 and PJ0 are general purpose input or output pins. They can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode .

#### 2.3.32 PK7 / ECS / ROMONE — Port K I/O Pin 7

PK7 is a general purpose input or output pin. During MCU expanded modes of operation, this pin is used as the emulation chip select output ( $\overline{ECS}$ ). During MCU normal expanded wide and narrow modes of operation, this pin is used to enable the Flash EEPROM memory in the memory map (ROMONE). At the rising edge of  $\overline{RESET}$ , the state of this pin is latched to the ROMON bit.

## 2.3.33 PK[5:0] / XADDR[19:14] — Port K I/O Pins [5:0]

PK5-PK0 are general purpose input or output pins. In MCU expanded modes of operation, these pins provide the expanded address XADDR[19:14] for the external bus.

#### 2.3.34 PM7 / TXCAN3 / TXCAN4 — Port M I/O Pin 7

PM7 is a general purpose input or output pin. It can be configured as the transmit pin TXCAN of the Motorola Scalable Controller Area Network controllers 3 or 4 (CAN3 or CAN4).

#### 2.3.35 PM6 / RXCAN3 / RXCAN4 — Port M I/O Pin 6

PM6 is a general purpose input or output pin. It can be configured as the receive pin RXCAN of the Motorola Scalable Controller Area Network controllers 3 or 4 (CAN3 or CAN4).

#### 2.3.36 PM5 / TXCAN2 / TXCAN0 / TXCAN4 / SCK0 — Port M I/O Pin 5

PM5 is a general purpose input or output pin. It can be configured as the transmit pin TXCAN of the Motorola Scalable Controller Area Network controllers 2, 0 or 4 (CAN2, CAN0 or CAN4). It can be configured as the serial clock pin SCK of the Serial Peripheral Interface 0 (SPI0).

#### 2.3.37 PM4 / RXCAN2 / RXCAN0 / RXCAN4/ MOSI0 — Port M I/O Pin 4

PM4 is a general purpose input or output pin. It can be configured as the receive pin RXCAN of the Motorola Scalable Controller Area Network controllers 2, 0 or 4 (CAN2, CAN0 or CAN4). It can be configured as the master output (during master mode) or slave input pin (during slave mode) MOSI for the Serial Peripheral Interface 0 (SPI0).

# MC9S12DP256B Device User Guide b ld Rdi Honnet bsnq+ Hhb-

### 2.4.1 VDDX,VSSX — Power & Ground Pins for I/O Drivers

External power and ground for I/O drivers. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. Bypass requirements depend on how heavily the MCU pins are loaded.

# 2.4.2 VDDR, VSSR — Power & Ground Pins for I/O Drivers & for Internal Voltage Regulator

External power and ground for I/O drivers and input to the internal voltage regulator. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. Bypass requirements depend on how heavily the MCU pins are loaded.

## 2.4.3 VDD1, VDD2, VSS1, VSS2 — Core Power Pins

Power is supplied to the MCU through VDD and VSS. Because fast signal transitions place high, short-duration current demands on the power supply, use bypass capacitors with high-frequency characteristics and place them as close to the MCU as possible. This 2.5V supply is derived from the internal voltage regulator. There is no static load on those pins allowed. The internal voltage regulator is turned off, if VREGEN is tied to ground.

**NOTE:** No load allowed except for bypass capacitors.

## 2.4.4 VDDA, VSSA — Power Supply Pins for ATD and VREG

VDDA, VSSA are the power supply and ground input pins for the voltage regulator and the analog to digital converter. It also provides the reference for the internal voltage regulator. This allows the supply voltage to the ATD and the reference voltage to be bypassed independently.

## 2.4.5 VRH, VRL — ATD Reference Voltage Input Pins

VRH and VRL are the reference voltage input pins for the analog to digital converter.

## 2.4.6 VDDPLL, VSSPLL — Power Supply Pins for PLL

Provides operating voltage and ground for the Oscillator and the Phased-Locked Loop. This allows the supply voltage to the Oscillator and PLL to be bypassed independently. This 2.5V voltage is generated by the internal voltage regulator.

**NOTE:** No load allowed except for bypass capacitors.

This module supports single-cycle misaligned word accesses.

## **Section 18 MSCAN Block Description**

There are five MSCAN modules (CAN4, CAN3, CAN2, CAN1 and CAN0) implemented on the MC9S12DP256B. Consult the MSCAN Block User Guide for information about the Motorola Scalable CAN Module.

## Section 19 Port Integration Module (PIM) Block Description

Consult the PIM\_9DP256 Block User Guide for information about the Port Integration Module.

## Section 20 Voltage Regulator (VREG) Block Description

Consult the VREG Block User Guide for information about the dual output linear voltage regulator.

| Component | Purpose             | Туре          | Value            |

|-----------|---------------------|---------------|------------------|

| C1        | VDD1 filter cap     | ceramic X7R   | 100 220nF        |

| C2        | VDD2 filter cap     | ceramic X7R   | 100 220nF        |

| C3        | VDDA filter cap     | ceramic X7R   | 100nF            |

| C4        | VDDR filter cap     | X7R/tantalum  | >=100nF          |

| C5        | VDDPLL filter cap   | ceramic X7R   | 100nF            |

| C6        | VDDX filter cap     | X7R/tantalum  | >=100nF          |

| C7        | OSC load cap        |               |                  |

| C8        | OSC load cap        |               |                  |

| C9        | PLL loop filter cap |               |                  |

| C10       | PLL loop filter cap | Soo DLL apopi | fication chapter |

| C11       | DC cutoff cap       | See PLL Speci | fication chapter |

| R1        | PLL loop filter res |               |                  |

| Q1        | Quartz              |               |                  |

The PCB must be carefully laid out to ensure proper operation of the voltage regulator as well as of the MCU itself. The following rules must be observed:

## A.1.4 Current Injection

Power supply must maintain regulation within operating  $V_{DD5}$  or  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > V_{DD5}$ ) is greater than  $I_{DD5}$ , the injection current may flow out of VDD5 and could result in external power supply going out of regulation. Ensure external VDD5 load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power; e.g. if no system clock is present, or if clock rate is very low which would reduce overall power consumption.

## A.1.5 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only. A functional operation under or outside those maxima is not guaranteed. Stress beyond those limits may affect the reliability or cause permanent damage of the device.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either V<sub>SS5</sub> or V<sub>DD5</sub>).

Table A-1 Absolute Maximum Ratings<sup>1</sup>

| Num | Rating                                                                               | Symbol             | Min         | Max  | Unit |

|-----|--------------------------------------------------------------------------------------|--------------------|-------------|------|------|

| 1   | I/O, Regulator and Analog Supply Voltage                                             | V <sub>DD5</sub>   | -0.3        | 6.0  | V    |

| 2   | Digital Logic Supply Voltage <sup>2</sup>                                            | V <sub>DD</sub>    | -0.3        | 3.0  | V    |

| 3   | PLL Supply Voltage <sup>2</sup>                                                      | V <sub>DDPLL</sub> | -0.3        | 3.0  | V    |

| 4   | Voltage difference VDDX to VDDR and VDDA                                             | $\Delta_{VDDX}$    | -0.3        | 0.3  | V    |

| 5   | Voltage difference VSSX to VSSR and VSSA                                             | $\Delta_{VSSX}$    | -0.3        | 0.3  | V    |

| 6   | Digital I/O Input Voltage                                                            | V <sub>IN</sub>    | -0.3        | 6.0  | V    |

| 7   | Analog Reference                                                                     | $V_{RH,}V_{RL}$    | -0.3        | 6.0  | V    |

| 8   | XFC, EXTAL, XTAL inputs                                                              | V <sub>ILV</sub>   | -0.3        | 3.0  | V    |

| 9   | TEST input                                                                           | V <sub>TEST</sub>  | -0.3        | 10.0 | V    |

| 10  | Instantaneous Maximum Current Single pin limit for all digital I/O pins <sup>3</sup> | I <sub>D</sub>     | -25         | +25  | mA   |

| 11  | Instantaneous Maximum Current Single pin limit for XFC, EXTAL, XTAL <sup>4</sup>     | I <sub>DL</sub>    | -25         | +25  | mA   |

| 12  | Instantaneous Maximum Current Single pin limit for TEST 5                            | I <sub>DT</sub>    | -0.25       | 0    | mA   |

| 13  | Storage Temperature Range                                                            | T <sub>stg</sub>   | <b>–</b> 65 | 155  | °C   |

NOTES:

<sup>1.</sup> Beyond absolute maximum ratings device might be damaged.

## A.1.7 Operating Conditions

This chapter describes the operating conditions of the device. Unless otherwise noted those conditions apply to all the following data.

**NOTE:** Please refer to the temperature rating of the device (C, V, M) with regards to the ambient temperature  $T_A$  and the junction temperature  $T_J$ . For power dissipation calculations refer to **Section A.1.8 Power Dissipation and Thermal** Characteristics.

**Table A-4 Operating Conditions**

| Rating                                           | Symbol             | Min  | Тур | Max  | Unit |

|--------------------------------------------------|--------------------|------|-----|------|------|

| I/O, Regulator and Analog Supply Voltage         | $V_{DD5}$          | 4.5  | 5   | 5.25 | V    |

| Digital Logic Supply Voltage <sup>1</sup>        | $V_{DD}$           | 2.35 | 2.5 | 2.75 | V    |

| PLL Supply Voltage <sup>2</sup>                  | V <sub>DDPLL</sub> | 2.35 | 2.5 | 2.75 | V    |

| Voltage Difference VDDX to VDDR and VDDA         | $\Delta_{VDDX}$    | -0.1 | 0   | 0.1  | V    |

| Voltage Difference VSSX to VSSR and VSSA         | $\Delta_{VSSX}$    | -0.1 | 0   | 0.1  | V    |

| Oscillator                                       | f <sub>osc</sub>   | 0.5  | -   | 16   | MHz  |

| Bus Frequency                                    | f <sub>bus</sub>   | 0.5  | -   | 25   | MHz  |

| MC9S12DP256B <b>C</b>                            |                    |      |     |      |      |

| Operating Junction Temperature Range             | $T_J$              | -40  | -   | 100  | °C   |

| Operating Ambient Temperature Range <sup>2</sup> | T <sub>A</sub>     | -40  | 27  | 85   | °C   |

| MC9S12DP256B <b>V</b>                            |                    |      |     |      |      |

| Operating Junction Temperature Range             | $T_J$              | -40  | -   | 120  | °C   |

| Operating Ambient Temperature Range <sup>2</sup> | T <sub>A</sub>     | -40  | 27  | 105  | °C   |

| MC9S12DP256B <b>M</b>                            |                    |      |     |      |      |

| Operating Junction Temperature Range             | $T_J$              | -40  | -   | 140  | °C   |

| Operating Ambient Temperature Range <sup>2</sup> | T <sub>A</sub>     | -40  | 27  | 125  | °C   |

#### NOTES:

## A.1.8 Power Dissipation and Thermal Characteristics

Power dissipation and thermal characteristics are closely related. The user must assure that the maximum operating junction temperature is not exceeded. The average chip-junction temperature  $(T_J)$  in  ${}^{\circ}C$  can be obtained from:

The device contains an internal voltage regulator to generate the logic and PLL supply out of the I/O supply. The

absolute maximum ratings apply when this regulator is disabled and the device is powered from an external

source.

<sup>2.</sup> Please refer to **Section A.1.8 Power Dissipation and Thermal Characteristics** for more details about the relation between ambient temperature T<sub>A</sub> and device junction temperature T<sub>J</sub>.

# MC9S12DP256B Device User Guide bold RdI Honnet banq+ Hrb-

#### A.5.1.4 Stop Recovery

Out of STOP the controller can be woken up by an external interrupt. A clock quality check as after POR is performed before releasing the clocks to the system.

#### A.5.1.5 Pseudo Stop and Wait Recovery

The recovery from Pseudo STOP and Wait are essentially the same since the oscillator was not stopped in both modes. The controller can be woken up by internal or external interrupts. After  $t_{wrs}$  the CPU starts fetching the interrupt vector.

#### A.5.2 Oscillator

The device features an internal Colpitts oscillator. By asserting the  $\overline{XCLKS}$  input during reset this oscillator can be bypassed allowing the input of a square wave. Before asserting the oscillator to the internal system clocks the quality of the oscillation is checked for each start from either power-on, STOP or oscillator fail.  $t_{CQOUT}$  specifies the maximum time before switching to the internal self clock mode after POR or STOP if a proper oscillation is not detected. The quality check also determines the minimum oscillator start-up time  $t_{UPOSC}$ . The device also features a clock monitor. A Clock Monitor Failure is asserted if the frequency of the incoming clock signal is below the Assert Frequency  $t_{CMFA}$ .

**Table A-15 Oscillator Characteristics**

| Condit | ions | s are shown in <b>Table A-4</b> unless otherwise noted   |                     |      |                |                  |      |

|--------|------|----------------------------------------------------------|---------------------|------|----------------|------------------|------|

| Num    | С    | Rating                                                   | Symbol              | Min  | Тур            | Max              | Unit |

| 1      | С    | Crystal oscillator range                                 | fosc                | 0.5  |                | 16               | MHz  |

| 2      | Р    | Startup Current                                          | iosc                | 100  |                |                  | μА   |

| 3      | С    | Oscillator start-up time                                 | t <sub>UPOSC</sub>  |      | 8 <sup>1</sup> | 100 <sup>2</sup> | ms   |

| 4      | D    | Clock Quality check time-out                             | tcqout              | 0.45 |                | 2.5              | S    |

| 5      | Р    | Clock Monitor Failure Assert Frequency                   | f <sub>CMFA</sub>   | 50   | 100            | 200              | KHz  |

| 6      | Р    | External square wave input frequency <sup>3</sup>        | f <sub>EXT</sub>    | 0.5  |                | 50               | MHz  |

| 7      | D    | External square wave pulse width low                     | t <sub>EXTL</sub>   | 9.5  |                |                  | ns   |

| 8      | D    | External square wave pulse width high                    | t <sub>EXTH</sub>   | 9.5  |                |                  | ns   |

| 9      | D    | External square wave rise time                           | t <sub>EXTR</sub>   |      |                | 1                | ns   |

| 10     | D    | External square wave fall time                           | t <sub>EXTF</sub>   |      |                | 1                | ns   |

| 11     | D    | Input Capacitance (EXTAL, XTAL pins)                     | C <sub>IN</sub>     |      | 9              |                  | pF   |

| 12     | С    | DC Operating Bias in Colpitts Configuration on EXTAL Pin | V <sub>DCBIAS</sub> |      | 1.1            |                  | V    |

#### NOTES:

- 1.  $f_{osc} = 4MHz$ , C = 22pF.

- 2. Maximum value is for extreme cases using high Q, low frequency crystals

- 3. XCLKS =0 during reset

## A.7 SPI

#### A.7.1 Master Mode

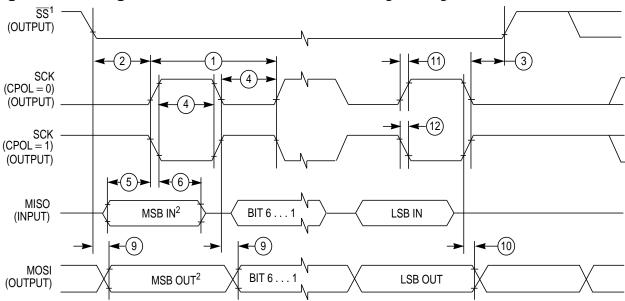

Figure A-5 and Figure A-6 illustrate the master mode timing. Timing values are shown in Table A-18.

<sup>1.</sup> If configured as output.

Figure A-5 SPI Master Timing (CPHA = 0)

<sup>2.</sup> LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

# MC9S12DP256B Device User Guide by ld RdI Honnet bsnq+ Hhb-

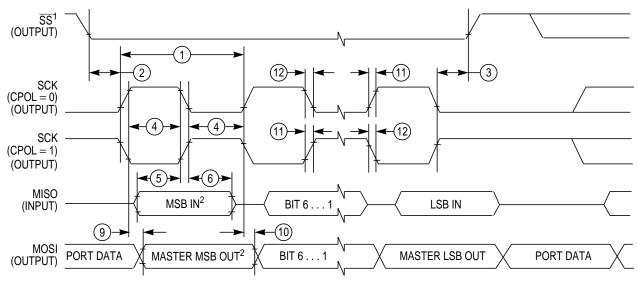

- 1. If configured as output

- 2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

Figure A-6 SPI Master Timing (CPHA =1)

## Table A-18 SPI Master Mode Timing Characteristics<sup>1</sup>

| Condit | ions | s are shown in <b>Table A-4</b> unless otherwise noted, $C_{LO}$ | <sub>AD</sub> = 200pF o | n all outputs         |     |                       |                  |

|--------|------|------------------------------------------------------------------|-------------------------|-----------------------|-----|-----------------------|------------------|

| Num    | С    | Rating                                                           | Symbol                  | Min                   | Тур | Max                   | Unit             |

| 1      | Р    | Operating Frequency                                              | f <sub>op</sub>         | DC                    |     | 1/4                   | f <sub>bus</sub> |

| 1      | Р    | SCK Period t <sub>sck</sub> = 1./f <sub>op</sub>                 | t <sub>sck</sub>        | 4                     |     | 2048                  | t <sub>bus</sub> |

| 2      | D    | Enable Lead Time                                                 | t <sub>lead</sub>       | 1/2                   |     | _                     | t <sub>sck</sub> |

| 3      | D    | Enable Lag Time                                                  | t <sub>lag</sub>        | 1/2                   |     |                       | t <sub>sck</sub> |

| 4      | D    | Clock (SCK) High or Low Time                                     | t <sub>wsck</sub>       | t <sub>bus</sub> - 30 |     | 1024 t <sub>bus</sub> | ns               |

| 5      | D    | Data Setup Time (Inputs)                                         | t <sub>su</sub>         | 25                    |     |                       | ns               |

| 6      | D    | Data Hold Time (Inputs)                                          | t <sub>hi</sub>         | 0                     |     |                       | ns               |

| 9      | D    | Data Valid (after Enable Edge)                                   | t <sub>v</sub>          |                       |     | 25                    | ns               |

| 10     | D    | Data Hold Time (Outputs)                                         | t <sub>ho</sub>         | 0                     |     |                       | ns               |

| 11     | D    | Rise Time Inputs and Outputs                                     | t <sub>r</sub>          |                       |     | 25                    | ns               |

| 12     | D    | Fall Time Inputs and Outputs                                     | t <sub>f</sub>          |                       |     | 25                    | ns               |

#### NOTES:

1. The numbers 7, 8 in the column labeled "Num" are missing. This has been done on purpose to be consistent between the Master and the Slave timing shown in **Table A-19**.

# MC9S12DP256B Device User Guide by ld RdI Honnet bsnq+ Hrb-

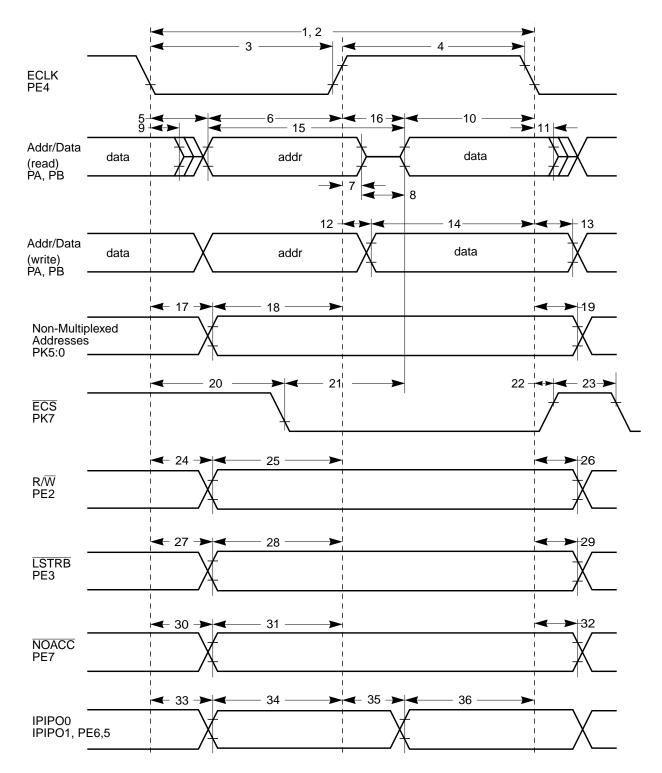

Figure A-9 General External Bus Timing