Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HCS12                                                        |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 25MHz                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                           |

| Peripherals                | PWM, WDT                                                     |

| Number of I/O              | 91                                                           |

| Program Memory Size        | 256KB (256K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 4K x 8                                                       |

| RAM Size                   | 12K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                |

| Data Converters            | A/D 16x10b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 112-LQFP                                                     |

| Supplier Device Package    | 112-LQFP (20x20)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12dg256ccpv |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

MC9S12DP256B Device User Guide 9512DP256BDG V2/D V02.14

| Section 7 Clock and Reset Generator (CRG) Block Description   7.1 Device-specific information |

|-----------------------------------------------------------------------------------------------|

| 7.1.1   XCLKS                                                                                 |

| Section 8 Enhanced Capture Timer (ECT) Block Description                                      |

| Section 9 Analog to Digital Converter (ATD) Block Description                                 |

| Section 10 Inter-IC Bus (IIC) Block Description                                               |

| Section 11 Serial Communications Interface (SCI) Block Description                            |

| Section 12 Serial Peripheral Interface (SPI) Block Description                                |

| Section 13 J1850 (BDLC) Block Description                                                     |

| Section 14 Pulse Width Modulator (PWM) Block Description                                      |

| Section 15 Flash EEPROM 256K Block Description                                                |

| Section 16 EEPROM 4K Block Description                                                        |

| Section 17 RAM Block Description                                                              |

| Section 18 MSCAN Block Description                                                            |

| Section 19 Port Integration Module (PIM) Block Description                                    |

| Section 20 Voltage Regulator (VREG) Block Description                                         |

| Appendix A Electrical Characteristics                                                         |

| A.1 General                                                                                   |

| A. I  | General                                |

|-------|----------------------------------------|

| A.1.1 | Parameter Classification               |

| A.1.2 | Power Supply                           |

| A.1.3 | Pins                                   |

| A.1.4 | Current Injection                      |

| A.1.5 | Absolute Maximum Ratings               |

| A.1.6 | ESD Protection and Latch-up Immunity90 |

|       |                                        |

- 5V A/D converter inputs

- Operation at 50MHz equivalent to 25MHz Bus Speed

- Development support

- Single-wire background debug<sup>TM</sup> mode (BDM)

- On-chip hardware breakpoints

## **1.3 Modes of Operation**

User modes

- Normal and Emulation Operating Modes

- Normal Single-Chip Mode

- Normal Expanded Wide Mode

- Normal Expanded Narrow Mode

- Emulation Expanded Wide Mode

- Emulation Expanded Narrow Mode

- Special Operating Modes

- Special Single-Chip Mode with active Background Debug Mode

- Special Test Mode (Motorola use only)

- Special Peripheral Mode (Motorola use only)

### Low power modes

- Stop Mode

- Pseudo Stop Mode

- Wait Mode

## 1.6 Detailed Register Map

The following tables show the detailed register map of the MC9S12DP256B.

### \$0000 - \$000F

### MEBI map 1 of 3 (Core User Guide)

| Address | Name     |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| \$0000  | PORTA    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0001  | PORTB    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0002  | DDRA     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0003  | DDRB     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$0004  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0005  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0006  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0007  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0008  | PORTE    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | Bit 1 | Bit 0 |

| \$0009  | DDRE     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | Bit 2 | 0     | 0     |

| \$000A  | PEAR     | Read:<br>Write: | NOACCE | 0     | PIPOE | NECLK | LSTRE | RDWE  | 0     | 0     |

| \$000B  | MODE     | Read:<br>Write: | MODC   | MODB  | MODA  | 0     | IVIS  | 0     | EMK   | EME   |

| \$000C  | PUCR     | Read:<br>Write: | PUPKE  | 0     | 0     | PUPEE | 0     | 0     | PUPBE | PUPAE |

| \$000D  | RDRIV    | Read:<br>Write: | RDPK   | 0     | 0     | RDPE  | 0     | 0     | RDPB  | RDPA  |

| \$000E  | EBICTL   | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | ESTR  |

| \$000F  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

### \$0010 - \$0014

## MMC map 1 of 4 (Core User Guide)

| Address | Name   |        | Bit 7   | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  |

|---------|--------|--------|---------|-------|---------|-------|-------|-------|-------|--------|

| \$0010  | INITRM | Read:  | RAM15   | RAM14 | RAM13   | RAM12 | RAM11 | 0     | 0     | RAMHAL |

| \$0010  |        | Write: | INAIM13 |       | INAIM13 |       |       |       |       |        |

| \$0011  | INITRG | Read:  | 0       | REG14 | REG13   | REG12 | REG11 | 0     | 0     | 0      |

| \$0011  | INTRO  | Write: |         | NL014 | KLG13   | NL012 | KL011 |       |       |        |

### Freescale Semiconductor, Inc. MC9S12DP256B Device User Guide — V02.14

### \$001E - \$001E

Address

\$001E

### MEBI map 2 of 3 (Core User Guide)

| Name  | [      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| INTCR | Read:  | IRQE  | IRQEN | 0     | 0     | 0     | 0     | 0     | 0     |

| INTOR | Write: | INQE  | INQEN |       |       |       |       |       |       |

### \$001F - \$001F

## INT map 2 of 2 (Core User Guide)

| Address | Name  |        | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|--------|-------|-------|-------|--------|-------|-------|-------|-------|

| \$001F  | HPRIO | Read:  | PSEL7 | PSEL6 | PSEL5 | PSEL4  | PSEL3 | PSEL2 | PSEL1 | 0     |

| φυστη   | IFRIO | Write: | FSEL/ | FSELO | FOELD | F JEL4 | FOELO | FJELZ | FJELI |       |

### \$0020 - \$0027

### Reserved

| Address       | Name      | Γ      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| ¢0000         | Decembrad | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$0020        | Reserved  | Write: |       |       |       |       |       |       |       |       |

| \$0021        | Reserved  | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| φ002 I        | Reserveu  | Write: |       |       |       |       |       |       |       |       |

| \$0022        | Reserved  | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| ψ002Z         | Reserveu  | Write: |       |       |       |       |       |       |       |       |

| \$0023        | Reserved  | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| <b>00020</b>  | Reserved  | Write: |       |       |       |       |       |       |       |       |

| \$0024        | Reserved  | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| <b>\$602</b>  | Reserved  | Write: |       |       |       |       |       |       |       |       |

| \$0025        | Reserved  | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| <b>\$0020</b> | Reserved  | Write: |       |       |       |       |       |       |       |       |

| \$0026        | Reserved  | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| <b>00020</b>  | Reserved  | Write: |       |       |       |       |       |       |       |       |

| \$0027        | Reserved  | Read   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| ΨΟΟΖΙ         | Reserved  | Write: |       |       |       |       |       |       |       |       |

### \$0028 - \$002F

Address \$0028

\$0029

\$002A

\$002B

\$002C

## **BKP (Core User Guide)**

| _ | N I a una a |        | D:4 7  | D:4 0  | D:4 C   | D:4 4    | D:+ 0         | D:+ 0        | D:44   | D:+ 0  |  |

|---|-------------|--------|--------|--------|---------|----------|---------------|--------------|--------|--------|--|

| 5 | Name        |        | Bit 7  | Bit 6  | Bit 5   | Bit 4    | Bit 3         | Bit 2        | Bit 1  | Bit 0  |  |

|   | BKPCT0      | Read:  | BKEN   | BKFULL | BKBDM   | BKTAG    | 0             | 0            | 0      | 0      |  |

|   | DRICIO      | Write: | DICLIN |        | DIADDIM | DIVIAO   |               |              |        |        |  |

|   | BKPCT1      | Read:  | вкомвн | BK0MBL | BK1MBH  | BK1MBL   | <b>BKORWE</b> | <b>BK0RW</b> | BK1RWE | BK1RW  |  |

|   | DRECTI      | Write: | DRONDI | DROMDL |         | DIVINIDE | DROITVL       | DROIN        | DRINVL | DIVITY |  |

|   | BKP0X       | Read:  | 0      | 0      | BK0V5   | BK0V4    | BK0V3         | BK0V2        | BK0V1  | BK0V0  |  |

|   | DKFUA       | Write: |        |        | BRUVS   | DR0V4    | DR0V3         | DRUVZ        | BRUVI  | BRUVU  |  |

|   |             | Read:  | Bit 15 | 14     | 13      | 12       | 11            | 10           | 9      | Bit 8  |  |

|   | BKP0H       | Write: | DILTO  | 14     | 15      | 12       | 11            | 10           | 9      | DILO   |  |

|   | DICDOL      | Read:  |        | 6      | F       | 4        | 2             | 2            | 4      |        |  |

|   | BKP0L       | Write: | Bit 7  | 6      | 5       | 4        | 3             | 2            | 1      | Bit 0  |  |

\$0040 - \$007F

## ECT (Enhanced Capture Timer 16 Bit 8 Channels)

| Address | Name       |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4      | Bit 3     | Bit 2 | Bit 1 | Bit 0 |

|---------|------------|-----------------|--------|-------|-------|------------|-----------|-------|-------|-------|

| \$0053  | TC1 (lo)   | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0054  | TC2 (hi)   | Read:<br>Write: | Bit 15 | 14    | 13    | 12         | 11        | 10    | 9     | Bit 8 |

| \$0055  | TC2 (lo)   | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0056  | TC3 (hi)   | Read:<br>Write: | Bit 15 | 14    | 13    | 12         | 11        | 10    | 9     | Bit 8 |

| \$0057  | TC3 (lo)   | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0058  | TC4 (hi)   | Read:<br>Write: | Bit 15 | 14    | 13    | 12         | 11        | 10    | 9     | Bit 8 |

| \$0059  | TC4 (lo)   | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$005A  | TC5 (hi)   | Read:<br>Write: | Bit 15 | 14    | 13    | 12         | 11        | 10    | 9     | Bit 8 |

| \$005B  | TC5 (lo)   | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$005C  | TC6 (hi)   | Read:<br>Write: | Bit 15 | 14    | 13    | 12         | 11        | 10    | 9     | Bit 8 |

| \$005D  | TC6 (lo)   | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$005E  | TC7 (hi)   | Read:<br>Write: | Bit 15 | 14    | 13    | 12         | 11        | 10    | 9     | Bit 8 |

| \$005F  | TC7 (lo)   | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0060  | PACTL      | Read:<br>Write: | 0      | PAEN  | PAMOD | PEDGE      | CLK1      | CLK0  | PAOVI | PAI   |

| \$0061  | PAFLG      | Read:<br>Write: | 0      | 0     | 0     | 0          | 0         | 0     | PAOVF | PAIF  |

| \$0062  | PACN3 (hi) | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0063  | PACN2 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0064  | PACN1 (hi) | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0065  | PACN0 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4          | 3         | 2     | 1     | Bit 0 |

| \$0066  | MCCTL      | Read:<br>Write: | MCZI   | MODMC | RDMCL | 0<br>ICLAT | 0<br>FLMC | MCEN  | MCPR1 | MCPR0 |

| \$0067  | MCFLG      | Read:<br>Write: | MCZF   | 0     | 0     | 0          | POLF3     | POLF2 | POLF1 | POLF0 |

| \$0068  | ICPAR      | Read:<br>Write: | 0      | 0     | 0     | 0          | PA3EN     | PA2EN | PA1EN | PA0EN |

| \$0069  | DLYCT      | Read:<br>Write: | 0      | 0     | 0     | 0          | 0         | 0     | DLY1  | DLY0  |

| \$006A  | ICOVW      | Read:<br>Write: | NOVW7  | NOVW6 | NOVW5 | NOVW4      | NOVW3     | NOVW2 | NOVW1 | NOVW0 |

| \$006B  | ICSYS      | Read:<br>Write: | SH37   | SH26  | SH15  | SH04       | TFMOD     | PACMX | BUFEN | LATQ  |

### Freescale Semiconductor, Inc. MC9S12DP256B Device User Guide — V02.14

| Pin Name | Power  |               | nal Pull<br>sistor | Description                                              |

|----------|----------|----------|----------|----------|--------|---------------|--------------------|----------------------------------------------------------|

| Funct. 1 | Funct. 2 | Funct. 3 | Funct. 4 | Funct. 5 | Supply | CTRL          | Reset<br>State     | Description                                              |

| PP6      | KWP6     | PWM6     | SS2      | _        | VDDX   | PERP/<br>PPSP | Disabled           | Port P I/O, Interrupt, Channel 6 of PWM, SS of SPI2      |

| PP5      | KWP5     | PWM5     | MOSI2    | _        | VDDX   | PERP/<br>PPSP | Disabled           | Port P I/O, Interrupt, Channel 5 of PWM, MOSI of SPI2    |

| PP4      | KWP4     | PWM4     | MISO2    | _        | VDDX   | PERP/<br>PPSP | Disabled           | Port P I/O, Interrupt, Channel 4 of PWM, MISO2 of SPI2   |

| PP3      | KWP3     | PWM3     | SS1      | _        | VDDX   | PERP/<br>PPSP | Disabled           | Port P I/O, Interrupt, Channel 3 of PWM, SS of SPI1      |

| PP2      | KWP2     | PWM2     | SCK1     | _        | VDDX   | PERP/<br>PPSP | Disabled           | Port P I/O, Interrupt, Channel 2 of<br>PWM, SCK of SPI1  |

| PP1      | KWP1     | PWM1     | MOSI1    | _        | VDDX   | PERP/<br>PPSP | Disabled           | Port P I/O, Interrupt, Channel 1 of<br>PWM, MOSI of SPI1 |

| PP0      | KWP0     | PWM0     | MISO1    | _        | VDDX   | PERP/<br>PPSP | Disabled           | Port P I/O, Interrupt, Channel 0 of PWM, MISO2 of SPI1   |

| PS7      | SS0      | _        | _        | _        | VDDX   | PERS/<br>PPSS | Up                 | Port S I/O, SS of SPI0                                   |

| PS6      | SCK0     | _        | _        | _        | VDDX   | PERS/<br>PPSS | Up                 | Port S I/O, SCK of SPI0                                  |

| PS5      | MOSI0    | _        | _        | _        | VDDX   | PERS/<br>PPSS | Up                 | Port S I/O, MOSI of SPI0                                 |

| PS4      | MISO0    |          |          | _        | VDDX   | PERS/<br>PPSS | Up                 | Port S I/O, MISO of SPI0                                 |

| PS3      | TXD1     | _        | _        | _        | VDDX   | PERS/<br>PPSS | Up                 | Port S I/O, TXD of SCI1                                  |

| PS2      | RXD1     | —        | —        | —        | VDDX   | PERS/<br>PPSS | Up                 | Port S I/O, RXD of SCI1                                  |

| PS1      | TXD0     | _        |          |          | VDDX   | PERS/<br>PPSS | Up                 | Port S I/O, TXD of SCI0                                  |

| PS0      | RXD0     | _        |          |          | VDDX   | PERS/<br>PPSS | Up                 | Port S I/O, RXD of SCI0                                  |

| PT[7:0]  | IOC[7:0] | _        |          |          | VDDX   | PERT/<br>PPST | Disabled           | Port T I/O, Timer channels                               |

## 2.3 Detailed Signal Descriptions

## 2.3.1 EXTAL, XTAL — Oscillator Pins

EXTAL and XTAL are the crystal driver and external clock pins. On reset all the device clocks are derived from the EXTAL input frequency. XTAL is the crystal output.

| VREGEN | VREGEN Description                                                                           |  |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1      | Internal Voltage Regulator enabled                                                           |  |  |  |  |  |

| 0      | Internal Voltage Regulator disabled, VDD1,2 and VDDPLL must be supplied externally with 2.5V |  |  |  |  |  |

## Table 4-3 Voltage Regulator VREGEN

## 4.3 Security

The device will make available a security feature preventing the unauthorized read and write of the memory contents. This feature allows:

- Protection of the contents of FLASH,

- Protection of the contents of EEPROM,

- Operation in single-chip mode,

- Operation from external memory with internal FLASH and EEPROM disabled.

The user must be reminded that part of the security must lie with the user's code. An extreme example would be user's code that dumps the contents of the internal program. This code would defeat the purpose of security. At the same time the user may also wish to put a back door in the user's program. An example of this is the user downloads a key through the SCI which allows access to a programming routine that updates parameters stored in EEPROM.

## 4.3.1 Securing the Microcontroller

Once the user has programmed the FLASH and EEPROM (if desired), the part can be secured by programming the security bits located in the FLASH module. These non-volatile bits will keep the part secured through resetting the part and through powering down the part.

The security byte resides in a portion of the Flash array.

Check the Flash Block User Guide for more details on the security configuration.

## 4.3.2 Operation of the Secured Microcontroller

## 4.3.2.1 Normal Single Chip Mode

This will be the most common usage of the secured part. Everything will appear the same as if the part was not secured with the exception of BDM operation. The BDM operation will be blocked.

## 4.3.2.2 Executing from External Memory

The user may wish to execute from external space with a secured microcontroller. This is accomplished by resetting directly into expanded mode. The internal FLASH and EEPROM will be disabled. BDM operations will be blocked.

# Section 10 Inter-IC Bus (IIC) Block Description

Consult the IIC Block User Guide for information about the Inter-IC Bus module.

# Section 11 Serial Communications Interface (SCI) Block Description

There are two Serial Communications Interfaces (SCI1 and SCI0) implemented on the MC9S12DP256B device. Consult the SCI Block User Guide for information about each Serial Communications Interface module.

# Section 12 Serial Peripheral Interface (SPI) Block Description

There are three Serial Peripheral Interfaces(SPI2, SPI1 and SPI0) implemented on MC9S12DP256B. Consult the SPI Block User Guide for information about each Serial Peripheral Interface module.

# Section 13 J1850 (BDLC) Block Description

Consult the BDLC Block User Guide for information about the J1850 module.

# Section 14 Pulse Width Modulator (PWM) Block Description

Consult the PWM\_8B8C Block User Guide for information about the Pulse Width Modulator module.

# Section 15 Flash EEPROM 256K Block Description

Consult the FTS256K Block User Guide for information about the flash module.

# Section 16 EEPROM 4K Block Description

Consult the EETS4K Block User Guide for information about the EEPROM module.

## Section 17 RAM Block Description

This module supports single-cycle misaligned word accesses.

# Section 18 MSCAN Block Description

There are five MSCAN modules (CAN4, CAN3, CAN2, CAN1 and CAN0) implemented on the MC9S12DP256B. Consult the MSCAN Block User Guide for information about the Motorola Scalable CAN Module.

## Section 19 Port Integration Module (PIM) Block Description

Consult the PIM\_9DP256 Block User Guide for information about the Port Integration Module.

# Section 20 Voltage Regulator (VREG) Block Description

Consult the VREG Block User Guide for information about the dual output linear voltage regulator.

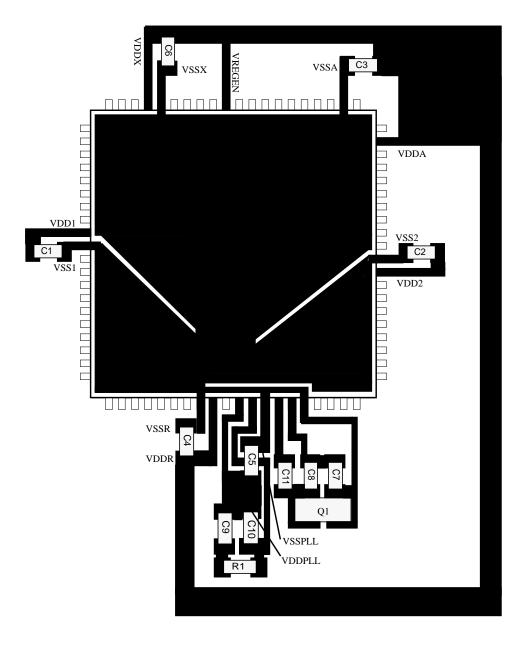

| Component | Purpose             | Туре                            | Value     |  |  |

|-----------|---------------------|---------------------------------|-----------|--|--|

| C1        | VDD1 filter cap     | ceramic X7R                     | 100 220nF |  |  |

| C2        | VDD2 filter cap     | ceramic X7R                     | 100 220nF |  |  |

| C3        | VDDA filter cap     | ceramic X7R                     | 100nF     |  |  |

| C4        | VDDR filter cap     | X7R/tantalum                    | >=100nF   |  |  |

| C5        | VDDPLL filter cap   | ceramic X7R                     | 100nF     |  |  |

| C6        | VDDX filter cap     | X7R/tantalum                    | >=100nF   |  |  |

| C7        | OSC load cap        |                                 |           |  |  |

| C8        | OSC load cap        |                                 |           |  |  |

| C9        | PLL loop filter cap |                                 |           |  |  |

| C10       | PLL loop filter cap |                                 |           |  |  |

| C11       | DC cutoff cap       | - See PLL specification chapter |           |  |  |

| R1        | PLL loop filter res |                                 |           |  |  |

| Q1        | Quartz              |                                 |           |  |  |

The PCB must be carefully laid out to ensure proper operation of the voltage regulator as well as of the MCU itself. The following rules must be observed:

Figure 20-2 Recommended PCB Layout for 80QFP

- 2. The device contains an internal voltage regulator to generate the logic and PLL supply out of the I/O supply.

- The absolute maximum ratings apply when the device is powered from an external source.

- 3. All digital I/O pins are internally clamped to V<sub>SSX</sub> and V<sub>DDX</sub>, V<sub>SSR</sub> and V<sub>DDR</sub> or V<sub>SSA</sub> and V<sub>DDA</sub>.

- 4. Those pins are internally clamped to  $V_{SSPLL}$  and  $V_{DDPLL}$ . 5. This pin is clamped low to  $V_{SSPLL}$ , but not clamped high. This pin must be tied low in applications.

## A.1.6 ESD Protection and Latch-up Immunity

All ESD testing is in conformity with CDF-AEC-Q100 Stress test qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model.

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Model      | Description                                               | Symbol | Value       | Unit |

|------------|-----------------------------------------------------------|--------|-------------|------|

|            | Series Resistance                                         | R1     | 1500        | Ohm  |

|            | Storage Capacitance                                       | С      | 100         | pF   |

| Human Body | n Body<br>Number of Pulse per pin<br>positive<br>negative |        | -<br>3<br>3 |      |

|            | Series Resistance                                         | R1     | 0           | Ohm  |

|            | Storage Capacitance                                       | С      | 200         | pF   |

| Machine    | Number of Pulse per pin<br>positive<br>negative           |        | -<br>3<br>3 |      |

| Latab up   | Minimum input voltage limit                               |        | -2.5        | V    |

| Latch-up   | Maximum input voltage limit                               |        | 7.5         | V    |

### Table A-2 ESD and Latch-up Test Conditions

## Table A-3 ESD and Latch-Up Protection Characteristics

| Num | С | Rating                                                             | Symbol           | Min          | Max | Unit |

|-----|---|--------------------------------------------------------------------|------------------|--------------|-----|------|

| 1   | С | Human Body Model (HBM)                                             | V <sub>HBM</sub> | 2000         | -   | V    |

| 2   | С | Machine Model (MM)                                                 | V <sub>MM</sub>  | 200          | -   | V    |

| 3   | С | Charge Device Model (CDM)                                          | V <sub>CDM</sub> | 500          | -   | V    |

| 4   | с | Latch-up Current at T <sub>A</sub> = 125°C<br>positive<br>negative | I <sub>LAT</sub> | +100<br>-100 | -   | mA   |

| 5   | с | Latch-up Current at $T_A = 27^{\circ}C$<br>positive<br>negative    | I <sub>LAT</sub> | +200<br>-200 | -   | mA   |

## A.3 NVM, Flash and EEPROM

**NOTE:** Unless otherwise noted the abbreviation NVM (Non Volatile Memory) is used for both Flash and EEPROM.

## A.3.1 NVM timing

The time base for all NVM program or erase operations is derived from the oscillator. A minimum oscillator frequency  $f_{NVMOSC}$  is required for performing program or erase operations. The NVM modules do not have any means to monitor the frequency and will not prevent program or erase operation at frequencies above or below the specified minimum. Attempting to program or erase the NVM modules at a lower frequency a full program or erase transition is not assured.

The Flash and EEPROM program and erase operations are timed using a clock derived from the oscillator using the FCLKDIV and ECLKDIV registers respectively. The frequency of this clock must be set within the limits specified as  $f_{NVMOP}$ .

The minimum program and erase times shown in **Table A-11** are calculated for maximum  $f_{NVMOP}$  and maximum  $f_{bus}$ . The maximum times are calculated for minimum  $f_{NVMOP}$  and a  $f_{bus}$  of 2MHz.

## A.3.1.1 Single Word Programming

The programming time for single word programming is dependent on the bus frequency as a well as on the frequency  $f_{NVMOP}$  and can be calculated according to the following formula.

$$t_{swpgm} = 9 \cdot \frac{1}{f_{NVMOP}} + 25 \cdot \frac{1}{f_{bus}}$$

## A.3.1.2 Burst Programming

This applies only to the Flash where up to 32 words in a row can be programmed consecutively using burst programming by keeping the command pipeline filled. The time to program a consecutive word can be calculated as:

$$t_{bwpgm} = 4 \cdot \frac{1}{f_{NVMOP}} + 9 \cdot \frac{1}{f_{bus}}$$

The time to program a whole row is:

$$t_{brpgm} = t_{swpgm} + 31 \cdot t_{bwpgm}$$

Burst programming is more than 2 times faster than single word programming.

1. If configured as output

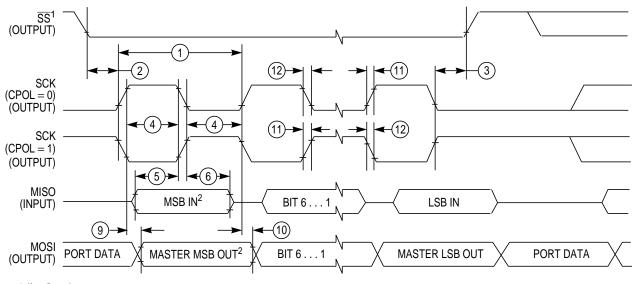

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

## Figure A-6 SPI Master Timing (CPHA =1)

| Table A-18 | SPI Master | Mode Timing | Characteristics <sup>1</sup> |

|------------|------------|-------------|------------------------------|

|------------|------------|-------------|------------------------------|

| Condit | Conditions are shown in <b>Table A-4</b> unless otherwise noted, C <sub>LOAD</sub> = 200pF on all outputs |                                                  |                   |                       |     |                       |                  |  |

|--------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------|-----------------------|-----|-----------------------|------------------|--|

| Num    | С                                                                                                         | Rating                                           | Symbol            | Min                   | Тур | Max                   | Unit             |  |

| 1      | Ρ                                                                                                         | Operating Frequency                              | f <sub>op</sub>   | DC                    |     | 1/4                   | f <sub>bus</sub> |  |

| 1      | Ρ                                                                                                         | SCK Period t <sub>sck</sub> = 1./f <sub>op</sub> | t <sub>sck</sub>  | 4                     |     | 2048                  | t <sub>bus</sub> |  |

| 2      | D                                                                                                         | Enable Lead Time                                 | t <sub>lead</sub> | 1/2                   |     | —                     | t <sub>sck</sub> |  |

| 3      | D                                                                                                         | Enable Lag Time                                  | t <sub>lag</sub>  | 1/2                   |     |                       | t <sub>sck</sub> |  |

| 4      | D                                                                                                         | Clock (SCK) High or Low Time                     | t <sub>wsck</sub> | t <sub>bus</sub> – 30 |     | 1024 t <sub>bus</sub> | ns               |  |

| 5      | D                                                                                                         | Data Setup Time (Inputs)                         | t <sub>su</sub>   | 25                    |     |                       | ns               |  |

| 6      | D                                                                                                         | Data Hold Time (Inputs)                          | t <sub>hi</sub>   | 0                     |     |                       | ns               |  |

| 9      | D                                                                                                         | Data Valid (after Enable Edge)                   | t <sub>v</sub>    |                       |     | 25                    | ns               |  |

| 10     | D                                                                                                         | Data Hold Time (Outputs)                         | t <sub>ho</sub>   | 0                     |     |                       | ns               |  |

| 11     | D                                                                                                         | Rise Time Inputs and Outputs                     | t <sub>r</sub>    |                       |     | 25                    | ns               |  |

| 12     | D                                                                                                         | Fall Time Inputs and Outputs                     | t <sub>f</sub>    |                       |     | 25                    | ns               |  |

NOTES:

1. The numbers 7, 8 in the column labeled "Num" are missing. This has been done on purpose to be consistent between the Master and the Slave timing shown in **Table A-19**.

| Condit | tions | s are shown in <b>Table A-4</b> unless otherwise noted, CL | OAD = 200pF       | on all outputs        |     |      |                  |

|--------|-------|------------------------------------------------------------|-------------------|-----------------------|-----|------|------------------|

| Num    | С     | Rating                                                     | Symbol            | Min                   | Тур | Max  | Unit             |

| 1      | Р     | Operating Frequency                                        | f <sub>op</sub>   | DC                    |     | 1/4  | f <sub>bus</sub> |

| 1      | Р     | SCK Period t <sub>sck</sub> = 1./f <sub>op</sub>           | t <sub>sck</sub>  | 4                     |     | 2048 | t <sub>bus</sub> |

| 2      | D     | Enable Lead Time                                           | t <sub>lead</sub> | 1                     |     |      | t <sub>cyc</sub> |

| 3      | D     | Enable Lag Time                                            | t <sub>lag</sub>  | 1                     |     |      | t <sub>cyc</sub> |

| 4      | D     | Clock (SCK) High or Low Time                               | t <sub>wsck</sub> | t <sub>cyc</sub> – 30 |     |      | ns               |

| 5      | D     | Data Setup Time (Inputs)                                   | t <sub>su</sub>   | 25                    |     |      | ns               |

| 6      | D     | Data Hold Time (Inputs)                                    | t <sub>hi</sub>   | 25                    |     |      | ns               |

| 7      | D     | Slave Access Time                                          | ta                |                       |     | 1    | t <sub>cyc</sub> |

| 8      | D     | Slave MISO Disable Time                                    | t <sub>dis</sub>  |                       |     | 1    | t <sub>cyc</sub> |

| 9      | D     | Data Valid (after SCK Edge)                                | t <sub>v</sub>    |                       |     | 25   | ns               |

| 10     | D     | Data Hold Time (Outputs)                                   | t <sub>ho</sub>   | 0                     |     |      | ns               |

| 11     | D     | Rise Time Inputs and Outputs                               | t <sub>r</sub>    |                       |     | 25   | ns               |

| 12     | D     | Fall Time Inputs and Outputs                               | t <sub>f</sub>    |                       |     | 25   | ns               |

## Table A-19 SPI Slave Mode Timing Characteristics

| Conditions are shown in <b>Table A-4</b> unless otherwise noted, C <sub>LOAD</sub> = 50pF |   |                                                                          |                  |     |     |     |      |

|-------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Num                                                                                       | С | Rating                                                                   | Symbol           | Min | Тур | Max | Unit |

| 32                                                                                        | D | NOACC hold time                                                          | t <sub>NOH</sub> | 2   |     |     | ns   |

| 33                                                                                        | D | IPIPO[1:0] delay time                                                    | t <sub>P0D</sub> | 2   |     | 7   | ns   |

| 34                                                                                        | D | IPIPO[1:0] valid time to E rise ( $PW_{EL}$ - $t_{P0D}$ )                | t <sub>P0V</sub> | 11  |     |     | ns   |

| 35                                                                                        | D | IPIPO[1:0] delay time <sup>1</sup> (PW <sub>EH</sub> -t <sub>P1V</sub> ) | t <sub>P1D</sub> | 2   |     | 25  | ns   |

| 36                                                                                        | D | IPIPO[1:0] valid time to E fall                                          | t <sub>P1V</sub> | 11  |     |     | ns   |

## Table A-20 Expanded Bus Timing Characteristics

NOTES:

1. Affected by clock stretch: add N x  $t_{cyc}$  where N=0,1,2 or 3, depending on the number of clock stretches.

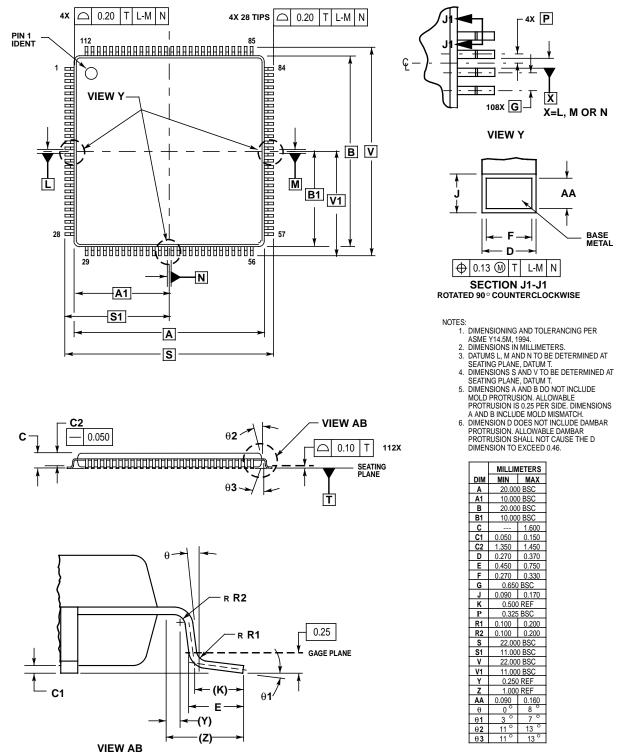

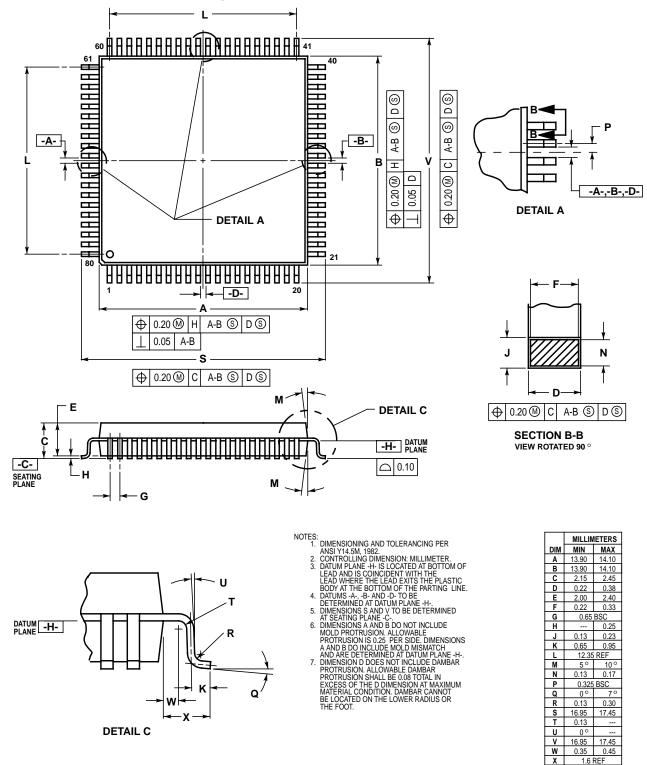

## B.2 112-pin LQFP package

Figure B-1 112-pin LQFP mechanical dimensions (case no. 987)

Semiconductor, Inc.

٩

reescal

(A) MOTOROLA

## B.3 80-pin QFP package