Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Active                                                        |

| Core Processor             | HC08                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | I <sup>2</sup> C, IRSCI, SPI                                  |

| Peripherals                | LCD, LVD, POR, PWM                                            |

| Number of I/O              | 40                                                            |

| Program Memory Size        | 24KB (24K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 768 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                     |

| Data Converters            | A/D 6x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 64-QFP                                                        |

| Supplier Device Package    | 64-QFP (14x14)                                                |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908lj24cfu |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **List of Sections**

| Section 1. General Description                                      |

|---------------------------------------------------------------------|

| Section 2. Memory Map49                                             |

| Section 3. Random-Access Memory (RAM)67                             |

| Section 4. FLASH Memory (FLASH)69                                   |

| Section 5. Configuration Registers (CONFIG)79                       |

| Section 6. Central Processor Unit (CPU)85                           |

| Section 7. Oscillator (OSC)                                         |

| Section 8. Clock Generator Module (CGM)109                          |

| Section 9. System Integration Module (SIM)139                       |

| Section 10. Monitor ROM (MON)                                       |

| Section 11. Timer Interface Module (TIM)193                         |

| Section 12. Real Time Clock (RTC)217                                |

| Section 13. Infrared Serial Communications Interface Module (IRSCI) |

| Section 14. Serial Peripheral Interface Module (SPI)287             |

| Section 15. Multi-Master IIC Interface (MMIIC) 319                  |

| Section 16. Analog-to-Digital Converter (ADC)333                    |

| Section 17. Liquid Crystal Display (LCD) Driver349                  |

| Section 18. Input/Output (I/O) Ports375                             |

| Section 19. External Interrupt (IRQ)401                             |

MC68HC908LJ24/LK24 — Rev. 2.1

## Data Sheet — MC68HC908LJ24

# Section 4. FLASH Memory (FLASH)

### 4.1 Contents

| 4.2          | Introduction               | .69 |

|--------------|----------------------------|-----|

| 4.3          | Functional Description     | .70 |

| 4.4          | FLASH Control Register     | .71 |

| 4.5          | FLASH Page Erase Operation | .72 |

| 4.6          | FLASH Mass Erase Operation | .73 |

| 4.7          | FLASH Program Operation    | .74 |

| 4.8<br>4.8.1 | FLASH Block Protection     |     |

## 4.2 Introduction

This section describes the operation of the embedded FLASH memory. This memory can be read, programmed, and erased from a single external supply. The program and erase operations are enabled through the use of an internal charge pump.

Table 6-1. Instruction Set Summary (Sheet 4 of 8)

| Source                                                                                        | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                              |    | E |   | ct c | on  |    | ress                                                | əpo                                              | Operand                                         | es                                   |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|---|------|-----|----|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                          |    | Н | I | N    | N Z |    | Address<br>Mode<br>Opcode                           |                                                  | Ope                                             | Cycles                               |

| CMP #opr<br>CMP opr<br>CMP opr<br>CMP opr,X<br>CMP opr,X<br>CMP,X<br>CMP opr,SP<br>CMP opr,SP | Compare A with M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (A) – (M)                                                                                                                                                |    | _ | _ | \$   | \$  | \$ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A1<br>B1<br>C1<br>D1<br>E1<br>F1<br>9EE1<br>9ED1 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| COM opr<br>COMA<br>COMX<br>COM opr,X<br>COM ,X<br>COM opr,SP                                  | $ \begin{array}{c} M \leftarrow (\overline{M}) = \$FF - (M) \\ A \leftarrow (\overline{A}) = \$FF - (M) \\ X \leftarrow (\overline{X}) = \$FF - (M) \\ M \leftarrow (\overline{M}) = \$FF - (M) \\ \end{array} $                                                                                                 |                                                                                                                                                          | 0  | _ | _ | \$   | \$  | 1  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 33<br>43<br>53<br>63<br>73<br>9E63               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| CPHX #opr<br>CPHX opr                                                                         | Compare H:X with M                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (H:X) – (M:M + 1)                                                                                                                                        | \$ | - | _ | \$   | \$  | \$ | IMM<br>DIR                                          | 65<br>75                                         | ii ii+1<br>dd                                   | 3<br>4                               |

| CPX #opr<br>CPX opr<br>CPX opr<br>CPX,X<br>CPX opr,X<br>CPX opr,X<br>CPX opr,SP<br>CPX opr,SP | Compare X with M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (X) – (M)                                                                                                                                                | \$ | _ | _ | \$   | \$  | \$ | IMM DIR EXT IX2 IX1 IX SP1 SP2                      | A3<br>B3<br>C3<br>D3<br>E3<br>F3<br>9EE3<br>9ED3 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| DAA                                                                                           | Decimal Adjust A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (A) <sub>10</sub>                                                                                                                                        | U  | _ | _ | \$   | \$  | \$ | INH                                                 | 72                                               |                                                 | 2                                    |

| DBNZ opr,rel DBNZA rel DBNZX rel DBNZ opr,X,rel DBNZ X,rel DBNZ opr,SP,rel                    | $A \leftarrow (A) - 1 \text{ or } M \leftarrow (M) - 1 \text{ or } X \leftarrow (X) - 2$ $PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0$ $PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0$ $PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0$ $PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0$ $PC \leftarrow (PC) + 3 + rel? \text{ (result)} \neq 0$ $PC \leftarrow (PC) + 2 + rel? \text{ (result)} \neq 0$ $PC \leftarrow (PC) + 4 + rel? \text{ (result)} \neq 0$ |                                                                                                                                                          | _  | _ | _ | _    | _   | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3B<br>4B<br>5B<br>6B<br>7B<br>9E6B               | dd rr<br>rr<br>rr<br>ff rr<br>rr<br>ff rr       | 5<br>3<br>3<br>5<br>4<br>6           |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                  | Decrement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $M \leftarrow (M) - 1$<br>$A \leftarrow (A) - 1$<br>$X \leftarrow (X) - 1$<br>$M \leftarrow (M) - 1$<br>$M \leftarrow (M) - 1$<br>$M \leftarrow (M) - 1$ | \$ | _ | _ | \$   | \$  | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                           | Divide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A ← (H:A)/(X)<br>H ← Remainder                                                                                                                           | _  | _ | _ | _    | \$  | \$ | INH                                                 | 52                                               |                                                 | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP | Exclusive OR M with A                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $A \leftarrow (A \oplus M)$                                                                                                                              | 0  | _ | _ | \$   | \$  | _  | IMM DIR EXT IX2 IX1 IX SP1 SP2                      | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8         | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

MC68HC908LJ24/LK24 — Rev. 2.1

## Data Sheet — MC68HC908LJ24

# Section 7. Oscillator (OSC)

### 7.1 Contents

| 7.2   | Introduction                           |

|-------|----------------------------------------|

| 7.3   | Internal Oscillator                    |

| 7.4   | X-tal Oscillator                       |

| 7.5   | I/O Signals                            |

| 7.5.1 | Crystal Amplifier Input Pin (OSC1)106  |

| 7.5.2 | Crystal Amplifier Output Pin (OSC2)    |

| 7.5.3 | Oscillator Enable Signal (SIMOSCEN)106 |

| 7.5.4 | Internal RC Clock (ICLK)               |

| 7.5.5 | CGM Oscillator Clock (CGMXCLK)         |

| 7.5.6 | CGM Reference Clock (CGMRCLK)          |

| 7.6   | Low Power Modes                        |

| 7.6.1 | Wait Mode                              |

| 7.6.2 | Stop Mode                              |

| 7.7   | Oscillator During Break Mode107        |

## 7.2 Introduction

The oscillator module provides the reference clock for the clock generator module (CGM), the real time clock module (RTC), and other MCU sub-systems.

The oscillator module consist of two types of oscillator circuits:

- Internal RC oscillator

- 32.768kHz crystal (x-tal) oscillator

MC68HC908LJ24/LK24 — Rev. 2.1

# Clock Generator Module (CGM)

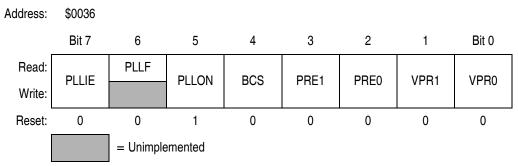

### 8.6.1 PLL Control Register

The PLL control register (PCTL) contains the interrupt enable and flag bits, the on/off switch, the base clock selector bit, the prescaler bits, and the VCO power-of-two range selector bits.

Figure 8-4. PLL Control Register (PCTL)

### PLLIE — PLL Interrupt Enable Bit

This read/write bit enables the PLL to generate an interrupt request when the LOCK bit toggles, setting the PLL flag, PLLF. When the AUTO bit in the PLL bandwidth control register (PBWC) is clear, PLLIE cannot be written and reads as logic 0. Reset clears the PLLIE bit.

1 = PLL interrupts enabled

0 = PLL interrupts disabled

### PLLF — PLL Interrupt Flag Bit

This read-only bit is set whenever the LOCK bit toggles. PLLF generates an interrupt request if the PLLIE bit also is set. PLLF always reads as logic 0 when the AUTO bit in the PLL bandwidth control register (PBWC) is clear. Clear the PLLF bit by reading the PLL control register. Reset clears the PLLF bit.

1 = Change in lock condition

0 = No change in lock condition

# **NOTE:** Do not inadvertently clear the PLLF bit. Any read or read-modify-write operation on the PLL control register clears the PLLF bit.

## System Integration Module (SIM)

## 9.3.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt, break, or reset, the SIM allows ICLK to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay timeout. This timeout is selectable as 4096 or 32 ICLK cycles. (See **9.7.2 Stop Mode**.)

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

## 9.4 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- · Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE:\$FFFF (\$FEFE:\$FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see **9.5 SIM Counter**), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). (See **9.8 SIM Registers**.)

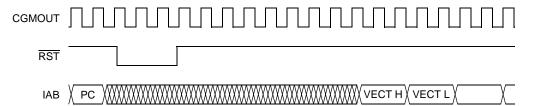

### 9.4.1 External Pin Reset

The RST pin circuit includes an internal pull-up device. Pulling the asynchronous RST pin low halts all processing. The PIN bit of the SIM reset status register (SRSR) is set as long as RST is held low for a minimum of 67 ICLK cycles, assuming that neither the POR nor the LVI was the source of the reset. See **Table 9-2** for details.

Figure 9-4 shows the relative timing.

**Table 9-2. PIN Bit Set Timing**

| Reset Type | Number of Cycles Required to Set PIN |

|------------|--------------------------------------|

| POR/LVI    | 4163 (4096 + 64 + 3)                 |

| All others | 67 (64 + 3)                          |

Figure 9-4. External Reset Timing

### 9.4.2 Active Resets from Internal Sources

All internal reset sources actively pull the RST pin low for 32 ICLK cycles to allow resetting of external peripherals. The internal reset signal IRST continues to be asserted for an additional 32 cycles (see Figure 9-5). An internal reset can be caused by an illegal address, illegal opcode, COP timeout, LVI, or POR (see Figure 9-6).

NOTE:

For LVI or POR resets, the SIM cycles through 4096 + 32 ICLK cycles during which the SIM forces the  $\overline{RST}$  pin low. The internal reset signal then follows the sequence from the falling edge of  $\overline{RST}$  shown in Figure 9-5.

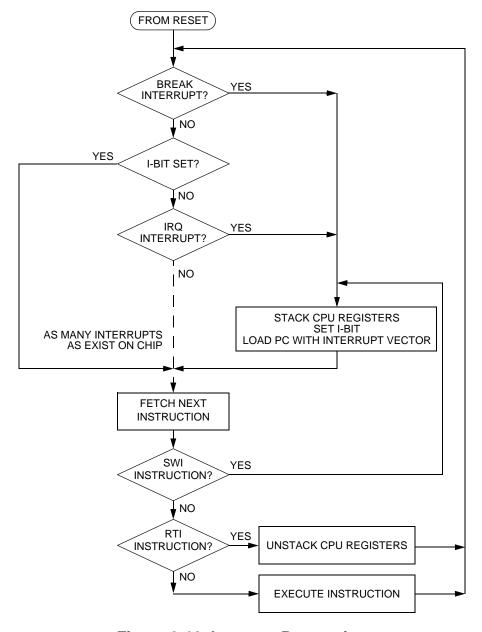

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. Once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced (or the I bit is cleared).

(See Figure 9-10.)

Figure 9-10. Interrupt Processing

## **Monitor ROM (MON)**

**Table 10-3** lists external frequencies required to achieve a standard baud rate of 9600 BPS. Other standard baud rates can be accomplished using proportionally higher or lower frequency generators. If using a crystal as the clock source, be aware of the upper frequency limit that the internal clock module can handle.

Table 10-3. Monitor Baud Rate Selection

| External<br>Frequency | ĪRQ              | PTC1 | Internal<br>Frequency | Baud Rate<br>(BPS) |

|-----------------------|------------------|------|-----------------------|--------------------|

| 4.9152 MHz            | V <sub>TST</sub> | 0    | 2.4576 MHz            | 9600               |

| 9.8304 MHz            | V <sub>TST</sub> | 1    | 2.4576 MHz            | 9600               |

| 9.8304 MHz            | V <sub>DD</sub>  | Х    | 2.4576 MHz            | 9600               |

| 32.768 kHz            | V <sub>SS</sub>  | Х    | 2.4576 MHz            | 9600               |

### 10.4.5 Commands

The monitor ROM firmware uses these commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

The monitor ROM firmware echoes each received byte back to the PTA0 pin for error checking. An 11-bit delay at the end of each command allows the host to send a break character to cancel the command. A delay of two bit times occurs before each echo and before READ, IREAD, or READSP data is returned. The data returned by a read command appears after the echo of the last byte of the command.

**NOTE:** Wait one bit time after each echo before sending the next byte.

**Data Sheet**

MC68HC908LJ24/LK24 — Rev. 2.1

## Monitor ROM (MON)

### 10.6.5 MON\_ERARNGE

In monitor mode, ERARNGE is used to erase a range of locations in FLASH.

Table 10-15. MON\_ERARNGE Routine

| Routine Name        | MON_ERARNGE                                                                  |

|---------------------|------------------------------------------------------------------------------|

| Routine Description | Erase a page or the entire array, in monitor mode                            |

| Calling Address     | \$FF2C                                                                       |

| Stack Used          | 11 bytes                                                                     |

| Data Block Format   | Bus speed Data size Starting address (high byte) Starting address (low byte) |

The MON\_ERARNGE routine is designed to be used in monitor mode. It performs the same function as the ERARNGE routine (see 10.6.2 ERARNGE), except that MON\_ERARNGE returns to the main program via an SWI instruction. After a MON\_ERARNGE call, the SWI instruction will return the control back to the monitor code.

186

### TOF — TIM Overflow Flag Bit

This read/write flag is set when the TIM counter reaches the modulo value programmed in the TIM counter modulo registers. Clear TOF by reading the TIM status and control register when TOF is set and then writing a logic 0 to TOF. If another TIM overflow occurs before the clearing sequence is complete, then writing logic 0 to TOF has no effect. Therefore, a TOF interrupt request cannot be lost due to inadvertent clearing of TOF. Reset clears the TOF bit. Writing a logic 1 to TOF has no effect.

- 1 = TIM counter has reached modulo value

- 0 = TIM counter has not reached modulo value

### TOIE — TIM Overflow Interrupt Enable Bit

This read/write bit enables TIM overflow interrupts when the TOF bit becomes set. Reset clears the TOIE bit.

- 1 = TIM overflow interrupts enabled

- 0 = TIM overflow interrupts disabled

### TSTOP — TIM Stop Bit

This read/write bit stops the TIM counter. Counting resumes when TSTOP is cleared. Reset sets the TSTOP bit, stopping the TIM counter until software clears the TSTOP bit.

- 1 = TIM counter stopped

- 0 = TIM counter active

# **NOTE:** Do not set the TSTOP bit before entering wait mode if the TIM is required to exit wait mode.

#### TRST — TIM Reset Bit

Setting this write-only bit resets the TIM counter and the TIM prescaler. Setting TRST has no effect on any other registers. Counting resumes from \$0000. TRST is cleared automatically after the TIM counter is reset and always reads as logic 0. Reset clears the TRST bit.

- 1 = Prescaler and TIM counter cleared

- 0 = No effect

# **NOTE:** Setting the TSTOP and TRST bits simultaneously stops the TIM counter at a value of \$0000.

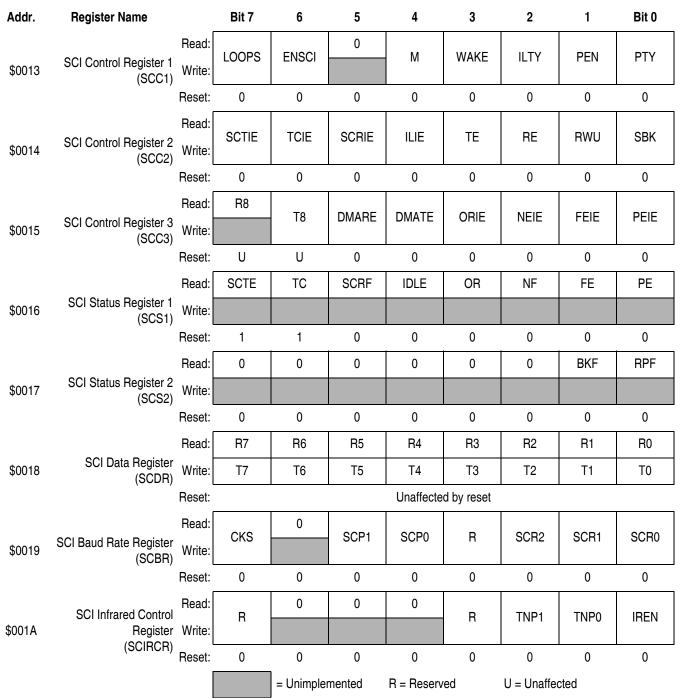

## **Infrared Serial Communications**

Figure 13-1. IRSCI I/O Registers Summary

**Data Sheet**

MC68HC908LJ24/LK24 — Rev. 2.1

## **Infrared Serial Communications**

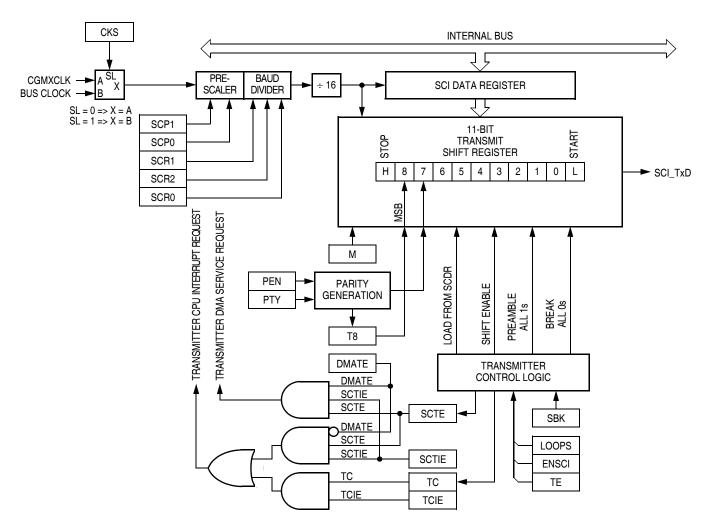

### 13.7.2 Transmitter

Figure 13-7 shows the structure of the SCI transmitter.

The baud rate clock source for the SCI can be selected by the CKS bit, in the SCI baud rate register (see 13.11.7 SCI Baud Rate Register).

Figure 13-7. SCI Transmitter

When an SPI is configured as a master, the  $\overline{SS}$  input can be used in conjunction with the MODF flag to prevent multiple masters from driving MOSI and SPSCK. (See 14.8.2 Mode Fault Error.) For the state of the  $\overline{SS}$  pin to set the MODF flag, the MODFEN bit in the SPSCK register must be set. If the MODFEN bit is low for an SPI master, the  $\overline{SS}$  pin can be used as a general-purpose I/O under the control of the data direction register of the shared I/O port. With MODFEN high, it is an input-only pin to the SPI regardless of the state of the data direction register of the shared I/O port.

The CPU can always read the state of the  $\overline{SS}$  pin by configuring the appropriate pin as an input and reading the port data register. (See Table 14-3.)

SPE **SPMSTR MODFEN SPI Configuration** State of SS Logic General-purpose I/O:  $X^{(1)}$ Χ Not enabled SS ignored by SPI 1 0 Χ Slave Input-only to SPI General-purpose I/O; 1 0 Master without MODF 1 SS ignored by SPI 1 1 1 Master with MODF Input-only to SPI

**Table 14-3. SPI Configuration**

Note 1. X = Don't care

### 14.13.5 CGND (Clock Ground)

CGND is the ground return for the serial clock pin, SPSCK, and the ground for the port output buffers. It is internally connected to  $V_{SS}$  as shown in Table 14-1.

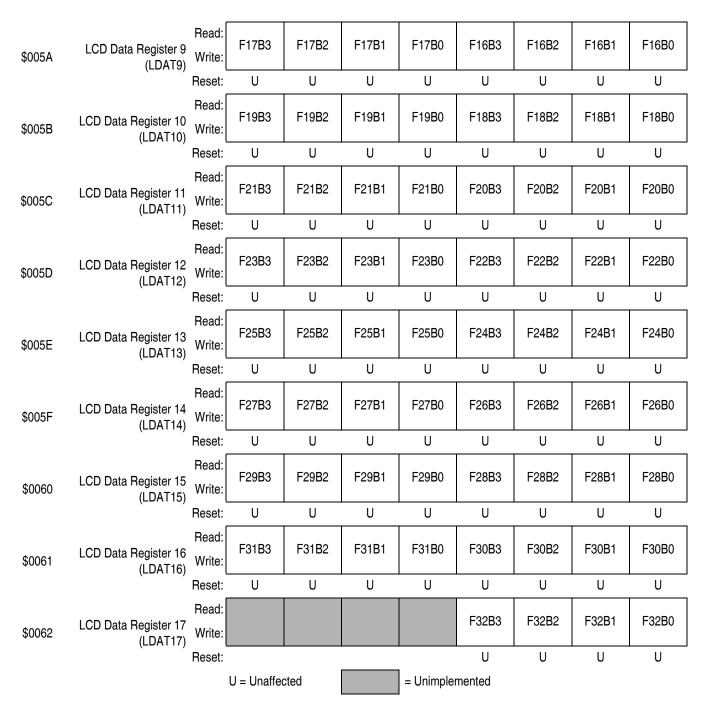

## Liquid Crystal Display (LCD) Driver

Figure 17-1. LCD I/O Register Summary

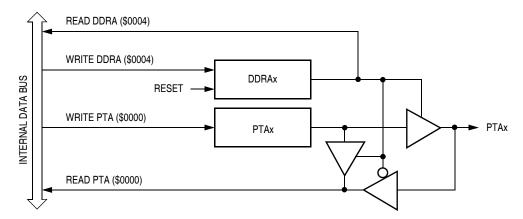

## Input/Output (I/O) Ports

Figure 18-4. Port A I/O Circuit

When DDRAx is a logic 1, reading address \$0000 reads the PTAx data latch. When DDRAx is a logic 0, reading address \$0000 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit.

Table 18-2 summarizes the operation of the port A pins.

**Table 18-2. Port A Pin Functions**

| DDRA | PTA Bit          | I/O Pin Mode               | Accesses to DDRA | Accesse  | s to PTA                |

|------|------------------|----------------------------|------------------|----------|-------------------------|

| Bit  | FIABIL           | I/O FIII WIOGE             | Read/Write       | Read     | Write                   |

| 0    | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRA[7:0]        | Pin      | PTA[7:0] <sup>(3)</sup> |

| 1    | Х                | Output                     | DDRA[7:0]        | PTA[7:0] | PTA[7:0]                |

#### Notes:

- 1. X = don't care.

- 2. Hi-Z = high impedance.

- 3. Writing affects data register, but does not affect input.

## Input/Output (I/O) Ports

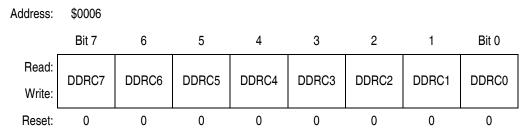

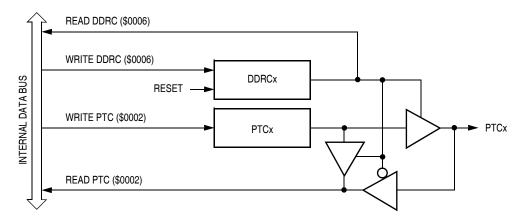

### 18.5.2 Data Direction Register C (DDRC)

Data direction register C determines whether each port C pin is an input or an output. Writing a logic 1 to a DDRC bit enables the output buffer for the corresponding port C pin; a logic 0 disables the output buffer.

Figure 18-10. Data Direction Register C (DDRC)

DDRC[7:0] — Data Direction Register C Bits

These read/write bits control port C data direction. Reset clears DDRC[7:0], configuring all port C pins as inputs.

- 1 = Corresponding port C pin configured as output

- 0 = Corresponding port C pin configured as input

**NOTE:** Avoid glitches on port C pins by writing to the port C data register before changing data direction register C bits from 0 to 1. **Figure 18-11** shows the port C I/O logic.

Figure 18-11. Port C I/O Circuit

**Data Sheet**

MC68HC908LJ24/LK24 — Rev. 2.1

## Section 20. Keyboard Interrupt Module (KBI)

## 20.1 Contents

| 20.2                     | Introduction                            |

|--------------------------|-----------------------------------------|

| 20.3                     | Features                                |

| 20.4                     | I/O Pins                                |

| 20.5<br>20.5.1           | Functional Description                  |

| 20.6<br>20.6.1<br>20.6.2 | Keyboard Interrupt Registers            |

| 20.7<br>20.7.1<br>20.7.2 | Low-Power Modes                         |

| 20.8                     | Keyboard Module During Break Interrupts |

## 20.2 Introduction

The keyboard interrupt module (KBI) provides eight independently maskable external interrupts which are accessible via PTA0–PTA3 and PTD4–PTD7. When a port pin is enabled for keyboard interrupt function (except PTD6 and PTD7), an internal  $30\,\mathrm{k}\Omega$  pullup device is also enabled on the pin.

### **NOTE:**

PTD6/KBI6/SCL-PTD7/KBI7/SDA pins do not have internal pullup devices. These two pins are open-drain when configured as outputs. User should connect pullup devices when using these two pins for KBI function.

MC68HC908LJ24/LK24 — Rev. 2.1

## **Keyboard Interrupt Module (KBI)**

If the MODEK bit is set, the keyboard interrupt pins are both falling edgeand low level-sensitive, and both of the following actions must occur to clear a keyboard interrupt request:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the interrupt request. Software may generate the interrupt acknowledge signal by writing a logic 1 to the ACKK bit in the keyboard status and control register KBSCR. The ACKK bit is useful in applications that poll the keyboard interrupt pins and require software to clear the keyboard interrupt request. Writing to the ACKK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt pins. A falling edge that occurs after writing to the ACKK bit latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the CPU loads the program counter with the vector address at locations \$FFDC and \$FFDD.

- Return of all enabled keyboard interrupt pins to logic 1 As long as any enabled keyboard interrupt pin is at logic 0, the keyboard interrupt remains set.

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to logic 1 may occur in any order.

If the MODEK bit is clear, the keyboard interrupt pin is falling-edgesensitive only. With MODEK clear, a vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt pin stays at logic 0.

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes it useful in applications where polling is preferred.

To determine the logic level on a keyboard interrupt pin, use the data direction register to configure the pin as an input and read the data register.

## Data Sheet — MC68HC908LJ24

# Section 22. Low-Voltage Inhibit (LVI)

### 22.1 Contents

| 22.2   | Introduction                  |

|--------|-------------------------------|

| 22.3   | Features                      |

| 22.4   | Functional Description        |

| 22.4.1 | Polled LVI Operation          |

| 22.4.2 | Forced Reset Operation        |

| 22.4.3 | Voltage Hysteresis Protection |

| 22.4.4 | LVI Trip Selection            |

| 22.5   | LVI Status Register425        |

| 22.6   | Low-Power Modes               |

| 22.6.1 | Wait Mode                     |

| 22.6.2 | Stop Mode                     |

## 22.2 Introduction

This section describes the low-voltage inhibit (LVI) module, which monitors the voltage on the  $V_{DD}$  pin and can force a reset when the  $V_{DD}$  voltage falls below the LVI trip falling voltage,  $V_{TRIPF}$ .

## 22.3 Features

Features of the LVI module include:

- Programmable LVI interrupt and reset

- Selectable LVI trip voltage

- Programmable stop mode operation

MC68HC908LJ24/LK24 — Rev. 2.1