Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Active                                                        |

| Core Processor             | HC08                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | I <sup>2</sup> C, IRSCI, SPI                                  |

| Peripherals                | LCD, LVD, POR, PWM                                            |

| Number of I/O              | 40                                                            |

| Program Memory Size        | 24KB (24K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | · .                                                           |

| RAM Size                   | 768 × 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                     |

| Data Converters            | A/D 6x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 64-LQFP                                                       |

| Supplier Device Package    | 64-LQFP (10x10)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908lj24cpb |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Tables

| Table                                                                         | Title                                                                                                                                                                                                                                                                                                                                            | Page                                                         |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 2-1                                                                           | Vector Addresses                                                                                                                                                                                                                                                                                                                                 | 65                                                           |

| 4-1                                                                           | FLASH Block Protect Register to Physical Address                                                                                                                                                                                                                                                                                                 | 78                                                           |

| 5-1                                                                           | LVI Trip Point Selection                                                                                                                                                                                                                                                                                                                         | 84                                                           |

| 6-1<br>6-2                                                                    | Instruction Set Summary                                                                                                                                                                                                                                                                                                                          |                                                              |

| 8-1<br>8-3<br>8-2                                                             | Numeric ExamplesVPR1 and VPR0 ProgrammingPRE 1 and PRE0 Programming                                                                                                                                                                                                                                                                              | .128                                                         |

| 9-1<br>9-2<br>9-3                                                             | Signal Name Conventions                                                                                                                                                                                                                                                                                                                          | .145                                                         |

| 10-1<br>10-2<br>10-3<br>10-4<br>10-5<br>10-6<br>10-7<br>10-8<br>10-9<br>10-10 | Monitor Mode Signal Requirements and OptionsMode Differences (Vectors)Monitor Baud Rate SelectionREAD (Read Memory) CommandWRITE (Write Memory) CommandIREAD (Indexed Read) CommandINRITE (Indexed Write) CommandIWRITE (Indexed Write) CommandREADSP (Read Stack Pointer) CommandRUN (Run User Program) CommandSummary of ROM-Resident Routines | .170<br>.172<br>.173<br>.174<br>.174<br>.175<br>.175<br>.175 |

| 10-11<br>10-12                                                                | PRGRNGE Routine                                                                                                                                                                                                                                                                                                                                  | .181<br>.183                                                 |

| 10-13                                                                         |                                                                                                                                                                                                                                                                                                                                                  | . 104                                                        |

## Memory Map

| Addr.  | Register Name                       |                 | Bit 7                           | 6     | 5     | 4         | 3      | 2     | 1          | Bit 0 |

|--------|-------------------------------------|-----------------|---------------------------------|-------|-------|-----------|--------|-------|------------|-------|

| \$0000 | Port A Data Register<br>(PTA)       | Read:<br>Write: | PTA7                            | PTA6  | PTA5  | PTA4      | PTA3   | PTA2  | PTA1       | PTA0  |

|        | (177)                               | Reset:          | U                               | U     | U     | U         | U      | U     | U          | U     |

| \$0001 | Port B Data Register<br>(PTB)       | Read:<br>Write: | PTB7                            | PTB6  | PTB5  | PTB4      | PTB3   | PTB2  | PTB1       | PTB0  |

|        | (1.10)                              | Reset:          | U                               | U     | U     | U         | U      | U     | U          | U     |

| \$0002 | Port C Data Register<br>(PTC)       | Read:<br>Write: | PTC7                            | PTC6  | PTC5  | PTC4      | PTC3   | PTC2  | PTC1       | PTC0  |

|        | ()                                  | Reset:          | U                               | U     | U     | U         | U      | U     | U          | U     |

| \$0003 | Port D Data Register<br>(PTD)       | Read:<br>Write: | PTD7                            | PTD6  | PTD5  | PTD4      | PTD3   | PTD2  | PTD1       | PTD0  |

|        | ( )                                 | Reset:          | U                               | U     | U     | U         | U      | U     | U          | U     |

| \$0004 | Data Direction Register A<br>(DDRA) | Read:<br>Write: | DDRA7                           | DDRA6 | DDRA5 | DDRA4     | DDRA3  | DDRA2 | DDRA1      | DDRA0 |

|        | ( )                                 | Reset:          | 0                               | 0     | 0     | 0         | 0      | 0     | 0          | 0     |

| \$0005 | Data Direction Register B<br>(DDRB) | Read:<br>Write: | DDRB7                           | DDRB6 | DDRB5 | DDRB4     | DDRB3  | DDRB2 | DDRB1      | DDRB0 |

|        |                                     | Reset:          | 0                               | 0     | 0     | 0         | 0      | 0     | 0          | 0     |

| \$0006 | Data Direction Register C<br>(DDRC) | Read:<br>Write: | DDRC7                           | DDRC6 | DDRC5 | DDRC4     | DDRC3  | DDRC2 | DDRC1      | DDRC0 |

|        | (==,                                | Reset:          | 0                               | 0     | 0     | 0         | 0      | 0     | 0          | 0     |

| \$0007 | Data Direction Register D<br>(DDRD) | Read:<br>Write: | DDRD7                           | DDRD6 | DDRD5 | DDRD4     | DDRD3  | DDRD2 | DDRD1      | DDRD0 |

|        | ()                                  | Reset:          | 0                               | 0     | 0     | 0         | 0      | 0     | 0          | 0     |

| \$0008 | Port E Data Register<br>(PTE)       | Read:<br>Write: | PTE7                            | PTE6  | PTE5  | PTE4      | PTE3   | PTE2  | PTE1       | PTE0  |

|        | ()                                  | Reset:          | U                               | U     | U     | U         | U      | U     | U          | U     |

| \$0009 | Data Direction Periotor E           | Read:<br>Write: | DDRE7                           | DDRE6 | DDRE5 | DDRE4     | DDRE3  | DDRE2 | DDRE1      | DDRE0 |

|        |                                     |                 | 0                               | 0     | 0     | 0         | 0      | 0     | 0          | 0     |

|        | U = Unaffected                      |                 | Reset: 0 0<br>X = Indeterminate |       |       | = Unimple | mented | R     | = Reserved | b     |

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 13)

Data Sheet

# NP

Memory Map

| Addr.        | Register Name                         |                 | Bit 7       | 6       | 5      | 4         | 3      | 2       | 1         | Bit 0   |

|--------------|---------------------------------------|-----------------|-------------|---------|--------|-----------|--------|---------|-----------|---------|

| \$0062       | LCD Data Register 17<br>(LDAT17)      | Read:<br>Write: |             |         |        |           | F32B3  | F32B2   | F32B1     | F32B0   |

|              | · · · · · · · · · · · · · · · · · · · | Reset:          |             |         |        |           | U      | U       | U         | U       |

| \$0063<br>to | Unimplemented                         | Read:<br>Write: |             |         |        |           |        |         |           |         |

| \$0069       | eninplemented                         | Reset:          |             |         |        |           |        |         |           |         |

|              |                                       | Read:           | MMALIF      | MMNAKIF | MMBB   |           |        |         |           |         |

| \$006A       | MMIIC Master Control<br>Register      |                 | 0           | 0       |        | MMAST     | MMRW   | MMBR2   | MMBR1     | MMBR0   |

| ,            |                                       | Reset:          | 0           | 0       | 0      | 0         | 0      | 0       | 0         | 0       |

|              |                                       | Read:           |             |         |        |           |        |         |           |         |

| \$006B       | MMIIC Address Register<br>(MMADR)     | Write:          | MMAD7       | MMAD6   | MMAD5  | MMAD4     | MMAD3  | MMAD2   | MMAD1     | MMEXTAD |

|              | ( )                                   | Reset:          | 1           | 0       | 1      | 0         | 0      | 0       | 0         | 0       |

|              | MMIIC Control Register<br>(MMCR)      | Read:           | MMEN        | MMIEN   | 0      | 0         | MMTXAK | REPSEN  | 0         | 0       |

| \$006C       |                                       | Write:          |             |         |        |           |        | HEI OEN |           |         |

|              |                                       | Reset:          | 0           | 0       | 0      | 0         | 0      | 0       | 0         | 0       |

|              | MMIIC Status Register<br>(MMSR)       | Read:           | MMRXIF      | MMTXIF  | MMATCH | MMSRW     | MMRXAK | 0       | MMTXBE    | MMRXBF  |

| \$006D       |                                       | Write:          | 0           | 0       |        |           |        |         |           |         |

|              |                                       | Reset:          | 0           | 0       | 0      | 0         | 1      | 0       | 1         | 0       |

| \$006E       | MMIIC Data Transmit<br>Register       | Read:<br>Write: | MMTD7       | MMTD6   | MMTD5  | MMTD4     | MMTD3  | MMTD2   | MMTD1     | MMTD0   |

|              | (MMDTR)                               | Reset:          | 1           | 1       | 1      | 1         | 1      | 1       | 1         | 1       |

|              | MMIIC Data Receive                    | Read:           | MMRD7       | MMRD6   | MMRD5  | MMRD4     | MMRD3  | MMRD2   | MMRD1     | MMRD0   |

| \$006F       | Register                              | Write:          |             |         |        |           |        |         |           |         |

|              | (MMDRR)                               | Reset:          | 0           | 0       | 0      | 0         | 0      | 0       | 0         | 0       |

| \$0070<br>to | Reserved                              | Read:<br>Write: | R           | R       | R      | R         | R      | R       | R         | R       |

| \$007F       |                                       | Reset:          |             |         |        |           |        |         |           | 1       |

|              | U = Unaffected                        |                 | X = Indeter | minate  |        | = Unimple | mented | R       | = Reserve | d       |

Figure 2-2. Control, Status, and Data Registers (Sheet 11 of 13)

## 6.4 CPU Registers

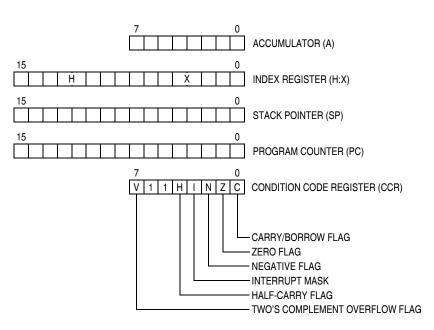

**Figure 6-1** shows the five CPU registers. CPU registers are not part of the memory map.

Figure 6-1. CPU Registers

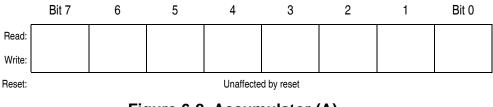

#### 6.4.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 6-2. Accumulator (A)

## Section 7. Oscillator (OSC)

## 7.1 Contents

| Introduction                        |

|-------------------------------------|

| Internal Oscillator                 |

| X-tal Oscillator                    |

| I/O Signals                         |

| Crystal Amplifier Input Pin (OSC1)  |

| Crystal Amplifier Output Pin (OSC2) |

| Oscillator Enable Signal (SIMOSCEN) |

| Internal RC Clock (ICLK)106         |

| CGM Oscillator Clock (CGMXCLK)      |

| CGM Reference Clock (CGMRCLK)       |

| Low Power Modes                     |

| Wait Mode                           |

| Stop Mode                           |

| Oscillator During Break Mode107     |

|                                     |

## 7.2 Introduction

The oscillator module provides the reference clock for the clock generator module (CGM), the real time clock module (RTC), and other MCU sub-systems.

The oscillator module consist of two types of oscillator circuits:

- Internal RC oscillator

- 32.768kHz crystal (x-tal) oscillator

The relationship between the VCO frequency,  $f_{VCLK}$ , and the reference frequency,  $f_{RCLK}$ , is

$$f_{VCLK} = \frac{2^{P}N}{R}(f_{RCLK})$$

where N is the integer range multiplier, between 1 and 4095.

In cases where desired bus frequency has some tolerance, choose  $f_{RCLK}$  to a value determined either by other module requirements (such as modules which are clocked by CGMXCLK), cost requirements, or ideally, as high as the specified range allows. See **Section 24. Electrical Specifications**. Choose the reference divider, R = 1.

When the tolerance on the bus frequency is tight, choose  $f_{RCLK}$  to an integer divisor of  $f_{BUSDES}$ , and R = 1. If  $f_{RCLK}$  cannot meet this requirement, use the following equation to solve for R with practical choices of  $f_{RCLK}$ , and choose the  $f_{RCLK}$  that gives the lowest R.

$$R = round \left[ R_{MAX} \times \left\{ \left( \frac{f_{VCLKDES}}{f_{RCLK}} \right) - integer \left( \frac{f_{VCLKDES}}{f_{RCLK}} \right) \right\} \right]$$

4. Calculate N:

$$N = round \left( \frac{R \times f_{VCLKDES}}{f_{RCLK} \times 2^{P}} \right)$$

5. Calculate and verify the adequacy of the VCO and bus frequencies  $f_{VCLK}$  and  $f_{BUS}$ .

$$f_{VCLK} = \frac{2^{P}N}{R}(f_{RCLK})$$

$$f_{BUS} = \frac{f_{VCLK}}{2^{P} \times 4}$$

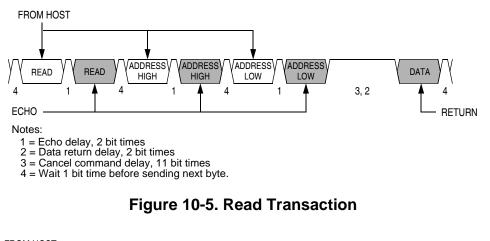

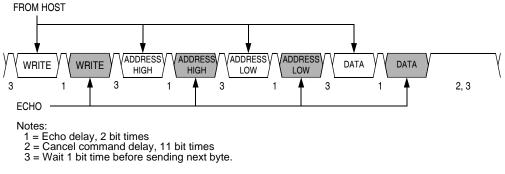

#### Figure 10-6. Write Transaction

A brief description of each monitor mode command is given in **Table 10-4** through **Table 10-9**.

#### Table 10-4. READ (Read Memory) Command

MC68HC908LJ24/LK24 — Rev. 2.1

Data Sheet

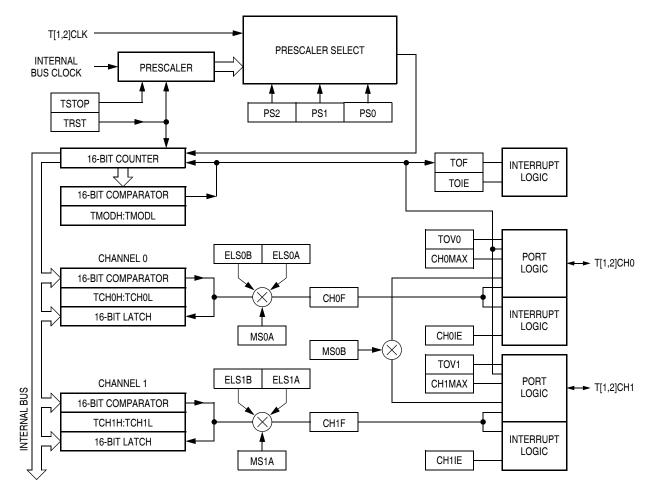

## Timer Interface Module (TIM)

Figure 11-1. TIM Block Diagram

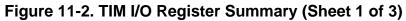

Figure 11-2 summarizes the timer registers.

**NOTE:** References to either timer 1 or timer 2 may be made in the following text by omitting the timer number. For example, TSC may generically refer to both T1SC and T2SC.

| Addr.                                               | Register Name                                               |                 | Bit 7  | 6         | 5      | 4            | 3             | 2     | 1     | Bit 0  |

|-----------------------------------------------------|-------------------------------------------------------------|-----------------|--------|-----------|--------|--------------|---------------|-------|-------|--------|

|                                                     | Timer 1 Status and<br>Control Register                      | Read:           | TOF    | тог       | TOTOD  | 0            | 0             | DCO   | D01   | PS0    |

| \$0020                                              |                                                             | Write:          | 0      | TOIE      | TSTOP  | TRST         |               | PS2   | PS1   | P50    |

|                                                     | (T1SC)                                                      | Reset:          | 0      | 0         | 1      | 0            | 0             | 0     | 0     | 0      |

|                                                     | Timer 1 Counter                                             | Read:           | Bit 15 | 14        | 13     | 12           | 11            | 10    | 9     | Bit 8  |

| \$0021                                              | Register High                                               | Write:          |        |           |        |              |               |       |       |        |

|                                                     | (T1CNTH)                                                    | Reset:          | 0      | 0         | 0      | 0            | 0             | 0     | 0     | 0      |

|                                                     | Timer 1 Counter                                             | Read:           | Bit 7  | 6         | 5      | 4            | 3             | 2     | 1     | Bit 0  |

| \$0022                                              | Register Low                                                | Write:          |        |           |        |              |               |       |       |        |

|                                                     | (T1CNTL)                                                    | Reset:          | 0      | 0         | 0      | 0            | 0             | 0     | 0     | 0      |

| \$0023                                              | Timer 1 Counter Modulo<br>Register High                     | Read:<br>Write: | Bit 15 | 14        | 13     | 12           | 11            | 10    | 9     | Bit 8  |

|                                                     | (T1MODH)                                                    | Reset:          | 1      | 1         | 1      | 1            | 1             | 1     | 1     | 1      |

| •                                                   | Timer 1 Counter Modulo<br>Register Low<br>(T1MODL)          | Read:           | Bit 7  | 6         | 5      | 4            | 3             | 2     | 1     | Bit 0  |

| \$0024                                              |                                                             | Reset:          | 1      | 1         | 1      | 1            | 1             | 1     | 1     | 1      |

|                                                     |                                                             | Read:           | CH0F   | 1         | 1      |              | 1             | I     |       |        |

| \$0025                                              | Timer 1 Channel 0 Status<br>and Control Register<br>(T1SC0) | Write:          | 0      | CHOIE     | MS0B   | MS0A         | ELS0B         | ELS0A | TOV0  | CH0MAX |

| φ0020                                               |                                                             | Reset:          | 0      | 0         | 0      | 0            | 0             | 0     | 0     | 0      |

|                                                     |                                                             | Read:           | 0      |           |        | U            | U             | 0     | Ū     | Ŭ,     |

| \$0026                                              | Timer 1 Channel 0<br>Register High                          | Write:          | Bit 15 | 14        | 13     | 12           | 11            | 10    | 9     | Bit 8  |

|                                                     | (T1CH0H)                                                    | Reset:          |        |           |        | Indeterminat | te after rese | t     |       |        |

| \$0027                                              | Timer 1 Channel 0<br>Register Low                           | Read:<br>Write: | Bit 7  | 6         | 5      | 4            | 3             | 2     | 1     | Bit 0  |

|                                                     | (T1CH0L)                                                    | Reset:          |        |           |        | Indeterminat | te after rese | t     |       | II     |

|                                                     | Timer 1 Channel 1 Status                                    | Read:           | CH1F   |           | 0      | M044         |               |       | TO)// |        |

| \$0028                                              | Timer 1 Channel 1 Status<br>and Control Register<br>(T1SC1) | Write:          | 0      | CH1IE     |        | MS1A         | ELS1B         | ELS1A | TOV1  | CH1MAX |

|                                                     |                                                             | Reset:          | 0      | 0         | 0      | 0            | 0             | 0     | 0     | 0      |

|                                                     |                                                             |                 |        | = Unimple | mented |              |               |       |       |        |

| Figure 11-2 TIM I/O Register Summary (Sheet 1 of 3) |                                                             |                 |        |           |        |              |               |       |       |        |

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the new value in the output compare interrupt routine. The output compare interrupt occurs at the end of the current pulse. The interrupt routine has until the end of the PWM period to write the new value.

- When changing to a longer pulse width, enable TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

- **NOTE:** In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to selfcorrect in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

#### 11.5.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The TIM channel 0 registers initially control the pulse width on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM channel registers (0 or 1) that control the pulse width are the ones written to last. TSC0 controls and monitors the buffered PWM function, and TIM channel 1 status and control register (TSC1) is unused. While the MS0B bit is set, the channel 1 pin, TCH1, is available as a general-purpose I/O pin.

## 13.3 Features

Features of the SCI module include the following:

- Full duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- Programmable 8-bit or 9-bit character length

- Separately enabled transmitter and receiver

- Separate receiver and transmitter CPU interrupt requests

- Two receiver wakeup methods:

- Idle line wakeup

- Address mark wakeup

- Interrupt-driven operation with eight interrupt flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

Features of the infrared (IR) sub-module include the following:

- IR sub-module enable/disable for infrared SCI or conventional SCI on TxD and RxD pins

- Software selectable infrared modulation/demodulation (3/16, 1/16 or 1/32 width pulses)

#### 13.8 Low-Power Modes

The WAIT and STOP instructions put the MCU in low powerconsumption standby modes.

#### 13.8.1 Wait Mode

The SCI module remains active after the execution of a WAIT instruction. In wait mode, the SCI module registers are not accessible by the CPU. Any enabled CPU interrupt request from the SCI module can bring the MCU out of wait mode.

If SCI module functions are not required during wait mode, reduce power consumption by disabling the module before executing the WAIT instruction.

Refer to 9.7 Low-Power Modes for information on exiting wait mode.

#### 13.8.2 Stop Mode

The SCI module is inactive after the execution of a STOP instruction. The STOP instruction does not affect SCI register states. SCI module operation resumes after an external interrupt.

Because the internal clock is inactive during stop mode, entering stop mode during an SCI transmission or reception results in invalid data.

Refer to **9.7 Low-Power Modes** for information on exiting stop mode.

Data Sheet

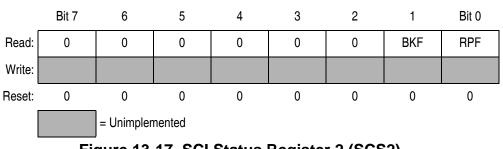

#### 13.11.5 SCI Status Register 2 (SCS2)

SCI status register 2 contains flags to signal the following conditions:

- Break character detected

- Incoming data

Address: \$0017

#### BKF — Break Flag Bit

This clearable, read-only bit is set when the SCI detects a break character on the RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after logic 1s again appear on the RxD pin followed by another break character. Reset clears the BKF bit.

1 = Break character detected

0 = No break character detected

RPF — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a logic 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch) or when the receiver detects an idle character. Polling RPF before disabling the SCI module or entering stop mode can show whether a reception is in progress.

1 = Reception in progress

0 = No reception in progress

#### 13.11.6 SCI Data Register

The SCI data register is the buffer between the internal data bus and the receive and transmit shift registers. Reset has no effect on data in the SCI data register.

Address: \$0018

|        | Bit 7                | 6  | 5  | 4  | 3  | 2  | 1  | Bit 0 |  |  |  |

|--------|----------------------|----|----|----|----|----|----|-------|--|--|--|

| Read:  | R7                   | R6 | R5 | R4 | R3 | R2 | R1 | R0    |  |  |  |

| Write: | T7                   | T6 | T5 | T4 | Т3 | T2 | T1 | Т0    |  |  |  |

| Bacat. | Linaffected by reset |    |    |    |    |    |    |       |  |  |  |

Reset:

Unaffected by reset

#### Figure 13-18. SCI Data Register (SCDR)

R7/T7-R0/T0 — Receive/Transmit Data Bits

Reading the SCDR accesses the read-only received data bits, R7–R0. Writing to the SCDR writes the data to be transmitted, T7–T0. Reset has no effect on the SCDR.

NOTE: Do not use read/modify/write instructions on the SCI data register.

The SPI has limited inter-integrated circuit (I<sup>2</sup>C) capability (requiring software support) as a master in a single-master environment. To communicate with I<sup>2</sup>C peripherals, MOSI becomes an open-drain output when the SPWOM bit in the SPI control register is set. In I<sup>2</sup>C communication, the MOSI and MISO pins are connected to a bidirectional pin from the I<sup>2</sup>C peripheral and through a pullup resistor to  $V_{DD}$ .

#### 14.13.1 MISO (Master In/Slave Out)

MISO is one of the two SPI module pins that transmits serial data. In full duplex operation, the MISO pin of the master SPI module is connected to the MISO pin of the slave SPI module. The master SPI simultaneously receives data on its MISO pin and transmits data from its MOSI pin.

Slave output data on the MISO pin is enabled only when the SPI is configured as a slave. The SPI is configured as a slave when its SPMSTR bit is logic 0 and its  $\overline{SS}$  pin is at logic 0. To support a multiple-slave system, a logic 1 on the  $\overline{SS}$  pin puts the MISO pin in a high-impedance state.

When enabled, the SPI controls data direction of the MISO pin regardless of the state of the data direction register of the shared I/O port.

#### 14.13.2 MOSI (Master Out/Slave In)

MOSI is one of the two SPI module pins that transmits serial data. In fullduplex operation, the MOSI pin of the master SPI module is connected to the MOSI pin of the slave SPI module. The master SPI simultaneously transmits data from its MOSI pin and receives data on its MISO pin.

When enabled, the SPI controls data direction of the MOSI pin regardless of the state of the data direction register of the shared I/O port.

#### SPMSTR — SPI Master Bit

This read/write bit selects master mode operation or slave mode operation. Reset sets the SPMSTR bit.

- 1 = Master mode

- 0 = Slave mode

- CPOL Clock Polarity Bit

This read/write bit determines the logic state of the SPSCK pin between transmissions. (See **Figure 14-4** and **Figure 14-6**.) To transmit data between SPI modules, the SPI modules must have identical CPOL values. Reset clears the CPOL bit.

CPHA — Clock Phase Bit

This read/write bit controls the timing relationship between the serial clock and SPI data. (See **Figure 14-4** and **Figure 14-6**.) To transmit data between SPI modules, the SPI modules must have identical CPHA values. When CPHA = 0, the  $\overline{SS}$  pin of the slave SPI module must be set to logic 1 between bytes. (See **Figure 14-12**.) Reset sets the CPHA bit.

#### SPWOM — SPI Wired-OR Mode Bit

This read/write bit disables the pullup devices on pins SPSCK, MOSI, and MISO so that those pins become open-drain outputs.

- 1 = Wired-OR SPSCK, MOSI, and MISO pins

- 0 = Normal push-pull SPSCK, MOSI, and MISO pins

### SPE — SPI Enable

This read/write bit enables the SPI module. Clearing SPE causes a partial reset of the SPI. (See **14.10 Resetting the SPI**.) Reset clears the SPE bit.

1 = SPI module enabled

0 = SPI module disabled

SPTIE— SPI Transmit Interrupt Enable

This read/write bit enables CPU interrupt requests generated by the SPTE bit. SPTE is set when a byte transfers from the transmit data register to the shift register. Reset clears the SPTIE bit.

1 = SPTE CPU interrupt requests enabled

0 = SPTE CPU interrupt requests disabled

In left justified mode the ADRH holds the eight most significant bits (MSBs), and the ADRL holds the two least significant bits (LSBs), of the 10-bit result. The ADRH and ADRL are updated each time a single channel ADC conversion completes. Reading ADRH latches the contents of ADRL. Until ADRL is read all subsequent ADC results will be lost. (See Figure 16-7 . ADRH and ADRL in Left Justified Mode.)

| Addr.  | Register Name                    |        | Bit 7 | 6   | 5   | 4   | 3   | 2   | 1   | Bit 0 |

|--------|----------------------------------|--------|-------|-----|-----|-----|-----|-----|-----|-------|

| \$003D | ADC Data Register High<br>(ADRH) | Read:  | AD9   | AD8 | AD7 | AD6 | AD5 | AD4 | AD3 | AD2   |

|        |                                  | Write: | R     | R   | R   | R   | R   | R   | R   | R     |

|        |                                  | Reset: | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |

| \$003E | ADC Data Register Low<br>(ADRL)  | Read:  | AD1   | AD0 | 0   | 0   | 0   | 0   | 0   | 0     |

|        |                                  | Write: | R     | R   | R   | R   | R   | R   | R   | R     |

|        |                                  | Reset: | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |

#### Figure 16-7. ADRH and ADRL in Left Justified Mode

In left justified sign mode the ADRH holds the eight MSBs with the MSB complemented, and the ADRL holds the two least significant bits (LSBs), of the 10-bit result. The ADRH and ADRL are updated each time a single channel ADC conversion completes. Reading ADRH latches the contents of ADRL. Until ADRL is read all subsequent ADC results will be lost. (See Figure 16-8 . ADRH and ADRL in Left Justified Sign Data Mode.)

| Addr.  | Register Name                    |        | Bit 7 | 6   | 5   | 4   | 3   | 2   | 1   | Bit 0 |

|--------|----------------------------------|--------|-------|-----|-----|-----|-----|-----|-----|-------|

| \$003D | ADC Data Register High<br>(ADRH) | Read:  | AD9   | AD8 | AD7 | AD6 | AD5 | AD4 | AD3 | AD2   |

|        |                                  | Write: | R     | R   | R   | R   | R   | R   | R   | R     |

|        |                                  | Reset: | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |

| \$003E | ADC Data Register Low<br>(ADRL)  | Read:  | AD1   | AD0 | 0   | 0   | 0   | 0   | 0   | 0     |

|        |                                  | Write: | R     | R   | R   | R   | R   | R   | R   | R     |

|        |                                  | Reset: | 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0     |

Figure 16-8. ADRH and ADRL in Left Justified Sign Data Mode

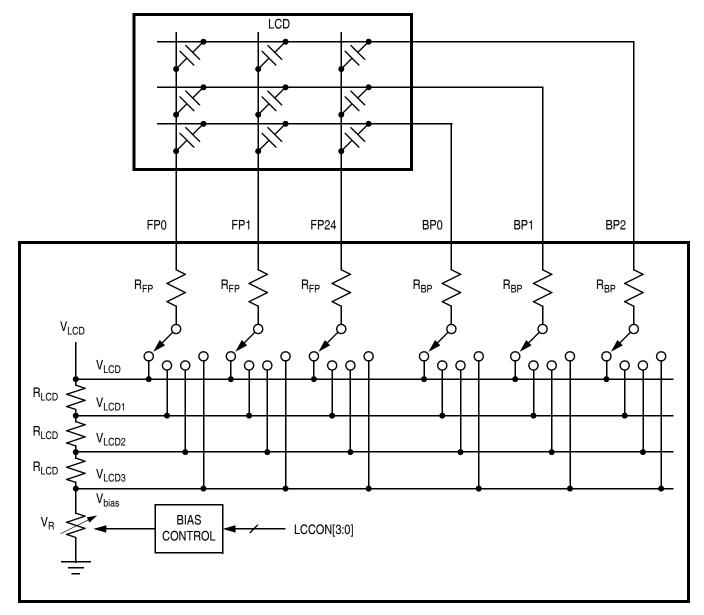

## Liquid Crystal Display (LCD) Driver

Figure 17-3. Simplified LCD Schematic (1/3 Duty, 1/3 Bias)

354

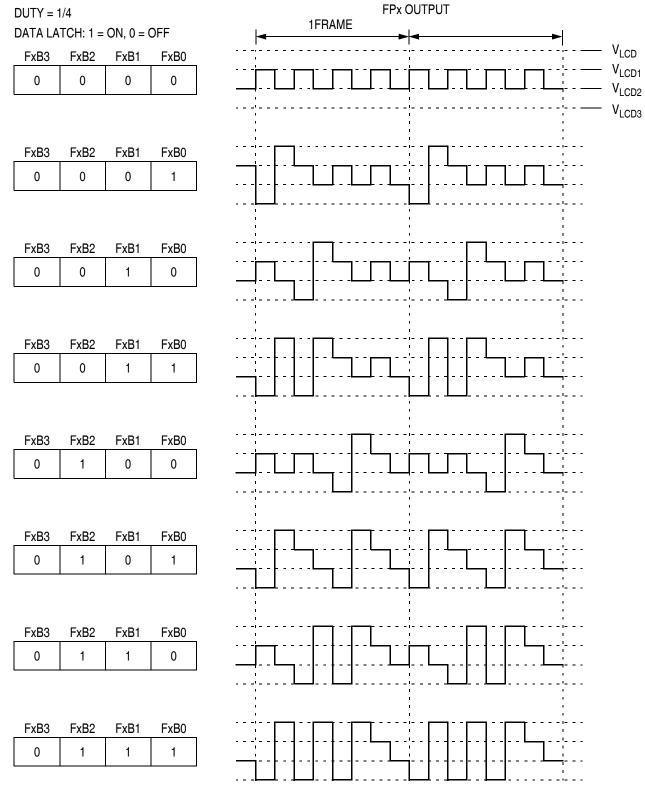

Figure 17-10. 1/4 Duty LCD Frontplane Driver Waveforms

## 18.6 Port D

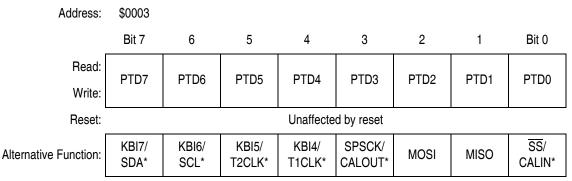

Port D is an 8-bit special function port that shares its pins with the serial peripheral interface (SPI) module, keyboard interrupt module, RTC module, MMIIC module, and timer modules.

## 18.6.1 Port D Data Register (PTD)

The port D data register contains a data latch for each of the eight port D pins.

\* These port pins are shared with two other modules. For each of the pins, ONLY enable ONE module at any one time to avoid pin contention.

### Figure 18-13. Port D Data Register (PTD)

PTD[7:0] — Port D Data Bits

These read/write bits are software programmable. Data direction of each port D pin is under the control of the corresponding bit in data direction register D. Reset has no effect on port D data.

KBI[7:4] — Keyboard Interrupt Channels 7 to 4

KBI[7:4] are pins used for the keyboard interrupt input. The corresponding input, KBI[7:4], can be enabled in the keyboard interrupt enable register, KBIER. Port pins used as KBI input will override any control from the port I/O logic. See Section 20. Keyboard Interrupt Module (KBI).

390