Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Active                                                        |

| Core Processor             | HC08                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | I²C, IRSCI, SPI                                               |

| Peripherals                | LCD, LVD, POR, PWM                                            |

| Number of I/O              | 40                                                            |

| Program Memory Size        | 24KB (24K x 8)                                                |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 768 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                     |

| Data Converters            | A/D 6x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 80-LQFP                                                       |

| Supplier Device Package    | 80-FQFP (12x12)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908lk24cpk |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

# **Revision History**

| Date   | Revision<br>Level | Description            | Page<br>Number(s) |  |

|--------|-------------------|------------------------|-------------------|--|

| 8/2003 | 2                 | First general release. |                   |  |

# List of Sections

| Section 20. Keyboard Interrupt Module (KBI)   | 407 |

|-----------------------------------------------|-----|

| Section 21. Computer Operating Properly (COP) | 415 |

| Section 22. Low-Voltage Inhibit (LVI)         | 421 |

| Section 23. Break Module (BRK)                | 427 |

| Section 24. Electrical Specifications         | 435 |

| Section 25. Mechanical Specifications         | 451 |

| Section 26. Ordering Information              | 457 |

| Appendix A. MC68HC908LK24                     | 459 |

Data Sheet

6

# Table of Contents

# Section 12. Real Time Clock (RTC)

| 12.1 Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.2 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12.3 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12.4 I/O Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12.5 Functional Description     .221       12.5.1 Time Functions     .223       12.5.2 Calendar Functions     .223       12.5.3 Alarm Functions     .223       12.5.4 Chronograph Functions     .223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12.5.5 Timebase Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12.6 RTC Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12.7 RTC Clock Calibration and Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12.8 RTC Register and Bit Write Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 12.9 Low-Power Modes     .229       12.9.1 Wait Mode     .229       12.9.2 Stop Mode     .230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12.10 RTC Registers     230       12.10.1 RTC Calibration Control Register (RTCCOMR)     231       12.10.2 RTC Calibration Data Register (RTCCDAT)     233       12.10.3 RTC Control Register 1 (RTCCR1)     234       12.10.4 RTC Control Register 2 (RTCCR2)     235       12.10.5 RTC Status Register (RTCSR)     237       12.10.6 Alarm Minute and Hour Registers (ALMR and ALHR)     240       12.10.7 Second Register (SECR)     241       12.10.8 Minute Register (MINR)     241       12.10.9 Hour Register (HRR)     242       12.10.10 Day Register (DAYR)     242       12.10.11 Month Register (MTHR)     243       12.10.12 Year Register (YRR)     243       12.10.13 Day-Of-Week Register (DOWR)     244       12.10.14 Chronograph Data Register (CHRR)     244 |

Data Sheet

MC68HC908LJ24/LK24 — Rev. 2.1

# Data Sheet — MC68HC908LJ24

# Section 1. General Description

# 1.1 Contents

| 1.2                   | Introduction                                          |  |  |  |  |  |  |  |

|-----------------------|-------------------------------------------------------|--|--|--|--|--|--|--|

| 1.3                   | Features                                              |  |  |  |  |  |  |  |

| 1.4                   | MCU Block Diagram                                     |  |  |  |  |  |  |  |

| 1.5                   | Pin Assignments42                                     |  |  |  |  |  |  |  |

| 1.6<br>1.6.1<br>1.6.2 | Pin Functions                                         |  |  |  |  |  |  |  |

| 1.6.3                 | LCD Bias Voltage (V <sub>LCD</sub> )                  |  |  |  |  |  |  |  |

| 1.6.4<br>1.6.5        | Oscillator Pins (OSC1 and OSC2)                       |  |  |  |  |  |  |  |

| 1.6.6<br>1.6.7        | External Interrupt Pin (IRQ)                          |  |  |  |  |  |  |  |

| 1.6.8                 | ADC Voltage High Reference Pin (V <sub>REFH</sub> )45 |  |  |  |  |  |  |  |

| 1.6.9<br>1.6.10       | ADC Voltage Low Reference Pin (V <sub>REFL</sub> )    |  |  |  |  |  |  |  |

| 1.6.11                | Port B I/O Pins (PTB7–PTB0)                           |  |  |  |  |  |  |  |

| 1.6.12<br>1.6.13      |                                                       |  |  |  |  |  |  |  |

| 1.6.14                | Port E I/O Pins (PTE7–PTE0)                           |  |  |  |  |  |  |  |

| 1.6.15<br>1.6.16      | LCD Backplane and Frontplane                          |  |  |  |  |  |  |  |

|                       | (BP0-BP2, BP3/FP0, FP1-FP10, FP27-FP32) 47            |  |  |  |  |  |  |  |

MC68HC908LJ24/LK24 — Rev. 2.1

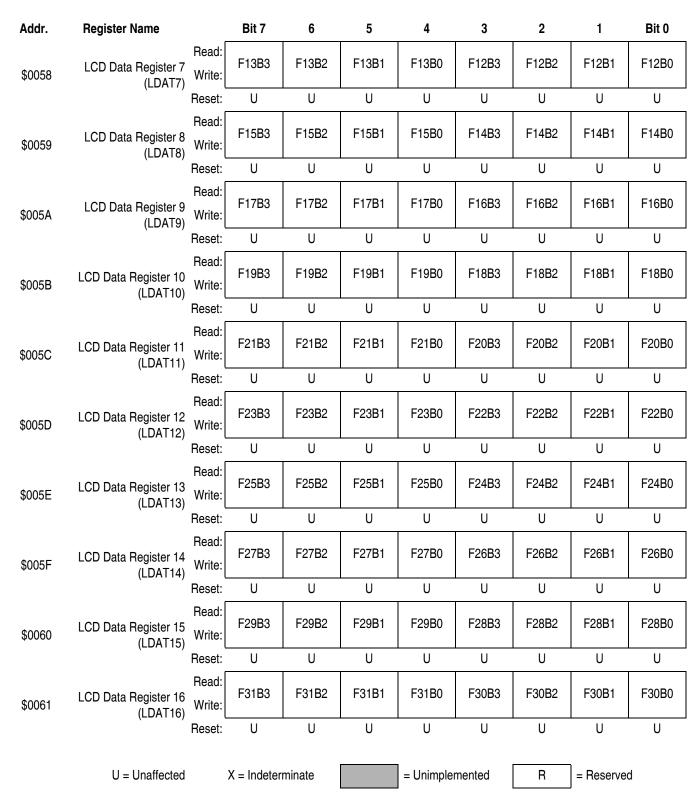

Figure 2-2. Control, Status, and Data Registers (Sheet 10 of 13)

MC68HC908LJ24/LK24 — Rev. 2.1

## **FLASH Memory (FLASH)**

### 4.8 FLASH Block Protection

Due to the ability of the on-board charge pump to erase and program the FLASH memory in the target application, provision is made to protect pages of memory from unintentional erase or program operations due to system malfunction. This protection is done by use of a FLASH block protect register (FLBPR). The FLBPR determines the range of the FLASH memory which is to be protected. The range of the protected area starts from a location defined by FLBPR and ends to the bottom of the FLASH memory (\$FFFF). When the memory is protected, the HVEN bit cannot be set in either erase or program operations.

NOTE:

The 48 bytes of user interrupt vectors are always protected, regardless of the value in the FLASH block protect register. A mass erase is required to erase the vectors.

When the FLBPR is program with \$20, the entire memory is protected from being programmed and erased. When the FLBPR is erased (\$FF), the entire memory is accessible for program and erase.

Once the FLBPR is programmed with a value other than \$FF, the FLBPR itself is protected. It can only be erased using a mass erase operation.

**NOTE:**

In performing a program or erase operation, the FLASH block protect register must be read after setting the PGM or ERASE bit and before asserting the HVEN bit

### 6.6.2 Stop Mode

#### The STOP instruction:

- Clears the interrupt mask (I bit) in the condition code register, enabling external interrupts. After exit from stop mode by external interrupt, the I bit remains clear. After exit by reset, the I bit is set.

- Disables the CPU clock.

After exiting stop mode, the CPU clock begins running after the oscillator stabilization delay.

## 6.7 CPU During Break Interrupts

If the break module is enabled, a break interrupt causes the CPU to execute the software interrupt instruction (SWI) at the completion of the current CPU instruction. (See **Section 23. Break Module (BRK)**.) The program counter vectors to \$FFFC-\$FFFD (\$FEFC-\$FEFD in monitor mode).

A return-from-interrupt instruction (RTI) in the break routine ends the break interrupt and returns the MCU to normal operation if the break interrupt has been deasserted.

# 6.8 Instruction Set Summary

Table 6-1 provides a summary of the M68HC08 instruction set.

# 6.9 Opcode Map

The opcode map is provided in Table 6-2.

### PLLON — PLL On Bit

This read/write bit activates the PLL and enables the VCO clock, CGMVCLK. PLLON cannot be cleared if the VCO clock is driving the base clock, CGMOUT (BCS = 1). (See **8.4.8 Base Clock Selector Circuit**.) Reset sets this bit so that the loop can stabilize as the MCU is powering up.

1 = PLL on

0 = PLL off

#### BCS — Base Clock Select Bit

This read/write bit selects either the oscillator output, CGMXCLK, or the divided VCO clock, CGMPCLK, as the source of the CGM output, CGMOUT. CGMOUT frequency is one-half the frequency of the selected clock. BCS cannot be set while the PLLON bit is clear. After toggling BCS, it may take up to three CGMXCLK and three CGMPCLK cycles to complete the transition from one source clock to the other. During the transition, CGMOUT is held in stasis. (See 8.4.8 Base Clock Selector Circuit.) Reset clears the BCS bit.

1 = CGMPCLK divided by two drives CGMOUT

0 = CGMXCLK divided by two drives CGMOUT

#### **NOTE:**

PLLON and BCS have built-in protection that prevents the base clock selector circuit from selecting the VCO clock as the source of the base clock if the PLL is off. Therefore, PLLON cannot be cleared when BCS is set, and BCS cannot be set when PLLON is clear. If the PLL is off (PLLON = 0), selecting CGMPCLK requires two writes to the PLL control register. (See **8.4.8 Base Clock Selector Circuit**.)

#### PRE1 and PRE0 — Prescaler Program Bits

These read/write bits control a prescaler that selects the prescaler power-of-two multiplier, P. (See **8.4.3 PLL Circuits** and **8.4.6 Programming the PLL.**) PRE1 and PRE0 cannot be written when the PLLON bit is set. Reset clears these bits.

These prescaler bits affects the relationship between the VCO clock and the final system bus clock.

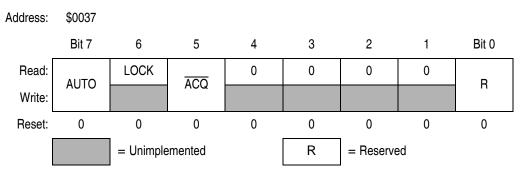

Figure 8-5. PLL Bandwidth Control Register (PBWCR)

#### AUTO — Automatic Bandwidth Control Bit

This read/write bit selects automatic or manual bandwidth control. When initializing the PLL for manual operation (AUTO = 0), clear the  $\overline{ACQ}$  bit before turning on the PLL. Reset clears the AUTO bit.

- 1 = Automatic bandwidth control

- 0 = Manual bandwidth control

#### LOCK — Lock Indicator Bit

When the AUTO bit is set, LOCK is a read-only bit that becomes set when the VCO clock, CGMVCLK, is locked (running at the programmed frequency). When the AUTO bit is clear, LOCK reads as logic 0 and has no meaning. The write one function of this bit is reserved for test, so this bit must *always* be written a 0. Reset clears the LOCK bit.

- 1 = VCO frequency correct or locked

- 0 = VCO frequency incorrect or unlocked

### ACQ — Acquisition Mode Bit

When the AUTO bit is set,  $\overline{ACQ}$  is a read-only bit that indicates whether the PLL is in acquisition mode or tracking mode. When the AUTO bit is clear,  $\overline{ACQ}$  is a read/write bit that controls whether the PLL is in acquisition or tracking mode.

In automatic bandwidth control mode (AUTO = 1), the last-written value from manual operation is stored in a temporary location and is recovered when manual operation resumes. Reset clears this bit, enabling acquisition mode.

- 1 = Tracking mode

- 0 = Acquisition mode

# **System Integration Module (SIM)**

| Addr.   | Register Name                       |                 | Bit 7 | 6         | 5      | 4    | 3    | 2          | 1            | Bit 0 |

|---------|-------------------------------------|-----------------|-------|-----------|--------|------|------|------------|--------------|-------|

| \$FE00  | SIM Break Status Register<br>(SBSR) | Read:<br>Write: | R     | R         | R      | R    | R    | R          | SBSW<br>Note | R     |

| (0-0.1) |                                     | Reset:          |       |           |        |      |      |            | 0            |       |

| Note: W | riting a logic 0 clears SBSW        | l.              |       |           |        |      |      |            |              |       |

|         |                                     | Read:           | POR   | PIN       | COP    | ILOP | ILAD | 0          | LVI          | 0     |

| \$FE01  | SIM Reset Status Register (SRSR)    | Write:          |       |           |        |      |      |            |              |       |

|         | (0.1017)                            | POR:            | 1     | 0         | 0      | 0    | 0    | 0          | 0            | 0     |

| \$FE03  |                                     | Read:<br>Write: | BCFE  | R         | R      | R    | R    | R          | R            | R     |

|         | (SBFCR)                             | Reset:          | 0     |           |        |      |      |            |              |       |

| \$FE04  | Interrupt Status Register 1 (INT1)  | Read:           | IF6   | IF5       | IF4    | IF3  | IF2  | IF1        | 0            | 0     |

|         |                                     | Write:          | R     | R         | R      | R    | R    | R          | R            | R     |

|         |                                     | Reset:          | 0     | 0         | 0      | 0    | 0    | 0          | 0            | 0     |

|         | Interrupt Status Register 2 (INT2)  | Read:           | IF14  | IF13      | IF12   | IF11 | IF10 | IF9        | IF8          | IF7   |

| \$FE05  |                                     | Write:          | R     | R         | R      | R    | R    | R          | R            | R     |

|         | (***-2)                             | Reset:          | 0     | 0         | 0      | 0    | 0    | 0          | 0            | 0     |

|         |                                     | Read:           | 0     | 0         | 0      | 0    | IF18 | IF17       | IF16         | IF15  |

| \$FE06  | (IN I 3)                            | Write:          | R     | R         | R      | R    | R    | R          | R            | R     |

|         |                                     | Reset:          | 0     | 0         | 0      | 0    | 0    | 0          | 0            | 0     |

|         |                                     |                 |       | = Unimple | mented |      | R    | = Reserved | I            |       |

Figure 9-2. SIM I/O Register Summary

### 9.3 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, CGMOUT, as shown in **Figure 9-3**. This clock can come from either the oscillator module or from the on-chip PLL. (See **Section 8. Clock Generator Module (CGM)**.)

# System Integration Module (SIM)

# 9.6 Exception Control

Normal, sequential program execution can be changed in three different ways:

- Interrupts:

- Maskable hardware CPU interrupts

- Non-maskable software interrupt instruction (SWI)

- Reset

- · Break interrupts

### 9.6.1 Interrupts

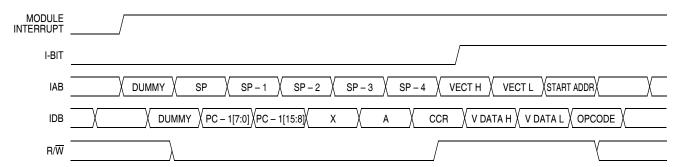

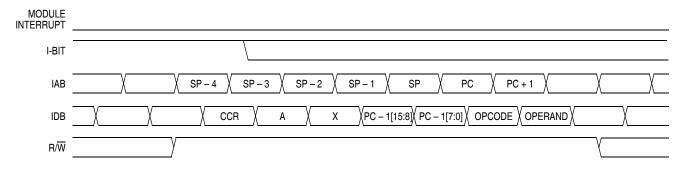

At the beginning of an interrupt, the CPU saves the CPU register contents on the stack and sets the interrupt mask (I bit) to prevent additional interrupts. At the end of an interrupt, the RTI instruction recovers the CPU register contents from the stack so that normal processing can resume. **Figure 9-8** shows interrupt entry timing, and **Figure 9-9** shows interrupt recovery timing.

Figure 9-8. Interrupt Entry Timing

Figure 9-9. Interrupt Recovery Timing

## System Integration Module (SIM)

### 9.6.1.1 Hardware Interrupts

A hardware interrupt does not stop the current instruction. Processing of a hardware interrupt begins after completion of the current instruction. When the current instruction is complete, the SIM checks all pending hardware interrupts. If interrupts are not masked (I bit clear in the condition code register) and if the corresponding interrupt enable bit is set, the SIM proceeds with interrupt processing; otherwise, the next instruction is fetched and executed.

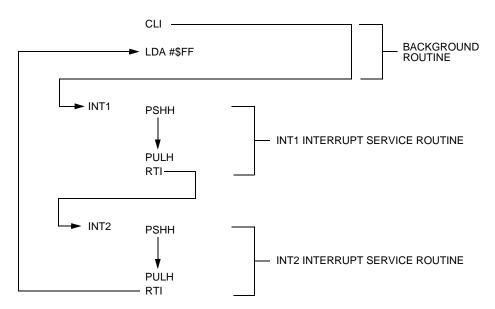

If more than one interrupt is pending at the end of an instruction execution, the highest priority interrupt is serviced first. **Figure 9-11** demonstrates what happens when two interrupts are pending. If an interrupt is pending upon exit from the original interrupt service routine, the pending interrupt is serviced before the LDA instruction is executed.

Figure 9-11. Interrupt Recognition Example

The LDA opcode is prefetched by both the INT1 and INT2 RTI instructions. However, in the case of the INT1 RTI prefetch, this is a redundant operation.

**NOTE:**

To maintain compatibility with the M6805 Family, the H register is not pushed on the stack during interrupt entry. If the interrupt service routine modifies the H register or uses the indexed addressing mode, software should save the H register and then restore it prior to exiting the routine.

# Data Sheet — MC68HC908LJ24

# Section 10. Monitor ROM (MON)

# 10.1 Contents

| 10.2 Introduction               |

|---------------------------------|

| 10.3 Features                   |

| 10.4 Functional Description     |

| 10.4.1 Entering Monitor Mode167 |

| 10.4.2 Data Format              |

| 10.4.3 Break Signal171          |

| 10.4.4 Baud Rate171             |

| 10.4.5 Commands172              |

| 10.5 Security177                |

| 10.6 ROM-Resident Routines179   |

| 10.6.1 PRGRNGE181               |

| 10.6.2 ERARNGE                  |

| 10.6.3 LDRNGE                   |

| 10.6.4 MON_PRGRNGE185           |

| 10.6.5 MON_ERARNGE186           |

| 10.6.6 MON_LDRNGE               |

| 10.6.7 EE_WRITE188              |

| 10.6.8 EE_READ191               |

MC68HC908LJ24/LK24 — Rev. 2.1

## 10.4 Functional Description

The monitor ROM receives and executes commands from a host computer. Figure 10-1 shows an example circuit used to enter monitor mode and communicate with a host computer via a standard RS-232 interface.

Simple monitor commands can access any memory address. In monitor mode, the MCU can execute code downloaded into RAM by a host computer while most MCU pins retain normal operating mode functions. All communication between the host computer and the MCU is through the PTA0 pin. A level-shifting and multiplexing interface is required between PTA0 and the host computer. PTA0 is used in a wired-OR configuration and requires a pullup resistor.

The monitor code allows enabling the PLL to generate the internal clock, provided the reset vector is blank, when the device is being clocked by a low-frequency crystal. This entry method, which is enabled when  $\overline{IRQ}$  is held low out of reset, is intended to support serial communication/programming at 9600 baud in monitor mode by stepping up the external frequency (assumed to be 32.768 kHz) by a fixed amount to generate the desired internal frequency (2.4576 MHz). Since this feature is enabled only when  $\overline{IRQ}$  is held low out of reset, it cannot be used when the reset vector is non-zero because entry into monitor mode in this case requires  $V_{TST}$  on  $\overline{IRQ}$ .

## 14.7 Queuing Transmission Data

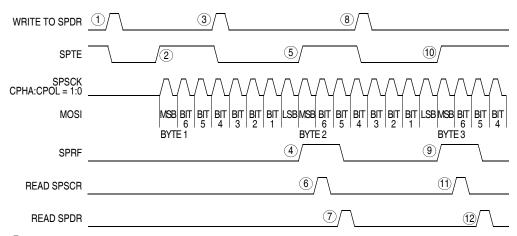

The double-buffered transmit data register allows a data byte to be queued and transmitted. For an SPI configured as a master, a queued data byte is transmitted immediately after the previous transmission has completed. The SPI transmitter empty flag (SPTE) indicates when the transmit data buffer is ready to accept new data. Write to the transmit data register only when the SPTE bit is high. **Figure 14-8** shows the timing associated with doing back-to-back transmissions with the SPI (SPSCK has CPHA: CPOL = 1:0).

- (1) CPU WRITES BYTE 1 TO SPDR, CLEARING SPTE BIT.

- 2 BYTE 1 TRANSFERS FROM TRANSMIT DATA REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

- ③ CPU WRITES BYTE 2 TO SPDR, QUEUEING BYTE 2 AND CLEARING SPTE BIT.

- (4) FIRST INCOMING BYTE TRANSFERS FROM SHIFT REGISTER TO RECEIVE DATA REGISTER, SETTING SPRF BIT.

- 5 BYTE 2 TRANSFERS FROM TRANSMIT DATA REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

- (6) CPU READS SPSCR WITH SPRF BIT SET.

- (7) CPU READS SPDR, CLEARING SPRF BIT.

- (8) CPU WRITES BYTE 3 TO SPDR, QUEUEING BYTE 3 AND CLEARING SPTE BIT.

- (9) SECOND INCOMING BYTE TRANSFERS FROM SHIFT REGISTER TO RECEIVE DATA REGISTER, SETTING SPRF BIT.

- (10) BYTE 3 TRANSFERS FROM TRANSMIT DATA REGISTER TO SHIFT REGISTER, SETTING SPTE BIT.

- (1) CPU READS SPSCR WITH SPRF BIT SET.

- 12 CPU READS SPDR, CLEARING SPRF BIT.

Figure 14-8. SPRF/SPTE CPU Interrupt Timing

The transmit data buffer allows back-to-back transmissions without the slave precisely timing its writes between transmissions as in a system with a single data buffer. Also, if no new data is written to the data buffer, the last value contained in the shift register is the next data word to be transmitted.

MC68HC908LJ24/LK24 — Rev. 2.1

Table 18-1. Port Control Register Bits Summary (Sheet 2 of 2)

| Port             | Bit     | DDR   | Module Control |                  |             | Pin                    |  |

|------------------|---------|-------|----------------|------------------|-------------|------------------------|--|

| Port             | DIL     | DDR   | Module         | Register         | Control Bit | - Pin                  |  |

|                  | 0       | DDRD0 |                | SPCR (\$0010)    | SPE         | PTD0/SS/CALIN          |  |

|                  | U       | DDRD0 |                | RTCCOMR (\$0040) | CAL         |                        |  |

|                  | 1       | DDRD1 | SPI            | SPCR (\$0010)    | SPE         | PTD1/MISO              |  |

|                  | 2       | DDRD2 | RTC            |                  | SFE         | PTD2/MOSI              |  |

|                  | 3       | DDRD3 |                | SPCR (\$0010)    | SPE         | PTD3/SPSCK/CALOUT      |  |

|                  | 3       | DDND3 |                | RTCCOMR (\$0040) | CAL         | F 1D3/3F 3CIVCALOUT    |  |

| D <sup>(1)</sup> | 4       | DDRD4 |                | KBIER (\$001C)   | KBIE4       | PTD4/KBI4/T1CLK        |  |

| D(·)             | 4       | DDND4 | KBI            | T1SC (\$0020)    | PS[2:0]     | F I D4/RBI4/ I TCLR    |  |

|                  | 5       | DDRD5 | TIM            | KBIER (\$001C)   | KBIE5       | PTD5/KBI5/T2CLK        |  |

|                  | 3       | DDND3 |                | T2SC (\$002B)    | PS[2:0]     | - F1D3/RBI3/12GER      |  |

|                  | 6       | DDRD6 |                | KBIER (\$001C)   | KBIE6       | PTD6/KBI6/SCL          |  |

|                  | 0       | DDND0 | KBI            | MMCR (\$006C)    | MMEN        | F 1D0/RBI0/SCL         |  |

|                  | 7       | DDRD7 | MMIIC          | KBIER (\$001C)   | KBIE7       | PTD7/KBI7/SDA          |  |

|                  | ,       | וטאטט |                | MMCR (\$006C)    | MMEN        | FIDI/KBII/SDA          |  |

|                  | 0       | DDRE0 |                |                  | PEE         | PTE0/FP11              |  |

|                  | 1       | DDRE1 | LCD            | CONFIG2 (\$001D) |             | PTE1/FP12              |  |

|                  | 2       | DDRE2 |                |                  |             | PTE2/FP13              |  |

| E                | 3       | DDRE3 |                |                  |             | PTE3/FP14              |  |

| _                | 4       | DDRE4 |                |                  |             | PTE4/FP15              |  |

|                  | 5       | DDRE5 |                |                  |             | PTE5/FP16<br>PTE6/FP17 |  |

|                  | 6       | DDRE6 |                |                  |             |                        |  |

|                  | 7       | DDRE7 |                |                  |             | PTE7/FP18              |  |

|                  | 0       | DDRF0 |                |                  |             | PTF0                   |  |

|                  | 1       | DDRF1 |                |                  |             | PTF1                   |  |

|                  | 2 DDRF2 |       |                |                  | PTF2        |                        |  |

| F                | 3       | DDRF3 |                |                  | _           | PTF3                   |  |

|                  | 4       | DDRF4 | _              |                  |             | PTF4                   |  |

|                  | 5       | DDRF5 |                |                  |             | PTF5                   |  |

|                  | 6       | DDRF6 |                |                  |             | PTF6                   |  |

|                  | 7       | DDRF7 |                |                  |             | PTF7                   |  |

### Notes:

MC68HC908LJ24/LK24 — Rev. 2.1

<sup>1.</sup> In addition to the standard I/O function on PTD0 and PTD3–PTD7 pins, these pins are shared with two other modules. For each of the pins, ONLY enable ONE module at any one time to avoid pin contention.

NOTE:

Setting a keyboard interrupt enable bit (KBIEx) forces the corresponding keyboard interrupt pin to be an input, overriding the data direction register. However, the data direction register bit must be a logic 0 for software to read the pin.

### 20.5.1 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pullup to reach a logic 1. Therefore a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

- 1. Mask keyboard interrupts by setting the IMASKK bit in the keyboard status and control register.

- 2. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

- 3. Write to the ACKK bit in the keyboard status and control register to clear any false interrupts.

- 4. Clear the IMASKK bit.

An interrupt signal on an edge-triggered pin can be acknowledged immediately after enabling the pin. An interrupt signal on an edge- and level-triggered interrupt pin must be acknowledged after a delay that depends on the external load.

Another way to avoid a false interrupt:

- 1. Configure the keyboard pins as outputs by setting the appropriate DDR bits in data direction register.

- 2. Write logic 1s to the appropriate data register bits.

- 3. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

# Section 21. Computer Operating Properly (COP)

### 21.1 Contents

| 21.2 Introduction                                                                             |

|-----------------------------------------------------------------------------------------------|

| 21.3 Functional Description                                                                   |

| 21.4 I/O Signals                                                                              |

| 21.4.1 ICLK                                                                                   |

| 21.4.2 STOP Instruction                                                                       |

| 21.4.3 COPCTL Write                                                                           |

| 21.4.4 Power-On Reset                                                                         |

| 21.4.5 Internal Reset                                                                         |

| 21.4.6 Reset Vector Fetch                                                                     |

| 21.4.7 COPD (COP Disable)                                                                     |

| 21.4.8 COPRS (COP Rate Select)                                                                |

| 21.5 COP Control Register                                                                     |

| 21.6 Interrupts419                                                                            |

| 21.7 Monitor Mode                                                                             |

| 21.8 Low-Power Modes     .419       21.8.1 Wait Mode     .420       21.8.2 Stop Mode     .420 |

| 21.9 COP Module During Break Mode                                                             |

# 21.2 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by clearing the COP counter periodically. The COP module can be disabled through the COPD bit in the configuration register 1 (CONFIG1).

MC68HC908LJ24/LK24 — Rev. 2.1

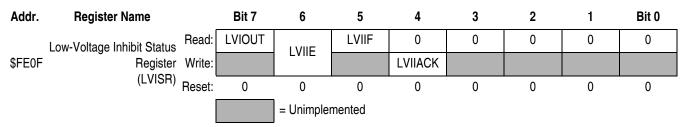

# Low-Voltage Inhibit (LVI)

Figure 22-1. LVI I/O Register Summary

### 22.4 Functional Description

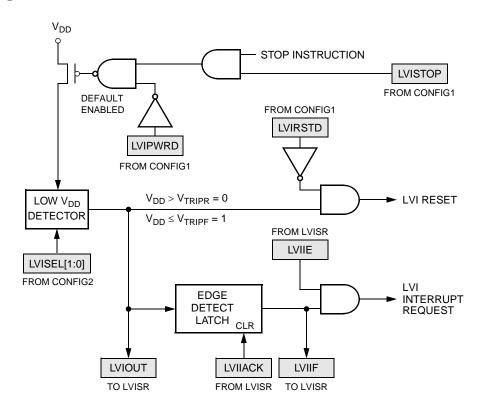

Figure 22-2 shows the structure of the LVI module.

Figure 22-2. LVI Module Block Diagram

The LVI is enabled out of reset. The LVI module contains a bandgap reference circuit and comparator. Clearing the LVI power disable bit, LVIPWRD, enables the LVI to monitor  $V_{DD}$  voltage. Clearing the LVI reset disable bit, LVIRSTD, enables the LVI module to generate a reset when  $V_{DD}$  falls below a voltage,  $V_{TRIPF}$ . Setting the LVI enable in stop mode bit, LVISTOP, enables the LVI to operate in stop mode.

**Data Sheet**

MC68HC908LJ24/LK24 — Rev. 2.1

## **Break Module (BRK)**

### BRKA — Break Active Bit

This read/write status and control bit is set when a break address match occurs. Writing a logic 1 to BRKA generates a break interrupt. Clear BRKA by writing a logic 0 to it before exiting the break routine. Reset clears the BRKA bit.

1 = (When read) Break address match

0 = (When read) No break address match

### 23.6.2 Break Address Registers

The break address registers (BRKH and BRKL) contain the high and low bytes of the desired breakpoint address. Reset clears the break address registers.

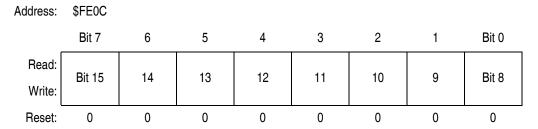

Figure 23-4. Break Address Register High (BRKH)

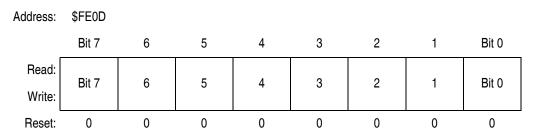

Figure 23-5. Break Address Register Low (BRKL)

### 23.6.3 SIM Break Status Register

The SIM break status register (SBSR) contains a flag to indicate that a break caused an exit from wait mode. The flag is useful in applications requiring a return to wait mode after exiting from a break interrupt.

**Data Sheet**

MC68HC908LJ24/LK24 — Rev. 2.1