Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HC08                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 8MHz                                                        |

| Connectivity               | I <sup>2</sup> C, IRSCI, SPI                                |

| Peripherals                | LCD, LVD, POR, PWM                                          |

| Number of I/O              | 40                                                          |

| Program Memory Size        | 24KB (24K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 768 × 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                   |

| Data Converters            | A/D 6x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 64-QFP                                                      |

| Supplier Device Package    | 64-QFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908lj24cfuer |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table         | e Title                                   | Ρ       | age |

|---------------|-------------------------------------------|---------|-----|

| 17-1          | Pin Name Conventions                      |         | 350 |

| 17-3          | LCD Bias Voltage Control.                 |         | 369 |

| 17-2          | Resistor Ladder Selection.                |         | 369 |

| 17-4          | Fast Charge Duty Cycle Selection          |         | 370 |

| 17-5          | LCD Duty Cycle Selection                  |         | 371 |

| 17-6          | LCD Waveform Base Clock Selection         | • • • • | 371 |

| 18-1          | Port Control Register Bits Summary        |         | 378 |

| 18-2          | Port A Pin Functions                      |         | 382 |

| 18-3          | Port B Pin Functions                      |         | 386 |

| 18-4          | Port C Pin Functions                      |         | 389 |

| 18-5          | Port D Pin Functions                      |         | 393 |

| 18-6          | Port E Pin Functions                      |         | 396 |

| 18-7          | Port F Pin Functions                      |         | 399 |

| 20-1          | Pin Name Conventions                      |         | 408 |

| 22-1          | LVI Status Register (LVISR)               |         | 425 |

| 22-2          | LVIOUT Bit Indication                     | • • • • | 425 |

| 24-1          | Absolute Maximum Ratings                  |         | 436 |

| 24-2          | Functional Operating Range                |         | 437 |

| 24-3          | Thermal Characteristics                   |         | 437 |

| 24-4          | 5V DC Electrical Characteristics          |         | 438 |

| 24-5          | 3.3V DC Electrical Characteristics        |         | 439 |

| 24 <b>-</b> 6 | 5V Control Timing                         |         | 440 |

| 24-7          | 3.3V Control Timing                       |         |     |

| 24-8          | 5V Oscillator Specifications              |         | 441 |

| 24-9          |                                           |         |     |

|               | ) 5V ADC Electrical Characteristics       |         |     |

|               | 3.3V ADC Electrical Characteristics       |         |     |

| 24-12         | 2 Timer Interface Module Characteristics  |         | 445 |

|               | 3 CGM Electrical Specifications           |         |     |

|               | 5V SPI Characteristics                    |         |     |

|               | 5 3.3V SPI Characteristics                |         |     |

| 24-16         | 5 FLASH Memory Electrical Characteristics |         | 450 |

| 26-1          | MC Order Numbers                          |         | 457 |

MC68HC908LJ24/LK24 - Rev. 2.1

# 1.2 Introduction

The MC68HC908LJ24 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08 Family is based on the customer-specified integrated circuit (CSIC) design strategy. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

## 1.3 Features

Features of the MC68HC908LJ24 include the following:

- High-performance M68HC08 architecture

- Fully upward-compatible object code with M6805, M146805, and M68HC05 Families

- 8-MHz at 5V operating voltage

- 4-MHz at 3.3V operating voltage

- 32.768kHz crystal oscillator clock input with 32MHz internal PLL

- Optional continuous crystal oscillator operation in stop mode

- 24K-bytes user program FLASH memory with security<sup>1</sup> feature

- 768 bytes of on-chip RAM

- Up to 48 general-purpose input/output (I/O) pins:

- High current 15mA sink capability on 30 pins

- Two 16-bit, 2-channel timer interface modules (TIM1 and TIM2) with selectable input capture, output compare, PWM capability on each channel, and external clock input option (T1CLK and T2CLK)

- Real time clock (RTC) with:

- Clock, calendar, alarm, and chronograph functions

- Selectable periodic interrupt requests for seconds, minutes, hours, days, 2-Hz, 4-Hz, 8-Hz, 16-Hz, and 128-Hz

<sup>1.</sup> No security feature is absolutely secure. However, Freescale strategy is to make reading or copying the FLASH difficult for unauthorized users.

# NP

# Memory Map

| Addr.  | Register Name                           | _               | Bit 7       | 6      | 5     | 4         | 3      | 2     | 1         | Bit 0  |

|--------|-----------------------------------------|-----------------|-------------|--------|-------|-----------|--------|-------|-----------|--------|

| \$0027 | Timer 1 Channel 0<br>Register Low       | Read:<br>Write: | Bit 7       | 6      | 5     | 4         | 3      | 2     | 1         | Bit 0  |

|        | (T1CH0L)                                | Reset:          | Х           | Х      | Х     | Х         | Х      | Х     | Х         | Х      |

|        | Timer 1 Channel 1 Status                | Read:           | CH1F        | CH1IE  | 0     | MS1A      | ELS1B  | ELS1A | TOV1      | CH1MAX |

|        | and Control Register                    | Write:          | 0           | CHIE   |       | MOTA      | ELSID  | ELSIA | 1001      | CHINAA |

|        | (T1SC1)                                 | Reset:          | 0           | 0      | 0     | 0         | 0      | 0     | 0         | 0      |

| \$0029 | Timer 1 Channel 1<br>Register High      | Read:<br>Write: | Bit 15      | 14     | 13    | 12        | 11     | 10    | 9         | Bit 8  |

|        | (T1CH1H)                                | Reset:          | Х           | Х      | Х     | Х         | Х      | Х     | Х         | Х      |

| \$002A | Timer 1 Channel 1<br>Register Low       | Read:<br>Write: | Bit 7       | 6      | 5     | 4         | 3      | 2     | 1         | Bit 0  |

|        | (T1CH1L)                                | Reset:          | Х           | Х      | Х     | Х         | Х      | Х     | Х         | Х      |

| \$002B | Timer 2 Status and Control              | Read:           | TOF         | TOIE   | TSTOP | 0         | 0      | PS2   | PS1       | PS0    |

|        | Register                                | Write:          | 0           | TOIL   |       | TRST      |        | F 52  |           | F30    |

|        | (T2SC)                                  | Reset:          | 0           | 0      | 1     | 0         | 0      | 0     | 0         | 0      |

|        | TOONTUN                                 | Read:           | Bit 15      | 14     | 13    | 12        | 11     | 10    | 9         | Bit 8  |

| \$002C |                                         | Write:          |             |        |       |           |        |       |           |        |

|        |                                         | Reset:          | 0           | 0      | 0     | 0         | 0      | 0     | 0         | 0      |

|        | Timer 2 Counter                         | Read:           | Bit 7       | 6      | 5     | 4         | 3      | 2     | 1         | Bit 0  |

| \$002D | Register Low                            | Write:          |             |        |       |           |        |       |           |        |

|        | (T2CNTL)                                | Reset:          | 0           | 0      | 0     | 0         | 0      | 0     | 0         | 0      |

| \$002E | Timer 2 Counter Modulo<br>Register High | Read:<br>Write: | Bit 15      | 14     | 13    | 12        | 11     | 10    | 9         | Bit 8  |

|        | (T2MODH)                                | Reset:          | 1           | 1      | 1     | 1         | 1      | 1     | 1         | 1      |

| \$002F | Timer 2 Counter Modulo<br>Register Low  | Read:<br>Write: | Bit 7       | 6      | 5     | 4         | 3      | 2     | 1         | Bit 0  |

|        | (T2MODL)                                | Reset:          | 1           | 1      | 1     | 1         | 1      | 1     | 1         | 1      |

|        | Timer 2 Channel 0 Status                | Read:           | CH0F        | CHOIE  | MS0B  | MS0A      | ELS0B  | ELS0A | TOV0      | CHOMAX |

| \$0030 | and Control Register                    | Write:          | 0           | CHUE   | MOUD  | WISUA     | ELSUB  | ELSUA | 1000      | CHUWAA |

|        | (T2SC0)                                 | Reset:          | 0           | 0      | 0     | 0         | 0      | 0     | 0         | 0      |

|        | U = Unaffected                          |                 | X = Indeter | minate |       | = Unimple | mented | R     | = Reserve | d      |

Figure 2-2. Control, Status, and Data Registers (Sheet 5 of 13)

## 4.6 FLASH Mass Erase Operation

Use the following procedure to erase the entire FLASH memory:

- 1. Set both the ERASE bit and the MASS bit in the FLASH control register.

- 2. Read the FLASH block protect register.

- 3. Write any data to any FLASH address within the FLASH memory address range.

- 4. Wait for a time,  $t_{nvs}$  (10µs).

- 5. Set the HVEN bit.

- 6. Wait for a time t<sub>merase</sub> (4ms).

- 7. Clear the ERASE bit.

- 8. Wait for a time,  $t_{nvh1}$  (100 µs).

- 9. Clear the HVEN bit.

- 10. After time,  $t_{rcv}$  (1µs), the memory can be accessed again in read mode.

- **NOTE:** Programming and erasing of FLASH locations cannot be performed by code being executed from the FLASH memory; the code must be executed from RAM. While these operations must be performed in the order as shown, but other unrelated operations may occur between the steps.

| Source<br>Form                                                                                 | Operation                                            | Description                                                         |   | E | ffe<br>C( | ct o<br>CR | on | • | Address<br>Mode                                     | Opcode                                           | Operand                                   | les                             |

|------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------|---|---|-----------|------------|----|---|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------|---------------------------------|

|                                                                                                |                                                      |                                                                     | v | н | I         | N          | z  | С | Add                                                 | odo                                              | Ope                                       | Cycles                          |

| BCS rel                                                                                        | Branch if Carry Bit Set (Same as BLO)                | PC ← (PC) + 2 + <i>rel</i> ? (C) = 1                                | - | - | -         | -          | -  | - | REL                                                 | 25                                               | rr                                        | 3                               |

| BEQ rel                                                                                        | Branch if Equal                                      | PC ← (PC) + 2 + <i>rel</i> ? (Z) = 1                                | - | - | -         | -          | -  | - | REL                                                 | 27                                               | rr                                        | 3                               |

| BGE opr                                                                                        | Branch if Greater Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 0$          | - | - | -         | -          | -  | - | REL                                                 | 90                                               | rr                                        | 3                               |

| BGT opr                                                                                        | Branch if Greater Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 0$ | - | - | -         | _          | -  | - | REL                                                 | 92                                               | rr                                        | 3                               |

| BHCC rel                                                                                       | Branch if Half Carry Bit Clear                       | PC ← (PC) + 2 + <i>rel</i> ? (H) = 0                                | - | - | -         | -          | -  | - | REL                                                 | 28                                               | rr                                        | 3                               |

| BHCS rel                                                                                       | Branch if Half Carry Bit Set                         | PC ← (PC) + 2 + <i>rel</i> ? (H) = 1                                | - | - | -         | -          | -  | - | REL                                                 | 29                                               | rr                                        | 3                               |

| BHI rel                                                                                        | Branch if Higher                                     | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 0$          | - | - | -         | -          | -  | - | REL                                                 | 22                                               | rr                                        | 3                               |

| BHS rel                                                                                        | Branch if Higher or Same<br>(Same as BCC)            | PC ← (PC) + 2 + <i>rel</i> ? (C) = 0                                | - | - | -         | -          | -  | - | REL                                                 | 24                                               | rr                                        | 3                               |

| BIH rel                                                                                        | Branch if IRQ Pin High                               | $PC \leftarrow (PC) + 2 + rel? \overline{IRQ} = 1$                  | - | - | -         | -          | -  | - | REL                                                 | 2F                                               | rr                                        | 3                               |

| BIL rel                                                                                        | Branch if IRQ Pin Low                                | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 0$                 | - | - | -         | -          | -  | - | REL                                                 | 2E                                               | rr                                        | 3                               |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT ,X<br>BIT opr,SP<br>BIT opr,SP | Bit Test                                             | (A) & (M)                                                           | 0 | _ | _         | \$         | \$ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9EE5<br>9ED5 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff | 2<br>3<br>4<br>3<br>2<br>4<br>5 |

| BLE opr                                                                                        | Branch if Less Than or Equal To (Signed Operands)    | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 1$ | - | - | -         | -          | -  | - | REL                                                 | 93                                               | rr                                        | 3                               |

| BLO rel                                                                                        | Branch if Lower (Same as BCS)                        | PC ← (PC) + 2 + <i>rel</i> ? (C) = 1                                | - | - | -         | -          | -  | - | REL                                                 | 25                                               | rr                                        | 3                               |

| BLS rel                                                                                        | Branch if Lower or Same                              | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 1$          | - | - | -         | -          | -  | - | REL                                                 | 23                                               | rr                                        | 3                               |

| BLT opr                                                                                        | Branch if Less Than (Signed Operands)                | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 1$          | - | - | -         | -          | -  | - | REL                                                 | 91                                               | rr                                        | 3                               |

| BMC rel                                                                                        | Branch if Interrupt Mask Clear                       | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (I) = 0$                   | - | Ι | -         | -          | -  | - | REL                                                 | 2C                                               | rr                                        | 3                               |

| BMI rel                                                                                        | Branch if Minus                                      | PC ← (PC) + 2 + <i>rel</i> ? (N) = 1                                | - | - | -         | -          | -  | - | REL                                                 | 2B                                               | rr                                        | 3                               |

| BMS rel                                                                                        | Branch if Interrupt Mask Set                         | PC ← (PC) + 2 + <i>rel</i> ? (I) = 1                                | - | - | -         | -          | -  | - | REL                                                 | 2D                                               | rr                                        | 3                               |

| BNE rel                                                                                        | Branch if Not Equal                                  | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) = 0$                   | _ | _ | -         | _          | -  | _ | REL                                                 | 26                                               | rr                                        | 3                               |

| BPL rel                                                                                        | Branch if Plus                                       | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N) = 0$                   | - | - | -         | _          | -  | - | REL                                                 | 2A                                               | rr                                        | 3                               |

| BRA rel                                                                                        | Branch Always                                        | $PC \leftarrow (PC) + 2 + \mathit{rel}$                             | _ | _ | -         | _          | -  | _ | REL                                                 | 20                                               | rr                                        | 3                               |

#### Table 6-1. Instruction Set Summary (Sheet 2 of 8)

#### 9.3.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt, break, or reset, the SIM allows ICLK to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay timeout. This timeout is selectable as 4096 or 32 ICLK cycles. (See **9.7.2 Stop Mode**.)

In wait mode, the CPU clocks are inactive. The SIM also produces two sets of clocks for other modules. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

#### 9.4 Reset and System Initialization

The MCU has these reset sources:

- Power-on reset module (POR)

- External reset pin (RST)

- Computer operating properly module (COP)

- Low-voltage inhibit module (LVI)

- Illegal opcode

- Illegal address

All of these resets produce the vector \$FFFE:\$FFFF (\$FEFE:\$FEFF in monitor mode) and assert the internal reset signal (IRST). IRST causes all registers to be returned to their default values and all modules to be returned to their reset states.

An internal reset clears the SIM counter (see **9.5 SIM Counter**), but an external reset does not. Each of the resets sets a corresponding bit in the SIM reset status register (SRSR). (See **9.8 SIM Registers**.)

Monitor ROM (MON)

**Table 10-3** lists external frequencies required to achieve a standard baud rate of 9600 BPS. Other standard baud rates can be accomplished using proportionally higher or lower frequency generators. If using a crystal as the clock source, be aware of the upper frequency limit that the internal clock module can handle.

| External<br>Frequency | ĪRQ              | PTC1 | Internal<br>Frequency | Baud Rate<br>(BPS) |

|-----------------------|------------------|------|-----------------------|--------------------|

| 4.9152 MHz            | V <sub>TST</sub> | 0    | 2.4576 MHz            | 9600               |

| 9.8304 MHz            | V <sub>TST</sub> | 1    | 2.4576 MHz            | 9600               |

| 9.8304 MHz            | V <sub>DD</sub>  | Х    | 2.4576 MHz            | 9600               |

| 32.768 kHz            | V <sub>SS</sub>  | Х    | 2.4576 MHz            | 9600               |

Table 10-3. Monitor Baud Rate Selection

#### 10.4.5 Commands

The monitor ROM firmware uses these commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

The monitor ROM firmware echoes each received byte back to the PTA0 pin for error checking. An 11-bit delay at the end of each command allows the host to send a break character to cancel the command. A delay of two bit times occurs before each echo and before READ, IREAD, or READSP data is returned. The data returned by a read command appears after the echo of the last byte of the command.

**NOTE:** Wait one bit time after each echo before sending the next byte.

# Monitor ROM (MON)

**NOTE:** The EE\_READ routine is unable to check for incorrect data blocks, such as the FLASH page boundary address and data size. It is the responsibility of the user to ensure the starting address indicated in the data block is at the FLASH page boundary and the data size is 2 to 15. If the FLASH page is programmed with a data array with a different size, the EE\_READ call will be ignored.

# 12.4 I/O Pins

Two RTC clock calibration pins are shared with standard port I/O pins.

| RTC<br>Generic Pin Name | Full MCU Pin Name                | Pin Selected for RTC Function by<br>Bits in RTCCOMR (\$0040) |  |  |

|-------------------------|----------------------------------|--------------------------------------------------------------|--|--|

| CALIN                   | PTD0/SS/CALIN                    | AUTOCAL                                                      |  |  |

| CALOUT                  | PTD3/SPSCK/CALOUT <sup>(1)</sup> | OUTF[1:0}                                                    |  |  |

#### Table 12-1. Pin Name Conventions

#### Notes:

1. Do not enable the SPI function if the pin is used for RTC calibration.

| Addr.      | Register Name                         |        | Bit 7      | 6      | 5      | 4               | 3      | 2     | 1          | Bit 0  |

|------------|---------------------------------------|--------|------------|--------|--------|-----------------|--------|-------|------------|--------|

|            |                                       | Read:  | 0          | 0      | CAL    | AUTOCAL         | OUTF1  | OUTF0 | 0          | 0      |

| \$0040     |                                       | Write: | R          | R      | UAL    | AUTOCAL         | OUTFI  | OUTFU | RTCWE1     | RTCWE0 |

|            |                                       | Reset: | 0          | 0      | 0      | 0               | 0      | 0     | 0          | 0      |

|            | RTC Calibration Data                  | Read:  | EOVL       | 0      | E5     | E4              | E3     | E2    | E1         | E0     |

| \$0041     | Register                              | Write: |            |        | LJ     | L7              | LU     |       | <b>L</b> 1 | LU     |

|            | (RTCCDAT)                             | Reset: | U          | 0      | U      | U               | U      | U     | U          | U      |

|            | DTC Control Deviator 1                | Read:  | ALMIE      | CHRIE  | DAYIE  | HRIE            | MINIE  | SECIE | TB1IE      | TB2IE  |

| \$0042     | 2 RTC Control Register 1<br>(RTCCR1)  | Write: | e:         | OTTAL  | DATIE  |                 |        | GLOIL | IBIL       | IDEIL  |

|            |                                       | Reset: | 0          | 0      | 0      | 0               | 0      | 0     | 0          | 0      |

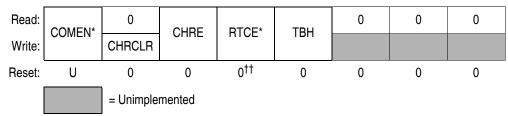

|            | RTC Control Register 2<br>(RTCCR2)    | Read:  | COMEN      | 0      | CHRE   | RTCE            | TBH    | 0     | 0          | 0      |

| \$0043     |                                       | Write: | COMEN      | CHRCLR | 01111L |                 |        |       |            |        |

|            | , , , , , , , , , , , , , , , , , , , | Reset: | U          | 0      | 0      | 0 <sup>††</sup> | 0      | 0     | 0          | 0      |

|            |                                       | Read:  | ALMF       | CHRF   | DAYF   | HRF             | MINF   | SECF  | TB1F       | TB2F   |

| \$0044     | RTC Status Register<br>(RTCSR)        | Write: |            |        |        |                 |        |       |            |        |

|            | ,                                     | Reset: | 0          | 0      | 0      | 0               | 0      | 0     | 0          | 0      |

|            |                                       | Read:  | 0          | 0      | AM5    | AM4             | AM3    | AM2   | AM1        | AM0    |

| \$0045     | Alarm Minute Register<br>(ALMR)       | Write: |            |        | AIVIJ  |                 | AIVIO  |       |            | AIVIO  |

|            | (                                     | Reset: | 0          | 0      | U      | U               | U      | U     | U          | U      |

| †† Reset b | †† Reset by POR only.                 |        |            |        |        |                 |        |       |            |        |

|            |                                       |        | U = Unaffe | cted   |        | = Unimpler      | nented | R     | = Reserved | b      |

Figure 12-1. RTC I/O Register Summary

MC68HC908LJ24/LK24 - Rev. 2.1

#### SECIE — Second Interrupt Enable

This read/write bit enables the second flag, SECF, to generate CPU interrupt requests. Reset clears the SECIE bit.

- 1 = SECF enabled to generate CPU interrupt

- 0 = SECF not enabled to generate CPU interrupt

- TB1IE Timebase 1 Interrupt Enable

This read/write bit enables the timebase1 flag, TB1F, to generate CPU interrupt requests. Reset clears the TB1IE bit.

- 1 = TB1F enabled to generate CPU interrupt

- 0 = TB1F not enabled to generate CPU interrupt

TB2IE — Timebase 2 Interrupt Enable

This read/write bit enables the timebase2 flag, TB2F, to generate CPU interrupt requests. Reset clears the TB2IE bit.

- 1 = TB2F enabled to generate CPU interrupt

- 0 = TB2F not enabled to generate CPU interrupt

#### 12.10.4 RTC Control Register 2 (RTCCR2)

The RTC control register 2 (RTCCR2) contains control and clock selection bits for RTC operation.

Address: \$0043

†† Reset by POR only.

\* COMEN and RTCE bits are write-protected; unprotect by a write sequence to RTCWE[1:0] in RTCCOMR.

#### Figure 12-9. RTC Control Register 2 (RTCCR2)

COMEN — RTC Compensation Enable

This read/write bit enables the clock compensation mechanism for CGMXCLK frequency errors. Reset has no effect on COMEN bit.

- 1 = Compensation mechanism enabled

- 0 = Compensation mechanism not enabled

## 13.3 Features

Features of the SCI module include the following:

- Full duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- Programmable 8-bit or 9-bit character length

- Separately enabled transmitter and receiver

- Separate receiver and transmitter CPU interrupt requests

- Two receiver wakeup methods:

- Idle line wakeup

- Address mark wakeup

- Interrupt-driven operation with eight interrupt flags:

- Transmitter empty

- Transmission complete

- Receiver full

- Idle receiver input

- Receiver overrun

- Noise error

- Framing error

- Parity error

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

Features of the infrared (IR) sub-module include the following:

- IR sub-module enable/disable for infrared SCI or conventional SCI on TxD and RxD pins

- Software selectable infrared modulation/demodulation (3/16, 1/16 or 1/32 width pulses)

MC68HC908LJ24/LK24 — Rev. 2.1

When an SPI is configured as a master, the  $\overline{SS}$  input can be used in conjunction with the MODF flag to prevent multiple masters from driving MOSI and SPSCK. (See **14.8.2 Mode Fault Error**.) For the state of the  $\overline{SS}$  pin to set the MODF flag, the MODFEN bit in the SPSCK register must be set. If the MODFEN bit is low for an SPI master, the  $\overline{SS}$  pin can be used as a general-purpose I/O under the control of the data direction register of the shared I/O port. With MODFEN high, it is an input-only pin to the SPI regardless of the state of the data direction register of the shared I/O port.

The CPU can always read the state of the  $\overline{SS}$  pin by configuring the appropriate pin as an input and reading the port data register. (See **Table 14-3**.)

| SPE | SPMSTR           | MODFEN | SPI Configuration   | State of SS Logic                         |

|-----|------------------|--------|---------------------|-------------------------------------------|

| 0   | X <sup>(1)</sup> | х      | Not enabled         | General-purpose I/O;<br>SS ignored by SPI |

| 1   | 0                | Х      | Slave               | Input-only to SPI                         |

| 1   | 1                | 0      | Master without MODF | General-purpose I/O;<br>SS ignored by SPI |

| 1   | 1                | 1      | Master with MODF    | Input-only to SPI                         |

Table 14-3. SPI Configuration

Note 1. X = Don't care

#### 14.13.5 CGND (Clock Ground)

CGND is the ground return for the serial clock pin, SPSCK, and the ground for the port output buffers. It is internally connected to  $V_{SS}$  as shown in Table 14-1.

# Section 15. Multi-Master IIC Interface (MMIIC)

## 15.1 Contents

| 15.2 Introduction                                           |

|-------------------------------------------------------------|

| 15.3 Features                                               |

| 15.4 I/O Pins                                               |

| 15.5 Multi-Master IIC Registers                             |

| 15.5.1 Multi-Master IIC Address Register (MMADR)            |

| 15.5.2 Multi-Master IIC Control Register (MMCR)             |

| 15.5.3 Multi-Master IIC Master Control Register (MIMCR) 324 |

| 15.5.4 Multi-Master IIC Status Register (MMSR)              |

| 15.5.5 Multi-Master IIC Data Transmit Register (MMDTR) 328  |

| 15.5.6 Multi-Master IIC Data Receive Register (MMDRR) 329   |

| 15.6 Programming Considerations                             |

### 15.2 Introduction

This Multi-master IIC (MMIIC) Interface is designed for internal serial communication between the MCU and other IIC devices. A hardware circuit generates "start" and "stop" signal, while byte by byte data transfer is interrupt driven by the software algorithm. Therefore, it can greatly help the software in dealing with other devices to have higher system efficiency in a typical digital monitor system.

This module not only can be applied in internal communications, but can also be used as a typical command reception serial bus for factory setup and alignment purposes. It also provides the flexibility of hooking additional devices to an existing system for future expansion without adding extra hardware.

If the external clock (CGMXCLK) is equal to or greater than 1MHz, CGMXCLK can be used as the clock source for the ADC. If CGMXCLK is less than 1MHz, use the PLL-generated bus clock as the clock source. As long as the internal ADC clock is at  $f_{ADIC}$ , correct operation can be guaranteed.

1 = Internal bus clock

0 = External clock, CGMXCLK

$$f_{ADIC} = \frac{CGMXCLK \text{ or bus frequency}}{ADIV[2:0]}$$

MODE1 and MODE0 — Modes of Result Justification

MODE1 and MODE0 selects between four modes of operation. The manner in which the ADC conversion results will be placed in the ADC data registers is controlled by these modes of operation. Reset returns right-justified mode.

| MODE1 | MODE0 | ADC Clock Rate                |

|-------|-------|-------------------------------|

| 0     | 0     | 8-bit truncated mode          |

| 0     | 1     | Right justified mode          |

| 1     | 0     | Left justified mode           |

| 1     | 1     | Left justified sign data mode |

Table 16-3. ADC Mode Select

# Liquid Crystal Display (LCD) Driver

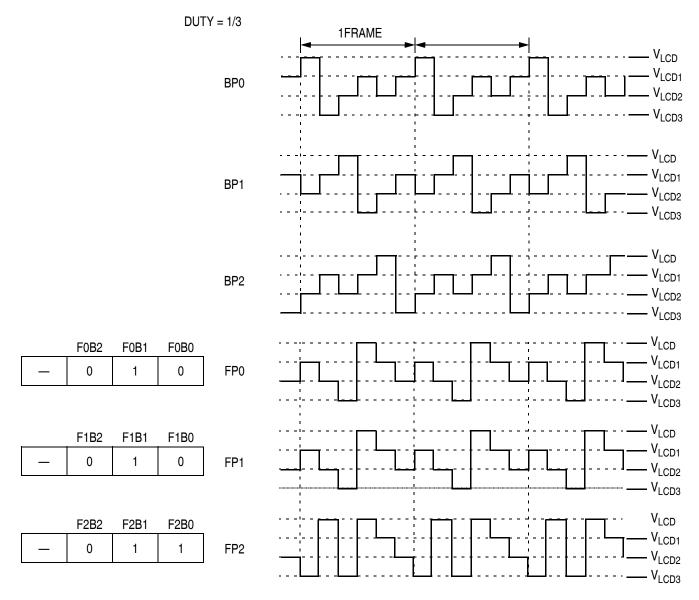

Figure 17-13. BP0–BP2 and FP0–FP2 Output Waveforms for 7-Segment Display Example

# Input/Output (I/O) Ports

#### 19.4.1 IRQ Pin

A logic 0 on the  $\overline{IRQ}$  pin can latch an interrupt request into the IRQ latch. A vector fetch, software clear, or reset clears the IRQ latch.

If the MODE bit is set, the IRQ pin is both falling-edge-sensitive and lowlevel-sensitive. With MODE set, both of the following actions must occur to clear IRQ:

- Vector fetch or software clear A vector fetch generates an interrupt acknowledge signal to clear the latch. Software may generate the interrupt acknowledge signal by writing a logic 1 to the ACK bit in the interrupt status and control register (INTSCR). The ACK bit is useful in applications that poll the IRQ pin and require software to clear the IRQ latch. Writing to the ACK bit prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACK does not affect subsequent transitions on the IRQ pin. A falling edge that occurs after writing to the ACK bit latches another interrupt request. If the IRQ mask bit, IMASK, is clear, the CPU loads the program counter with the vector address at locations \$FFFA and \$FFFB.

- Return of the IRQ pin to logic 1 As long as the IRQ pin is at logic 0, IRQ remains active.

The vector fetch or software clear and the return of the  $\overline{IRQ}$  pin to logic 1 may occur in any order. The interrupt request remains pending as long as the  $\overline{IRQ}$  pin is at logic 0. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

If the MODE bit is clear, the  $\overline{IRQ}$  pin is falling-edge-sensitive only. With MODE clear, a vector fetch or software clear immediately clears the IRQ latch.

The IRQF bit in the INTSCR register can be used to check for pending interrupts. The IRQF bit is not affected by the IMASK bit, which makes it useful in applications where polling is preferred.

Use the BIH of BIL instruction to read the logic level on the IRQ pin.

**NOTE:** When using the level-sensitive interrupt trigger, avoid false interrupts by masking interrupt requests in the interrupt routine.

# Section 24. Electrical Specifications

## 24.1 Contents

| 24.2  | Introduction                           | 35 |

|-------|----------------------------------------|----|

| 24.3  | Absolute Maximum Ratings43             | 36 |

| 24.4  | Functional Operating Range43           | 37 |

| 24.5  | Thermal Characteristics                | 37 |

| 24.6  | 5V DC Electrical Characteristics       | 38 |

| 24.7  | 3.3V DC Electrical Characteristics     | 39 |

| 24.8  | 5V Control Timing                      | 10 |

| 24.9  | 3.3V Control Timing                    | 11 |

| 24.10 | 5V Oscillator Characteristics          | 11 |

| 24.11 | 3.3V Oscillator Characteristics        | 12 |

| 24.12 | 5V ADC Electrical Characteristics      | 13 |

| 24.13 | 3.3V ADC Electrical Characteristics    | 14 |

| 24.14 | Timer Interface Module Characteristics | 15 |

| 24.15 | CGM Electrical Specifications          | 15 |

| 24.16 | 5V SPI Characteristics                 | 16 |

| 24.17 | 3.3V SPI Characteristics               | 17 |

| 24.18 | FLASH Memory Characteristics           | 50 |

# 24.2 Introduction

This section contains electrical and timing specifications.

MC68HC908LJ24/LK24 - Rev. 2.1

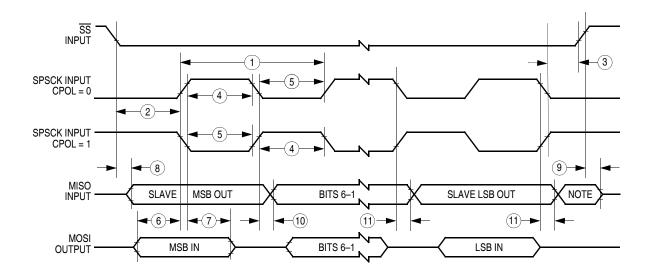

Note: Not defined but normally MSB of character just received

a) SPI Slave Timing (CPHA = 0)

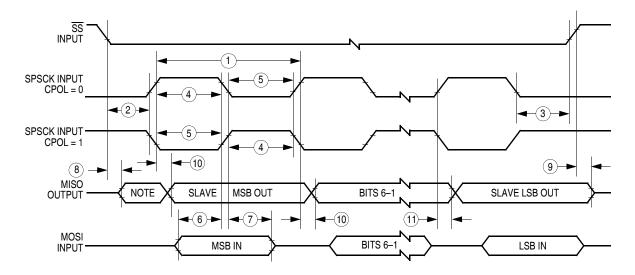

Note: Not defined but normally LSB of character previously transmitted

b) SPI Slave Timing (CPHA = 1)

#### Figure 24-3. SPI Slave Timing

# Section 26. Ordering Information

## 26.1 Contents

| 26.2 | Introduction      | 57 |

|------|-------------------|----|

| 26.3 | MC Order Numbers4 | 57 |

## 26.2 Introduction

This section contains ordering numbers for the MC68HC908LJ24.

# 26.3 MC Order Numbers

| Table | 26-1. | МС | Order | Numbers |

|-------|-------|----|-------|---------|

|-------|-------|----|-------|---------|

| MC Order Number  | Package     | Operating<br>Temperature Range |

|------------------|-------------|--------------------------------|

| MC68HC908LJ24CPB | 64-pin LQFP | −40 to +85 °C                  |

| MC68HC908LJ24CFU | 64-pin QFP  | −40 to +85 °C                  |

| MC68HC908LJ24CPK | 80-pin LQFP | −40 to +85 °C                  |

| MC68HC908LJ24CFQ | 80-pin QFP  | −40 to +85 °C                  |