Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                     |

| Core Processor             | ARM® Cortex®-M4                                                                            |

| Core Size                  | 32-Bit Single-Core                                                                         |

| Speed                      | 80MHz                                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                 |

| Number of I/O              | 51                                                                                         |

| Program Memory Size        | 1MB (1M x 8)                                                                               |

| Program Memory Type        | FLASH                                                                                      |

| EEPROM Size                | -                                                                                          |

| RAM Size                   | 128K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                      |

| Oscillator Type            | Internal                                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                              |

| Package / Case             | 64-LQFP                                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l486rgt7tr                    |

|                            |                                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

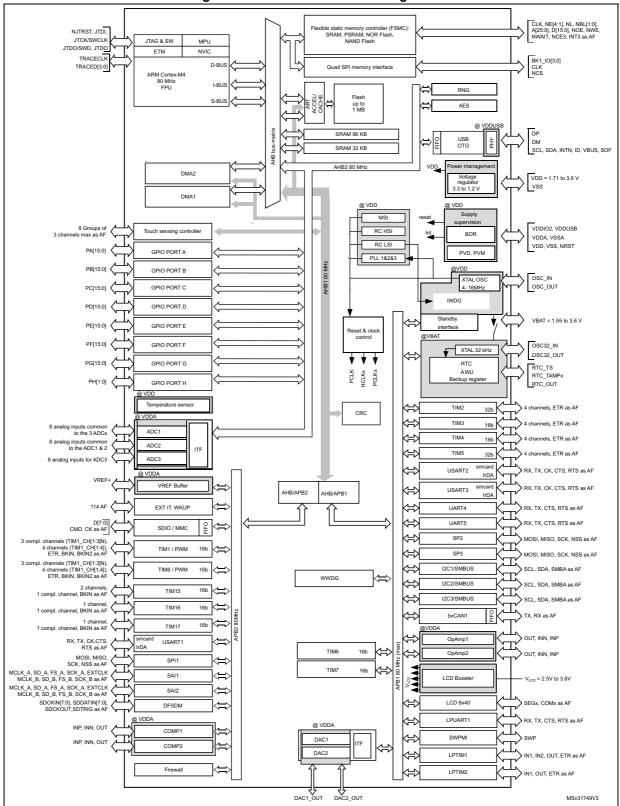

Figure 1. STM32L486xx block diagram

|                                                    |                  |                  | ionalitie            | o depen                |      |                   |     |                   |                  |                   | Shut | dower             |      |

|----------------------------------------------------|------------------|------------------|----------------------|------------------------|------|-------------------|-----|-------------------|------------------|-------------------|------|-------------------|------|

|                                                    |                  |                  |                      |                        | Stop | o 0/1             | Sto | p 2               | Star             | ndby              | Shut | down              |      |

| Peripheral                                         | Run              | Sleep            | Low-<br>power<br>run | Low-<br>power<br>sleep | -    | Wakeup capability | -   | Wakeup capability | -                | Wakeup capability | -    | Wakeup capability | VBAT |

| CPU                                                | Y                | -                | Y                    | -                      | -    | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Flash memory<br>(1 MB)                             | O <sup>(2)</sup> | O <sup>(2)</sup> | O <sup>(2)</sup>     | O <sup>(2)</sup>       | -    | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| SRAM1 (96 KB)                                      | Y                | Y <sup>(3)</sup> | Y                    | Y <sup>(3)</sup>       | Y    | -                 | Y   | -                 | -                | -                 | -    | -                 | -    |

| SRAM2 (32 KB)                                      | Y                | Y <sup>(3)</sup> | Y                    | Y <sup>(3)</sup>       | Y    | -                 | Y   | -                 | O <sup>(4)</sup> | -                 | -    | -                 | -    |

| FSMC                                               | 0                | 0                | 0                    | 0                      | -    | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Quad SPI                                           | 0                | 0                | 0                    | 0                      | -    | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Backup Registers                                   | Y                | Y                | Y                    | Y                      | Y    | -                 | Y   | -                 | Y                | -                 | Y    | -                 | Y    |

| Brown-out reset<br>(BOR)                           | Y                | Y                | Y                    | Y                      | Y    | Y                 | Y   | Y                 | Y                | Y                 | -    | -                 | -    |

| Programmable<br>Voltage Detector<br>(PVD)          | 0                | 0                | 0                    | 0                      | 0    | 0                 | 0   | 0                 | -                | -                 | -    | -                 | -    |

| Peripheral Voltage<br>Monitor (PVMx;<br>x=1,2,3,4) | 0                | 0                | 0                    | 0                      | 0    | 0                 | 0   | 0                 | -                | -                 | -    | -                 | -    |

| DMA                                                | 0                | 0                | 0                    | 0                      | -    | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| High Speed Internal<br>(HSI16)                     | 0                | 0                | 0                    | 0                      | (5)  | -                 | (5) | -                 | -                | -                 | -    | -                 | -    |

| High Speed<br>External (HSE)                       | 0                | 0                | 0                    | 0                      | -    | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Low Speed Internal<br>(LSI)                        | 0                | 0                | 0                    | 0                      | 0    | -                 | 0   | -                 | 0                | -                 | -    | -                 | -    |

| Low Speed External (LSE)                           | 0                | 0                | 0                    | 0                      | 0    | -                 | 0   | -                 | 0                | -                 | 0    | -                 | 0    |

| Multi-Speed Internal<br>(MSI)                      | 0                | 0                | 0                    | 0                      | -    | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Clock Security<br>System (CSS)                     | 0                | 0                | 0                    | 0                      | -    | -                 | -   | -                 | -                | -                 | -    | -                 | -    |

| Clock Security<br>System on LSE                    | 0                | 0                | 0                    | 0                      | 0    | 0                 | 0   | 0                 | 0                | 0                 | -    | -                 | -    |

| RTC / Auto wakeup                                  | 0                | 0                | 0                    | 0                      | 0    | 0                 | 0   | 0                 | 0                | 0                 | 0    | 0                 | 0    |

| Number of RTC<br>Tamper pins                       | 3                | 3                | 3                    | 3                      | 3    | 0                 | 3   | 0                 | 3                | 0                 | 3    | 0                 | 3    |

| LCD                                                | 0                | 0                | 0                    | 0                      | 0    | 0                 | 0   | 0                 | -                | -                 | -    | -                 | -    |

|                                                        | (1)           |

|--------------------------------------------------------|---------------|

| Table 5. Functionalities depending on the working mode | <b>)</b> ('') |

|                                  |                  |                  |                      | <u> </u>               |                  | o 0/1             | _                | op 2              | - | ndby              | - | down              |      |

|----------------------------------|------------------|------------------|----------------------|------------------------|------------------|-------------------|------------------|-------------------|---|-------------------|---|-------------------|------|

| Peripheral                       | Run              | Sleep            | Low-<br>power<br>run | Low-<br>power<br>sleep | -                | Wakeup capability | -                | Wakeup capability | - | Wakeup capability | - | Wakeup capability | VBAT |

| USB OTG FS                       | O <sup>(8)</sup> | O <sup>(8)</sup> | -                    | -                      | -                | 0                 | -                | -                 | - | -                 | - | -                 | -    |

| USARTx<br>(x=1,2,3,4,5)          | 0                | 0                | 0                    | 0                      | O <sup>(6)</sup> | O <sup>(6)</sup>  | -                | -                 | - | -                 | - | -                 | -    |

| Low-power UART<br>(LPUART)       | 0                | 0                | 0                    | 0                      | O <sup>(6)</sup> | O <sup>(6)</sup>  | O <sup>(6)</sup> | O <sup>(6)</sup>  | - | -                 | - | -                 | -    |

| I2Cx (x=1,2)                     | 0                | 0                | 0                    | 0                      | O <sup>(7)</sup> | O <sup>(7)</sup>  | -                | -                 | - | -                 | - | -                 | -    |

| I2C3                             | 0                | 0                | 0                    | 0                      | O <sup>(7)</sup> | O <sup>(7)</sup>  | O <sup>(7)</sup> | O <sup>(7)</sup>  | - | -                 | - | -                 | -    |

| SPIx (x=1,2,3)                   | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| CAN                              | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| SDMMC1                           | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| SWPMI1                           | 0                | 0                | 0                    | 0                      | -                | 0                 | -                | -                 | - | -                 | - | -                 | -    |

| SAlx (x=1,2)                     | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| DFSDM1                           | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| ADCx (x=1,2,3)                   | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| DACx (x=1,2)                     | 0                | 0                | 0                    | 0                      | 0                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| VREFBUF                          | 0                | 0                | 0                    | 0                      | 0                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| OPAMPx (x=1,2)                   | 0                | 0                | 0                    | 0                      | 0                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| COMPx (x=1,2)                    | 0                | 0                | 0                    | 0                      | 0                | 0                 | 0                | 0                 | - | -                 | - | -                 | -    |

| Temperature sensor               | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| Timers (TIMx)                    | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| Low-power timer 1<br>(LPTIM1)    | 0                | 0                | 0                    | 0                      | 0                | 0                 | 0                | 0                 | - | -                 | - | -                 | -    |

| Low-power timer 2<br>(LPTIM2)    | 0                | 0                | 0                    | 0                      | 0                | 0                 | -                | -                 | - | -                 | - | -                 | -    |

| Independent<br>watchdog (IWDG)   | 0                | 0                | 0                    | 0                      | 0                | 0                 | 0                | 0                 | 0 | 0                 | - | -                 | -    |

| Window watchdog<br>(WWDG)        | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| SysTick timer                    | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| Touch sensing controller (TSC)   | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| Random number<br>generator (RNG) | O <sup>(8)</sup> | O <sup>(8)</sup> | -                    | -                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

Table 5. Functionalities depending on the working mode<sup>(1)</sup> (continued)

interrupt is generated if enabled. LSE failure can also be detected and generated an interrupt.

- Clock-out capability:

- MCO: microcontroller clock output: it outputs one of the internal clocks for external use by the application

- LSCO: low speed clock output: it outputs LSI or LSE in all low-power modes (except VBAT).

Several prescalers allow to configure the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the APB domains is 80 MHz.

All comparators can wake up from Stop mode, generate interrupts and breaks for the timers and can be also combined into a window comparator.

## 3.19 Operational amplifier (OPAMP)

The STM32L486xx embeds two operational amplifiers with external or internal follower routing and PGA capability.

The operational amplifier features:

- Low input bias current

- Low offset voltage

- Low-power mode

- Rail-to-rail input

## **3.20** Touch sensing controller (TSC)

The touch sensing controller provides a simple solution for adding capacitive sensing functionality to any application. Capacitive sensing technology is able to detect finger presence near an electrode which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

The main features of the touch sensing controller are the following:

- Proven and robust surface charge transfer acquisition principle

- Supports up to 24 capacitive sensing channels

- Up to 3 capacitive sensing channels can be acquired in parallel offering a very good response time

- Spread spectrum feature to improve system robustness in noisy environments

- Full hardware management of the charge transfer acquisition sequence

- Programmable charge transfer frequency

- Programmable sampling capacitor I/O pin

- Programmable channel I/O pin

- Programmable max count value to avoid long acquisition when a channel is faulty

- Dedicated end of acquisition and max count error flags with interrupt capability

- One sampling capacitor for up to 3 capacitive sensing channels to reduce the system components

- Compatible with proximity, touchkey, linear and rotary touch sensor implementation

- Designed to operate with STMTouch touch sensing firmware library

- Note: The number of capacitive sensing channels is dependent on the size of the packages and subject to I/O availability.

| Timer type          | Timer        | Counter Coun<br>resolution typ |    | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>outputs |

|---------------------|--------------|--------------------------------|----|---------------------------------------|------------------------------|---------------------------------|--------------------------|

| General-<br>purpose | TIM16, TIM17 | 16-bit                         | Up | Any integer<br>between 1<br>and 65536 | Yes                          | 1                               | 1                        |

| Basic               | TIM6, TIM7   | 16-bit                         | Up | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                       |

Table 10. Timer feature comparison (continued)

## 3.25.1 Advanced-control timer (TIM1, TIM8)

The advanced-control timer can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as complete general-purpose timers. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

Many features are shared with those of the general-purpose TIMx timers (described in *Section 3.25.2*) using the same architecture, so the advanced-control timers can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

|        |     |                                       | able 17. Altern | ate function AF8 to | AF15 (for AF | U to AF7 see Table                      | 16) (continued) | 1)                                      |          |  |

|--------|-----|---------------------------------------|-----------------|---------------------|--------------|-----------------------------------------|-----------------|-----------------------------------------|----------|--|

|        |     | AF8                                   | AF9             | AF10                | AF11         | AF12                                    | AF13            | AF14                                    | AF15     |  |

| Port   |     | UART4,<br>UART5, CAN1, TSC<br>LPUART1 |                 | OTG_FS, QUADSPI LCD |              | SDMMC1, COMP1,<br>COMP2, FMC,<br>SWPMI1 | SAI1, SAI2      | TIM2, TIM15,<br>TIM16, TIM17,<br>LPTIM2 | EVENTOUT |  |

| Port H | PH0 | -                                     | -               | -                   | -            | -                                       | -               | -                                       | EVENTOUT |  |

|        | PH1 | -                                     | -               | -                   | -            | -                                       | -               | -                                       | EVENTOUT |  |

89/233

Pinouts and pin description

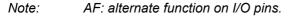

## 6.1.7 Current consumption measurement

## Figure 14. Current consumption measurement scheme

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 19: Voltage characteristics*, *Table 20: Current characteristics* and *Table 21: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                                                                            | Min                  | Мах                                                                                                                     | Unit |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------|------|

| V <sub>DDX</sub> - V <sub>SS</sub> | External main supply voltage (including $V_{DD}$ , $V_{DDA}$ , $V_{DDIO2}$ , $V_{DDUSB}$ , $V_{LCD}$ , $V_{BAT}$ ) | -0.3                 | 4.0                                                                                                                     | V    |

|                                    | Input voltage on FT_xxx pins                                                                                       | V <sub>SS</sub> -0.3 | min (V <sub>DD</sub> , V <sub>DDA</sub> , V <sub>DDIO2</sub> , V <sub>DDUSB</sub> , V <sub>LCD</sub> ) + $4.0^{(3)(4)}$ |      |

| V <sub>IN</sub> <sup>(2)</sup>     | Input voltage on TT_xx pins                                                                                        | V <sub>SS</sub> -0.3 | 4.0                                                                                                                     | V    |

|                                    | Input voltage on BOOT0 pin                                                                                         | V <sub>SS</sub>      | 9.0                                                                                                                     |      |

|                                    | Input voltage on any other pins                                                                                    | V <sub>SS</sub> -0.3 | 4.0                                                                                                                     |      |

| $ \Delta V_{DDx} $                 | Variations between different V <sub>DDX</sub> power pins of the same domain                                        | -                    | 50                                                                                                                      | mV   |

| V <sub>SSx</sub> -V <sub>SS</sub>  | Variations between all the different ground pins <sup>(5)</sup>                                                    | -                    | 50                                                                                                                      | mV   |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ,  $V_{DDIO2}$ ,  $V_{DDUSB}$ ,  $V_{LCD}$ ,  $V_{BAT}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

STM32L486xx

**Electrical characteristics**

|   | Cumph al                 | Parameter      | Coi                                         | nditions                      |                 |       |       | TYP   |        |        |       |       | MAX <sup>(1)</sup> | )      |        | Ur |

|---|--------------------------|----------------|---------------------------------------------|-------------------------------|-----------------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|--------|----|

|   | Symbol                   | Falametei      | -                                           | -                             | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C |    |

| Ī |                          |                |                                             |                               | 1.8 V           | 6.59  | 24.7  | 92.7  | 208    | 437    | 16    | 62    | 232                | 520    | 1093   |    |

|   |                          |                |                                             | LCD                           | 2.4 V           | 6.65  | 24.8  | 92.9  | 209    | 439    | 17    | 62    | 232                | 523    | 1098   |    |

|   |                          | Supply current | -                                           | disabled                      | 3 V             | 6.65  | 24.9  | 93.3  | 210    | 442    | 17    | 62    | 233                | 525    | 1105   |    |

|   | I <sub>DD</sub> (Stop 1) | in Stop 1      |                                             |                               | 3.6 V           | 6.70  | 25.1  | 93.8  | 212    | 447    | 17    | 63    | 235                | 530    | 1118   |    |

|   | IDD (Stop 1)             | mode,          |                                             | LCD                           | 1.8 V           | 7.00  | 25.2  | 97.2  | 219    | 461    | 18    | 63    | 243                | 548    | 1153   | •  |

|   |                          | RTC disabled   |                                             | enabled <sup>(2)</sup>        | 2.4 V           | 7.14  | 25.4  | 97.5  | 220    | 463    | 18    | 64    | 244                | 550    | 1158   |    |

|   |                          | -              | clocked by                                  | 3 V                           | 7.24            | 25.7  | 97.7  | 221   | 465    | 18     | 64    | 244   | 553                | 1163   |        |    |

|   |                          |                | LSI                                         | 3.6 V                         | 7.36            | 26.1  | 98.7  | 223   | 471    | 18     | 65    | 247   | 558                | 1178   |        |    |

| Ī |                          |                | RTC clocked by<br>LSI                       | LCD<br>disabled               | 1.8 V           | 6.88  | 25.0  | 93.1  | 209    | 439    | 17    | 63    | 233                | 523    | 1098   |    |

|   |                          |                |                                             |                               | 2.4 V           | 7.02  | 25.2  | 93.7  | 210    | 441    | 18    | 63    | 234                | 525    | 1103   |    |

|   |                          |                |                                             |                               | 3 V             | 7.12  | 25.4  | 94.2  | 212    | 444    | 18    | 64    | 236                | 530    | 1110   |    |

|   |                          |                |                                             |                               | 3.6 V           | 7.25  | 25.7  | 95.2  | 214    | 449    | 18    | 64    | 238                | 535    | 1123   |    |

|   |                          |                |                                             | LCD<br>enabled <sup>(2)</sup> | 1.8 V           | 7.01  | 26.1  | 99.0  | 223    | 467    | 18    | 65    | 248                | 558    | 1168   |    |

|   |                          |                |                                             |                               | 2.4 V           | 7.14  | 26.3  | 99.6  | 225    | 470    | 18    | 66    | 249                | 563    | 1175   |    |

|   |                          | Supply current |                                             |                               | 3 V             | 7.31  | 26.6  | 100.0 | 226    | 474    | 18    | 67    | 250                | 565    | 1185   |    |

|   | I <sub>DD</sub> (Stop 1  | in stop 1      |                                             |                               | 3.6 V           | 7.41  | 26.9  | 102.0 | 229    | 480    | 19    | 67    | 255                | 573    | 1200   | 1. |

|   | with RTC)                | mode,          |                                             |                               | 1.8 V           | 6.91  | 25.2  | 93.4  | 210    | 440    | 17    | 63    | 234                | 525    | 1100   | ł  |

|   |                          | RTC enabled    | RTC clocked by LSE bypassed                 | LCD                           | 2.4 V           | 7.04  | 25.3  | 94.2  | 211    | 443    | 18    | 63    | 236                | 528    | 1108   |    |

|   |                          |                | at 32768 Hz                                 | disabled                      | 3 V             | 7.19  | 25.7  | 95.0  | 212    | 446    | 18    | 64    | 238                | 530    | 1115   |    |

|   |                          |                |                                             |                               | 3.6 V           | 7.97  | 26.0  | 96.1  | 215    | 451    | 20    | 65    | 240                | 538    | 1128   |    |

|   |                          |                |                                             | 1.8 V                         | 6.85            | 25.0  | 93.0  | 208.3 | -      | 17     | 63    | 233   | 521                | -      |        |    |

|   |                          |                | RTC clocked by LSE quartz <sup>(3)</sup> in | LCD                           | 2.4 V           | 6.94  | 25.1  | 93.2  | 209.3  | -      | 17    | 63    | 233                | 523    | -      | 1  |

|   |                          |                | low drive mode                              | disabled                      | 3 V             | 7.10  | 25.2  | 93.6  | 210.3  | -      | 18    | 63    | 234                | 526    | -      | 1  |

|   |                          |                |                                             |                               | 3.6 V           | 7.34  | 25.4  | 94.1  | 212.3  | -      | 18    | 64    | 235                | 531    | -      | 1  |

115/233

| Multi-speed internal (MSI) RC oscillator |

|------------------------------------------|

|------------------------------------------|

| Symbol                     | Parameter                                           |                   | Conditions                     | Min  | Тур     | Max   | Unit        |  |  |  |

|----------------------------|-----------------------------------------------------|-------------------|--------------------------------|------|---------|-------|-------------|--|--|--|

|                            |                                                     |                   | Range 0                        | 99   | 100     | 101   |             |  |  |  |

|                            |                                                     |                   | Range 1                        | 198  | 200     | 202   |             |  |  |  |

|                            |                                                     |                   | Range 2                        | 396  | 400     | 404   | - kHz       |  |  |  |

|                            |                                                     |                   | Range 3                        | 792  | 800     | 808   |             |  |  |  |

|                            |                                                     |                   | Range 4                        | 0.99 | 1       | 1.01  |             |  |  |  |

|                            |                                                     | MSI mode          | Range 5                        | 1.98 | 2       | 2.02  |             |  |  |  |

|                            |                                                     | INISI MODE        | Range 6                        | 3.96 | 4       | 4.04  |             |  |  |  |

|                            |                                                     |                   | Range 7                        | 7.92 | 8       | 8.08  | MHz         |  |  |  |

|                            |                                                     |                   | Range 8                        | 15.8 | 16      | 16.16 |             |  |  |  |

| £                          |                                                     |                   | Range 9                        | 23.8 | 24      | 24.4  |             |  |  |  |

|                            | MSI frequency<br>after factory<br>calibration, done |                   | Range 10                       | 31.7 | 32      | 32.32 |             |  |  |  |

|                            |                                                     |                   | Range 11                       | 47.5 | 48      | 48.48 |             |  |  |  |

| f <sub>MSI</sub>           | at V <sub>DD</sub> =3 V and                         |                   | Range 0                        | -    | 98.304  | -     |             |  |  |  |

|                            | T <sub>A</sub> =30 °C                               |                   | Range 1                        | -    | 196.608 | -     | - kHz       |  |  |  |

|                            |                                                     |                   | Range 2                        | -    | 393.216 | -     |             |  |  |  |

|                            |                                                     |                   | Range 3                        | -    | 786.432 | -     |             |  |  |  |

|                            |                                                     |                   | Range 4                        | -    | 1.016   | -     |             |  |  |  |

|                            |                                                     | PLL mode<br>XTAL= | Range 5                        | -    | 1.999   | -     |             |  |  |  |

|                            |                                                     | 32.768 kHz        | Range 6                        | -    | 3.998   | -     |             |  |  |  |

|                            |                                                     |                   | Range 7                        | -    | 7.995   | -     | MHz         |  |  |  |

|                            |                                                     |                   | Range 8                        | -    | 15.991  | -     |             |  |  |  |

|                            |                                                     |                   | Range 9                        | -    | 23.986  | -     |             |  |  |  |

|                            |                                                     |                   | Range 10                       | -    | 32.014  | -     |             |  |  |  |

|                            |                                                     |                   | Range 11                       | -    | 48.005  | -     | 1           |  |  |  |

| (1.0.12)                   | MSI oscillator                                      |                   | T <sub>A</sub> = -0 to 85 °C   | -3.5 | -       | 3     | <i>c.</i> ′ |  |  |  |

| $\Delta_{TEMP}(MSI)^{(2)}$ | frequency drift over temperature                    | MSI mode          | T <sub>A</sub> = -40 to 125 °C | -8   | -       | 6     | %           |  |  |  |

## Table 49. MSI oscillator characteristics<sup>(1)</sup>

| Sym-<br>bol  | Parameter             | (                                                                                                                           | Conditions <sup>(4</sup> | )                        | Min  | Тур  | Max | Unit |

|--------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|------|------|-----|------|

|              |                       |                                                                                                                             | Single                   | Fast channel (max speed) | -    | 5    | 5.4 |      |

| ET           | Total                 |                                                                                                                             | ended                    | Slow channel (max speed) | -    | 4    | 5   |      |

|              | unadjusted<br>error   | 1                                                                                                                           | Differential             | Fast channel (max speed) | -    | 4    | 5   |      |

|              |                       |                                                                                                                             | Dillerential             | Slow channel (max speed) | -    | 3.5  | 4.5 |      |

|              |                       |                                                                                                                             | Single                   | Fast channel (max speed) | -    | 2    | 4   |      |

| EO           | Offset                |                                                                                                                             | ended                    | Slow channel (max speed) | -    | 2    | 4   |      |

| EU           | error                 |                                                                                                                             | Differential -           | Fast channel (max speed) | -    | 2    | 3.5 |      |

|              |                       |                                                                                                                             |                          | Slow channel (max speed) | -    | 2    | 3.5 |      |

|              |                       |                                                                                                                             | Single                   | Fast channel (max speed) | -    | 4    | 4.5 |      |

| EG           | Gain error            |                                                                                                                             | ended                    | Slow channel (max speed) | -    | 4    | 4.5 | LSB  |

| EG           |                       |                                                                                                                             | Differential -           | Fast channel (max speed) | -    | 3    | 4   | LOD  |

|              |                       |                                                                                                                             |                          | Slow channel (max speed) | -    | 3    | 4   |      |

|              |                       |                                                                                                                             | Single                   | Fast channel (max speed) | -    | 1    | 1.5 |      |

| Differential |                       | ended                                                                                                                       | Slow channel (max speed) | -                        | 1    | 1.5  |     |      |

|              | ED linearity<br>error | ADC clock frequency $\leq$<br>26 MHz,<br>1.65 V $\leq$ V <sub>DDA</sub> = VREF+ $\leq$<br>3.6 V,<br>Voltage scaling Range 2 | Differential             | Fast channel (max speed) | -    | 1    | 1.2 |      |

|              |                       |                                                                                                                             |                          | Slow channel (max speed) | -    | 1    | 1.2 |      |

|              |                       |                                                                                                                             | Single<br>ended          | Fast channel (max speed) | -    | 2.5  | 3   |      |

| EL           | Integral<br>linearity |                                                                                                                             |                          | Slow channel (max speed) | -    | 2.5  | 3   |      |

|              | error                 |                                                                                                                             | Differential             | Fast channel (max speed) | -    | 2    | 2.5 |      |

|              |                       |                                                                                                                             | Differentia              | Slow channel (max speed) | -    | 2    | 2.5 |      |

|              |                       |                                                                                                                             | Single                   | Fast channel (max speed) | 10.2 | 10.5 | -   |      |

| ENOB         | Effective number of   |                                                                                                                             | ended                    | Slow channel (max speed) | 10.2 | 10.5 | -   | bits |

| LINOD        | bits                  |                                                                                                                             | Differential             | Fast channel (max speed) | 10.6 | 10.7 | -   | 5113 |

|              |                       |                                                                                                                             | Billerentia              | Slow channel (max speed) | 10.6 | 10.7 | -   |      |

|              | Signal-to-            |                                                                                                                             | Single                   | Fast channel (max speed) | 63   | 65   | -   |      |

| SINAD        | noise and             |                                                                                                                             | ended                    | Slow channel (max speed) | 63   | 65   | -   |      |

|              | distortion<br>ratio   |                                                                                                                             | Differential             | Fast channel (max speed) | 65   | 66   | -   | dB   |

|              |                       |                                                                                                                             | Sincronia                | Slow channel (max speed) | 65   | 66   | -   |      |

|              |                       |                                                                                                                             | Single                   | Fast channel (max speed) | 64   | 65   | -   |      |

| SNR          | Signal-to-            |                                                                                                                             | ended                    | Slow channel (max speed) | 64   | 65   | -   | ]    |

| C. W.        | noise ratio           |                                                                                                                             | Differential             | Fast channel (max speed) | 66   | 67   | -   |      |

|              |                       |                                                                                                                             | Sincronia                | Slow channel (max speed) | 66   | 67   | -   |      |

| Table 69. ADC accuracy | - limited test | conditions $4^{(1)(2)(3)}$ |

|------------------------|----------------|----------------------------|

| Table 03. ADO acculacy | - mmeu test    | Conditions +               |

|             | Table 03. Abb accuracy - initied test conditions 4 (continued) |                         |                          |                          |     |      |     |  |  |

|-------------|----------------------------------------------------------------|-------------------------|--------------------------|--------------------------|-----|------|-----|--|--|

| Sym-<br>bol | Parameter                                                      | (                       | Min                      | Тур                      | Max | Unit |     |  |  |

|             |                                                                | ADC clock frequency ≤   | Single                   | Fast channel (max speed) | -   | -71  | -69 |  |  |

| THD         | Total 26 MHz,<br>THD harmonic $1.65 V \le V_{DDA} = VREF \le$  | ended                   | Slow channel (max speed) | -                        | -71 | -69  | dB  |  |  |

|             | 36V                                                            | Differential            | Fast channel (max speed) | -                        | -73 | -72  | uв  |  |  |

|             |                                                                | Voltage scaling Range 2 | Differential             | Slow channel (max speed) | -   | -73  | -72 |  |  |

| Table 69. ADC accuracy - limited test c | conditions 4 <sup>(1)(2)(3)</sup> (continued) |  |

|-----------------------------------------|-----------------------------------------------|--|

|-----------------------------------------|-----------------------------------------------|--|

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

| Symbol                         | Parameter             | Conditions                 | Min | Тур   | Мах | Unit |  |  |

|--------------------------------|-----------------------|----------------------------|-----|-------|-----|------|--|--|

| I <sub>DDA</sub> (VREF<br>BUF) | . VREFBUF             | I <sub>load</sub> = 0 μA   | -   | 16    | 25  |      |  |  |

|                                |                       | I <sub>load</sub> = 500 μA | -   | 18 30 | 30  | μA   |  |  |

|                                | from V <sub>DDA</sub> | I <sub>load</sub> = 4 mA   | -   | 35    | 50  |      |  |  |

Table 72. VREFBUF characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design, unless otherwise specified.

2. In degraded mode, the voltage reference buffer can not maintain accurately the output voltage which will follow (V<sub>DDA</sub> - drop voltage).

3. Guaranteed by test in production.

4. The capacitive load must include a 100 nF capacitor in order to cut-off the high frequency noise.

5. To correctly control the VREFBUF inrush current during start-up phase and scaling change, the  $V_{DDA}$  voltage should be in the range [2.4 V to 3.6 V] and [2.8 V to 3.6 V] respectively for  $V_{RS}$  = 0 and  $V_{RS}$  = 1.

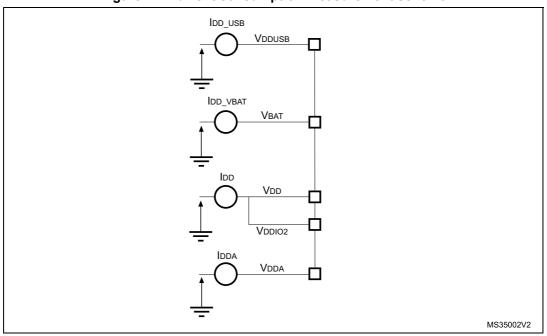

## 6.3.25 **DFSDM** characteristics

Unless otherwise specified, the parameters given in *Table 79* for DFSDM are derived from tests performed under the ambient temperature,  $f_{APB2}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22: General operating conditions*.

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x VDD

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (DFSDM1\_CKINy, DFSDM1\_DATINy, DFSDM1\_CKOUT for DFSDM).

| Symbol                                         | Parameter                                                                                                | Conditions                                                                                    | Min                                         | Тур                  | Мах                                       | Unit |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------|----------------------|-------------------------------------------|------|

| f <sub>DFSDMCLK</sub>                          | DFSDM clock                                                                                              | -                                                                                             | -                                           | -                    | f <sub>SYSCLK</sub>                       |      |

| f <sub>CKIN</sub><br>(1/T <sub>CKIN</sub> )    | Input clock<br>frequency                                                                                 | SPI mode (SITP[1:0] = 01)                                                                     | -                                           | -                    | 20<br>(f <sub>DFSDMCLK</sub> /4)          | MHz  |

| f <sub>скоит</sub>                             | Output clock<br>frequency                                                                                | -                                                                                             |                                             |                      | 20                                        | MHz  |

| DuCy <sub>CKOUT</sub>                          | Output clock<br>frequency<br>duty cycle                                                                  | -                                                                                             | 45                                          | 50                   | 55                                        | %    |

| <sup>t</sup> wh(CKIN)<br><sup>t</sup> wl(CKIN) | Input clock<br>high and low<br>time                                                                      | SPI mode (SITP[1:0] = 01),<br>External clock mode<br>(SPICKSEL[1:0] = 0)                      | T <sub>CKIN</sub> /2-0.5                    | T <sub>CKIN</sub> /2 | -                                         |      |

| t <sub>su</sub>                                | Data input<br>setup time                                                                                 | SPI mode (SITP[1:0]=01),<br>External clock mode<br>(SPICKSEL[1:0] = 0)                        | 0                                           | -                    | -                                         |      |

| t <sub>h</sub>                                 | t <sub>h</sub> Data input<br>hold time SPI mode (SITP[1:0]<br>External clock mode<br>(SPICKSEL[1:0] = 0) |                                                                                               | 2                                           | -                    | -                                         | ns   |

| T <sub>Manchester</sub>                        | Manchester<br>data period<br>(recovered<br>clock period)                                                 | Manchester mode (SITP[1:0]<br>= 10 or 11),<br>Internal clock mode<br>(SPICKSEL[1:0] $\neq$ 0) | (CKOUT<br>DIV+1) x<br>T <sub>DFSDMCLK</sub> | -                    | (2 x CKOUTDIV)<br>x T <sub>DFSDMCLK</sub> |      |

## Table 79. DFSDM characteristics<sup>(1)</sup>

1. Data based on characterization results, not tested in production.

Figure 16: DFSDM timing diagram

#### 6.3.26 **Timer characteristics**

The parameters given in the following tables are guaranteed by design.

Refer to Section 6.3.14: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

Г

Т

Т

## **SPI characteristics**

Unless otherwise specified, the parameters given in *Table 84* for SPI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 22: General operating conditions*.

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                       | Parameter                | Conditions                                                                              | Min                              | Тур               | Мах                                                        | Unit |    |  |

|----------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------|----------------------------------|-------------------|------------------------------------------------------------|------|----|--|

|                                              |                          | Master mode receiver/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1    | V <sub>DD</sub> < 3.6 V          | 24                |                                                            |      |    |  |

|                                              |                          | Master mode receiver/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1   |                                  |                   | 13<br>40<br>40                                             |      |    |  |

|                                              |                          | Master mode transmitter<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1            |                                  |                   | 40                                                         |      |    |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency      | Slave mode receiver<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                | -                                | -                 | 40 MH<br>26 <sup>(2)</sup><br>16 <sup>(2)</sup><br>13<br>8 | MHz  |    |  |

|                                              |                          | Slave mode transmitter/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  |                                  |                   |                                                            |      |    |  |

|                                              |                          | Slave mode transmitter/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 |                                  |                   | 16 <sup>(2)</sup>                                          |      |    |  |

|                                              |                          | Voltage Range 2                                                                         |                                  |                   |                                                            | 1    | 13 |  |

|                                              |                          | 1.08 < V <sub>DDIO2</sub> < 1.32 V <sup>(3)</sup>                                       |                                  |                   | 8                                                          |      |    |  |

| t <sub>su(NSS)</sub>                         | NSS setup time           | Slave mode, SPI prescaler = 2                                                           | 4 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                                                          | ns   |    |  |

| t <sub>h(NSS)</sub>                          | NSS hold time            | Slave mode, SPI prescaler = 2                                                           | 2 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                                                          | ns   |    |  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time    | Master mode                                                                             | T <sub>PCLK</sub> -2             | T <sub>PCLK</sub> | T <sub>PCLK</sub> +2                                       | ns   |    |  |

| t <sub>su(MI)</sub>                          | Data input setup time    | Master mode                                                                             | 3.5                              | -                 | -                                                          | ns   |    |  |

| t <sub>su(SI)</sub>                          |                          | Slave mode                                                                              | 3                                | -                 | -                                                          | 115  |    |  |

| t <sub>h(MI)</sub>                           | Data input hold time     | Master mode                                                                             | 6.5                              | -                 | -                                                          | ns   |    |  |

| t <sub>h(SI)</sub>                           |                          | Slave mode                                                                              | 3                                | -                 | -                                                          | 115  |    |  |

| t <sub>a(SO)</sub>                           | Data output access time  | Slave mode                                                                              | 9                                | -                 | 36                                                         | ns   |    |  |

| t <sub>dis(SO)</sub>                         | Data output disable time | Slave mode                                                                              | 9                                | -                 | 16                                                         | ns   |    |  |

| Table | 84. | SPI | characteristics <sup>(7</sup> | 1) | ) |

|-------|-----|-----|-------------------------------|----|---|

|-------|-----|-----|-------------------------------|----|---|

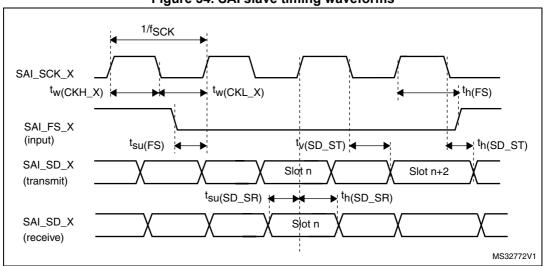

Figure 34. SAI slave timing waveforms

## **SDMMC** characteristics

Unless otherwise specified, the parameters given in *Table 88* for SDIO are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in *Table 22: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output characteristics.

| Symbol                                              | Parameter                             | Conditions               | Min | Тур | Max | Unit |  |  |

|-----------------------------------------------------|---------------------------------------|--------------------------|-----|-----|-----|------|--|--|

| f <sub>PP</sub>                                     | Clock frequency in data transfer mode | -                        | 0   | -   | 50  | MHz  |  |  |

| -                                                   | SDIO_CK/fPCLK2 frequency ratio        | -                        | -   | -   | 4/3 | -    |  |  |

| t <sub>W(CKL)</sub>                                 | Clock low time                        | f <sub>PP</sub> = 50 MHz | 8   | 10  | -   | ns   |  |  |

| t <sub>W(CKH)</sub>                                 | Clock high time                       | f <sub>PP</sub> = 50 MHz | 8   | 10  | -   | ns   |  |  |

| CMD, D input                                        | ts (referenced to CK) in MMC and SD H | S mode                   |     |     |     |      |  |  |

| t <sub>ISU</sub>                                    | Input setup time HS                   | f <sub>PP</sub> = 50 MHz | 2   | -   | -   | ns   |  |  |

| t <sub>IH</sub>                                     | Input hold time HS                    | f <sub>PP</sub> = 50 MHz | 4.5 | -   | -   | ns   |  |  |

| CMD, D outp                                         | uts (referenced to CK) in MMC and SD  | HS mode                  |     |     |     |      |  |  |

| t <sub>OV</sub>                                     | Output valid time HS                  | f <sub>PP</sub> = 50 MHz | -   | 12  | 14  | ns   |  |  |

| t <sub>OH</sub>                                     | Output hold time HS                   | f <sub>PP</sub> = 50 MHz | 9   | -   | -   | ns   |  |  |

| CMD, D inputs (referenced to CK) in SD default mode |                                       |                          |     |     |     |      |  |  |

| t <sub>ISUD</sub>                                   | Input setup time SD                   | f <sub>PP</sub> = 50 MHz | 2   | -   | -   | ns   |  |  |

| t <sub>IHD</sub>                                    | Input hold time SD                    | f <sub>PP</sub> = 50 MHz | 4.5 | -   | -   | ns   |  |  |

Table 88. SD / MMC dynamic characteristics,  $V_{DD}$ =2.7 V to 3.6 V<sup>(1)</sup>

| Table 94. Asynchronous non-multiplexed SRAM/PSRAM/NOR write-N | NAIT |

|---------------------------------------------------------------|------|

| timings <sup>(1)(2)</sup>                                     |      |

| Symbol                    | Parameter                                                        | Min                     | Мах                     | Unit |

|---------------------------|------------------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                                  | 8T <sub>HCLK</sub> +0.5 | 8T <sub>HCLK</sub> +0.5 |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                                                 | 6T <sub>HCLK</sub> -0.5 | 6T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(NWAIT_NE)</sub> | t <sub>su(NWAIT_NE)</sub> FMC_NWAIT valid before FMC_NEx high 6T |                         |                         | ns   |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid                        | 4T <sub>HCLK</sub> +2   | -                       |      |

1. CL = 30 pF.

2. Guaranteed by characterization results.

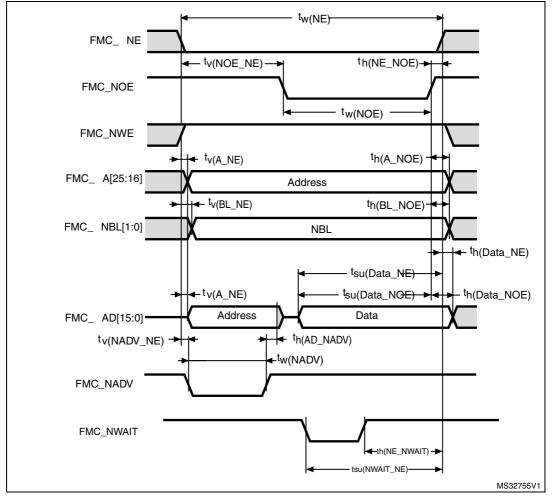

## Figure 39. Asynchronous multiplexed PSRAM/NOR read waveforms

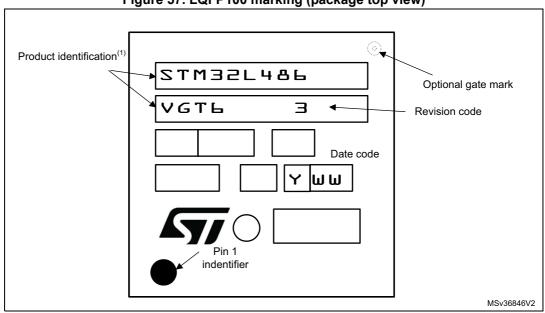

Figure 57. LQFP100 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# Table 110. WLCSP72 - 72-ball, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level chip scale

| package mechanical data (continue |

|-----------------------------------|

|-----------------------------------|

| Symbol |     | millimeters    |   |     | inches <sup>(1)</sup> |     |

|--------|-----|----------------|---|-----|-----------------------|-----|

| Symbol | Min | in Typ Max Min |   | Min | Тур                   | Max |

| G      | -   | 0.2797         | - | -   | 0.0110                | -   |

| aaa    | -   | 0.100          | - | -   | 0.0039                | -   |

| bbb    | -   | 0.100          | - | -   | 0.0039                | -   |

| CCC    | -   | 0.100          | - | -   | 0.0039                | -   |

| ddd    | -   | 0.050          | - | -   | 0.0020                | -   |

| eee    | -   | 0.050          | - | -   | 0.0020                | -   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

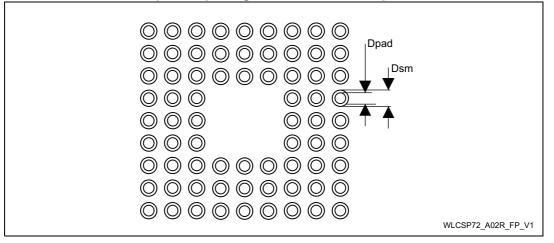

## Figure 59. WLCSP72 - 72-ball, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

#### Table 111. WLCSP72 recommended PCB design rules (0.4 mm pitch BGA)

| Dimension         | Recommended values                                                |

|-------------------|-------------------------------------------------------------------|

| Pitch             | 0.4 mm                                                            |

| Dpad              | 0.225 mm                                                          |

| Dsm               | 0.290 mm typ. (depends on the solder mask registration tolerance) |

| Stencil opening   | 0.250 mm                                                          |

| Stencil thickness | 0.100 mm                                                          |