# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 80MHz                                                                                               |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                          |

| Number of I/O              | 114                                                                                                 |

| Program Memory Size        | 1MB (1M x 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 128K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                                        |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

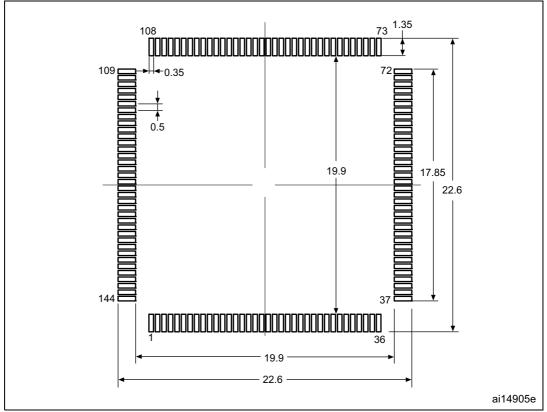

| Package / Case             | 144-LQFP                                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l486zgt6                               |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32L486xx devices are the ultra-low-power microcontrollers based on the highperformance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 80 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32L486xx devices embed high-speed memories (1 Mbyte of Flash memory, 128 Kbyte of SRAM), a flexible external memory controller (FSMC) for static memories (for devices with packages of 100 pins and more), a Quad SPI flash memories interface (available on all packages) and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

The STM32L486xx devices embed several protection mechanisms for embedded Flash memory and SRAM: readout protection, write protection, proprietary code readout protection and Firewall.

The devices offer up to three fast 12-bit ADCs (5 Msps), two comparators, two operational amplifiers, two DAC channels, an internal voltage reference buffer, a low-power RTC, two general-purpose 32-bit timer, two 16-bit PWM timers dedicated to motor control, seven general-purpose 16-bit timers, and two 16-bit low-power timers. The devices support four digital filters for external sigma delta modulators (DFSDM).

In addition, up to 24 capacitive sensing channels are available. The devices also embed an integrated LCD driver 8x40 or 4x44, with internal step-up converter.

They also feature standard and advanced communication interfaces.

- Three I2Cs

- Three SPIs

- Three USARTs, two UARTs and one Low-Power UART.

- Two SAIs (Serial Audio Interfaces)

- One SDMMC

- One CAN

- One USB OTG full-speed

- One SWPMI (Single Wire Protocol Master Interface)

The STM32L486xx devices embed AES hardware accelerator.

The STM32L486xx operates in the -40 to +85  $^{\circ}$ C (+105  $^{\circ}$ C junction), -40 to +105  $^{\circ}$ C (+125  $^{\circ}$ C junction) and -40 to +125  $^{\circ}$ C (+130  $^{\circ}$ C junction) temperature ranges from a 1.71 to 3.6 V power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

Some independent power supplies are supported: analog independent supply input for ADC, DAC, OPAMPs and comparators, 3.3 V dedicated supply input for USB and up to 14 I/Os can be supplied independently down to 1.08V. A VBAT input allows to backup the RTC and backup registers.

The STM32L486xx family offers five packages from 64-pin to 144-pin packages.

| Peripheral                               | STM32L486Zx | STM32L486Qx | STM32L486Vx   | STM32L486Jx                                  | STM32L486Rx |

|------------------------------------------|-------------|-------------|---------------|----------------------------------------------|-------------|

| GPIOs                                    | 114         | 109         | 82            | 57                                           | 51          |

| Wakeup pins                              | 5           | 5           | 5             | 4                                            | 4           |

| Nb of I/Os down to 1.08 V                | 14          | 14          | 0             | 6                                            | 0           |

| Capacitive sensing<br>Number of channels | 24          | 24          | 21            | 12                                           | 12          |

| 12-bit ADCs                              | 3           | 3           | 3             | 3                                            | 3           |

| Number of channels                       | 24          | 19          | 16            | 16                                           | 16          |

| 12-bit DAC channels                      |             |             | 2             |                                              |             |

| Internal voltage reference buffer        |             | Ŷ           | ⁄es           |                                              | No          |

| Analog comparator                        |             |             | 2             |                                              |             |

| Operational amplifiers                   |             |             | 2             |                                              |             |

| Max. CPU frequency                       |             |             | 80 MHz        |                                              |             |

| Operating voltage                        |             |             | 1.71 to 3.6 V |                                              |             |

| Operating temperature                    |             |             |               | / -40 to 105 °C / -4<br>0 to 125 °C / -40 to |             |

| Packages                                 | LQFP144     | UFBGA132    | LQFP100       | WLCSP72                                      | LQFP64      |

## Table 2. STM32L486xx family device features and peripheral counts (continued)

1. For the LQFP100 package, only FMC Bank1 is available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select.

# 3 Functional overview

# 3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU 32-bit RISC processor features exceptional codeefficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU speeds up software development by using metalanguage development tools, while avoiding saturation.

With its embedded ARM core, the STM32L486xx family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the STM32L486xx family devices.

# 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor near 100 DMIPS performance at 80MHz, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 64-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 80 MHz.

# 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

DocID025977 Rev 5

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                            | Memory address            |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------|---------------------------|--|--|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C (± 5 °C), $V_{DDA} = V_{REF+} = 3.0 V (\pm 10 mV)$  | 0x1FFF 75A8 - 0x1FFF 75A9 |  |  |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 °C (± 5 °C), $V_{DDA} = V_{REF+} = 3.0 V (\pm 10 mV)$ | 0x1FFF 75CA - 0x1FFF 75CB |  |  |

Table 8. Temperature sensor calibration values

# 3.15.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference (VREFINT) provides a stable (bandgap) voltage output for the ADC and Comparators. VREFINT is internally connected to the ADC1\_IN0 input channel. The precise voltage of VREFINT is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Calibration value name | Description                                                                                                        | Memory address            |

|------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------|

| VREFINT                | Raw data acquired at a<br>temperature of 30 °C (± 5 °C),<br>V <sub>DDA</sub> = V <sub>REF+</sub> = 3.0 V (± 10 mV) | 0x1FFF 75AA - 0x1FFF 75AB |

#### Table 9. Internal voltage reference calibration values

## 3.15.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC1\_IN18 or ADC3\_IN18. As the V<sub>BAT</sub> voltage may be higher than VDDA, and thus outside the ADC input range, the VBAT pin is internally connected to a bridge divider by 3. As a consequence, the converted digital value is one third the V<sub>BAT</sub> voltage.

# 3.16 Digital to analog converter (DAC)

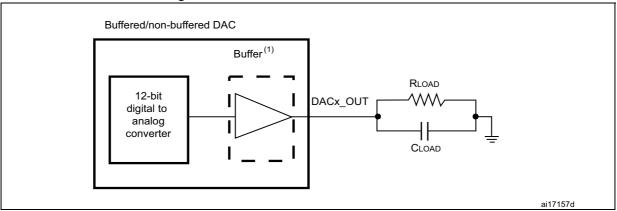

Two 12-bit buffered DAC channels can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital interface supports the following features:

- Up to two DAC output channels

- 8-bit or 12-bit output mode

- Buffer offset calibration (factory and user trimming)

- Left or right data alignment in 12-bit mode

- Synchronized update capability

|        | Pi      | n Nur   | nber     |         |                                       |          |               |       | Pin functions                                                                                                                                                               |                         |  |

|--------|---------|---------|----------|---------|---------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| LQFP64 | WLCSP72 | LQFP100 | UFBGA132 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                                         | Additional<br>functions |  |

| 55     | A6      | 89      | A8       | 133     | PB3<br>(JTDO-<br>TRACESWO)            | I/O      | FT_la         | (3)   | JTDO-TRACESWO,<br>TIM2_CH2, SPI1_SCK,<br>SPI3_SCK,<br>USART1_RTS_DE,<br>LCD_SEG7, SAI1_SCK_B,<br>EVENTOUT                                                                   | COMP2_INM               |  |

| 56     | C6      | 90      | A7       | 134     | PB4<br>(NJTRST)                       | I/O      | FT_la         | (3)   | NJTRST, TIM3_CH1,<br>SPI1_MISO, SPI3_MISO,<br>USART1_CTS,<br>UART5_RTS_DE,<br>TSC_G2_IO1,LCD_SEG8,<br>SAI1_MCLK_B,<br>TIM17_BKIN, EVENTOUT                                  | COMP2_INP               |  |

| 57     | C7      | 91      | C5       | 135     | PB5                                   | I/O      | FT_la         | -     | LPTIM1_IN1, TIM3_CH2,<br>I2C1_SMBA, SPI1_MOSI,<br>SPI3_MOSI, USART1_CK,<br>UART5_CTS,<br>TSC_G2_IO2, LCD_SEG9,<br>COMP2_OUT,<br>SAI1_SD_B, TIM16_BKIN,<br>EVENTOUT          | -                       |  |

| 58     | В7      | 92      | В5       | 136     | PB6                                   | I/O      | FT_fa         | -     | LPTIM1_ETR, TIM4_CH1,<br>TIM8_BKIN2, I2C1_SCL,<br>DFSDM1_DATIN5,<br>USART1_TX,<br>TSC_G2_IO3,<br>TIM8_BKIN2_COMP2,<br>SAI1_FS_B, TIM16_CH1N,<br>EVENTOUT                    | COMP2_INP               |  |

| 59     | A7      | 93      | B4       | 137     | PB7                                   | I/O      | FT_fla        | -     | LPTIM1_IN2, TIM4_CH2,<br>TIM8_BKIN, I2C1_SDA,<br>DFSDM1_CKIN5,<br>USART1_RX,<br>UART4_CTS,<br>TSC_G2_IO4,<br>LCD_SEG21, FMC_NL,<br>TIM8_BKIN_COMP1,<br>TIM17_CH1N, EVENTOUT | COMP2_INM,<br>PVD_IN    |  |

| 60     | D7      | 94      | A4       | 138     | BOOT0                                 | I        | -             | -     | -                                                                                                                                                                           | -                       |  |

| 61     | E7      | 95      | A3       | 139     | PB8                                   | I/O      | FT_fl         | -     | TIM4_CH3, I2C1_SCL,<br>DFSDM1_DATIN6,<br>CAN1_RX, LCD_SEG16,<br>SDMMC1_D4,<br>SAI1_MCLK_A,<br>TIM16_CH1, EVENTOUT                                                           | -                       |  |

Table 15. STM32L486xx pin definitions (continued)

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

# 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

# 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 6.1.4 Loading capacitor

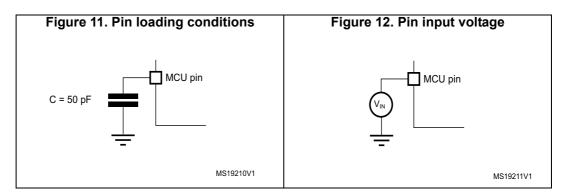

The loading conditions used for pin parameter measurement are shown in Figure 11.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 12*.

|                                             |                                                         | Table 37. Curre                                         |                 | isump |       | Stanub | y moue | (Contin            | ueu)  |       |       |        |        |    |

|---------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|-----------------|-------|-------|--------|--------|--------------------|-------|-------|-------|--------|--------|----|

| Symbol                                      | Parameter                                               | Conditions                                              |                 | ТҮР   |       |        |        | MAX <sup>(1)</sup> |       |       |       | Unit   |        |    |

| Symbol                                      | Farameter                                               | -                                                       | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C  | 105 °C | 125 °C             | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C |    |

|                                             | Supply current                                          |                                                         | 1.8 V           | 235   | 641   | 2293   | 5192   | 11213              | 588   | 1603  | 5733  | 12980  | 28033  |    |

| I <sub>DD</sub> (SRAM2)                     | to be added in                                          |                                                         | 2.4 V           | 237   | 645   | 2303   | 5213   | 11246              | 593   | 1613  | 5758  | 13033  | 28115  | nA |

| (4)                                         | Standby mode when SRAM2                                 | -                                                       | 3 V             | 236   | 647   | 2306   | 5221   | 11333              | 593   | 1618  | 5765  | 13053  | 28333  |    |

|                                             | is retained                                             |                                                         | 3.6 V           | 235   | 646   | 2308   | 5200   | 11327              | 595   | 1620  | 5770  | 13075  | 28350  |    |

| I <sub>DD</sub> (wakeup<br>from<br>Standby) | Supply current<br>during wakeup<br>from Standby<br>mode | Wakeup clock is<br>MSI = 4 MHz.<br>See <sup>(5)</sup> . | 3 V             | 1.7   | -     | -      | -      | -                  |       |       | -     |        |        | mA |

#### Table 27 Convent concurrentian in Standby mode (continued)

1. Guaranteed by characterization results, unless otherwise specified.

2. Guaranteed by test in production.

3. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

The supply current in Standby with SRAM2 mode is: I<sub>DD</sub>(Standby) + I<sub>DD</sub>(SRAM2). The supply current in Standby with RTC with SRAM2 mode is: I<sub>DD</sub>(Standby + RTC) + I<sub>DD</sub>(SRAM2).

5. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in Table 41: Low-power mode wakeup timings.

#### Table 38. Current consumption in Shutdown mode

| Symbol                     | Parameter                                         | Conditions |                 |       |       | ТҮР   |        |        |       |       | MAX <sup>(1)</sup> |        |        | Unit |

|----------------------------|---------------------------------------------------|------------|-----------------|-------|-------|-------|--------|--------|-------|-------|--------------------|--------|--------|------|

|                            |                                                   | -          | V <sub>DD</sub> | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C |      |

|                            | Supply current                                    |            | 1.8 V           | 29.8  | 194   | 1110  | 3250   | 9093   | 75    | 485   | 2775               | 8125   | 22733  |      |

|                            | in Shutdown<br>mode                               |            | 2.4 V           | 44.3  | 237   | 1310  | 3798   | 10473  | 111   | 593   | 3275               | 9495   | 26183  |      |

| I <sub>DD</sub> (Shutdown) |                                                   | -          | 3 V             | 64.1  | 293   | 1554  | 4461   | 12082  | 160   | 733   | 3885               | 11153  | 30205  | nA   |

|                            | (backup<br>registers<br>retained) RTC<br>disabled |            | 3.6 V           | 112   | 420   | 2041  | 5689   | 15186  | 280   | 1050  | 5103               | 14223  | 37965  |      |

## On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 40*. The MCU is placed under the following conditions:

- All I/O pins are in Analog mode

- The given value is calculated by measuring the difference of the current consumptions:

- when the peripheral is clocked on

- when the peripheral is clocked off

- Ambient operating temperature and supply voltage conditions summarized in *Table 19: Voltage characteristics*

- The power consumption of the digital part of the on-chip peripherals is given in *Table 40*. The power consumption of the analog part of the peripherals (where applicable) is indicated in each related section of the datasheet.

|     | Peripheral                      | Range 1 | Range 2 | Low-power run<br>and sleep | Unit   |

|-----|---------------------------------|---------|---------|----------------------------|--------|

|     | Bus Matrix <sup>(1)</sup>       | 4.5     | 3.7     | 4.1                        |        |

|     | ADC independent clock domain    | 0.4     | 0.1     | 0.2                        |        |

|     | ADC AHB clock domain            | 5.5     | 4.7     | 5.5                        |        |

|     | AES                             | 1.7     | 1.5     | 1.6                        |        |

|     | CRC                             | 0.4     | 0.2     | 0.3                        |        |

|     | DMA1                            | 1.4     | 1.3     | 1.4                        |        |

|     | DMA2                            | 1.5     | 1.3     | 1.4                        |        |

|     | FLASH                           | 6.2     | 5.2     | 5.8                        |        |

|     | FMC                             | 8.9     | 7.5     | 8.4                        |        |

|     | GPIOA <sup>(2)</sup>            | 4.8     | 3.8     | 4.4                        | 7      |

|     | GPIOB <sup>(2)</sup>            | 4.8     | 4.0     | 4.6                        |        |

| AHB | GPIOC <sup>(2)</sup>            | 4.5     | 3.8     | 4.3                        | µA/MHz |

|     | GPIOD <sup>(2)</sup>            | 4.6     | 3.9     | 4.4                        | P      |

|     | GPIOE <sup>(2)</sup>            | 5.2     | 4.5     | 4.9                        |        |

|     | GPIOF <sup>(2)</sup>            | 5.9     | 4.9     | 5.7                        |        |

|     | GPIOG <sup>(2)</sup>            | 4.3     | 3.8     | 4.2                        |        |

|     | GPIOH <sup>(2)</sup>            | 0.7     | 0.6     | 0.8                        |        |

|     | OTG_FS independent clock domain | 23.2    | NA      | NA                         |        |

|     | OTG_FS AHB clock domain         | 16.4    | NA      | NA                         |        |

|     | QUADSPI                         | 7.8     | 6.7     | 7.3                        |        |

|     | RNG independent clock domain    | 2.2     | NA      | NA                         |        |

|     | RNG AHB clock domain            | 0.6     | NA      | NA                         |        |

|     | SRAM1                           | 0.9     | 0.8     | 0.9                        |        |

#### Table 40. Peripheral current consumption

# 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 54*. They are based on the EMS levels and classes defined in application note AN1709.

| , | Symbol            | Parameter                                                                                                                         | Conditions                                                                                                    | Level/<br>Class |

|---|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|

|   | V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD} = 3.3 \text{ V}, T_A = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 80 MHz,<br>conforming to IEC 61000-4-2 | 3B              |

|   | V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD}$ = 3.3 V, $T_{A}$ = +25 °C,<br>f <sub>HCLK</sub> = 80 MHz,<br>conforming to IEC 61000-4-4             | 4A              |

Table 54. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

|             | Tun                     | ne 05. Abo accuracy - In |                           |                          |     | ,   |     |         |  |

|-------------|-------------------------|--------------------------|---------------------------|--------------------------|-----|-----|-----|---------|--|

| Sym-<br>bol | Parameter               | (                        | Conditions <sup>(4)</sup> |                          |     |     |     | Unit    |  |

|             |                         | ADC clock frequency ≤    | Single                    | Fast channel (max speed) | -   | -71 | -69 |         |  |

| THD         | Total<br>harmonic       |                          | ended                     | Slow channel (max speed) | -   | -71 | -69 | 9<br>dB |  |

|             | distortion              | 3.6 V,                   | Differential              | Fast channel (max speed) | -   | -73 | -72 | uв      |  |

|             | Voltage scaling Range 2 | Differential             | Slow channel (max speed)  | -                        | -73 | -72 |     |         |  |

| Table 69. ADC accuracy - limited test c | conditions 4 <sup>(1)(2)(3)</sup> (continued) |  |

|-----------------------------------------|-----------------------------------------------|--|

|-----------------------------------------|-----------------------------------------------|--|

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

4. Ton is the Refresh phase duration. Toff is the Hold phase duration. Refer to RM0351 reference manual for more details.

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

| Symbol    | Parameter                                                       | Conditio                                      | ons                       | Min | Тур       | Max  | Unit |

|-----------|-----------------------------------------------------------------|-----------------------------------------------|---------------------------|-----|-----------|------|------|

| DNI       | Differential non                                                | DAC output buffer ON                          |                           | -   | -         | ±2   |      |

| DNL       | linearity <sup>(2)</sup>                                        | DAC output buffer OFF                         |                           | -   | -         | ±2   |      |

| -         | monotonicity                                                    | 10 bits                                       |                           | ę   | guarantee | d    |      |

| INL       | Integral non                                                    | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ |                           | -   | -         | ±4   |      |

| INL       | linearity <sup>(3)</sup>                                        | DAC output buffer OFF<br>CL ≤ 50 pF, no RL    |                           | -   | -         | ±4   |      |

|           | Offset error at code 0x800 <sup>(3)</sup>                       | DAC output buffer ON                          | V <sub>REF+</sub> = 3.6 V | -   | -         | ±12  |      |

| Offset    |                                                                 | CL ≤ 50 pF, RL ≥ 5 kΩ                         | V <sub>REF+</sub> = 1.8 V | -   | -         | ±25  | LSB  |

|           |                                                                 | DAC output buffer OFF<br>CL ≤ 50 pF, no RL    | ·                         | -   | -         | ±8   |      |

| Offset1   | Offset error at code 0x001 <sup>(4)</sup>                       | DAC output buffer OFF<br>CL ≤ 50 pF, no RL    |                           | -   | -         | ±5   |      |

| OffsetCal | Offset Error at code 0x800                                      | DAC output buffer ON                          | V <sub>REF+</sub> = 3.6 V | _   | -         | ±5   |      |

| Unselual  | after calibration                                               | CL ≤ 50 pF, RL ≥ 5 kΩ                         | V <sub>REF+</sub> = 1.8 V | -   | -         | ±7   |      |

| Gain      | DAC output buffer ON<br>CL $\leq$ 50 pF, RL $\geq$ 5 k $\Omega$ |                                               |                           | -   | -         | ±0.5 | %    |

| Gain      | Gain error <sup>(5)</sup>                                       | DAC output buffer OFF<br>CL ≤ 50 pF, no RL    |                           | -   | -         | ±0.5 | 70   |

# Table 71. DAC accuracy<sup>(1)</sup>

| Symbol                 | Parameter                                  | Conditions                     | Min    | Мах                     | Unit                 |  |

|------------------------|--------------------------------------------|--------------------------------|--------|-------------------------|----------------------|--|

| t <sub>res(TIM)</sub>  | Timer resolution time                      | -                              | 1      | -                       | t <sub>TIMxCLK</sub> |  |

|                        |                                            | f <sub>TIMxCLK</sub> = 80 MHz  | 12.5   | -                       | ns                   |  |

| f                      | Timer external clock                       | -                              | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4                    | f <sub>TIMxCLK</sub> = 80 MHz  | 0      | 40                      | MHz                  |  |

| Res <sub>TIM</sub>     | Timer resolution                           | TIMx (except TIM2<br>and TIM5) | -      | 16                      | bit                  |  |

|                        |                                            | TIM2 and TIM5                  | -      | 32                      |                      |  |

| +                      | 16-bit counter clock                       | -                              | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |

| <sup>t</sup> COUNTER   | period                                     | f <sub>TIMxCLK</sub> = 80 MHz  | 0.0125 | 819.2                   | μs                   |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count with 32-bit counter | -                              | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |

|                        |                                            | f <sub>TIMxCLK</sub> = 80 MHz  | -      | 53.68                   | S                    |  |

Table 80. TIMx<sup>(1)</sup> characteristics

1. TIMx, is used as a general term in which x stands for 1,2,3,4,5,6,7,8,15,16 or 17.

| Table 81. IWDG min/max timeout | period at 32 kHz (LSI) <sup>(1</sup> | I) |

|--------------------------------|--------------------------------------|----|

|--------------------------------|--------------------------------------|----|

| Prescaler divider | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |

|-------------------|--------------|--------------------------------|--------------------------------|------|

| /4                | 0            | 0.125                          | 512                            |      |

| /8                | 1            | 0.250                          | 1024                           |      |

| /16               | 2            | 0.500                          | 2048                           |      |

| /32               | 3            | 1.0                            | 4096                           | ms   |

| /64               | 4            | 2.0                            | 8192                           |      |

| /128              | 5            | 4.0                            | 16384                          |      |

| /256              | 6 or 7       | 8.0                            | 32768                          |      |

The exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there

is always a full RC period of uncertainty.

| Prescaler | WDGTB | Min timeout value | Max timeout value | Unit |  |

|-----------|-------|-------------------|-------------------|------|--|

| 1         | 0     | 0.0512            | 3.2768            |      |  |

| 2         | 1     | 0.1024            | 6.5536            | ms   |  |

| 4         | 2     | 0.2048            | 13.1072           | ms   |  |

| 8         | 3     | 0.4096            | 26.2144           |      |  |

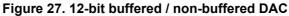

Figure 34. SAI slave timing waveforms

### **SDMMC** characteristics

Unless otherwise specified, the parameters given in *Table 88* for SDIO are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in *Table 22: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output characteristics.

| Symbol                                              | Parameter                             | Conditions               | Min | Тур | Max | Unit |  |

|-----------------------------------------------------|---------------------------------------|--------------------------|-----|-----|-----|------|--|

| f <sub>PP</sub>                                     | Clock frequency in data transfer mode | -                        | 0   | -   | 50  | MHz  |  |

| -                                                   | SDIO_CK/fPCLK2 frequency ratio        | -                        | -   | -   | 4/3 | -    |  |

| t <sub>W(CKL)</sub>                                 | Clock low time                        | f <sub>PP</sub> = 50 MHz | 8   | 10  | -   | ns   |  |

| t <sub>W(CKH)</sub>                                 | Clock high time                       | f <sub>PP</sub> = 50 MHz | 8   | 10  | -   | ns   |  |

| CMD, D input                                        | ts (referenced to CK) in MMC and SD H | S mode                   |     |     |     |      |  |

| t <sub>ISU</sub>                                    | Input setup time HS                   | f <sub>PP</sub> = 50 MHz | 2   | -   | -   | ns   |  |

| t <sub>IH</sub>                                     | Input hold time HS                    | f <sub>PP</sub> = 50 MHz | 4.5 | -   | -   | ns   |  |

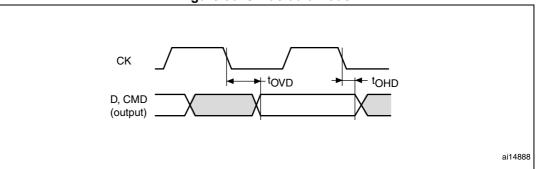

| CMD, D outp                                         | uts (referenced to CK) in MMC and SD  | HS mode                  |     |     |     |      |  |

| t <sub>OV</sub>                                     | Output valid time HS                  | f <sub>PP</sub> = 50 MHz | -   | 12  | 14  | ns   |  |

| t <sub>OH</sub>                                     | Output hold time HS                   | f <sub>PP</sub> = 50 MHz | 9   | -   | -   | ns   |  |

| CMD, D inputs (referenced to CK) in SD default mode |                                       |                          |     |     |     |      |  |

| t <sub>ISUD</sub>                                   | Input setup time SD                   | f <sub>PP</sub> = 50 MHz | 2   | -   | -   | ns   |  |

| t <sub>IHD</sub>                                    | Input hold time SD                    | f <sub>PP</sub> = 50 MHz | 4.5 | -   | -   | ns   |  |

Table 88. SD / MMC dynamic characteristics,  $V_{DD}$ =2.7 V to 3.6 V<sup>(1)</sup>

Figure 36. SD default mode

## **USB** characteristics

The STM32L486xx USB interface is fully compliant with the USB specification version 2.0 and is USB-IF certified (for Full-speed device operation).

| Symbol                          | Parameter                                      | Conditions              | Min                | Тур  | Max  | Unit |

|---------------------------------|------------------------------------------------|-------------------------|--------------------|------|------|------|

| V <sub>DDUSB</sub>              | USB transceiver operating voltage              |                         | 3.0 <sup>(1)</sup> | -    | 3.6  | V    |

| R <sub>PUI</sub>                | Embedded USB_DP pull-up value during idle      |                         | 900                | 1250 | 1600 |      |

| R <sub>PUR</sub>                | Embedded USB_DP pull-up value during reception |                         | 1400               | 2300 | 3200 | Ω    |

| Z <sub>DRV</sub> <sup>(2)</sup> | Output driver impedance <sup>(3)</sup>         | Driving high<br>and low | 28                 | 36   | 44   | Ω    |

Table 90. USB electrical characteristics

1. The STM32L486xx USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V voltage range.

2. Guaranteed by design.

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-); the matching impedance is already included in the embedded driver.

## CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

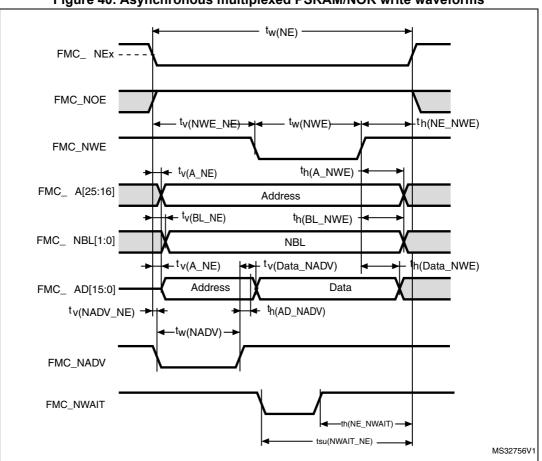

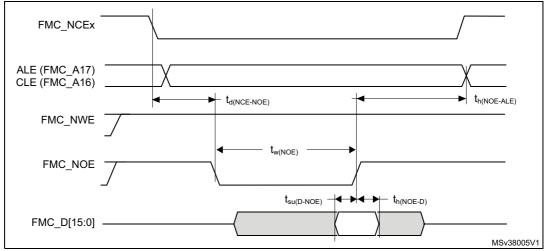

Figure 40. Asynchronous multiplexed PSRAM/NOR write waveforms

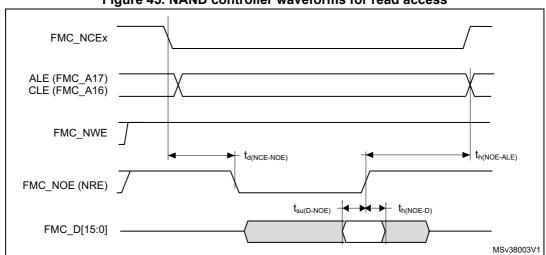

Figure 45. NAND controller waveforms for read access

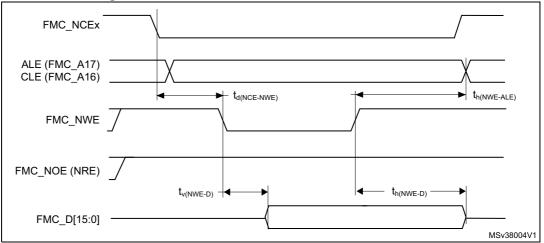

Figure 46. NAND controller waveforms for write access

Figure 47. NAND controller waveforms for common memory read access

1. Dimensions are expressed in millimeters.

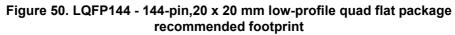

As applications do not commonly use the STM32L486xx at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 82 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V and maximum 8 I/Os used at the same time in output at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.3 V

P<sub>IOmax</sub> = 20 × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives:  $P_{INTmax}$  = 175 mW and  $P_{IOmax}$  = 272 mW:

P<sub>Dmax</sub> = 175 + 272 = 447 mW

Using the values obtained in Table 113  $T_{Jmax}$  is calculated as follows:

– For LQFP64, 45 °C/W

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ) see Section 8: Part numbering.

In this case, parts must be ordered at least with the temperature range suffix 6 (see Part numbering).

Note: With this given  $P_{Dmax}$  we can find the  $T_{Amax}$  allowed for a given device temperature range (order code suffix 6 or 7).

Suffix 6:  $T_{Amax} = T_{Jmax} - (45^{\circ}C/W \times 447 \text{ mW}) = 105\text{-}20.115 = 84.885 ^{\circ}C$ Suffix 7:  $T_{Amax} = T_{Jmax} - (45^{\circ}C/W \times 447 \text{ mW}) = 125\text{-}20.115 = 104.885 ^{\circ}C$

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 100 \degree C$  (measured according to JESD51-2),  $I_{DDmax} = 20 \text{ mA}, V_{DD} = 3.5 \text{ V}, \text{ maximum } 20 \text{ I/Os used at the same time in output at low level with } I_{OL} = 8 \text{ mA}, V_{OL} = 0.4 \text{ V}$   $P_{INTmax} = 20 \text{ mA} \times 3.5 \text{ V} = 70 \text{ mW}$   $P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$ This gives:  $P_{INTmax} = 70 \text{ mW}$  and  $P_{IOmax} = 64 \text{ mW}$ :  $P_{Dmax} = 70 + 64 = 134 \text{ mW}$

Thus: P<sub>Dmax</sub> = 134 mW

Using the values obtained in *Table 113*  $T_{Jmax}$  is calculated as follows:

- For LQFP64, 45 °C/W

- T<sub>Jmax</sub> = 100 °C + (45 °C/W × 134 mW) = 100 °C + 6.03 °C = 106.03 °C

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Part numbering*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to *Figure 64* to select the required temperature range (suffix 6 or 7) according to your ambient temperature or power requirements.

Figure 64. LQFP64 P<sub>D</sub> max vs. T<sub>A</sub>

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID025977 Rev 5