Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                            |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 36MHz                                                               |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                           |

| Peripherals                | DMA, POR, PWM, WDT                                                  |

| Number of I/O              | 112                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                    |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K × 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                         |

| Data Converters            | A/D 16x10b                                                          |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                  |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 144-LFBGA                                                           |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str730fz1h7 |

|                            |                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Scope

This datasheet provides the STR73x ordering information, mechanical and electrical device characteristics.

For complete information on the STR73xF microcontroller memory, registers and peripherals. please refer to the STR73x reference manual.

For information on programming, erasing and protection of the internal Flash memory please refer to the STR7 Flash programming reference manual.

For information on the ARM7TDMI core please refer to the ARM7TDMI technical reference manual.

## 1.1 Description

## ARM core with embedded Flash & RAM

STR73xF family combines the high performance ARM7TDMI<sup>™</sup> CPU with an extensive range of peripheral functions and enhanced I/O capabilities. All devices have on-chip high-speed single voltage Flash memory and high-speed RAM. The STR73xF family has an embedded ARM core and is therefore compatible with all ARM tools and software.

### Extensive tools support

STMicroelectronics' 32-bit, ARM core-based microcontrollers are supported by a complete range of high-end and low-cost development tools to meet the needs of application developers. This extensive line of hardware/software tools includes starter kits and complete development packages all tailored for ST's ARM core-based MCUs.

The range of development packages includes third-party solutions that come complete with a graphical development environment and an in-circuit emulator/programmer featuring a JTAG application interface. These support a range of embedded operating systems (OS), while several royalty-free OSs are also available.

For more information, please refer to ST MCU site http://www.st.com/mcu

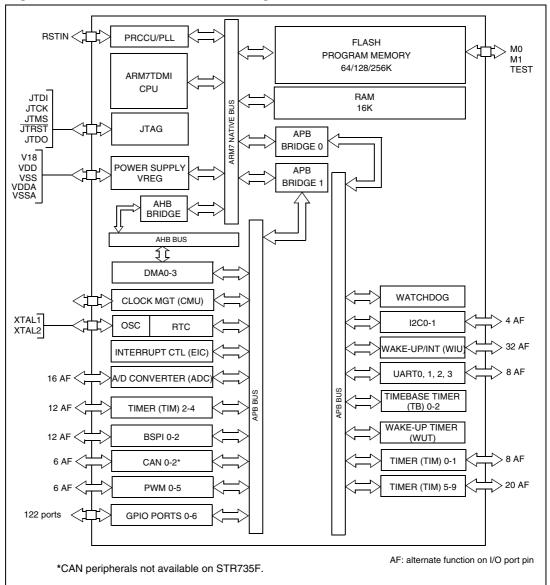

Figure 1 shows the general block diagram of the device family.

### Flexible clock control

Two clock sources are used to drive the microcontroller, a main clock driven by an external crystal or ceramic resonator and an internal backup RC oscillator that operates at 2 MHz or 32 kHz. The embedded PLL can be configured to generate an internal system clock of up to 36 MHz. The PLL output frequency can be programmed using a wide selection of multipliers and dividers.

### Voltage regulators

The STR73xF requires an external 4.5 to 5.5 V power supply. There are two internal Voltage Regulators for generating the 1.8 V power supply needed by the core and peripherals. The main VR is switched off and the Low Power VR switched on when the application puts the STR73xF in Low Power Wait for Interrupt (LPWFI) mode.

### Low voltage detectors

The voltage regulator and Flash modules each have an embedded LVD that monitors the internal 1.8 V supply. If the voltage drops below a certain threshold, the LVD will reset the STR73xF.

Note: An external power-on reset must be provided ensure the microcontroller starts-up correctly.

## 2.1 On-chip peripherals

## **CAN** interfaces

The three CAN modules are compliant with the CAN specification V2.0 part B (active). The bit rate can be programmed up to 1 MBaud. These are not available in the STR735 and STR736.

## DMA

4 DMA controllers, each with 4 data streams manage memory to memory, peripheral to peripheral, peripheral to memory and memory to peripheral transfers. The DMA requests are connected to TIM timers, BSPI0, BSPI1, BSPI2 and ADC. One of the streams can be configured to be triggered by a software request, independently from any peripheral activity.

#### 16-bit timers (TIM)

Each of the ten timers (six in 100-pin devices) have a 16-bit free-running counter with 7-bit prescaler, up to two input capture/output compare functions, a pulse counter function, and a PWM channel with selectable frequency. This provides a total of 16 independent PWMs (12 in 100-pin devices) when added with the PWM modules (see next paragraph).

#### **PWM modules (PWM)**

The six 16-bit PWM modules have independently programmable periods and duty-cycles, with 5+3 bit prescaler factor.

#### Timebase timers (TB)

The three 16-bit timebase timers with 8-bit prescaler for general purpose time triggering operations.

## Real-time clock (RTC)

The RTC provides a set of continuously running counters driven by separate clock signal derived from the main oscillator. The RTC can be used as a general timebase or

# 3 Block diagram

### Figure 1. STR730F/STR735F block diagram

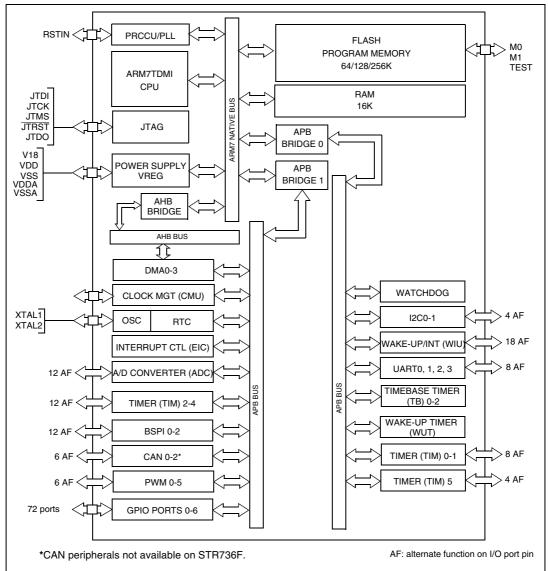

Figure 2. STR731F/STR736 block diagram

# 3.1 Related documentation

Available from www.arm.com:

ARM7TDMI technical reference manual

Available from http://www.st.com:

STR73x reference manual (RM0001)

STR7 Flash programming reference manual

STR73x software library user manual

For a list of related application notes refer to http://www.st.com.

| Table 4. | STR73xF pin | description |

|----------|-------------|-------------|

|----------|-------------|-------------|

|         | Pin n°   | )       |                 |      |                | Inp   | ut        | Ou         | tpu | t  | Main                                 |                                                                                                                                              |

|---------|----------|---------|-----------------|------|----------------|-------|-----------|------------|-----|----|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| TQFP144 | LFBGA144 | TQFP100 | Pin name        | Type | Input Level    | pd/nd | interrupt | Capability | OD  | ЪР | Main<br>function<br>(after<br>reset) | Alternate function                                                                                                                           |

| 119     | B8       | 84      | P5.9/PWM5       | I/O  | Τ <sub>Τ</sub> |       | INT7      | 2mA        | х   | х  | Port 5.9                             | PWM5: PWM output (TQFP100 only)                                                                                                              |

| 120     | C8       | 85      | P5.10/RDI2      | I/O  | Τ <sub>T</sub> |       | INT8      | 2mA        | Х   | Х  | Port 5.10                            | UART2: receive data input                                                                                                                    |

| 121     | A12      | 86      | P5.11/TDO2      | I/O  | Τ <sub>Τ</sub> |       | INT9      | 2mA        | Х   | Х  | Port 5.11                            | UART2: transmit data output                                                                                                                  |

| 122     | D8       | 87      | P5.12           | I/O  | Τ <sub>Τ</sub> |       | INT10     | 2mA        | Х   | Х  | Port 5.12                            |                                                                                                                                              |

| 123     | E8       |         | P5.13           | I/O  | Τ <sub>Τ</sub> |       | INT11     | 2mA        | Х   | Х  | Port 5.13                            |                                                                                                                                              |

| 124     | B7       |         | P5.14           | I/O  | Τ <sub>Τ</sub> |       | INT12     | 2mA        | Х   | Х  | Port 5.14                            |                                                                                                                                              |

| 125     | A7       |         | P5.15           | I/O  | Τ <sub>Τ</sub> |       | INT13     | 2mA        | Х   | Х  | Port 5.15                            |                                                                                                                                              |

| 126     | A6       | 88      | V <sub>18</sub> | S    |                |       |           |            |     |    |                                      | 1.8 V decoupling pin: a<br>decoupling capacitor<br>(recommended value: 100 nF)<br>must be connected between this<br>pin and nearest Vss pin. |

| 127     | C7       | 89      | V <sub>SS</sub> | S    |                |       |           |            |     |    |                                      | Ground                                                                                                                                       |

| 128     | D7       | 90      | V <sub>DD</sub> | S    |                |       |           |            |     |    |                                      | Supply voltage (5 V)                                                                                                                         |

| 129     | E7       | 91      | P6.0            | I/O  | Τ <sub>Τ</sub> |       | WUP0      | 8mA        | Х   | Х  | Port 6.0                             |                                                                                                                                              |

| 130     | F7       |         | P6.1            | I/O  | Τ <sub>Τ</sub> |       | WUP1      | 2mA        | Х   | Х  | Port 6.1                             |                                                                                                                                              |

| 131     | B6       | 92      | P6.2/RDI3       | I/O  | Τ <sub>T</sub> |       | WUP2      | 2mA        | Х   | х  | Port 6.2                             | UART3: receive data input                                                                                                                    |

| 132     | C6       |         | P6.3            | I/O  | Τ <sub>Τ</sub> |       | WUP3      | 2mA        | Х   | Х  | Port 6.3                             |                                                                                                                                              |

| 133     | D6       | 93      | P6.4/TDO3       | I/O  | Τ <sub>Τ</sub> |       | WUP4      | 2mA        | Х   | Х  | Port 6.4                             | UART3: transmit data output                                                                                                                  |

| 134     | E6       |         | P6.5            | I/O  | Τ <sub>T</sub> |       | WUP5      | 2mA        | Х   | х  | Port 6.5                             |                                                                                                                                              |

| 135     | A5       | 94      | P6.6            | I/O  | Τ <sub>Τ</sub> |       | WUP6      | 2mA        | Х   | Х  | Port 6.6                             |                                                                                                                                              |

| 136     | B5       |         | P6.7            | I/O  | Τ <sub>Τ</sub> |       | WUP7      | 2mA        | Х   | Х  | Port 6.7                             |                                                                                                                                              |

| 137     | C5       | 95      | P6.8/RDI0       | I/O  | Τ <sub>T</sub> |       | WUP10     | 2mA        | Х   | х  | Port 6.8                             | UART0: receive data input                                                                                                                    |

| 138     | A3       | 96      | P6.9/TDO0       | I/O  | Τ <sub>T</sub> |       |           | 2mA        | Х   | Х  | Port 6.9                             | UART0: transmit data output                                                                                                                  |

| 139     | A2       |         | P6.10           | I/O  | Τ <sub>Τ</sub> |       | WUP8      | 2mA        | Х   | х  | Port 6.10                            |                                                                                                                                              |

| 140     | D5       | 97      | P6.11/MISO0     | I/O  | Τ <sub>Τ</sub> |       |           | 2mA        | х   | х  | Port 6.11                            | BSPI0: master input/slave<br>output                                                                                                          |

| 141     | A4       | 98      | P6.12/MOSI0     | I/O  | Τ <sub>Τ</sub> |       |           | 2mA        | х   | х  | Port 6.12                            | BSPI0: master output/slave input                                                                                                             |

| 142     | B4       | 99      | P6.13/SCK0      | I/O  | Τ <sub>Τ</sub> |       | WUP11     | 2mA        | Х   | х  | Port 6.13                            | BSPI0: serial clock                                                                                                                          |

| 143     | C4       | 100     | P6.14/SS0       | I/O  | Τ <sub>Τ</sub> |       |           | 2mA        | Х   | х  | Port 6.14                            | BSPI0: slave select                                                                                                                          |

| 144     | B3       |         | P6.15           | I/O  | Τ <sub>Τ</sub> |       | WUP9      | 2mA        | Х   | х  | Port 6.15                            |                                                                                                                                              |

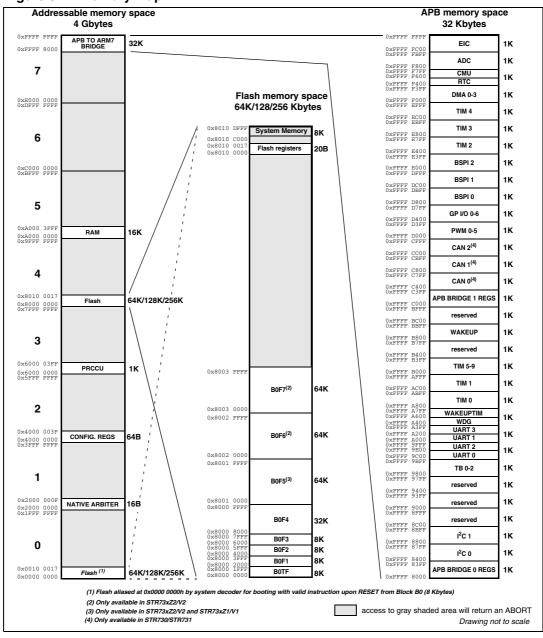

## 3.3 Memory mapping

*Figure 5* shows the various memory configurations of the STR73xF system. The system memory map (from 0x0000\_0000 to 0xFFFF\_FFFF) is shown on the left part of the figure, the right part shows maps of the Flash and APB areas. For flexibility the Flash or RAM addresses can be aliased to Block 0 addresses using the remapping feature

Most reserved memory spaces (gray shaded areas in *Figure 5*) are protected from access by the user code. When an access this memory space is attempted, an ABORT signal is generated. Depending on the type of access, the ARM processor will enter "prefetch abort" state (Exception vector 0x0000\_000C) or "data abort" state (Exception vector 0x0000\_000C) or "data abort" state (Exception vector 0x0000\_000C). It is up to the application software to manage these abort exceptions.

Figure 5. Memory map

| Symbol           | Ratings                                                                            | atings Value                          |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|--|

| T <sub>STG</sub> | Storage temperature range                                                          | Storage temperature range -55 to +150 |  |  |  |  |  |

| TJ               | Maximum junction temperature (see Section 5.2: Thermal characteristics on page 48) |                                       |  |  |  |  |  |

Table 7.

Thermal characteristics

57

57

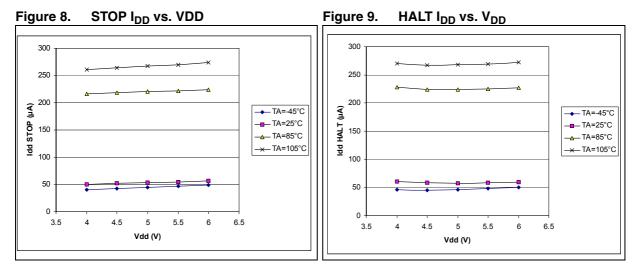

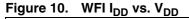

# Typical application current consumption

| Table 11. | Typical consumption in Run mode at 25°C and 85°C |

|-----------|--------------------------------------------------|

|-----------|--------------------------------------------------|

| Conditions                                                                  | 6                          | f <sub>MCLK</sub> (MHz) | f <sub>ADC</sub> (MHz) | Typical I <sub>DD</sub> (mA) |

|-----------------------------------------------------------------------------|----------------------------|-------------------------|------------------------|------------------------------|

|                                                                             |                            | 10                      | 10                     | 20                           |

|                                                                             | Code executing in RAM      | 20                      | 10                     | 29                           |

| V <sub>DD</sub> = 5.5 V, RC oscillator off,<br>PLL on, RTC enabled, 1 Timer |                            | 36                      | 9                      | 42                           |

| (TIM) running, and ADC running in scan mode.                                | Code executing in<br>Flash | 10                      | 10                     | 22                           |

|                                                                             |                            | 20                      | 10                     | 32                           |

|                                                                             |                            | 36                      | 9                      | 48                           |

## Table 12. Typical consumption in Run and low power modes at 25°C

| Mode  | Conditions                                                                                      | f <sub>MCLK</sub> | Typical I <sub>DD</sub> |

|-------|-------------------------------------------------------------------------------------------------|-------------------|-------------------------|

| RUN   | All paripharals on RAM execution                                                                | 36 MHz            | 76 mA                   |

| NUN   | All peripherals on, RAM execution                                                               | 24 MHz            | 56 mA                   |

| WFI   | Main voltage regulator on, Flash on, EIC on, WIU on,                                            | 36 MHz            | 33 mA                   |

| VVEI  | GPIOs on.                                                                                       | 24 MHz            | 31 mA                   |

|       | PLL off, main voltage regulator on                                                              | 4 MHz             | 11 mA                   |

|       | CLOCK2/16, main voltage regulator on                                                            | 250 kHz           | 8 mA                    |

| SLOW  | CLOCK2/16, main voltage regulator off                                                           | 250 kHz           | 3 mA                    |

|       | RC oscillator running in low frequency, main crystal oscillator off, main voltage regulator off | 29 kHz            | 2.5 mA                  |

| LPWFI | CLOCK2/16, main voltage regulator off, LP voltage regulator = 2 mA, Flash in power down mode.   | 250 kHz           | 528 µA                  |

|       | Main voltage regulator off, RTC on, RC oscillator off,<br>LP voltage regulator = 6 mA           | -                 | 378 µA                  |

| STOP  | Main voltage regulator off, RTC off, RC oscillator off,<br>LP voltage regulator = 6 mA          | -                 | 83 µA                   |

| 3105  | Main voltage regulator off, RTC off, RC oscillator off,<br>LP voltage regulator = 4 mA          | -                 | 64 µA                   |

|       | Main voltage regulator off, RTC off, RC oscillator off,<br>LP voltage regulator = 2 mA          | -                 | 44 µA                   |

| HALT  | RTC off, LP voltage regulator = 2 mA                                                            | -                 | 44 µA                   |

27/52

## **On-chip peripherals**

| Symbol                | Parameter                                        | Conditions                | Тур  | Unit |

|-----------------------|--------------------------------------------------|---------------------------|------|------|

|                       | RC (backup oscillator) supply current            | High frequency            | 120  | μA   |

| I <sub>DD(RC)</sub>   | no (backup oscillator) supply current            | Low frequency             | 60   | μA   |

| I <sub>DD(TIM)</sub>  | TIM timer supply current 1)                      |                           | 350  | μA   |

| I <sub>DD(BSPI)</sub> | BSPI supply current <sup>1)</sup>                |                           | 1.1  | mA   |

| I <sub>DD(UART)</sub> | UART supply current <sup>1)</sup>                |                           | 850  | μA   |

| I <sub>DD(I2C)</sub>  | I2C supply current <sup>1)</sup>                 |                           | 430  | μA   |

| I <sub>DD(ADC)</sub>  | ADC supply current when converting <sup>2)</sup> |                           | 5    | mA   |

| I <sub>DD(EIC)</sub>  | EIC supply current                               |                           | 2.88 | mA   |

| I <sub>DD(CAN)</sub>  | CAN supply current <sup>1)</sup>                 |                           | 2.95 | mA   |

| I <sub>DD(GPIO)</sub> | GPIO supply current                              | f <sub>MCLK</sub> =36 MHz | 150  | μA   |

| I <sub>DD(TB)</sub>   | TB supply current                                | MCLK-00 MI 12             | 250  | μA   |

| I <sub>DD(PWM)</sub>  | PWM supply current                               |                           | 240  | μA   |

| I <sub>DD(RTC)</sub>  | RTC supply current                               |                           | 370  | μA   |

| I <sub>DD(DMA)</sub>  | DMA supply current                               |                           | 2.5  | mA   |

| I <sub>DD(ARB)</sub>  | Native arbiter supply current                    |                           | 180  | μA   |

| I <sub>DD(AHB)</sub>  | AHB arbiter supply current                       |                           | 570  | μA   |

| I <sub>DD(WUT)</sub>  | WUT supply current                               |                           | 300  | μA   |

| I <sub>DD(WIU)</sub>  | WIU supply current                               |                           | 460  | μA   |

Table 13. Peripheral current consumption at T<sub>A</sub>= 25°C

Data based on a differential I<sub>DD</sub> measurement between the on-chip peripheral when kept under reset, not clocked and the on-chip peripheral when clocked and not kept under reset. This measurement does not include the pad toggling consumption.

2. Data based on a differential  $I_{\text{DD}}$  measurement between reset configuration and continuous A/D conversions.

## Main oscillator characteristics

$V_{DD}$  = 5 V  $\pm$  10%,  $T_A$  = -40° C to  $T_{Amax}\text{,}$  unless otherwise specified.

| Symbol                          | Devemeter                      | Conditions                                                                                               |     | Unit |     |      |  |

|---------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------|-----|------|-----|------|--|

| Symbol                          | Parameter                      | Conditions                                                                                               | Min | Тур  | Max | Jint |  |

| f <sub>OSC</sub>                | Oscillator frequency           |                                                                                                          | 4   |      | 8   | MHz  |  |

| 9 <sub>m</sub>                  | Oscillator<br>transconductance |                                                                                                          | 1.5 |      | 4.2 | mA/V |  |

| V <sub>OSC</sub> <sup>1)</sup>  | Oscillation amplitude          | $f_{OSC} = 4 \text{ MHz}, T_A = 25^{\circ} \text{ C}$                                                    | -   | 2.4  | -   | v    |  |

| VOSC /                          | Oscillation amplitude          | $f_{OSC}$ = 8 MHz, $T_A$ = 25° C                                                                         |     | 1    |     | v    |  |

| V <sub>AV</sub> <sup>1)</sup>   | Oscillator operating point     | Sine wave middle, $T_A = 25^{\circ} C$                                                                   | -   | 0.77 | -   | v    |  |

|                                 | Oscillator start-up time       | External crystal, $V_{DD}$ = 5.5 V,<br>f <sub>OSC</sub> = 4 MHz, T <sub>A</sub> =-40 <sup>o</sup> C      | -   | -    | 12  | ms   |  |

|                                 |                                | External crystal, $V_{DD}$ = 5.0 V,<br>f <sub>OSC</sub> = 4 MHz, T <sub>A</sub> =25 <sup>o</sup> C       | -   | 5.5  | -   | ms   |  |

| + 1)                            |                                | External crystal, $V_{DD}$ = 5.5 V,<br>f <sub>OSC</sub> = 6 MHz, T <sub>A</sub> =-40 <sup>o</sup> C      | -   | -    | 8   | ms   |  |

| t <sub>STUP</sub> <sup>1)</sup> |                                | External crystal, $V_{DD}$ = 5.0 V,<br>f <sub>OSC</sub> = 6 MHz, T <sub>A</sub> =25° C                   | -   | 3.3  | -   | ms   |  |

|                                 |                                | External crystal, $V_{DD}$ = 5.5 V,<br>f <sub>OSC</sub> = 8 MHz, T <sub>A</sub> =-40 <sup>o</sup> C      | -   | -    | 7   | ms   |  |

|                                 |                                | External crystal, $V_{DD} = 5.0 \text{ V}$ ,<br>$f_{OSC} = 8 \text{ MHz}$ , $T_A = 25^{\circ} \text{ C}$ | -   | 2.7  | -   | ms   |  |

### Table 14. Main oscillator characteristics

| 0h.sl                        | Parameter         | Conditions                             |                                         |     | Value |      |   |  |

|------------------------------|-------------------|----------------------------------------|-----------------------------------------|-----|-------|------|---|--|

| Symbol                       |                   | Co                                     | Min                                     | Тур | Max   | Unit |   |  |

|                              |                   |                                        | $C_1^{(3)} = C_2^{(4)} = 10 \text{ pF}$ | 150 | 555   | -    |   |  |

|                              |                   | f <sub>OSC</sub> = 4 MHz               | $C_1 = C_2 = 20 \text{ pF}$             | 490 | 1035  | -    |   |  |

|                              |                   | Cp <sup>2)</sup> = 10 pF               | $C_1 = C_2 = 30 \text{ pF}$             | 490 | 1030  | -    |   |  |

|                              |                   |                                        | $C_1 = C_2 = 40 \text{ pF}$             | 380 | 850   | -    |   |  |

|                              |                   |                                        | $C_1 = C_2 = 10 \text{ pF}$             | 160 | 470   | -    |   |  |

|                              |                   | f <sub>OSC</sub> = 5 MHz               | $C_1 = C_2 = 20 \text{ pF}$             | 415 | 800   | -    |   |  |

|                              |                   | Cp = 10 pF                             | $C_1 = C_2 = 30 \text{ pF}$             | 340 | 735   | -    | Ω |  |

|                              |                   |                                        | $C_1 = C_2 = 40 \text{ pF}$             | 260 | 580   | -    |   |  |

|                              |                   | f <sub>OSC</sub> = 6 MHz<br>Cp = 10 pF | $C_1 = C_2 = 10 \text{ pF}$             | 160 | 415   | -    |   |  |

| R <sub>F</sub> <sup>1)</sup> | Feedback resistor |                                        | $C_1 = C_2 = 20 \text{ pF}$             | 325 | 640   | -    |   |  |

| ''F                          | recuback resistor |                                        | $C_1 = C_2 = 30 \text{ pF}$             | 250 | 550   | -    |   |  |

|                              |                   |                                        | $C_1 = C_2 = 40 \text{ pF}$             | 180 | 420   | -    |   |  |

|                              |                   |                                        | $C_1 = C_2 = 10 \text{ pF}$             | 160 | 375   | -    |   |  |

|                              |                   | f <sub>OSC</sub> = 7 MHz               | $C_1 = C_2 = 20 \text{ pF}$             | 260 | 525   | -    |   |  |

|                              |                   | Cp = 10 pF                             | $C_1 = C_2 = 30 \text{ pF}$             | 185 | 420   | -    |   |  |

|                              |                   |                                        | $C_1 = C_2 = 40 \text{ pF}$             | 135 | 315   | -    |   |  |

|                              |                   |                                        | $C_1 = C_2 = 10 \text{ pF}$             | 155 | 340   | -    |   |  |

|                              |                   | f <sub>OSC</sub> = 8 MHz               | $C_1 = C_2 = 20 \text{ pF}$             | 210 | 435   | -    |   |  |

|                              |                   | Cp = 10 pF                             | $C_1 = C_2 = 30 \text{ pF}$             | 145 | 335   | -    |   |  |

|                              |                   |                                        | $C_1 = C_2 = 40 \text{ pF}$             | 100 | 245   | -    |   |  |

Table 14. Main oscillator characteristics (continued)

1. Min and max values are guaranteed by characterization, not tested in production.

- C<sub>P</sub> represents the total capacitance between XTAL1 and XTAL2, including the shunt capacitance of the external quartz crystal as well as the total board parasitic cross-capacitance between XTAL1 track and XTAL2 track.

- C<sub>1</sub> represents the total capacitance between XTAL1 and ground, including the external capacitance tied to XTAL1 pin (C<sub>L</sub>) as well as the total parasitic capacitance between XTAL1 track and ground (this includes application board track capacitance to ground and device pin capacitance).

- C<sub>2</sub> represents the total capacitance between XTAL2 and ground, including the external capacitance tied to XTAL1 pin (C<sub>L</sub>) as well as the total parasitic capacitance between XTAL2 track and ground (this includes application board track capacitance to ground and device pin capacitance).

## **PLL electrical characteristics**

$V_{DD}$  = 5 V  $\pm$  10%,  $T_{A}$  = -40° C to  $T_{Amax}$ , unless otherwise specified

| Symbol                            | Parameter                  | Conditions                                                                                                               | Value                                                      |                          |            | Unit |

|-----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------|------------|------|

| Symbol                            | Falameter                  | Conditions                                                                                                               | Min                                                        | Тур                      | Max        | Onit |

| f <sub>PLLIN</sub> <sup>(1)</sup> | PLL reference clock        | FREF_RANGE = '0'<br>FREF_RANGE = '1'                                                                                     | 1.5<br>3.0                                                 |                          | 3.0<br>5.0 | MHz  |

| f <sub>PLLOUT</sub>               | PLL output clock           | MX = "00"<br>MX = "01"<br>MX = "10"<br>MX = "11"                                                                         | 01" 12 x f <sub>PLLIN</sub><br>10" 28 x f <sub>PLLIN</sub> |                          | N<br>N     | MHz  |

| f <sub>MCLK</sub>                 | System clock               | DX = 17                                                                                                                  | f <sub>PLLOU</sub>                                         | <sub>JT</sub> /DX        | 36         | MHz  |

| f <sub>FREE</sub> <sup>(2)</sup>  | PLL free running frequency | FREF_RANGE = '0', MX0 = '1'<br>FREF_RANGE = '0', MX0 = '0'<br>FREF_RANGE = '1', MX0 = '1'<br>FREF_RANGE = '1', MX0 = '0' |                                                            | 120<br>240<br>240<br>480 |            | kHz  |

| t <sub>LOCK</sub> <sup>(3)</sup>  | PLL lock time              | Stable oscillator<br>(f <sub>PLLIN</sub> = 4 MHz), stable V <sub>DD</sub>                                                |                                                            | 100                      | 300        | μs   |

| ∆t <sub>PKJIT</sub>               | PLL jitter (pk to pk)      | f <sub>PLLIN</sub> = 4 MHz (pulse<br>generator)                                                                          |                                                            |                          | 1.5        | ns   |

Table 16. PLL characteristics

1.  $f_{\mbox{PLLIN}}$  is obtained from  $f_{\mbox{OSC}}$  directly or through an optional divider by 2.

2. Typical data are based on  $T_A=25^{\circ}C$ ,  $V_{DD}=5V$

3. Max value is guaranteed by characterization, not tested in production.

| Table 17. | Low-power | mode | wake-up | timing |

|-----------|-----------|------|---------|--------|

|           |           |      |         |        |

| Symbol                             | Parameter               | Conditions                                                                                                                                     | Тур | Unit |

|------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|

| t <sub>WUHALT</sub>                | Wake-up from HALT mode  |                                                                                                                                                | 200 | μs   |

| twustop                            | Wake up from STOP mode  | RC high frequency in STOP mode                                                                                                                 | 180 | μs   |

|                                    | Wake-up from STOP mode  | RC low frequency in STOP mode                                                                                                                  | 234 | μs   |

| <sup>t</sup> wulpwfi <sup>1)</sup> |                         | Main voltage regulator on<br>RC oscillator off<br>f <sub>OSC</sub> = 4 MHz, f <sub>MCLK</sub> = f <sub>OSC</sub> /16<br>RAM or FLASH execution | 27  | μs   |

|                                    | Wake-up from LPWFI mode | Main voltage regulator on<br>RC oscillator = high frequency<br>Flash execution                                                                 | 46  | μs   |

|                                    |                         | Main voltage regulator on<br>RC oscillator = low frequency<br>Flash execution                                                                  | 3.6 | ms   |

1. Flash memory programmed to enter Power Down mode during LPWFI.

## **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

Table 20. EMI data

| Symbol              | Parameter  | Conditions                                                       | Monitored<br>frequency band | Max vs.<br>[f <sub>OSC4M</sub> /f <sub>MCLK</sub> ] |         | Unit |

|---------------------|------------|------------------------------------------------------------------|-----------------------------|-----------------------------------------------------|---------|------|

|                     |            |                                                                  |                             | 6/36 MHz                                            | 8/8 MHz |      |

| S <sub>EMI</sub> Pe | Peak level | V <sub>DD</sub> =5.0V,<br>T <sub>A</sub> =+25°C,<br>All packages | 0.1 MHz to 30 MHz           | 23                                                  | 30      |      |

|                     |            |                                                                  | 30 MHz to 130 MHz           | 37                                                  | 34      | dBµV |

|                     |            |                                                                  | 130 MHz to 1 GHz            | 20                                                  | 7       |      |

|                     |            |                                                                  | SAE EMI Level               | 4                                                   | 3.5     | -    |

## Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

## **Electrostatic discharge (ESD)**

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: human body model and machine model. This test conforms to the JESD22-A114A/A115A standard.

| Table 21. | ESD Absolute Maximum ratings |

|-----------|------------------------------|

|-----------|------------------------------|

| Symbol                | Ratings                                                                   | Conditions | Maximum<br>value <sup>1)</sup>          | Unit |

|-----------------------|---------------------------------------------------------------------------|------------|-----------------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)                        |            | 2000                                    |      |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage<br>(machine model) T <sub>A</sub> =+25° C |            | 200                                     | v    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model)                     |            | 750 on corner<br>pins, 500 on<br>others |      |

#### Notes:

1. Data based on characterization results, not tested in production.

## Static and dynamic latch-up

• LU: 3 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each

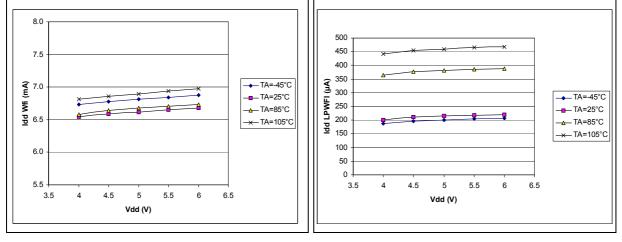

# 5 Package characteristics

# 5.1 Package mechanical data

## Figure 24. 100-pin thin quad flat package

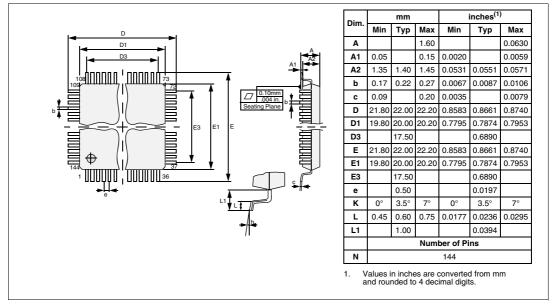

## Figure 25. 144-pin thin quad flat package

## 5.2 Thermal characteristics

The average chip-junction temperature,  $T_J$ , in degrees Celsius, may be calculated using the following equation:

(1)

(2)

$$T_{J} = T_{A} + (P_{D} \times \Theta_{JA})$$

Where:

- T<sub>A</sub> is the ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- $P_D$  is the sum of  $P_{INT}$  and  $P_{I/O} (P_D = P_{INT} + P_{I/O})$ ,

- P<sub>INT</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the chip internal power,

- P<sub>I/O</sub> represents the power dissipation on input and output pins; user determined.

Most of the time for the applications  $P_{I/O} < P_{INT}$  and may be neglected. On the other hand,  $P_{I/O}$  may be significant if the device is configured to drive continuously external modules and/or memories.

An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is given by:

$$P_{D} = K / (T_{J} + 273^{\circ}C)$$

Therefore (solving equations 1 and 2):

$$K = P_{D} x (T_{A} + 273^{\circ}C) + \Theta_{JA} x P_{D}^{2}$$

(3)

Where:

K is a constant for the particular part, which may be determined from equation (3) by measuring P<sub>D</sub> (at equilibrium) for a known T<sub>A</sub>. Using this value of K, the values of P<sub>D</sub> and T<sub>J</sub> may be obtained by solving equations (1) and (2) iteratively for any value of T<sub>A</sub>

| Table 28. | Thermal characteristi | ics |

|-----------|-----------------------|-----|

|           |                       | 03  |

| Symbol        | Description                         | Package  | Value (typical) | Unit |

|---------------|-------------------------------------|----------|-----------------|------|

|               |                                     | LFBGA144 | 50              |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient | TQFP144  | 40              | °C/W |

|               |                                     | TQFP100  | 40              |      |

# 7 Known limitations

## 7.1 Low power wait for interrupt mode

When the STR73x device is put in Low Power Wait For Interrupt mode (LPWFI), the Flash goes into low power mode or power down mode, depending on the setting of the PWD bit in the Flash Control Register 0 (default is '0', Low Power mode). This default mode can create excessive voltage conditions on the transistor gates and may affect the long term behavior of the Low Power mode circuitry.

## Workaround

There is no workaround. If Low Power Wait For Interrupt mode is used, it is strongly suggested to configure the Flash to enter power down mode (bit PWD = '1').

# 7.2 PLL free running mode at high temperature

When the STR73x device is operated and an ambient temperature ( $T_A$ ) of more than 55° C and the main system clock ( $f_{MCLK}$ ) is sourced by the PLL in free running mode, the device may not work properly.

### Workaround

At high temperature (more than  $55^{\circ}$  C), it is recommended to use the internal RC oscillator as a backup clock source rather than the PLL free running mode.

# 8 Revision history

| Table 30. | Document revision history |

|-----------|---------------------------|

|-----------|---------------------------|

| Date        | Revision | Description of changes                                                                                                                                                                                          |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19-Sep-2005 | 1        | First release                                                                                                                                                                                                   |

| 02-Nov-2005 | 2        | Removed Table 8 power consumption in LP modes<br>Updated PLL frequency in <i>Section 1.1</i> and <i>Table 12</i>                                                                                                |

| 08-Mar-2006 | 3        | Section 3.4: Preliminary power consumption data updated<br>Section 3.5: DC electrical characteristics updated<br>Section 7: Known limitations added                                                             |

| 04-Jun-2006 | 4        | Section 4: Electrical parameters updated<br>Section 7: Known limitations updated<br>Added temperature range -40°C to 85°C in Section 6: Order<br>codes                                                          |

| 19-Jun-2006 | 5        | Changed Flash data retention to 20 years at 85°C in <i>Table 18 on page 34</i> .                                                                                                                                |

| 08-Sep-2006 | 6        | Changed Table 24: Output driving current on page 39<br>Added Figure 14: VOL standard ports vs IOL @ VDD 5 V thru<br>Figure 18: VOL P6.0 pin vs IOL @ VDD 5 V on page 40.<br>Added Figure 20: NRSTIN RPU vs. VDD |

| 08-Jun-2008 | 7        | Inch values rounded to 4 decimal digits in <i>Section 5.1: Package mechanical data</i><br>Modified BSPI speed in <i>Section 2.1: On-chip peripherals</i>                                                        |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com