Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Obsolete                                                            |

| Core Processor             | ARM7®                                                               |

| Core Size                  | 32-Bit Single-Core                                                  |

| Speed                      | 36MHz                                                               |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                   |

| Peripherals                | DMA, POR, PWM, WDT                                                  |

| Number of I/O              | 112                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                    |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 16K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                         |

| Data Converters            | A/D 16x10b                                                          |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                  |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 144-LQFP                                                            |

| Supplier Device Package    | -                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/str735fz1t7 |

Contents STR73xFxx

# **Contents**

| 1 | Sco  | ре        |                                  | 4  |

|---|------|-----------|----------------------------------|----|

|   | 1.1  | Descri    | iption                           | 4  |

| 2 | Ove  | rview .   |                                  | 5  |

|   | 2.1  | On-ch     | ip peripherals                   | 6  |

| 3 | Bloc | k diagr   | am                               | 8  |

|   | 3.1  | Relate    | ed documentation                 | 10 |

|   | 3.2  | Pin de    | scription                        | 11 |

|   |      | 3.2.1     | STR730F/STR735F (TQFP144)        |    |

|   |      | 3.2.2     | STR730F/STR735F (LFBGA144)       | 12 |

|   |      | 3.2.3     | STR731F/STR736F (TQFP100)        | 13 |

|   | 3.3  | Memo      | ry mapping                       | 20 |

| 4 | Elec | trical pa | arameters                        | 21 |

|   | 4.1  | Param     | neter conditions                 | 21 |

|   |      | 4.1.1     | Minimum and maximum values       | 21 |

|   |      | 4.1.2     | Typical values                   | 21 |

|   |      | 4.1.3     | Typical curves                   | 21 |

|   |      | 4.1.4     | Loading capacitor                | 21 |

|   |      | 4.1.5     | Pin input voltage                | 21 |

|   | 4.2  | Absolu    | ute maximum ratings              | 22 |

|   | 4.3  | Opera     | ting conditions                  | 24 |

|   |      | 4.3.1     | Supply current characteristics   | 25 |

|   |      | 4.3.2     | Clock and timing characteristics | 29 |

|   |      | 4.3.3     | Memory characteristics           | 34 |

|   |      | 4.3.4     | EMC characteristics              | 35 |

|   |      | 4.3.5     | I/O port pin characteristics     | 38 |

|   |      | 4.3.6     | 10-bit ADC characteristics       | 43 |

| 5 | Pack | kage ch   | aracteristics                    | 46 |

|   | 5.1  | Packa     | ge mechanical data               | 46 |

|   | 5.2  | Therm     | nal characteristics              | 48 |

Overview STR73xFxx

#### Flexible clock control

Two clock sources are used to drive the microcontroller, a main clock driven by an external crystal or ceramic resonator and an internal backup RC oscillator that operates at 2 MHz or 32 kHz. The embedded PLL can be configured to generate an internal system clock of up to 36 MHz. The PLL output frequency can be programmed using a wide selection of multipliers and dividers.

### Voltage regulators

The STR73xF requires an external 4.5 to 5.5 V power supply. There are two internal Voltage Regulators for generating the 1.8 V power supply needed by the core and peripherals. The main VR is switched off and the Low Power VR switched on when the application puts the STR73xF in Low Power Wait for Interrupt (LPWFI) mode.

#### Low voltage detectors

The voltage regulator and Flash modules each have an embedded LVD that monitors the internal 1.8 V supply. If the voltage drops below a certain threshold, the LVD will reset the STR73xF.

Note: An external power-on reset must be provided ensure the microcontroller starts-up correctly.

# 2.1 On-chip peripherals

### **CAN** interfaces

The three CAN modules are compliant with the CAN specification V2.0 part B (active). The bit rate can be programmed up to 1 MBaud. These are not available in the STR735 and STR736.

### **DMA**

4 DMA controllers, each with 4 data streams manage memory to memory, peripheral to peripheral, peripheral to memory and memory to peripheral transfers. The DMA requests are connected to TIM timers, BSPI0, BSPI1, BSPI2 and ADC. One of the streams can be configured to be triggered by a software request, independently from any peripheral activity.

### 16-bit timers (TIM)

Each of the ten timers (six in 100-pin devices) have a 16-bit free-running counter with 7-bit prescaler, up to two input capture/output compare functions, a pulse counter function, and a PWM channel with selectable frequency. This provides a total of 16 independent PWMs (12 in 100-pin devices) when added with the PWM modules (see next paragraph).

### **PWM modules (PWM)**

The six 16-bit PWM modules have independently programmable periods and duty-cycles, with 5+3 bit prescaler factor.

#### Timebase timers (TB)

The three 16-bit timebase timers with 8-bit prescaler for general purpose time triggering operations.

#### Real-time clock (RTC)

The RTC provides a set of continuously running counters driven by separate clock signal derived from the main oscillator. The RTC can be used as a general timebase or

Block diagram STR73xFxx

# 3 Block diagram

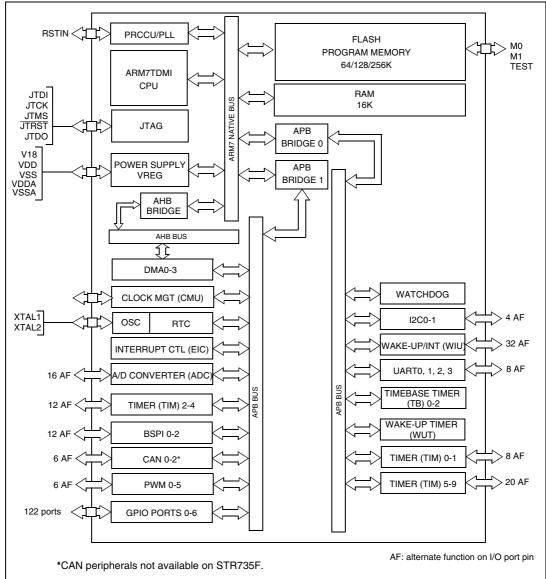

Figure 1. STR730F/STR735F block diagram

STR73xFxx Block diagram

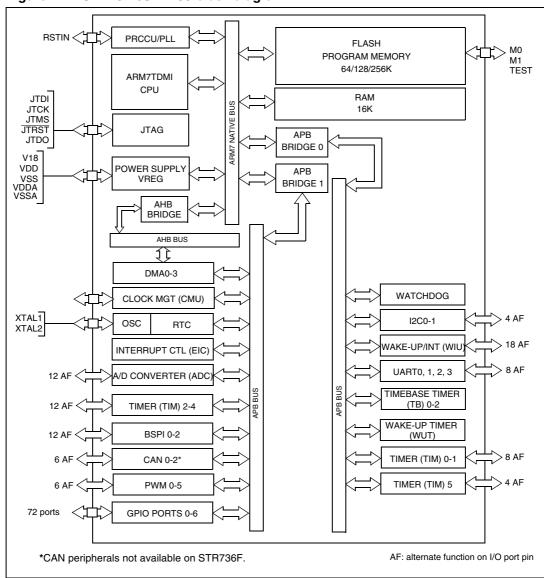

Figure 2. STR731F/STR736 block diagram

**Ly/**

Block diagram STR73xFxx

# 3.1 Related documentation

Available from www.arm.com:

ARM7TDMI technical reference manual

Available from http://www.st.com:

STR73x reference manual (RM0001)

STR7 Flash programming reference manual

STR73x software library user manual

For a list of related application notes refer to http://www.st.com.

STR73xFxx Block diagram

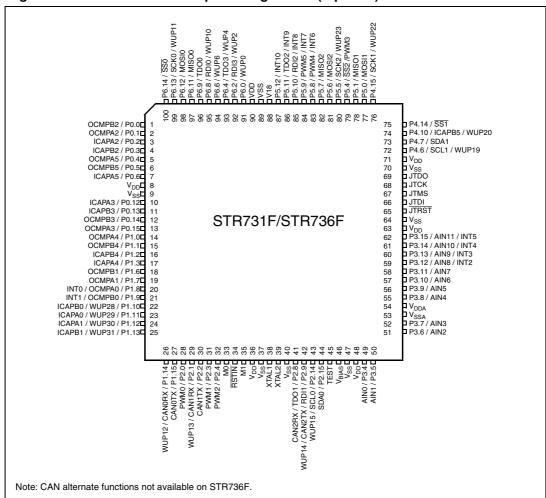

# 3.2.3 STR731F/STR736F (TQFP100)

Figure 4. STR731F/STR736F pin configuration (top view)

Block diagram STR73xFxx

Table 4. STR73xF pin description

|         | Pin n°   |         |                                |      |                | Inp   | out       | Ou         | tpu | t  |                                      |                                                         |                                                        |

|---------|----------|---------|--------------------------------|------|----------------|-------|-----------|------------|-----|----|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| TQFP144 | LFBGA144 | TQFP100 | Pin name                       | Туре | Input Level    | pd/nd | interrupt | Capability | QO  | ЬР | Main<br>function<br>(after<br>reset) | Alternate                                               | function                                               |

| 97      | F9       |         | P4.3/ICAPB8                    | I/O  | T <sub>T</sub> |       | WUP27     | 2mA        | Χ   | Χ  | Port 4.3                             | TIM8: input capt                                        | ure B input                                            |

| 98      | F8       |         | P4.4/CAN2TX                    | I/O  | T <sub>T</sub> |       |           | 2mA        | Χ   | Χ  | Port 4.4                             | CAN2: transmit                                          | data output                                            |

| 99      | E12      |         | P4.5/CAN2RX                    | I/O  | T <sub>T</sub> |       | WUP18     | 2mA        | Х   | Χ  | Port 4.5                             | CAN2: receive d                                         | ata input                                              |

| 100     | E11      | 72      | P4.6/SCL1                      | I/O  | T <sub>T</sub> |       | WUP19     | 2mA        | Χ   | Χ  | Port 4.6                             | I2C1: serial cloc                                       | k                                                      |

| 101     | C12      | 73      | P4.7/SDA1                      | I/O  | T <sub>T</sub> |       |           | 2mA        | Χ   | Χ  | Port 4.7                             | I2C1: serial data                                       | l                                                      |

| 102     | B12      |         | P4.8/OCMPA8                    | I/O  | T <sub>T</sub> |       |           | 2mA        | Χ   | Χ  | Port 4.8                             | TIM8: output cor                                        | mpare A output                                         |

| 103     | E10      |         | P4.9/ICAPB6                    | I/O  | T <sub>T</sub> |       |           | 2mA        | Х   | Х  | Port 4.9                             | TIM6: input capt                                        | ure B input                                            |

| 104     | E9       | 74      | P4.10/ICAPA6/I<br>CAPB5        | I/O  | T <sub>T</sub> |       | WUP20     | 2mA        | Х   | Х  | Port 4.10                            | TIM6: input<br>capture A input<br>(144-pin pkg<br>only) | TIM5: input<br>capture B<br>input<br>(TQFP100<br>only) |

| 105     | D12      |         | P4.11/OCMPB<br>8               | I/O  | T <sub>T</sub> |       |           | 2mA        | Х   | Х  | Port 4.11                            | TIM8: output compare B output                           |                                                        |

| 106     | D11      |         | P4.12/ICAPA9                   | I/O  | $T_T$          |       | WUP21     | 2mA        | Х   | Х  | Port 4.12                            | TIM9: input capture A input                             |                                                        |

| 107     | D10      |         | P4.13/ICAPB9                   | I/O  | T <sub>T</sub> |       |           | 2mA        | Χ   | Χ  | Port 4.13                            | TIM9: input capt                                        | ure B input                                            |

| 108     | C11      | 75      | P4.14/SS1                      | I/O  | T <sub>T</sub> |       |           | 2mA        | Χ   | Χ  | Port 4.14                            | BSPI1: slave sel                                        | ect                                                    |

| 109     | B11      | 76      | P4.15/SCK1                     | I/O  | $T_T$          |       | WUP22     | 2mA        | Χ   | Х  | Port 4.15                            | BSPI1: serial clo                                       | ock                                                    |

| 110     | B10      | 77      | P5.0/MOSI1                     | I/O  | T <sub>T</sub> |       |           | 2mA        | Х   | Х  | Port 5.0                             | BSPI1: master of input                                  | output/slave                                           |

| 111     | C10      | 78      | P5.1/MISO1                     | I/O  | T <sub>T</sub> |       |           | 2mA        | Х   | Х  | Port 5.1                             | BSPI1: master in output                                 | nput/Slave                                             |

| 112     | A9       |         | P5.2/OCMPA9                    | I/O  | T <sub>T</sub> |       |           | 2mA        | Χ   | Χ  | Port 5.2                             | TIM9: output cor                                        | mpare A output                                         |

| 113     | В9       |         | P5.3/OCMPB9                    | I/O  | T <sub>T</sub> |       |           | 2mA        | Х   | Х  | Port 5.3                             | TIM9: output cor                                        | mpare B output                                         |

| 114     | C9       | 79      | P5.4/ <del>SS</del> 2/PWM<br>3 | I/O  | T <sub>T</sub> |       |           | 2mA        | X   | X  | Port 5.4                             | BSPI2: slave select                                     | PWM3: PWM<br>output<br>(TQFP100<br>only)               |

| 115     | D9       | 80      | P5.5/SCK2                      | I/O  | T <sub>T</sub> |       | WUP23     | 2mA        | Х   | Х  | Port 5.5                             | BSPI2: serial clo                                       | ock                                                    |

| 116     | A11      | 81      | P5.6/MOSI2                     | I/O  | T <sub>T</sub> |       |           | 2mA        | Х   | Х  | Port 5.6                             | BSPI2: master output/slave input                        |                                                        |

| 117     | A10      | 82      | P5.7/MISO2                     | I/O  | T <sub>T</sub> |       |           | 2mA        | Х   | Х  | Port 5.7                             | BSPI2: master input/slave output                        |                                                        |

| 118     | A8       | 83      | P5.8/PWM4                      | I/O  | T <sub>T</sub> |       | INT6      | 2mA        | Х   | Х  | Port 5.8                             | PWM4: PWM ou<br>only)                                   | tput (TQFP100                                          |

# 4 Electrical parameters

### 4.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

### 4.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A=25^{\circ}$  C and  $T_A=T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

# 4.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A=25^{\circ}$  C and  $V_{DD}=5$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

# 4.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 4.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 6*.

### 4.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 7*.

Figure 6. Pin loading conditions

Figure 7. Pin input voltage

STR7 PIN

STR7 PIN

VIN

STR7 PIN

# 4.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Table 5. Voltage characteristics

| Symbol                                | Ratings                                            | Min                | Max                  | Unit |

|---------------------------------------|----------------------------------------------------|--------------------|----------------------|------|

| V <sub>DD</sub> - V <sub>SS</sub>     | External 5 V Supply voltage                        | -0.3               | 6.0                  | V    |

| V <sub>SSA</sub>                      | Reference ground for A/D converter                 | V <sub>SS</sub>    | V <sub>SS</sub>      | V    |

| V <sub>DDA</sub> - V <sub>SSA</sub>   | Reference voltage for A/D converter                | -0.3               | V <sub>DD</sub> +0.3 | V    |

| V <sub>IN</sub>                       | Input voltage on any pin                           | -0.3               | V <sub>DD</sub> +0.3 | V    |

| IΔV <sub>DDx</sub> I                  | Variations between different 5 V power pins        | -                  | 0.3                  | mV   |

| IV <sub>SSX</sub> - V <sub>SS</sub> I | Variations between all the different ground pins   | -                  | 0.3                  | IIIV |

| V <sub>ESD(HBM)</sub>                 | Electrostatic discharge voltage (Human Body Model) | see : Absolute n   | naximum ratings      |      |

| V <sub>ESD(MM)</sub>                  | Electrostatic discharge voltage (Machine Model)    | (electrical sensit |                      |      |

Table 6. Current characteristics

| Symbol                                       | Ratings                                                     | Max. | Unit |

|----------------------------------------------|-------------------------------------------------------------|------|------|

| I <sub>VDD</sub>                             | Total current into V <sub>DD</sub> power lines (source) 1)  | 100  |      |

| I <sub>VSS</sub>                             | Total current out of V <sub>SS</sub> ground lines (sink) 1) | 100  |      |

| l                                            | Output current sunk by any I/O and control pin              | 10   | mA   |

| IIO                                          | Output current source by any I/O and control pin            | 10   | mA   |

| I <sub>INJ(PIN)</sub> <sup>2) &amp; 3)</sup> | Injected current on any other pin 4) &5)                    | ±10  |      |

| ΣI <sub>INJ(PIN)</sub> <sup>2)</sup>         | Total injected current (sum of all I/O and control pins) 4) | ±75  |      |

All 5 V power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external 5 V supply

I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>.

Negative injection disturbs the analog performance of the device. See note in Section 4.3.6: 10-bit ADC characteristics on page 43.

<sup>4.</sup> When several inputs are submitted to a current injection, the maximum  $\mathfrak{L}_{\mathsf{INJ}(\mathsf{PIN})}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with  $\mathfrak{L}_{\mathsf{INJ}(\mathsf{PIN})}$  maximum current injection on four I/O port pins of the device.

<sup>5.)</sup> In 144-pin devices, only +10 mA on P0.3, P1.13, P3.6 and P4.13 pins (negative injection not allowed).

Table 7. Thermal characteristics

| Symbol           | Ratings                                              | Value                | Unit       |

|------------------|------------------------------------------------------|----------------------|------------|

| T <sub>STG</sub> | Storage temperature range                            | -55 to +150          | °C         |

| TJ               | Maximum junction temperature (see Section 5 page 48) | .2: Thermal characte | ristics on |

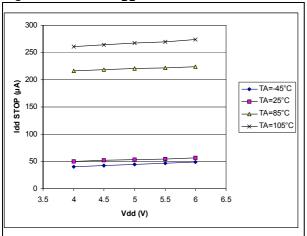

Figure 8. STOP I<sub>DD</sub> vs. VDD

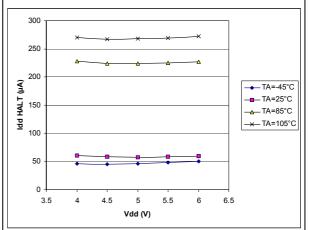

Figure 9. HALT I<sub>DD</sub> vs. V<sub>DD</sub>

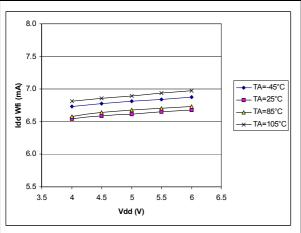

Figure 10. WFI  $I_{DD}$  vs.  $V_{DD}$

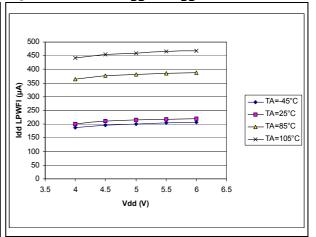

Figure 11. LPWFI  $I_{DD}$  vs.  $V_{DD}$

# 4.3.3 Memory characteristics

# Flash memory

Table 18. Flash memory characteristics

| Compleal                      | Downston                    | Took Conditions                                   |     | Value      | 9                 | Unit    |  |

|-------------------------------|-----------------------------|---------------------------------------------------|-----|------------|-------------------|---------|--|

| Symbol                        | Parameter                   | Test Conditions                                   | Min | Тур        | Max <sup>1)</sup> | Oilit   |  |

| t <sub>WP</sub>               | Word program (32-bit)       |                                                   |     | 35         | 80                | μS      |  |

| t <sub>DWP</sub>              | Double word program(64-bit) |                                                   |     | 64         | 150               | μS      |  |

| t <sub>BP64</sub>             | Bank program (64 K)         | Double word program                               |     | 0.5        | 1.25              | s       |  |

| t <sub>BP128</sub>            | Bank program (128 K)        | Double word program                               |     | 1          | 2.5               | s       |  |

| t <sub>BP256</sub>            | Bank program (256 K)        | Double word program                               |     | 2          | 4.9               | s       |  |

| t <sub>SE8</sub>              | Sector erase (8 K)          | Not preprogrammed<br>Preprogrammed <sup>2)</sup>  |     | 0.6<br>0.5 | 0.9<br>0.8        | s       |  |

| t <sub>SE32</sub>             | Sector erase (32 K)         | Not preprogrammed<br>Preprogrammed <sup>2)</sup>  |     | 1.1<br>0.8 | 2<br>1.8          | s       |  |

| t <sub>SE64</sub>             | Sector erase (64 K)         | Not preprogrammed preprogrammed <sup>2)</sup>     |     | 1.7<br>1.3 | 3.7<br>3.3        | S       |  |

| t <sub>RPD</sub> 3)           | Recovery from power-down    |                                                   |     |            | 20                | μS      |  |

| t <sub>PSL</sub> 3)           | Program suspend latency     |                                                   |     |            | 10                | μS      |  |

| t <sub>ESL</sub> 3)           | Erase suspend latency       |                                                   |     |            | 30                | μS      |  |

| t <sub>ESR</sub> 3)           | Erase suspend rate          | Min. time from erase resume to next erase suspend |     | 20         | 20                | ms      |  |

| t <sub>SP</sub> <sup>3)</sup> | Set protection              |                                                   |     | 40         | 170               | μs      |  |

| t <sub>FPW</sub> 3)           | First word program          |                                                   |     | 1          |                   | ms      |  |

| N <sub>END</sub>              | Endurance                   |                                                   | 10  |            |                   | kcycles |  |

| t <sub>RET</sub>              | Data retention              | T <sub>A</sub> = 85° C                            | 20  |            |                   | Years   |  |

<sup>1.</sup>  $T_A = -45^{\circ}$  C after 0 cycles, Guaranteed by characterization, not tested in production.

<sup>2.</sup> All bits programmed to 0.

<sup>3.</sup> Guaranteed by design, not tested in production.

### 4.3.4 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

# Functional EMS (electromagnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

### **Prequalification trials:**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RESET pin or the oscillator pins for 1 second

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

Table 19. EMS data

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                       | Level/<br>Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{DD}$ =5 V, $T_A$ =+25° C, $f_{MCLK}$ =36 MHz conforms to IEC 1000-4-2                        | 4A              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | V <sub>DD</sub> =5 V, T <sub>A</sub> =+25° C, f <sub>MCLK</sub> =36 MHz conforms to IEC 1000-4-4 | 4A              |

## **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

Table 20. EMI data

| Symbol           | Parameter  | Conditions                                                            | Monitored frequency band | Max<br>[f <sub>OSC4M</sub> | Unit    |      |

|------------------|------------|-----------------------------------------------------------------------|--------------------------|----------------------------|---------|------|

|                  |            |                                                                       | requericy barra          | 6/36 MHz                   | 8/8 MHz |      |

|                  | Peak level | v <sub>DD</sub> =5.0V,<br>evel T <sub>A</sub> =+25°C,<br>All packages | 0.1 MHz to 30 MHz        | 23                         | 30      |      |

| S                |            |                                                                       | 30 MHz to 130 MHz        | 37                         | 34      | dΒμV |

| S <sub>EMI</sub> |            |                                                                       | 130 MHz to 1 GHz         | 20                         | 7       |      |

|                  |            |                                                                       | SAE EMI Level            | 4                          | 3.5     | -    |

### Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: human body model and machine model. This test conforms to the JESD22-A114A/A115A standard.

Table 21. ESD Absolute Maximum ratings

| Symbol                | Ratings Conditions                                    |                        | Maximum<br>value <sup>1)</sup>    | Unit |

|-----------------------|-------------------------------------------------------|------------------------|-----------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    |                        | 2000                              |      |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (machine model)       | T <sub>A</sub> =+25° C |                                   | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) |                        | 750 on corner pins, 500 on others |      |

#### Notes:

1. Data based on characterization results, not tested in production.

# Static and dynamic latch-up

• LU: 3 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each

# **Output driving current**

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

Table 24. Output driving current

| I/O Type        | Symbol                        | Parameter                                                                     | Conditions             | Min                  | Max | Unit |

|-----------------|-------------------------------|-------------------------------------------------------------------------------|------------------------|----------------------|-----|------|

| 0               | V <sub>OL</sub> 1)            | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> =+2 mA |                      | 0.4 |      |

| Standard        | V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time | I <sub>IO</sub> =-2 mA | V <sub>DD</sub> -0.8 |     |      |

| Med.<br>Current | V <sub>OL</sub> 1)            | Output low level voltage for an I/O pin                                       | I <sub>IO</sub> =+6 mA |                      | 0.4 | ٧    |

| (JTDO)          | V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin                                      | I <sub>IO</sub> =-6 mA | V <sub>DD</sub> -0.8 |     |      |

| High<br>Current | V <sub>OL</sub> 1)            | Output low level voltage for an I/O pin                                       | I <sub>IO</sub> =+8 mA |                      | 0.4 |      |

| P6.0            | V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin                                      | I <sub>IO</sub> =-8 mA | V <sub>DD</sub> -0.8 |     |      |

<sup>1.</sup> The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in *Table 6* and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

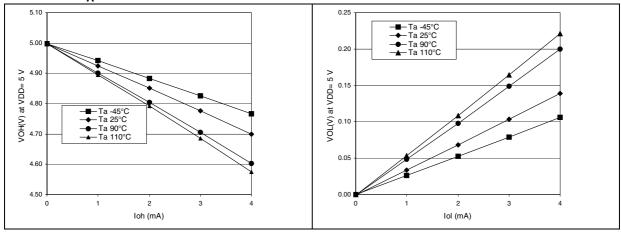

Figure 13.  $V_{OH}$  standard ports vs  $I_{OH}$  @  $V_{DD}$  5V Figure 14.  $V_{OL}$  standard ports vs  $I_{OL}$  @  $V_{DD}$  5 V  $T_A$  -45° C

577

<sup>2.</sup> The  $I_{IQ}$  current sourced must always respect the absolute maximum rating specified in *Table 6* and the sum of  $I_{IQ}$  (I/O ports and control pins) must not exceed IV<sub>DD</sub>.

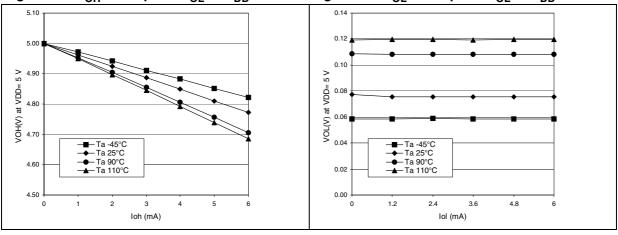

Figure 15.  $V_{OH}$  JTDO pin vs  $I_{OL}$  @  $V_{DD}$  5 V

Figure 16.  $V_{OL}$  JTDO pin vs  $I_{OL}$  @  $V_{DD}$  5 V

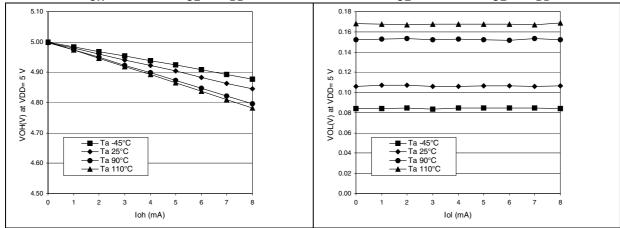

Figure 17.  $V_{OH}$  P6.0 pin vs  $I_{OL}$  @  $V_{DD}$  5 V

Figure 18.  $V_{OL}$  P6.0 pin vs  $I_{OL}$  @  $V_{DD}$  5 V

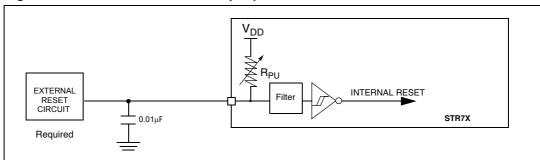

# **NRSTIN** pin

The NRSTIN pin input driver is CMOS. A permanent pull-up is present which is the same as  $R_{PU}$  (see : *General characteristics on page 38*)

Subject to general operating conditions for  $V_{DD}$  and  $T_{A}$  unless otherwise specified.

Table 25. Reset pin characteristics

| Symbol                   | Parameter                                               | Conditions | Min                 | Typ <sup>1)</sup> | Max                 | Unit |

|--------------------------|---------------------------------------------------------|------------|---------------------|-------------------|---------------------|------|

| V <sub>IL(NRSTIN)</sub>  | NRSTIN Input low level voltage 1)                       |            |                     |                   | 0.3 V <sub>DD</sub> | V    |

| V <sub>IH(NRSTIN)</sub>  | NRSTIN Input high level voltage 1)                      |            | 0.7 V <sub>DD</sub> |                   |                     | V    |

| V <sub>hys(NRSTIN)</sub> | NRSTIN Schmitt trigger voltage hysteresis <sup>2)</sup> |            |                     | 800               |                     | mV   |

| V <sub>F(RSTINn)</sub>   | NRSTIN Input filtered pulse <sup>3)</sup>               |            |                     |                   | 500                 | ns   |

| V <sub>NF(RSTINn)</sub>  | NRSTIN Input not filtered pulse <sup>3)</sup>           |            | 2                   |                   |                     | μs   |

| V <sub>RP(RSTINn)</sub>  | NRSTIN removal after Power-up <sup>3)</sup>             |            | 100                 |                   |                     | μs   |

- 1. Data based on characterization results, not tested in production.

- 2. Hysteresis voltage between Schmitt trigger switching levels.

- 3. Data guaranteed by design, not tested in production.

Figure 19. Recommended NRSTIN pin protection<sup>1)</sup>

- 1. The  $R_{\text{PU}}$  pull-up equivalent resistor is based on a resistive transistor.

- 2. The reset network protects the device against parasitic resets.

- 3. The user must ensure that the level on the NRSTIN pin can go below the V<sub>IL(NRSTIN)</sub> max. level specified in *Table 25*. Otherwise the reset will not be taken into account internally.

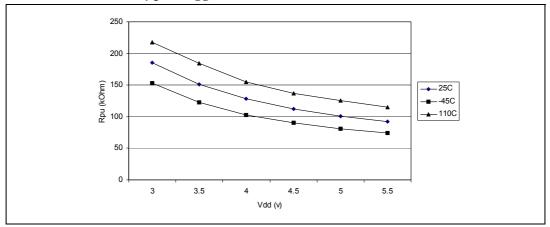

Figure 20. NRSTIN  $R_{PU}$  vs.  $V_{DD}$

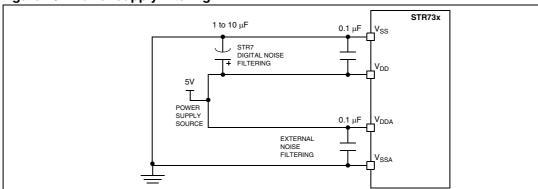

## Analog power supply and reference pins

The  $V_{DDA}$  and  $V_{SSA}$  pins are the analog power supply of the A/D converter cell. They act as the high and low reference voltages for the conversion.

Separation of the digital and analog power pins allow board designers to improve A/D performance. Conversion accuracy can be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines (see: General PCB design quidelines).

### General PCB design guidelines

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

- Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB.

- Filter power to the analog power planes. It is recommended to connect capacitors, with good high frequency characteristics, between the power and ground lines, placing 0.1 μF and optionally, if needed 10 pF capacitors as close as possible to the STR7 power supply pins and a 1 to 10 μF capacitor close to the power source (see Figure 23).

- The analog and digital power supplies should be connected in a star network. Do not use a resistor, as V<sub>DDA</sub> is used as a reference voltage by the A/D converter and any resistance would cause a voltage drop and a loss of accuracy.

- Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs near the A/D input being converted.

# Software filtering of spurious conversion results

For EMC performance reasons, it is recommended to filter A/D conversion outliers using software filtering techniques.

Figure 23. Power supply filtering

5/

SEATING Plane Ç inches1) mm Dim. Min Тур Max Min Тур Max Α 1.21 1.70 0.0476 0.0669 Ş **A**1 0.21 0.0083 1.085 0.0427 A2 E1 b 0.35 0.40 0.45 | 0.0138 | 0.0157 | 0.0177 10.15 0.3878 0.3937 0.3996 D 9.85 10.00 D1 0.3465 10.00 10.15 0.3878 0.3937 0.3996 Е 9.85 E1 8.80 0.3465 е 0.80 0.0315 F 0.60 0.0236 ddd 0.10 0.0039 0.15 0.0059 fff 0.08 0.0031 Number of Pins N <sup>1</sup>Values in inches are converted from mm and rounded to 4 decimal digits. <del>□</del>

Figure 26. 144-ball low profile fine pitch ball grid array package

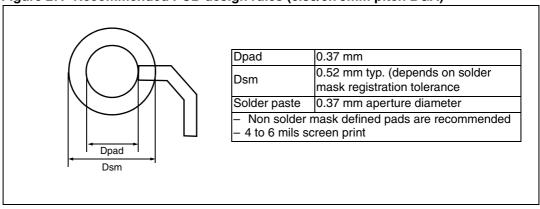

Figure 27. Recommended PCB design rules (0.80/0.75mm pitch BGA)