Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                        |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | XCore                                                         |

| Core Size                  | 32-Bit 6-Core                                                 |

| Speed                      | 500MIPS                                                       |

| Connectivity               | Configurable                                                  |

| Peripherals                | -                                                             |

| Number of I/O              | 64                                                            |

| Program Memory Size        | 64KB (16K x 32)                                               |

| Program Memory Type        | SRAM                                                          |

| EEPROM Size                | -                                                             |

| RAM Size                   | -                                                             |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                  |

| Data Converters            | -                                                             |

| Oscillator Type            | External                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 128-TQFP Exposed Pad                                          |

| Supplier Device Package    | 128-TQFP (14x14)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-l6a-64-tq128-i5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1   | xCORE Multicore Microcontrollers |

|-----|----------------------------------|

| 2   | XS1-L6A-64-TQ128 Features        |

| 3   | Pin Configuration                |

| 4   | Signal Description               |

| 5   | Product Overview                 |

| 6   | PLL                              |

| 7   | Boot Procedure                   |

| 8   | Memory                           |

| 9   | JTAG                             |

| 10  | Board Integration                |

| 11  | DC and Switching Characteristics |

| 12  | Package Information              |

| 13  | Ordering Information             |

| App | endices                          |

| Α   | Configuration of the XS1         |

| В   | Processor Status Configuration   |

| С   | Tile Configuration               |

| D   | Node Configuration               |

| E   | XMOS USB Interface               |

| F   | Device Errata                    |

| G   | JTAG, xSCOPE and Debugging       |

| Н   | Schematics Design Check List     |

| 1   | PCB Layout Design Check List     |

| J   | Associated Design Documentation  |

| K   | Related Documentation            |

| L   | Revision History                 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

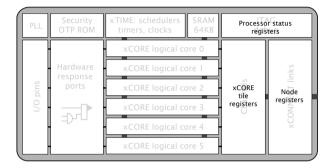

- Channels and channel ends Tasks running on logical cores communicate using channels formed between two channel ends. Data can be passed synchronously or asynchronously between the channel ends assigned to the communicating tasks. Section 5.5

- xCONNECT Switch and Links Between tiles, channel communications are implemented over a high performance network of xCONNECT Links and routed through a hardware xCONNECT Switch. Section 5.6

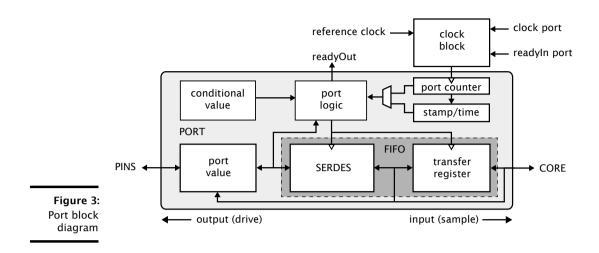

- ▶ **Ports** The I/O pins are connected to the processing cores by Hardware Response ports. The port logic can drive its pins high and low, or it can sample the value on its pins optionally waiting for a particular condition. Section 5.3

- Clock blocks xCORE devices include a set of programmable clock blocks that can be used to govern the rate at which ports execute. Section 5.4

- Memory Each xCORE Tile integrates a bank of SRAM for instructions and data, and a block of one-time programmable (OTP) memory that can be configured for system wide security features. Section 8

- PLL The PLL is used to create a high-speed processor clock given a low speed external oscillator. Section 6

- JTAG The JTAG module can be used for loading programs, boundary scan testing, in-circuit source-level debugging and programming the OTP memory. Section 9

#### 1.1 Software

Devices are programmed using C, C++ or xC (C with multicore extensions). XMOS provides tested and proven software libraries, which allow you to quickly add interface and processor functionality such as USB, Ethernet, PWM, graphics driver, and audio EQ to your applications.

## 1.2 xTIMEcomposer Studio

The xTIMEcomposer Studio development environment provides all the tools you need to write and debug your programs, profile your application, and write images into flash memory or OTP memory on the device. Because xCORE devices operate deterministically, they can be simulated like hardware within xTIMEcomposer: uniquely in the embedded world, xTIMEcomposer Studio therefore includes a static timing analyzer, cycle-accurate simulator, and high-speed in-circuit instrumentation.

xTIMEcomposer can be driven from either a graphical development environment, or the command line. The tools are supported on Windows, Linux and MacOS X and available at no cost from xmos.com/downloads. Information on using the tools is provided in the xTIMEcomposer User Guide, X3766.

$\cdot \mathbf{X} \wedge \Lambda(\cdot) \mathbf{S}$

## 4 Signal Description

This section lists the signals and I/O pins available on the XS1-L6A-64-TQ128. The device provides a combination of 1 bit, 4bit, 8bit and 16bit ports, as well as wider ports that are fully or partially (gray) bonded out. All pins of a port provide either output or input, but signals in different directions cannot be mapped onto the same port.

Pins may have one or more of the following properties:

PD/PU: The IO pin a weak pull-down or pull-up resistor. On GPIO pins this resistor can be enabled.

|          | Power pins (8)          |       |            |  |  |  |

|----------|-------------------------|-------|------------|--|--|--|

| Signal   | Function                | Туре  | Properties |  |  |  |

| GND      | Digital ground          | GND   |            |  |  |  |

| OTP_VCC  | OTP power supply        | PWR   |            |  |  |  |

| OTP_VPP  | OTP programming voltage | PWR   |            |  |  |  |

| PLL_AGND | Analog ground for PLL   | GND   |            |  |  |  |

| PLL_AVDD | Analog PLL power        | PWR   |            |  |  |  |

| RST_N    | Global reset input      | Input |            |  |  |  |

| VDD      | Digital tile power      | PWR   |            |  |  |  |

| VDDIO    | Digital I/O power       | PWR   |            |  |  |  |

ST: The IO pin has a Schmitt Trigger on its input.

| Clocks pins (2)                 |                     |       |        |  |

|---------------------------------|---------------------|-------|--------|--|

| Signal Function Type Properties |                     |       |        |  |

| CLK                             | PLL reference clock | Input | PD, ST |  |

| MODE[3:0]                       | Boot mode select    | Input | PU, ST |  |

| JTAG pins (6) |                  |        |            |  |  |

|---------------|------------------|--------|------------|--|--|

| Signal        | Function         | Туре   | Properties |  |  |

| DEBUG_N       | Multi-chip debug | I/0    | PU         |  |  |

| тск           | Test clock       | Input  | PU, ST     |  |  |

| TDI           | Test data input  | Input  | PU, ST     |  |  |

| TDO           | Test data output | Output | PD, OT     |  |  |

| TMS           | Test mode select | Input  | PU, ST     |  |  |

| TRST_N        | Test reset input | Input  | PU, ST     |  |  |

-XMOS

|        | I/O pins (64)                                                                                      |      |                                  |

|--------|----------------------------------------------------------------------------------------------------|------|----------------------------------|

| Signal | Function                                                                                           | Туре | Properties                       |

| X0D00  | 1A <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D01  | XLA <sup>4</sup> <sub>out</sub> 1B <sup>0</sup>                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D02  | XLA <sup>3</sup> <sub>out</sub> 4A <sup>0</sup> 8A <sup>0</sup> 16A <sup>0</sup> 32A <sup>20</sup> | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D03  | XLA <sup>2</sup> <sub>out</sub> 4A <sup>1</sup> 8A <sup>1</sup> 16A <sup>1</sup> 32A <sup>21</sup> | I/O  | PDs, Ru                          |

| X0D04  | $XLA_{out}^{1}$ $4B^{0}$ $8A^{2}$ $16A^{2}$ $32A^{22}$                                             | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D05  | $XLA_{out}^{0}$ 4B <sup>1</sup> 8A <sup>3</sup> 16A <sup>3</sup> 32A <sup>23</sup>                 | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D06  | $XLA_{in}^{0}$ $4B^{2}$ $8A^{4}$ $16A^{4}$ $32A^{24}$                                              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D07  | $XLA_{in}^{1}$ $4B^{3}$ $8A^{5}$ $16A^{5}$ $32A^{25}$                                              | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D08  | $XLA_{in}^2$ $4A^2$ $8A^6$ $16A^6$ $32A^{26}$                                                      | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D09  | XLA <sup>3</sup> <sub>in</sub> 4A <sup>3</sup> 8A <sup>7</sup> 16A <sup>7</sup> 32A <sup>27</sup>  | I/O  | PDs, Ru                          |

| X0D10  | XLA <sup>4</sup> <sub>in</sub> 1C <sup>0</sup>                                                     | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D11  | 1D <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>S</sub> |

| X0D12  | 1 E <sup>0</sup>                                                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D13  | XLB <sup>4</sup> <sub>out</sub> 1F <sup>0</sup>                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D14  | $XLB_{out}^3$ 4C <sup>0</sup> 8B <sup>0</sup> 16A <sup>8</sup> 32A <sup>28</sup>                   | I/O  | PDs, Ru                          |

| X0D15  | $XLB_{out}^2$ 4C <sup>1</sup> 8B <sup>1</sup> 16A <sup>9</sup> 32A <sup>29</sup>                   | I/O  | PDs, Ru                          |

| X0D16  | $XLB_{out}^{1}$ $4D^{0}$ $8B^{2}$ $16A^{10}$                                                       | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D17  | $XLB_{out}^{0}$ 4D <sup>1</sup> 8B <sup>3</sup> 16A <sup>11</sup>                                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D18  | $XLB_{in}^{0}$ $4D^{2}$ $8B^{4}$ $16A^{12}$                                                        | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D19  | XLB <sup>1</sup> <sub>in</sub> 4D <sup>3</sup> 8B <sup>5</sup> 16A <sup>13</sup>                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D20  | XLB <sup>2</sup> <sub>in</sub> 4C <sup>2</sup> 8B <sup>6</sup> 16A <sup>14</sup> 32A <sup>30</sup> | I/O  | PDs, Ru                          |

| X0D21  | $XLB_{in}^{3}$ 4C <sup>3</sup> 8B <sup>7</sup> 16A <sup>15</sup> 32A <sup>31</sup>                 | I/O  | PDs, Ru                          |

| X0D22  | XLB <sup>4</sup> <sub>in</sub> 1G <sup>0</sup>                                                     | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D23  | 1H <sup>0</sup>                                                                                    | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D24  | 110                                                                                                | I/O  | PDs                              |

| X0D25  | 1J <sup>0</sup>                                                                                    | I/O  | PDs                              |

| X0D26  | 4E <sup>0</sup> 8C <sup>0</sup> 16B <sup>0</sup>                                                   | I/O  | PDs, Ru                          |

| X0D27  | 4E <sup>1</sup> 8C <sup>1</sup> 16B <sup>1</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D28  | 4F <sup>0</sup> 8C <sup>2</sup> 16B <sup>2</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D29  | 4F <sup>1</sup> 8C <sup>3</sup> 16B <sup>3</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D30  | 4F <sup>2</sup> 8C <sup>4</sup> 16B <sup>4</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D31  | 4F <sup>3</sup> 8C <sup>5</sup> 16B <sup>5</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D32  | 4E <sup>2</sup> 8C <sup>6</sup> 16B <sup>6</sup>                                                   | I/O  | PDs, Ru                          |

| X0D33  | 4E <sup>3</sup> 8C <sup>7</sup> 16B <sup>7</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D34  | 1K <sup>0</sup>                                                                                    | I/O  | PDs                              |

| X0D35  | 1L <sup>0</sup>                                                                                    | I/O  | PDs                              |

| X0D36  | 1M <sup>0</sup> 8D <sup>0</sup> 16B <sup>8</sup>                                                   | I/O  | PDs                              |

| X0D37  | 1N <sup>0</sup> 8D <sup>1</sup> 16B <sup>9</sup>                                                   | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D38  | 10 <sup>0</sup> 8D <sup>2</sup> 16B <sup>10</sup>                                                  | I/O  | PDs, Ru                          |

| X0D39  | 1P <sup>0</sup> 8D <sup>3</sup> 16B <sup>11</sup>                                                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

| X0D40  | 8D <sup>4</sup> 16B <sup>12</sup>                                                                  | I/O  | PD <sub>S</sub> , R <sub>U</sub> |

|        |                                                                                                    |      | (continued)                      |

-XMOS<sup>®</sup>

XS1-L6A-64-TQ128

The port logic can drive its pins high or low, or it can sample the value on its pins, optionally waiting for a particular condition. Ports are accessed using dedicated instructions that are executed in a single processor cycle.

Data is transferred between the pins and core using a FIFO that comprises a SERDES and transfer register, providing options for serialization and buffered data.

Each port has a 16-bit counter that can be used to control the time at which data is transferred between the port value and transfer register. The counter values can be obtained at any time to find out when data was obtained, or used to delay I/O until some time in the future. The port counter value is automatically saved as a timestamp, that can be used to provide precise control of response times.

The ports and xCONNECT links are multiplexed onto the physical pins. If an xConnect Link is enabled, the pins of the underlying ports are disabled. If a port is enabled, it overrules ports with higher widths that share the same pins. The pins on the wider port that are not shared remain available for use when the narrower port is enabled. Ports always operate at their specified width, even if they share pins with another port.

## 5.4 Clock blocks

xCORE devices include a set of programmable clocks called clock blocks that can be used to govern the rate at which ports execute. Each xCORE tile has six clock blocks: the first clock block provides the tile reference clock and runs at a default frequency of 100MHz; the remaining clock blocks can be set to run at different frequencies.

A clock block can use a 1-bit port as its clock source allowing external application clocks to be used to drive the input and output interfaces.

-XMOS°

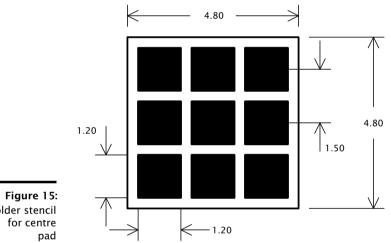

Solder stencil for centre

21

# 11 DC and Switching Characteristics

| Symbol   | Parameter                                                | MIN  | TYP  | MAX  | UNITS | Notes |

|----------|----------------------------------------------------------|------|------|------|-------|-------|

| VDD      | Tile DC supply voltage                                   | 0.95 | 1.00 | 1.05 | V     |       |

| VDDIO    | I/O supply voltage                                       | 3.00 | 3.30 | 3.60 | V     |       |

| PLL_AVDD | PLL analog supply                                        | 0.95 | 1.00 | 1.05 | V     |       |

| OTP_VCC  | OTP supply voltage                                       | 3.00 | 3.30 | 3.60 | V     |       |

| OTP_VPP  | OTP external programming voltage (optional program only) | 6.18 | 6.50 | 6.83 | V     |       |

| CI       | xCORE Tile I/O load<br>capacitance                       |      |      | 25   | pF    |       |

| Та       | Ambient operating<br>temperature (Commercial)            | 0    |      | 70   | °C    |       |

|          | Ambient operating<br>temperature (Industrial)            | -40  |      | 85   | °C    |       |

| Tj       | Junction temperature                                     |      |      | 125  | °C    |       |

| Tstg     | Storage temperature                                      | -65  |      | 150  | °C    |       |

## 11.1 Operating Conditions

Figure 16: Operating conditions

## 11.2 DC Characteristics

| Symbol | Parameter            | MIN   | ТҮР | MAX  | UNITS | Notes |

|--------|----------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage   | 2.00  |     | 3.60 | V     | A     |

| V(IL)  | Input low voltage    | -0.30 |     | 0.70 | V     | A     |

| V(OH)  | Output high voltage  | 2.00  |     |      | V     | B, C  |

| V(OL)  | Output low voltage   |       |     | 0.60 | V     | B, C  |

| R(PU)  | Pull-up resistance   |       | 35K |      | Ω     | D     |

| R(PD)  | Pull-down resistance |       | 35K |      | Ω     | D     |

Figure 17: DC characteristics

A All pins except power supply pins.

B Ports 1A, 1D, 1E, 1H, 1I, 1J, 1K and 1L are nominal 8 mA drivers, the remainder of the general-purpose I/Os are 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry.

# 11.3 ESD Stress Voltage

Figure 18 ESD stress voltage

| 18: | Symbol | Parameter        | MIN   | TYP | MAX  | UNITS | Notes |

|-----|--------|------------------|-------|-----|------|-------|-------|

| ess | HBM    | Human body model | -2.00 |     | 2.00 | KV    |       |

| age | MM     | Machine model    | -200  |     | 200  | V     |       |

-XMOS

# Appendices

# A Configuration of the XS1

The device is configured through three banks of registers, as shown in Figure 27.

Figure 27: Registers

> The following communication sequences specify how to access those registers. Any messages transmitted contain the most significant 24 bits of the channel-end to which a response is to be sent. This comprises the node-identifier and the channel number within the node. if no response is required on a write operation, supply 24-bits with the last 8-bits set, which suppresses the reply message. Any multi-byte data is sent most significant byte first.

## A.1 Accessing a processor status register

The processor status registers are accessed directly from the processor instruction set. The instructions GETPS and SETPS read and write a word. The register number should be translated into a processor-status resource identifier by shifting the register number left 8 places, and ORing it with 0x0C. Alternatively, the functions getps(reg) and setps(reg,value) can be used from XC.

## A.2 Accessing an xCORE Tile configuration register

xCORE Tile configuration registers can be accessed through the interconnect using the functions write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tile  $\rightarrow$  ref, ...), where tileref is the name of the xCORE Tile, e.g. tile[1]. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the xCORE tile configuration registers. The destination of the channel-end should be set to 0xnnnnC20C where nnnnn is the tile-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

-XM()S

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

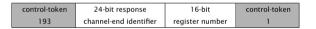

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to the read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.3 Accessing node configuration

Node configuration registers can be accessed through the interconnect using the functions write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...), where device is the name of the node. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the node configuration registers. The destination of the channel-end should be set to 0xnnnnC30C where nnnn is the node-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

$-X \wedge ()S$

The response to a read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

29

# **B** Processor Status Configuration

The processor status control registers can be accessed directly by the processor using processor status reads and writes (use getps(reg) and setps(reg,value) for reads and writes).

| Number    | Perm | Description                           |  |

|-----------|------|---------------------------------------|--|

| 0x00      | RW   | RAM base address                      |  |

| 0x01      | RW   | Vector base address                   |  |

| 0x02      | RW   | xCORE Tile control                    |  |

| 0x03      | RO   | xCORE Tile boot status                |  |

| 0x05      | RO   | Security configuration                |  |

| 0x06      | RW   | Ring Oscillator Control               |  |

| 0x07      | RO   | Ring Oscillator Value                 |  |

| 0x08      | RO   | Ring Oscillator Value                 |  |

| 0x09      | RO   | Ring Oscillator Value                 |  |

| 0x0A      | RO   | ing Oscillator Value                  |  |

| 0x10      | DRW  | Debug SSR                             |  |

| 0x11      | DRW  | Debug SPC                             |  |

| 0x12      | DRW  | Debug SSP                             |  |

| 0x13      | DRW  | DGETREG operand 1                     |  |

| 0x14      | DRW  | DGETREG operand 2                     |  |

| 0x15      | DRW  | Debug interrupt type                  |  |

| 0x16      | DRW  | Debug interrupt data                  |  |

| 0x18      | DRW  | Debug core control                    |  |

| 0x20 0x27 | DRW  | Debug scratch                         |  |

| 0x30 0x33 | DRW  | Instruction breakpoint address        |  |

| 0x40 0x43 | DRW  | Instruction breakpoint control        |  |

| 0x50 0x53 | DRW  | Data watchpoint address 1             |  |

| 0x60 0x63 | DRW  | Data watchpoint address 2             |  |

| 0x70 0x73 | DRW  | Data breakpoint control register      |  |

| 0x80 0x83 | DRW  | Resources breakpoint mask             |  |

| 0x90 0x93 | DRW  | Resources breakpoint value            |  |

| 0x9C 0x9F | DRW  | Resources breakpoint control register |  |

-XMOS<sup>®</sup>

Figure 28: Summary

#### B.1 RAM base address: 0x00

This register contains the base address of the RAM. It is initialized to 0x00010000.

**0x00**: RAM base address

| :00: | Bits | Perm | Init | Description                                |

|------|------|------|------|--------------------------------------------|

| ase  | 31:2 | RW   |      | Most significant 16 bits of all addresses. |

| ess  | 1:0  | RO   | -    | Reserved                                   |

## B.2 Vector base address: 0x01

Base address of event vectors in each resource. On an interrupt or event, the 16 most significant bits of the destination address are provided by this register; the least significant 16 bits come from the event vector.

0x01: Vector base address

|    | Bits  | Perm | Init | Description                                                    |

|----|-------|------|------|----------------------------------------------------------------|

| e. | 31:16 | RW   |      | The most significant bits for all event and interrupt vectors. |

| s  | 15:0  | RO   | -    | Reserved                                                       |

## B.3 xCORE Tile control: 0x02

Register to control features in the xCORE tile

| Bits | Perm | Init | Description                                                                                                                                                                                                                                             |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:6 | RO   | -    | Reserved                                                                                                                                                                                                                                                |

| 5    | RW   | 0    | Set to 1 to select the dynamic mode for the clock divider when<br>the clock divider is enabled. In dynamic mode the clock divider is<br>only activated when all active logical cores are paused. In static<br>mode the clock divider is always enabled. |

| 4    | RW   | 0    | Set to 1 to enable the clock divider. This slows down the xCORE tile clock in order to use less power.                                                                                                                                                  |

| 3:0  | RO   | -    | Reserved                                                                                                                                                                                                                                                |

0x02: xCORE Tile control

## B.4 xCORE Tile boot status: 0x03

This read-only register describes the boot status of the xCORE tile.

-XMOS-

| Bits  | Perm | Init | Description                                                                        |  |

|-------|------|------|------------------------------------------------------------------------------------|--|

| 31:24 | RO   | -    | Reserved                                                                           |  |

| 23:16 | RO   |      | xCORE tile number on the switch.                                                   |  |

| 15:9  | RO   | -    | eserved                                                                            |  |

| 8     | RO   |      | et to 1 if boot from OTP is enabled.                                               |  |

| 7:0   | RO   |      | The boot mode pins MODE0, MODE1,, specifying the boot frequency, boot source, etc. |  |

0x03: xCORE Tile boot status

## **B.5** Security configuration: 0x05

Copy of the security register as read from OTP.

0x05: Security configuration

| Bits | Perm | Init | Description |  |

|------|------|------|-------------|--|

| 31:0 | RO   |      | Value.      |  |

## B.6 Ring Oscillator Control: 0x06

There are four free-running oscillators that clock four counters. The oscillators can be started and stopped using this register. The counters should only be read when the ring oscillator is stopped. The counter values can be read using four subsequent registers. The ring oscillators are asynchronous to the xCORE tile clock and can be used as a source of random bits.

**0x06** Ring Oscillator Control

| _        | Bits | Perm | Init | Description                                        |  |

|----------|------|------|------|----------------------------------------------------|--|

| 6:       | 31:2 | RO   | -    | Reserved                                           |  |

| ig<br>or | 1    | RW   | 0    | Set to 1 to enable the xCORE tile ring oscillators |  |

| ol       | 0    | RW   | 0    | Set to 1 to enable the peripheral ring oscillators |  |

## B.7 Ring Oscillator Value: 0x07

This register contains the current count of the xCORE Tile Cell ring oscillator. This value is not reset on a system reset.

**0x07:** Ring Oscillator Value

|   | Bits  | Perm | Init | Description                   |  |

|---|-------|------|------|-------------------------------|--|

|   | 31:16 | RO   | -    | Reserved                      |  |

| l | 15:0  | RO   | -    | Ring oscillator counter data. |  |

-XMOS

#### B.8 Ring Oscillator Value: 0x08

This register contains the current count of the xCORE Tile Wire ring oscillator. This value is not reset on a system reset.

**0x08:** Ring Oscillator Value

| Bits  | Perm | Init | Description                   |  |

|-------|------|------|-------------------------------|--|

| 31:16 | RO   | -    | Reserved                      |  |

| 15:0  | RO   | -    | Ring oscillator counter data. |  |

## B.9 Ring Oscillator Value: 0x09

This register contains the current count of the Peripheral Cell ring oscillator. This value is not reset on a system reset.

**0x09** Ring Oscillator Value

| ):     | Bits  | Perm | Init | Description                   |

|--------|-------|------|------|-------------------------------|

| )<br>r | 31:16 | RO   | -    | Reserved                      |

| 5      | 15:0  | RO   | -    | Ring oscillator counter data. |

## B.10 Ring Oscillator Value: 0x0A

This register contains the current count of the Peripheral Wire ring oscillator. This value is not reset on a system reset.

**0x0A:** Ring Oscillator Value

| DA:<br>ng | Bits  | Perm | Init | Description                   |

|-----------|-------|------|------|-------------------------------|

| tor       | 31:16 | RO   | -    | Reserved                      |

| ue        | 15:0  | RO   | -    | Ring oscillator counter data. |

## B.11 Debug SSR: 0x10

This register contains the value of the SSR register when the debugger was called.

| <b>0x10:</b><br>Debug SSR | Bits | Perm | Init | Description |

|---------------------------|------|------|------|-------------|

| Debug SSR                 | 31:0 | RO   | -    | Reserved    |

## B.12 Debug SPC: 0x11

This register contains the value of the SPC register when the debugger was called.

0x80 .. 0x83: Resources breakpoint mask

| urces<br>point | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| mask           | 31:0 | DRW  |      | Value.      |

## B.26 Resources breakpoint value: 0x90 .. 0x93

This set of registers contains the value for the four resource watchpoints.

0x90 .. 0x93: Resources breakpoint value

| rces<br>oint | Bits | Perm | Init | Description |

|--------------|------|------|------|-------------|

| alue         | 31:0 | DRW  |      | Value.      |

## B.27 Resources breakpoint control register: 0x9C .. 0x9F

This set of registers controls each of the four resource watchpoints.

|                                                  | Bits  | Perm | Init | Description                                                                                                                                                                                                                          |

|--------------------------------------------------|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  | 31:24 | RO   | -    | Reserved                                                                                                                                                                                                                             |

|                                                  | 23:16 | DRW  | 0    | A bit for each logical core in the tile allowing the breakpoint to be enabled individually for each logical core.                                                                                                                    |

|                                                  | 15:2  | RO   | -    | Reserved                                                                                                                                                                                                                             |

| 0x9C 0x9F:<br>Resources<br>breakpoint<br>control | 1     | DRW  | 0    | By default, resource watchpoints trigger when the resource id<br>masked with the set Mask equals the Value. If set to 1, resource<br>watchpoints trigger when the resource id masked with the set<br>Mask is not equal to the Value. |

| register                                         | 0     | DRW  | 0    | When 1 the instruction breakpoint is enabled.                                                                                                                                                                                        |

-XMOS°

# C Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                                    |

|-----------|------|------------------------------------------------|

| 0x00      | RO   | Device identification                          |

| 0x01      | RO   | xCORE Tile description 1                       |

| 0x02      | RO   | xCORE Tile description 2                       |

| 0x04      | CRW  | Control PSwitch permissions to debug registers |

| 0x05      | CRW  | Cause debug interrupts                         |

| 0x06      | RW   | xCORE Tile clock divider                       |

| 0x07      | RO   | Security configuration                         |

| 0x100x13  | RO   | PLink status                                   |

| 0x200x27  | CRW  | Debug scratch                                  |

| 0x40      | RO   | PC of logical core 0                           |

| 0x41      | RO   | PC of logical core 1                           |

| 0x42      | RO   | PC of logical core 2                           |

| 0x43      | RO   | PC of logical core 3                           |

| 0x44      | RO   | PC of logical core 4                           |

| 0x45      | RO   | PC of logical core 5                           |

| 0x60      | RO   | SR of logical core 0                           |

| 0x61      | RO   | SR of logical core 1                           |

| 0x62      | RO   | SR of logical core 2                           |

| 0x63      | RO   | SR of logical core 3                           |

| 0x64      | RO   | SR of logical core 4                           |

| 0x65      | RO   | SR of logical core 5                           |

| 0x80 0x9F | RO   | Chanend status                                 |

-XMOS

Figure 29: Summary 0x04: Control PSwitch permissions to debug registers

| Bits | Perm | Init | Description                                                                                                 |

|------|------|------|-------------------------------------------------------------------------------------------------------------|

| 31:1 | RO   | -    | Reserved                                                                                                    |

| 0    | CRW  |      | Set to 1 to restrict PSwitch access to all CRW marked registers to become read-only rather than read-write. |

## C.5 Cause debug interrupts: 0x05

This register can be used to raise a debug interrupt in this xCORE tile.

**0x05:** Cause debug interrupts

| Bits | Perm | Init | Description                                             |

|------|------|------|---------------------------------------------------------|

| 31:2 | RO   | -    | Reserved                                                |

| 1    | RO   | 0    | Set to 1 when the processor is in debug mode.           |

| 0    | CRW  | 0    | Set to 1 to request a debug interrupt on the processor. |

## C.6 xCORE Tile clock divider: 0x06

This register contains the value used to divide the PLL clock to create the xCORE tile clock. The divider is enabled under control of the tile control register

0x06: xCORE Tile clock divider

| 6:  | Bits | Perm | Init | Description                           |

|-----|------|------|------|---------------------------------------|

| le. | 31:8 | RO   | -    | Reserved                              |

| er  | 7:0  | RW   |      | Value of the clock divider minus one. |

## C.7 Security configuration: 0x07

Copy of the security register as read from OTP.

0x07: Security configuration

| ty | Bits | Perm | Init | Description |

|----|------|------|------|-------------|

| on | 31:0 | RO   |      | Value.      |

## C.8 PLink status: 0x10 .. 0x13

Status of each of the four processor links; connecting the xCORE tile to the switch.

-XMOS-

| Bits  | Perm | Init | Description                                                                            |

|-------|------|------|----------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                               |

| 25:23 | RW   |      | OD: Output divider value<br>The initial value depends on pins MODE0 and MODE1.         |

| 22:21 | RO   | -    | Reserved                                                                               |

| 20:8  | RW   |      | F: Feedback multiplication ratio<br>The initial value depends on pins MODE0 and MODE1. |

| 7     | RO   | -    | Reserved                                                                               |

| 6:0   | RW   |      | R: Oscilator input divider value<br>The initial value depends on pins MODE0 and MODE1. |

0x06: PLL settings

## D.6 System switch clock divider: 0x07

Sets the ratio of the PLL clock and the switch clock.

**0x07** System switch clock divider

| 07:        | Bits  | Perm | Init | Description                                                                                            |

|------------|-------|------|------|--------------------------------------------------------------------------------------------------------|

| em         | 31:16 | RO   | -    | Reserved                                                                                               |

| ock<br>der | 15:0  | RW   | 0    | Switch clock divider. The PLL clock will be divided by this value plus one to derive the switch clock. |

## D.7 Reference clock: 0x08

Sets the ratio of the PLL clock and the reference clock used by the node.

**0x08:** Reference clock

| Bits  | Perm | Init | Description                                                                                                                       |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                                                          |

| 15:0  | RW   | 3    | Architecture reference clock divider. The PLL clock will be divided by this value plus one to derive the 100 MHz reference clock. |

## D.8 Directions 0-7: 0x0C

This register contains eight directions, for packets with a mismatch in bits 7..0 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

-XMOS-

## D.13 PLink status and network: 0x40 .. 0x43

These registers contain status information and the network number that each processor-link belongs to.

| Bits  | Perm | Init | Description                                                                                                                                                                              |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                 |

| 25:24 | RO   |      | If this link is currently routing data into the switch, this field<br>specifies the type of link that the data is routed to:<br>0: plink<br>1: external link<br>2: internal control link |

| 23:16 | RO   | 0    | If the link is routing data into the switch, this field specifies the destination link number to which all tokens are sent.                                                              |

| 15:6  | RO   | -    | Reserved                                                                                                                                                                                 |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, set for quality of service.                                                                                                           |

| 3     | RO   | -    | Reserved                                                                                                                                                                                 |

| 2     | RO   | 0    | Set to 1 if the current packet is junk and being thrown away. A packet is considered junk if, for example, it is not routable.                                                           |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                                                                                           |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch.                                                                           |

0x40 .. 0x43: PLink status and network

## D.14 Link configuration and initialization: 0x80 .. 0x87

-XMOS<sup>®</sup>

These registers contain configuration and debugging information specific to external links. The link speed and width can be set, the link can be initialized, and the link status can be monitored. The registers control links C, D, A, B, G, H, E, and F in that order.

| Bits  | Perm | Init | Description                                                                                                                                                                                         |

|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | RW   | 0    | Write '1' to this bit to enable the link, write '0' to disable it. This bit controls the muxing of ports with overlapping links.                                                                    |

| 30    | RW   | 0    | Set to 0 to operate in 2 wire mode or 1 to operate in 5 wire mode                                                                                                                                   |

| 29:28 | RO   | -    | Reserved                                                                                                                                                                                            |

| 27    | RO   | 0    | Set to 1 on error: an RX buffer overflow or illegal token encoding has been received. This bit clears on reading.                                                                                   |

| 26    | RO   | 0    | 1 if this end of the link has issued credit to allow the remote end to transmit.                                                                                                                    |

| 25    | RO   | 0    | 1 if this end of the link has credits to allow it to transmit.                                                                                                                                      |

| 24    | WO   | 0    | Set to 1 to initialize a half-duplex link. This clears this end of<br>the link's credit and issues a HELLO token; the other side of the<br>link will reply with credits. This bit is self-clearing. |

| 23    | WO   | 0    | Set to 1 to reset the receiver. The next symbol that is detected will be assumed to be the first symbol in a token. This bit is self-clearing.                                                      |

| 22    | RO   | -    | Reserved                                                                                                                                                                                            |

| 21:11 | RW   | 0    | The number of system clocks between two subsequent transi-<br>tions within a token                                                                                                                  |

| 10:0  | RW   | 0    | The number of system clocks between two subsequent transmit tokens.                                                                                                                                 |

#### 0x80 .. 0x87: Link configuration and initialization

## D.15 Static link configuration: 0xA0 .. 0xA7

These registers are used for static (ie, non-routed) links. When a link is made static, all traffic is forwarded to the designated channel end and no routing is attempted. The registers control links C, D, A, B, G, H, E, and F in that order.

|   | Bits | Perm | Init | Description                                                                                     |

|---|------|------|------|-------------------------------------------------------------------------------------------------|

|   | 31   | RW   | 0    | Enable static forwarding.                                                                       |

| : | 30:5 | RO   | -    | Reserved                                                                                        |

|   | 4:0  | RW   | 0    | The destination channel end on this node that packets received in static mode are forwarded to. |

-XMOS<sup>®</sup>

**0xA0 .. 0xA7** Static link configuration Pins MODE0 and MODE1 are set to the correct value for the chosen oscillator frequency. The MODE settings are shown in the Oscillator section, Section 6. If you have a choice between two values, choose the value with the highest multiplier ratio since that will boot faster.

#### H.5 USB ULPI Mode

This section can be skipped if you do not have an external USB PHY.

- □ If using ULPI, the ULPI signals are connected to specific ports as shown in Section E.

- □ If using ULPI, the ports that are used internally are not connected, see Section E. (Note that this limitation only applies when the ULPI is enabled, they can still be used before or after the ULPI is being used.)

#### H.6 Boot

- □ The device is connected to a SPI flash for booting, connected to X0D0, X0D01, X0D10, and X0D11 (Section 7). If not, you must boot the device through OTP or JTAG.

- □ The device that is connected to flash has both MODE2 and MODE3 connected to pin 3 on the xSYS Header (MSEL). If no debug adapter connection is supported (not recommended) MODE2 and MODE3 are to be left NC (Section 7).

- ☐ The SPI flash that you have chosen is supported by **xflash**, or you have created a specification file for it.

#### H.7 JTAG, XScope, and debugging

- $\Box$  You have decided as to whether you need an XSYS header or not (Section G)

- □ If you included an XSYS header, you connected pin 3 to any MODE2/MODE3 pin that would otherwise be NC (Section G).

- ☐ If you have not included an XSYS header, you have devised a method to program the SPI-flash or OTP (Section G).

#### H.8 GPIO

You have not mapped both inputs and outputs to the same multi-bit port.

-XM()S