Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | RS08                                                       |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 20MHz                                                      |

| Connectivity               | I²C, SPI                                                   |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 18                                                         |

| Program Memory Size        | 4KB (4K x 8)                                               |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 126 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                |

| Data Converters            | A/D 12x10b                                                 |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                             |

| Supplier Device Package    | 20-SOIC                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9rs08kb4cwj |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part Number   | Package Description | Original (gold wire) package document number | Current (copper wire) package document number |

|---------------|---------------------|----------------------------------------------|-----------------------------------------------|

| MC68HC908JW32 | 48 QFN              | 98ARH99048A                                  | 98ASA00466D                                   |

| MC9S08AC16    |                     |                                              |                                               |

| MC9S908AC60   |                     |                                              |                                               |

| MC9S08AC128   |                     |                                              |                                               |

| MC9S08AW60    |                     |                                              |                                               |

| MC9S08GB60A   |                     |                                              |                                               |

| MC9S08GT16A   |                     |                                              |                                               |

| MC9S08JM16    |                     |                                              |                                               |

| MC9S08JM60    |                     |                                              |                                               |

| MC9S08LL16    |                     |                                              |                                               |

| MC9S08QE128   |                     |                                              |                                               |

| MC9S08QE32    |                     |                                              |                                               |

| MC9S08RG60    |                     |                                              |                                               |

| MCF51CN128    |                     |                                              |                                               |

| MC9RS08LA8    | 48 QFN              | 98ARL10606D                                  | 98ASA00466D                                   |

| MC9S08GT16A   | 32 QFN              | 98ARH99035A                                  | 98ASA00473D                                   |

| MC9S908QE32   | 32 QFN              | 98ARE10566D                                  | 98ASA00473D                                   |

| MC9S908QE8    | 32 QFN              | 98ASA00071D                                  | 98ASA00736D                                   |

| MC9S08JS16    | 24 QFN              | 98ARL10608D                                  | 98ASA00734D                                   |

| MC9S08QB8     |                     |                                              |                                               |

| MC9S08QG8     | 24 QFN              | 98ARL10605D                                  | 98ASA00474D                                   |

| MC9S08SH8     | 24 QFN              | 98ARE10714D                                  | 98ASA00474D                                   |

| MC9RS08KB12   | 24 QFN              | 98ASA00087D                                  | 98ASA00602D                                   |

| MC9S08QG8     | 16 QFN              | 98ARE10614D                                  | 98ASA00671D                                   |

| MC9RS08KB12   | 8 DFN               | 98ARL10557D                                  | 98ASA00672D                                   |

| MC9S08QG8     |                     |                                              |                                               |

| MC9RS08KA2    | 6 DFN               | 98ARL10602D                                  | 98ASA00735D                                   |

# **Freescale Semiconductor**

Data Sheet: Technical Data

Document Number: MC9RS08KB12

Rev. 5, 1/2012

# **MC9RS08KB12**

# MC9RS08KB12 Series

Covers:MC9RS08KB12 MC9RS08KB8 MC9RS08KB4 MC9RS08KB2

- 8-Bit RS08 Central Processor Unit (CPU)

- Up to 20 MHz CPU at 1.8 V to 5.5 V across temperature range of –40 °C to 85 °C

- Subset of HC08 instruction set with added BGND instruction

- Single Global interrupt vector

- On-Chip Memory

- Up to 12 KB flash read/program/erase over full operating voltage and temperature,

12 KB/8 KB/4 KB/2 KB flash are optional

- Up to 254-byte random-access memory (RAM), 254-byte/126-byte RAM are optional

- Security circuitry to prevent unauthorized access to flash contents

- · Power-Saving Modes

- Wait mode CPU shuts down; system clocks continue to run; full voltage regulation

- Stop mode CPU shuts down; system clocks are stopped; voltage regulator in standby

- Wakeup from power-saving modes using RTI, KBI, ADC, ACMP, SCI and LVD

- · Clock Source Options

- Oscillator (XOSC) Loop-control Pierce oscillator; crystal or ceramic resonator range of 31.25 kHz to 39.0625 kHz or 1 MHz to 16 MHz

- Internal Clock Source (ICS) Internal clock source module containing a frequency-locked-loop (FLL) controlled by internal or external reference; precision trimming of internal reference allows 0.2% resolution and 2% deviation over temperature and voltage; supporting bus frequencies up to 10 MHz

- · System Protection

- Watchdog computer operating properly (COP) reset with option to run from dedicated 1 kHz internal low power oscillator

- Low-voltage detection with reset or interrupt

- Illegal opcode detection with reset

- Illegal address detection with reset

- Flash-block protection

20-Pin SOIC Case 751D

16-Pin TSSOP Case 948F

8-Pin DFN

Case 1452-02

24-Pin QFN Case 1982-01

16-Pin SOIC N/B Case 751B

8-Pin SOIC Case 751

- Development Support

- Single-wire background debug interface

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging

- Peripherals

- ADC 12-channel, 10-bit resolution; 2.5 μs conversion time; automatic compare function;

1.7 mV/°C temperature sensor; internal bandgap reference channel; operation in stop; hardware trigger

- ACMP Analog comparator; full rail-to-rail supply operation; option to compare to fixed internal bandgap reference voltage; can operate in stop mode

- TPM One 2-channel timer/pulse-width modulator module; selectable input capture, output compare, or buffered edge- or center-aligned PWM on each channel

- IIC Inter-integrated circuit bus module capable of operation up to 100 kbps with maximum bus loading; capable of higher baud rates with reduced loading

- SCI One serial communications interface module with optional 13-bit break; LIN extensions

- MTIM Two 8-bit modulo timers; optional clock sources

- **RTI** One real-time clock with optional clock sources

- **KBI** Keyboard interrupts; up to 8 ports

- Input/Output

- 18 GPIOs in 24- and 20-pin packages; 14 GPIOs in 16-pin package; 6 GPIOs in 8-pin package; including one output-only pin and one input-only pin

- Hysteresis and configurable pullup device on all input pins; configurable slew rate and drive strength on all output pins

- Package Options

- MC9RS08KB12/MC9RS08KB8/MC9RS08KB4

- 24-pin QFN, 20-pin SOIC, 16-pin SOIC NB or TSSOP

- MC9RS08KB2

- 8-pin SOIC or DFN

This document contains information on a product under development. Freescale reserves the right to change or discontinue this product without notice.

© Freescale Semiconductor, Inc., 2008-2012. All rights reserved.

### **Pin Assignments**

Table 1. Pin Availability by Package Pin-Count

|    | Pin Nu | umber | i |          | < Lov               | vest <b>Priority</b> | > Highest        |                 |

|----|--------|-------|---|----------|---------------------|----------------------|------------------|-----------------|

| 24 | 20     | 16    | 8 | Port Pin | Alt 1               | Alt 2                | Alt 3            | Alt 4           |

| 1  | 3      | 3     | 3 |          |                     |                      |                  | $V_{DD}$        |

| 2  | _      | _     | _ | NC       |                     |                      |                  |                 |

| 3  | 4      | 4     | 4 |          |                     |                      |                  | V <sub>SS</sub> |

| 4  | 5      | 5     | _ | PTB7     | SCL <sup>1</sup>    |                      |                  | EXTAL           |

| 5  | 6      | 6     | _ | PTB6     | SDA <sup>1</sup>    |                      |                  | XTAL            |

| 6  | 7      | 7     | _ | PTB5     | TPMCH1 <sup>2</sup> |                      |                  |                 |

| 7  | 8      | 8     | _ | PTB4     | TPMCH0 <sup>2</sup> |                      |                  |                 |

| 8  | 9      | _     | _ | PTC3     |                     |                      | ADP11            |                 |

| 9  | 10     | _     | _ | PTC2     |                     |                      | ADP10            |                 |

| 10 | 11     | _     | _ | PTC1     |                     |                      | ADP9             |                 |

| 11 | 12     | _     | _ | PTC0     |                     |                      | ADP8             |                 |

| 12 | 13     | 9     | _ | PTB3     | KBIP7               |                      | ADP7             |                 |

| 13 | 14     | 10    | _ | PTB2     | KBIP6               |                      | ADP6             |                 |

| 14 | 15     | 11    | _ | PTB1     | KBIP5               | TxD <sup>3</sup>     | ADP5             |                 |

| 15 | 16     | 12    | _ | PTB0     | KBIP4               | RxD <sup>3</sup>     | ADP4             |                 |

| 16 | 17     | 13    | 5 | PTA3     | KBIP3               | SCL <sup>1</sup>     | TxD <sup>3</sup> | ADP3            |

| 17 | 18     | 14    | 6 | PTA2     | KBIP2               | SDA <sup>1</sup>     | RxD <sup>3</sup> | ADP2            |

| 18 | 19     | 15    | 7 | PTA1     | KBIP1               | TPMCH1 <sup>2</sup>  | ADP1             | ACMP-           |

| 19 | 20     | 16    | 8 | PTA0     | KBIP0               | TPMCH0 <sup>2</sup>  | ADP0             | ACMP+           |

| 20 | _      | _     | _ | NC       |                     |                      |                  |                 |

| 21 | _      | _     | _ | NC       |                     |                      |                  |                 |

| 22 | _      | _     | _ | NC       |                     |                      |                  |                 |

| 23 | 1      | 1     | 1 | PTA5     |                     | TCLK                 | RESET            | V <sub>PP</sub> |

| 24 | 2      | 2     | 2 | PTA4     | ACMPO               | BKGD                 | MS               |                 |

IIC pins can be remapped to PTB6 and PTB7, default reset location is PTA2 and PTA3. It can be configured only once.

<sup>&</sup>lt;sup>2</sup> TPM pins can be remapped to PTB4 and PTB5, default reset location is PTA0 and PTA1.

<sup>&</sup>lt;sup>3</sup> SCI pins can be remapped to PTA2 and PTA3, default reset location is PTB0 and PTB1. It can be configured only once.

#### **Table 2. Parameter Classifications**

D Those parameters are derived mainly from simulations.

#### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 3.3 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 3 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this chapter.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance,  $V_{SS}$  or  $V_{DD}$ ) or the programmable pull-up resistor associated with the pin is enabled.

| Rating                                                                                       | Symbol           | Value                         | Unit |

|----------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage                                                                               | V <sub>DD</sub>  | -0.3 to 5.8                   | V    |

| Maximum current into V <sub>DD</sub>                                                         | I <sub>DD</sub>  | 120                           | mA   |

| Digital input voltage                                                                        | V <sub>In</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | I <sub>D</sub>   | ±25                           | mA   |

| Storage temperature range                                                                    | T <sub>stg</sub> | -55 to 150                    | °C   |

**Table 3. Absolute Maximum Ratings**

## 3.4 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of

Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

<sup>&</sup>lt;sup>2</sup> All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$  except the  $\overline{RESET}/V_{PP}$  pin which is internally clamped to  $V_{SS}$  only.

Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

**Table 4. Thermal Characteristics**

| Rating                                 | Symbol            | Value                                         | Unit |

|----------------------------------------|-------------------|-----------------------------------------------|------|

| Operating temperature range (packaged) | T <sub>A</sub>    | T <sub>L</sub> to T <sub>H</sub><br>-40 to 85 | °C   |

| Maximum junction temperature           | T <sub>JMAX</sub> | 150                                           | °C   |

| Thermal resistance 24-pin QFN          | $\theta_{JA}$     | 113                                           | °C/W |

| Thermal resistance 20-pin SOIC         | $\theta_{JA}$     | 83                                            | °C/W |

| Thermal resistance 16-pin SOIC NB      | $\theta_{JA}$     | 103                                           | °C/W |

| Thermal resistance 16-pin TSSOP        | $\theta_{JA}$     | 29                                            | °C/W |

| Thermal resistance 8-pin SOIC          | $\theta_{JA}$     | 150                                           | °C/W |

| Thermal resistance 8-pin DFN           | $\theta_{JA}$     | 110                                           | °C/W |

The average chip-junction temperature (TJ) in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

where:

$T_A = Ambient temperature, °C$

$\theta_{JA}$  = Package thermal resistance, junction-to-ambient, °C /W

$$P_D = P_{int} + P_{I/O}$$

$P_{int} = I_{DD} \times V_{DD}$ , Watts chip internal power

$P_{I/O}$  = Power dissipation on input and output pins user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between PD and TJ (if  $P_{I/O}$  is neglected) is:

$$P_D = K \div (T_J + 273^{\circ}C)$$

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (PD)^2$$

Eqn. 3

where K is a constant pertaining to the particular part. K can be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

# 3.5 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions must be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

MC9RS08KB12 Series MCU Data Sheet, Rev. 5

During the device qualification ESD stresses were performed for the human body model (HBM) and the charge device model (CDM).

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

**Table 5. ESD and Latch-Up Test Conditions**

| Model         | Description                 | Symbol | Value | Unit |

|---------------|-----------------------------|--------|-------|------|

|               | Series resistance           | R1     | 1500  | Ω    |

| Human<br>body | Storage capacitance         | С      | 100   | pF   |

|               | Number of pulses per pin    | _      | 1     |      |

| Lotob up      | Minimum input voltage limit | _      | -2.5  | V    |

| Latch-up      | Maximum input voltage limit | _      | 7.5   | V    |

Table 6. ESD and Latch-Up Protection Characteristics

| No. | Rating <sup>1</sup> Symbol Min             |                  | Min   | Max | Unit |

|-----|--------------------------------------------|------------------|-------|-----|------|

| 1   | Human body model (HBM)                     | V <sub>HBM</sub> | ±2000 | _   | V    |

| 2   | Charge device model (CDM)                  | V <sub>CDM</sub> | ±500  | _   | V    |

| 3   | Latch-up current at T <sub>A</sub> = 85 °C | I <sub>LAT</sub> | ±100  | _   | mA   |

Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

## 3.6 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

**Table 7. DC Characteristics (Temperature Range = −40 to 85°C Ambient)**

| No. | С | Parameter                                                                                                                                                                                                                                                                                   | Symbol                        | Min                   | Typical      | Max                  | Unit     |

|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------|--------------|----------------------|----------|

| 1   | _ | Supply voltage (run, wait and stop modes.)<br>0 < f <sub>Bus</sub> <10 MHz                                                                                                                                                                                                                  | V <sub>DD</sub>               | 1.8                   | _            | 5.5                  | V        |

| 2   | С | Minimum RAM retention supply voltage applied to $V_{DD}$                                                                                                                                                                                                                                    | V <sub>RAM</sub>              | 0.8 <sup>1</sup>      | _            | _                    | V        |

| 3   | Р | Low-voltage detection threshold $ (V_{DD} \text{ falling}) $ $ (V_{DD} \text{ rising}) $                                                                                                                                                                                                    | V <sub>LVD</sub>              | 1.80<br>1.88          | 1.86<br>1.94 | 1.95<br>2.05         | V        |

| 4   | С | Power on RESET (POR) voltage                                                                                                                                                                                                                                                                | V <sub>POR</sub> <sup>1</sup> | 0.9                   | _            | 1.7                  | V        |

| 5   | С | Input high voltage (V <sub>DD</sub> > 2.3V) (all digital inputs)                                                                                                                                                                                                                            | V <sub>IH</sub>               | $0.70 \times V_{DD}$  | _            | _                    | V        |

| 6   | С | Input high voltage (1.8 V $\leq$ V <sub>DD</sub> $\leq$ 2.3 V) (all digital inputs)                                                                                                                                                                                                         | V <sub>IH</sub>               | $0.85 \times V_{DD}$  | _            | _                    | V        |

| 7   | С | Input low voltage (V <sub>DD</sub> > 2.3 V) (all digital inputs)                                                                                                                                                                                                                            | V <sub>IL</sub>               | _                     | _            | $0.30 \times V_{DD}$ | V        |

| 8   | С | Input low voltage (1.8 V $\leq$ V <sub>DD</sub> $\leq$ 2.3 V) (all digital inputs)                                                                                                                                                                                                          | V <sub>IL</sub>               | _                     | _            | $0.30 \times V_{DD}$ | V        |

| 9   | С | Input hysteresis (all digital inputs)                                                                                                                                                                                                                                                       | V <sub>hys</sub> <sup>1</sup> | $0.06 \times V_{DD}$  | _            | _                    | V        |

| 10  | Р | Input leakage current (per pin) V <sub>In</sub> = V <sub>DD</sub> or V <sub>SS</sub> , all input only pins                                                                                                                                                                                  | IIn                           | _                     | 0.025        | 1.0                  | μА       |

| 11  | Р | High impedance (off-state) leakage current (per pin) $V_{ln} = V_{DD}$ or $V_{SS}$ , all input/output                                                                                                                                                                                       | llozl                         | _                     | 0.025        | 1.0                  | μА       |

| 12  | Р | Internal pullup resistors <sup>2</sup> (all port pins)                                                                                                                                                                                                                                      | R <sub>PU</sub>               | 20                    | 45           | 65                   | kΩ       |

| 13  | Р | Internal pulldown resistors <sup>2</sup> (all port pins)                                                                                                                                                                                                                                    | R <sub>PD</sub>               | 20                    | 45           | 65                   | kΩ       |

| 14  |   | Output high voltage — Low drive (PTxDSn = 0)  5 V, I <sub>Load</sub> = 2 mA  3 V, I <sub>Load</sub> = 1 mA  1.8 V, I <sub>Load</sub> = 0.5 mA  Output high voltage — High drive (PTxDSn = 1)  5 V, I <sub>Load</sub> = 5 mA  3 V, I <sub>Load</sub> = 3 mA  1.8 V, I <sub>Load</sub> = 2 mA | V                             | V <sub>DD</sub> – 0.8 |              |                      | V        |

| 14  |   |                                                                                                                                                                                                                                                                                             | V <sub>OH</sub>               | V <sub>DD</sub> – 0.8 | _<br>_<br>   | _<br>_<br>_          | <b>v</b> |

| 15  | С | Maximum total IOH for all port pins                                                                                                                                                                                                                                                         | I <sub>OHT</sub>              | _                     | _            | 40                   | mA       |

### MC9RS08KB12 Series MCU Data Sheet, Rev. 5

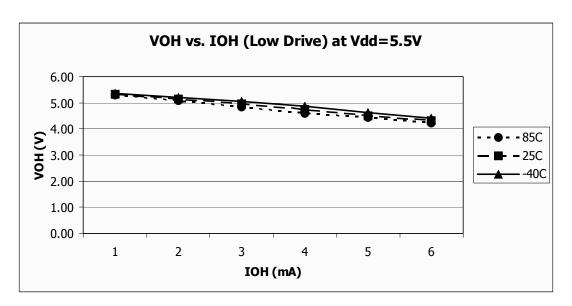

Figure 7. Typical V<sub>OH</sub> vs. I<sub>OH</sub> V<sub>DD</sub> = 5.5 V (Low Drive)

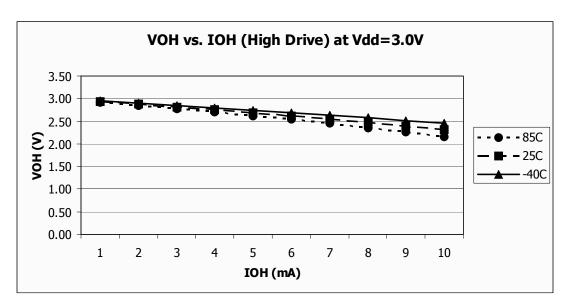

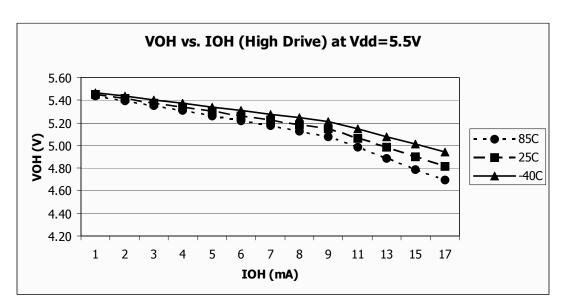

Figure 8. Typical  $V_{OH}$  vs.  $I_{OH}$   $V_{DD}$  = 3.0 V (High Drive)

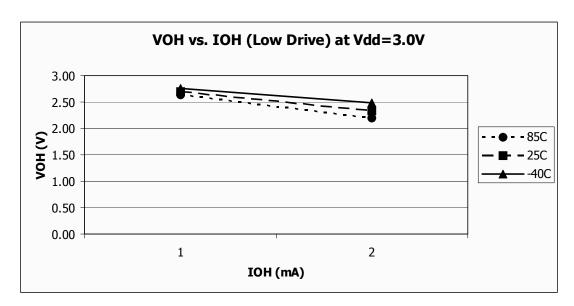

Figure 9. Typical  $V_{OH}$  vs.  $I_{OH}$   $V_{DD} = 3.0 \text{ V (Low Drive)}$

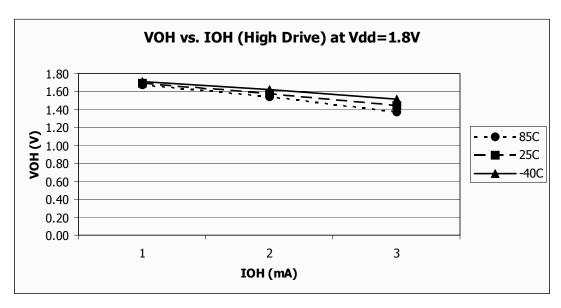

Figure 10. Typical  $V_{OH}$  vs.  $I_{OH}$   $V_{DD}$  = 1.8 V (High Drive)

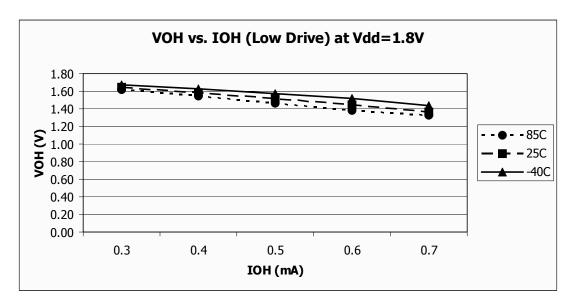

Figure 11. Typical  $V_{OH}$  vs.  $I_{OH}$   $V_{DD}$  = 1.8 V (Low Drive)

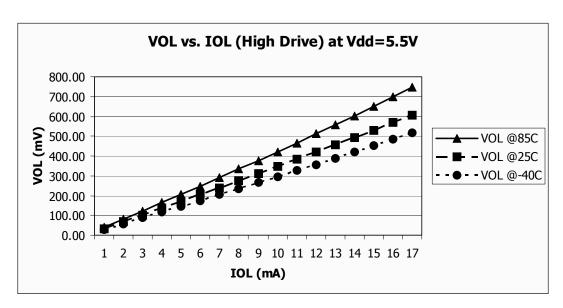

Figure 12. Typical  $V_{OL}$  vs.  $I_{OL}$   $V_{DD}$  = 5.5 V (High Drive)

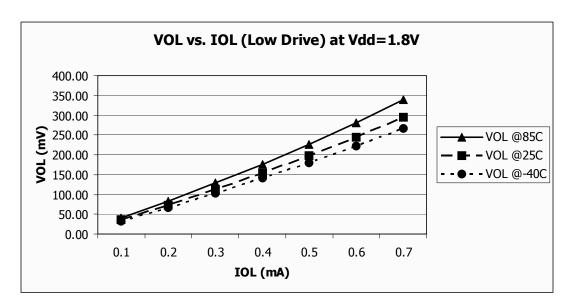

Figure 17. Typical  $V_{OL}$  vs.  $I_{OL}$  $V_{DD} = 1.8 \text{ V (Low Drive)}$

Figure 18. Typical  $I_{OH}$  vs.  $V_{DD}-V_{OH}$   $V_{DD}$  = 5.5 V (High Drive)

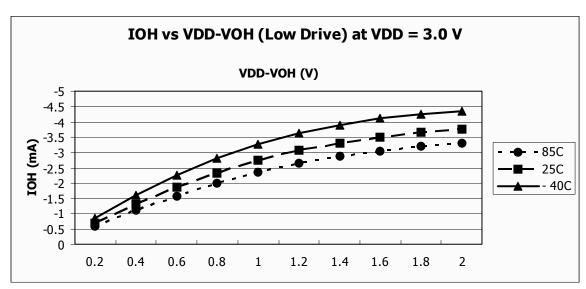

Figure 21. Typical  $I_{OH}$  vs.  $V_{DD}-V_{OH}$  $V_{DD}$  = 3 V (Low Drive)

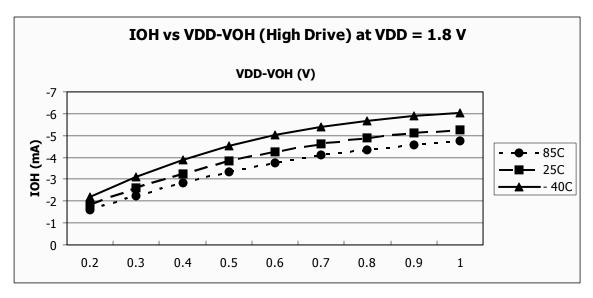

Figure 22. Typical  $I_{OH}$  vs.  $V_{DD}-V_{OH}$   $V_{DD}$  = 1.8 V (High Drive)

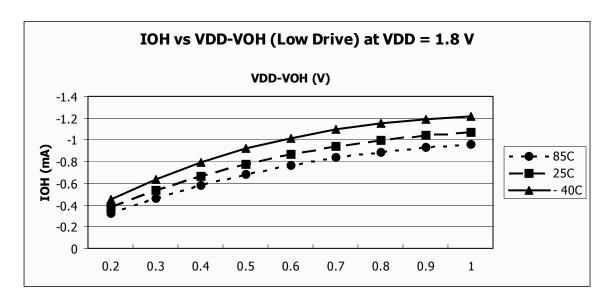

Figure 23. Typical  $I_{OH}$  vs.  $V_{DD}$ – $V_{OH}$   $V_{DD}$  = 1.8 V (Low Drive)

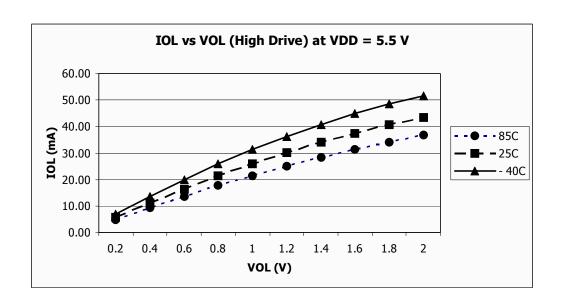

Figure 24. Typical  $I_{OL}$  vs.  $V_{OL}$  $V_{DD}$  = 5.5 V (High Drive)

# 3.9.1 Control Timing

**Table 10. Control Timing**

| Num | С | Parameter                                                                                                                        | Symbol                                | Min                  | Typical  | Max  | Unit |

|-----|---|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|----------|------|------|

| 1   | D | Bus frequency (t <sub>cyc</sub> = 1/f <sub>Bus</sub> )                                                                           | f <sub>Bus</sub>                      | 0                    | _        | 10   | MHz  |

| 2   | D | Real time interrupt internal oscillator period                                                                                   | t <sub>RTI</sub>                      | 700                  | 1000     | 1300 | μS   |

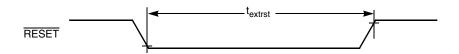

| 3   | D | External RESET pulse width <sup>1</sup>                                                                                          | t <sub>extrst</sub>                   | 150                  | _        | _    | ns   |

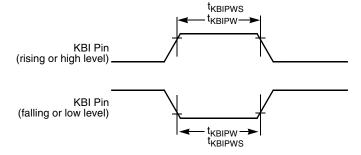

| 4   | D | KBI pulse width <sup>2</sup>                                                                                                     | t <sub>KBIPW</sub>                    | 1.5 t <sub>cyc</sub> | _        | _    | ns   |

| 5   | D | KBI pulse width in stop <sup>1</sup>                                                                                             | t <sub>KBIPWS</sub>                   | 100                  | _        | _    | ns   |

| 6   | D | Port rise and fall time (load = 50 pF) <sup>3</sup> Slew rate control disabled (PTxSE = 0) Slew rate control enabled (PTxSE = 1) | t <sub>Rise</sub> , t <sub>Fall</sub> | _                    | 11<br>35 |      | ns   |

<sup>1</sup> This is the shortest pulse guaranteed to pass through the pin input filter circuitry. Shorter pulses may or may not be recognized.

$<sup>^3</sup>$  Timing is shown with respect to 20%  $\rm V_{DD}$  and 80%  $\rm V_{DD}$  levels. Temperature range –40  $^{\circ}C$  to 85  $^{\circ}C$ .

Figure 30. Reset Timing

Figure 31. KBI Pulse Width

<sup>&</sup>lt;sup>2</sup> This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

# 3.9.2 TPM/MTIM Module Timing

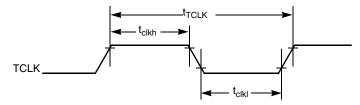

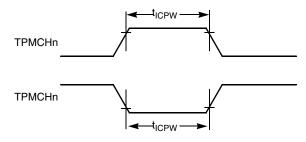

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that can be used as the optional external source to the timer counter. These synchronizers operate from the current bus rate clock.

| Num | С | Rating                    | Symbol              | Min | Max                 | Unit             |

|-----|---|---------------------------|---------------------|-----|---------------------|------------------|

| 1   | D | External clock frequency  | f <sub>TPMext</sub> | DC  | f <sub>Bus</sub> /4 | MHz              |

| 2   | D | External clock period     | t <sub>TPMext</sub> | 4   | _                   | t <sub>cyc</sub> |

| 3   | D | External clock high time  | t <sub>clkh</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| 4   | D | External clock low time   | t <sub>clkl</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

| 5   | D | Input capture pulse width | t <sub>ICPW</sub>   | 1.5 | _                   | t <sub>cyc</sub> |

**Table 11. TPM Input Timing**

Figure 32. Timer External Clock

Figure 33. Timer Input Capture Pulse

# 3.10 Analog Comparator (ACMP) Electrical

**Table 12. Analog Comparator Electrical Specifications**

| Num | С | Characteristic                            | Symbol             | Min                   | Typical | Max      | Unit |

|-----|---|-------------------------------------------|--------------------|-----------------------|---------|----------|------|

| 1   | D | Supply voltage                            | $V_{DD}$           | 1.80                  |         | 5.5      | V    |

| 2   | Р | Supply current (active)                   | I <sub>DDAC</sub>  | _                     | 20      | 35       | μΑ   |

| 3   | D | Analog input voltage <sup>1</sup>         | V <sub>AIN</sub>   | V <sub>SS</sub> – 0.3 | _       | $V_{DD}$ | V    |

| 4   | С | Analog input offset voltage <sup>1</sup>  | $V_{AIO}$          | _                     | 20      | 40       | mV   |

| 5   | С | Analog Comparator hysteresis <sup>1</sup> | $V_{H}$            | 3.0                   | 9.0     | 15.0     | mV   |

| 6   | С | Analog source impedance <sup>1</sup>      | R <sub>AS</sub>    | _                     | _       | 10       | kΩ   |

| 7   | Р | Analog input leakage current              | I <sub>ALKG</sub>  | _                     | _       | 1.0      | μΑ   |

| 8   | С | Analog Comparator initialization delay    | t <sub>AINIT</sub> | 1                     | _       | 1.0      | μS   |

MC9RS08KB12 Series MCU Data Sheet, Rev. 5

Table 14. 10-Bit ADC Operating Conditions (continued)

| Characteristic         | Conditions           | Symb              | Min | Typ <sup>1</sup> | Max | Unit | Comment |

|------------------------|----------------------|-------------------|-----|------------------|-----|------|---------|

| ADC                    | High speed (ADLPC=0) | f <sub>ADCK</sub> | 0.4 | _                | 8.0 | MHz  |         |

| conversion clock Freq. | Low power (ADLPC=1)  |                   | 0.4 | _                | 4.0 |      |         |

Typical values assume  $V_{DDAD}$  = 5.0 V, Temp = 25 °C,  $f_{ADCK}$  = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

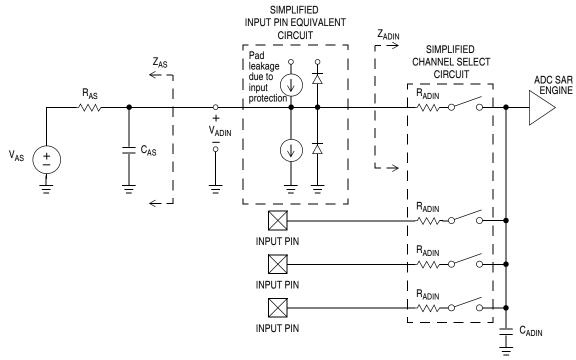

Figure 34. ADC Input Impedance Equivalency Diagram

Table 15. 10-Bit ADC Characteristics (V<sub>REFH</sub> = V<sub>DDAD</sub>, V<sub>REFL</sub> = V<sub>SSAD</sub>, 2.7 V < V<sub>DDAD</sub> < 5.5 V)

| С | Characteristic                                        | Conditions | Symb              | Min | Typ <sup>1</sup> | Max | Unit | Comment |

|---|-------------------------------------------------------|------------|-------------------|-----|------------------|-----|------|---------|

| Т | Supply Current<br>ADLPC = 1<br>ADLSMP = 1<br>ADCO = 1 |            | I <sub>DDAD</sub> | _   | 133              |     | μА   |         |

| Т | Supply Current<br>ADLPC = 1<br>ADLSMP = 0<br>ADCO = 1 |            | I <sub>DDAD</sub> | _   | 218              | _   | μΑ   |         |

| Т | Supply Current<br>ADLPC = 0<br>ADLSMP = 1<br>ADCO = 1 |            | I <sub>DDAD</sub> | _   | 327              | _   | μΑ   |         |

### MC9RS08KB12 Series MCU Data Sheet, Rev. 5

Table 15. 10-Bit ADC Characteristics ( $V_{REFH} = V_{DDAD}$ ,  $V_{REFL} = V_{SSAD}$ , 2.7 V <  $V_{DDAD}$  < 5.5 V)

| С | Characteristic                                        | Conditions                | Symb               | Min        | Typ <sup>1</sup> | Max       | Unit             | Comment                              |

|---|-------------------------------------------------------|---------------------------|--------------------|------------|------------------|-----------|------------------|--------------------------------------|

| С | Supply Current<br>ADLPC = 0<br>ADLSMP = 0<br>ADCO = 1 |                           | I <sub>DDAD</sub>  | _          | 0.582            | 1         | mA               |                                      |

| С | ADC                                                   | High Speed (ADLPC = 0)    | f <sub>ADACK</sub> | 2          | 3.3              | 5         | MHz              | t <sub>ADACK</sub> =                 |

|   | Asynchronous<br>Clock Source                          | Low Power (ADLPC = 1)     |                    | 1.25       | 2                | 3.3       |                  | 1/f <sub>ADACK</sub>                 |

| D | Conversion                                            | Short Sample (ADLSMP = 0) | t <sub>ADC</sub>   | _          | 20               | _         | ADCK             | See reference                        |

|   | Time (Including sample time)                          | Long Sample (ADLSMP = 1)  |                    | _          | 40               | _         | cycles           | manual for conversion                |

|   | Sample Time                                           | Short Sample (ADLSMP = 0) | t <sub>ADS</sub>   | _          | 3.5              | _         | ADCK             | time variances                       |

| D |                                                       | Long Sample (ADLSMP = 1)  |                    | _          | 23.5             | _         | cycles           |                                      |

| С | Total                                                 | 10-bit mode               | E <sub>TUE</sub>   | _          | ±1.5             | ±3.5      | LSB <sup>2</sup> | Includes                             |

|   | Unadjusted<br>Error                                   | 8-bit mode                |                    | _          | ±0.7             | ±1.5      |                  | quantization                         |

| Т | Differential                                          | 10-bit mode               | DNL                | _          | ±0.5             | ±1.0      | LSB <sup>2</sup> |                                      |

|   | Non-Linearity                                         | 8-bit mode                |                    | _          | ±0.3             | ±0.5      |                  |                                      |

|   |                                                       | Mon                       | otonicity and      | d No-Missi | ng-Codes (       | guarantee | d                |                                      |

| С | Integral                                              | 10-bit mode               | INL                | _          | ±0.5             | ±1.0      | LSB <sup>2</sup> |                                      |

|   | Non-Linearity                                         | 8-bit mode                |                    | _          | ±0.3             | ±0.5      |                  |                                      |

| Р | Zero-Scale                                            | 10-bit mode               | E <sub>ZS</sub>    | _          | ±1.5             | ±2.5      | LSB <sup>2</sup> | V <sub>ADIN</sub> = V <sub>SSA</sub> |

|   | Error                                                 | 8-bit mode                |                    | _          | ±0.5             | ±0.7      |                  |                                      |

| Р | Full-Scale Error                                      | 10-bit mode               | E <sub>FS</sub>    | _          | ±1               | ±1.5      | LSB <sup>2</sup> | $V_{ADIN} = V_{DDA}$                 |

|   |                                                       | 8-bit mode                |                    | _          | ±0.5             | ±0.5      |                  |                                      |

| D | Quantization                                          | 10-bit mode               | EQ                 | _          | _                | ±0.5      | LSB <sup>2</sup> |                                      |

|   | Error                                                 | 8-bit mode                |                    | _          | _                | ±0.5      |                  |                                      |

| D | Input Leakage<br>Error                                | 10-bit mode               | E <sub>IL</sub>    | _          | ±0.2             | ±2.5      | LSB <sup>2</sup> | Pad leakage <sup>2</sup> *           |

|   |                                                       | 8-bit mode                |                    | _          | ±0.1             | ±1        |                  | R <sub>AS</sub>                      |

Typical values assume V<sub>DDAD</sub> = 5.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>&</sup>lt;sup>2</sup> Based on input pad leakage current. Refer to pad electricals.

Table 16. 10-Bit ADC Characteristics ( $V_{REFH} = V_{DDAD}, V_{REFL} = V_{SSAD}, 1.8 \text{ V} < V_{DDAD} < 2.7 \text{ V}$ )

| С | Characteristic                                        | Conditions                | Symb               | Min        | Typ <sup>1</sup> | Max       | Unit             | Comment                                   |

|---|-------------------------------------------------------|---------------------------|--------------------|------------|------------------|-----------|------------------|-------------------------------------------|

| Т | Supply Current<br>ADLPC = 1<br>ADLSMP = 1<br>ADCO = 1 | 8-bit mode                | I <sub>DDAD</sub>  | _          | 88               | _         | μА               |                                           |

| Т | Supply Current<br>ADLPC = 1<br>ADLSMP = 0<br>ADCO = 1 | 8-bit mode                | I <sub>DDAD</sub>  | _          | 152              | _         | μА               |                                           |

| Т | Supply Current<br>ADLPC = 0<br>ADLSMP = 1<br>ADCO = 1 | 8-bit mode                | I <sub>DDAD</sub>  | _          | 214              | _         | μА               |                                           |

| Т | Supply Current<br>ADLPC = 0<br>ADLSMP = 0<br>ADCO = 1 | 8-bit mode                | I <sub>DDAD</sub>  | _          | 390              | _         | μА               |                                           |

| С | ADC<br>Asynchronous<br>Clock Source                   | High Speed (ADLPC = 0)    | f <sub>ADACK</sub> | 2          | 3.3              | 5         | MHz              | t <sub>ADACK</sub> =                      |

|   |                                                       | Low Power (ADLPC = 1)     |                    | 1.25       | 2                | 3.3       |                  | 1/f <sub>ADACK</sub>                      |

| D | Conversion<br>Time (Including<br>sample time)         | Short Sample (ADLSMP = 0) | t <sub>ADC</sub>   | _          | 20               | _         | ADCK<br>cycles   | See reference<br>manual for<br>conversion |

|   |                                                       | Long Sample (ADLSMP = 1)  |                    | _          | 40               | _         |                  |                                           |

|   | Sample Time                                           | Short Sample (ADLSMP = 0) | t <sub>ADS</sub>   | _          | 3.5              | _         | ADCK             | time variances                            |

| D |                                                       | Long Sample (ADLSMP = 1)  |                    | _          | 23.5             | _         | cycles           |                                           |

| С | Total<br>Unadjusted<br>Error                          | 10-bit mode               | E <sub>TUE</sub>   | _          | _                | _         | LSB <sup>2</sup> | Includes                                  |

|   |                                                       | 8-bit mode                |                    | _          | ±3.5             | _         |                  | quantization                              |

| Т | Differential                                          | 10-bit mode               | DNL                | _          | _                | _         | LSB <sup>2</sup> |                                           |

|   | Non-Linearity                                         | 8-bit mode                |                    | _          | ±1.0             | _         |                  |                                           |

|   |                                                       | Mon                       | otonicity and      | d No-Missi | ng-Codes (       | guarantee | d                | •                                         |

| С | Integral                                              | 10-bit mode               | INL                | _          | _                | _         | LSB <sup>2</sup> |                                           |

|   | Non-Linearity                                         | 8-bit mode                |                    | _          | ±1.5             | _         |                  |                                           |

| С | Zero-Scale<br>Error                                   | 10-bit mode               | E <sub>ZS</sub>    | _          | _                | _         | LSB <sup>2</sup> | $V_{ADIN} = V_{SSA}$                      |

|   |                                                       | 8-bit mode                |                    | _          | ±1.5             | _         |                  |                                           |

| С | Full-Scale Error                                      | 10-bit mode               | E <sub>FS</sub>    |            | _                | _         | LSB <sup>2</sup> | $V_{ADIN} = V_{DDA}$                      |

|   |                                                       | 8-bit mode                |                    |            | ±1.0             | _         |                  |                                           |

| D | Quantization<br>Error                                 | 10-bit mode               | EQ                 | _          | _                | _         | LSB <sup>2</sup> |                                           |

|   |                                                       | 8-bit mode                |                    | _          | _                | ±0.5      |                  |                                           |

## MC9RS08KB12 Series MCU Data Sheet, Rev. 5

Table 16. 10-Bit ADC Characteristics (V<sub>REFH</sub> = V<sub>DDAD</sub>, V<sub>REFL</sub> = V<sub>SSAD</sub>, 1.8 V < V<sub>DDAD</sub> < 2.7 V)

| С | Characteristic | Conditions  | Symb            | Min | Typ <sup>1</sup> | Max | Unit             | Comment                    |

|---|----------------|-------------|-----------------|-----|------------------|-----|------------------|----------------------------|

| D | Input Leakage  | 10-bit mode | E <sub>IL</sub> | _   | _                | _   | LSB <sup>2</sup> | Pad leakage <sup>2</sup> * |

|   | Error          | 8-bit mode  |                 | _   | ±0.1             | ±1  |                  | R <sub>AS</sub>            |

Typical values assume  $V_{DDAD} = 1.8 \text{ V}$ , Temp = 25 °C,  $f_{ADCK} = 1.0 \text{ MHz}$  unless otherwise stated. Typical values are for reference only and are not tested in production.

# 3.13 Flash Specifications

This section provides details about program/erase times and program-erase endurance for the flash memory. For detailed information about program/erase operations, see the reference manual.

**Table 17. Flash Characteristics**

| No. | С | Characteristic                                                  | Symbol                                          | Min  | Typical <sup>1</sup> | Max        | Unit                     |

|-----|---|-----------------------------------------------------------------|-------------------------------------------------|------|----------------------|------------|--------------------------|

| 1   | D | Supply voltage for program/erase                                | V <sub>DD</sub>                                 | 2.7  | _                    | 5.5        | V                        |

| 2   | D | Program/Erase voltage                                           | V <sub>PP</sub>                                 | 11.8 | 12                   | 12.2       | V                        |

| 3   | С | VPP current<br>Program<br>Mass erase                            | I <sub>VPP_prog</sub><br>I <sub>VPP_erase</sub> | _    |                      | 200<br>100 | μ <b>Α</b><br>μ <b>Α</b> |

| 4   | D | Supply voltage for read operation 0 < fBus < 10 MHz             | V <sub>Read</sub>                               | 1.8  | _                    | 5.5        | V                        |

| 5   | Р | Byte program time                                               | t <sub>prog</sub>                               | 20   | _                    | 40         | μS                       |

| 6   | Р | Mass erase time                                                 | t <sub>me</sub>                                 | 500  |                      | _          | ms                       |

| 7   | С | Cumulative program HV time <sup>2</sup>                         | t <sub>hv</sub>                                 | _    | _                    | 8          | ms                       |

| 8   | С | Total cumulative HV time (total of tme & thy applied to device) | t <sub>hv_total</sub>                           | _    | _                    | 2          | hours                    |

| 9   | D | HVEN to program setup time                                      | t <sub>pgs</sub>                                | 10   | _                    | _          | μS                       |

| 10  | D | PGM/MASS to HVEN setup time                                     | t <sub>nvs</sub>                                | 5    | _                    | _          | μS                       |

| 11  | D | HVEN hold time for PGM                                          | t <sub>nvh</sub>                                | 5    | _                    | _          | μS                       |

| 12  | D | HVEN hold time for MASS                                         | t <sub>nvh1</sub>                               | 100  | _                    | _          | μS                       |

| 13  | D | V <sub>PP</sub> to PGM/MASS setup time                          | t <sub>vps</sub>                                | 20   | _                    | _          | ns                       |

| 14  | D | HVEN to V <sub>PP</sub> hold time                               | t <sub>vph</sub>                                | 20   | _                    | _          | ns                       |

| 15  | D | V <sub>PP</sub> rise time <sup>3</sup>                          | t <sub>vrs</sub>                                | 200  | _                    | _          | ns                       |

| 16  | D | Recovery time                                                   | t <sub>rcv</sub>                                | 1    | _                    | _          | μS                       |

| 17  | D | Program/erase endurance TL to TH = -40 °C to 85 °C              | _                                               | 1000 | _                    | _          | cycles                   |

| 18  | С | Data retention                                                  | t <sub>D_ret</sub>                              | 15   | _                    | _          | years                    |

Typicals are measured at 25 °C.

<sup>&</sup>lt;sup>2</sup> Based on input pad leakage current. Refer to pad electricals.

t<sub>hv</sub> is the cumulative high voltage programming time to the same row before next erase. Same address can not be programmed more than twice before next erase.

<sup>&</sup>lt;sup>3</sup> Fast V<sub>PP</sub> rise time may potentially trigger the ESD protection structure, which may result in over current flowing into the pad and cause permanent damage to the pad. External filtering for the V<sub>PP</sub> power source is recommended. An example V<sub>PP</sub> filter is shown in Figure 35.

### 3.14 EMC Performance

Electromagnetic compatibility (EMC) performance is highly dependant on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation all play a significant role in EMC performance. The system designer should consult Freescale applications notes such as AN2321, AN1050, AN1263, AN2764, and AN1259 for advice and guidance specifically targeted at optimizing EMC performance.

## 3.14.1 Radiated Emissions

Microcontroller radiated RF emissions are measured from 150 kHz to 1 GHz using the TEM/GTEM Cell method in accordance with the IEC 61967-2 and SAE J1752/3 standards. The measurement is performed with the microcontroller installed on a custom EMC evaluation board while running specialized EMC test software. The radiated emissions from the microcontroller are measured in a TEM cell in two package orientations (North and East).