Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | F <sup>2</sup> MC-8FX                                                          |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 16MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SIO, UART/USART                                              |

| Peripherals                | LCD, POR, PWM, WDT                                                             |

| Number of I/O              | 74                                                                             |

| Program Memory Size        | 60KB (60K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1.98K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x8/10b                                                                    |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-LQFP                                                                        |

| Supplier Device Package    | 80-LQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f418hpmc-g-sne2 |

Low-voltage detection reset circuit

Built-in low-voltage detector

Clock supervisor counter

Built-in clock supervisor counter function

Programmable port input voltage level

CMOS input level / hysteresis input level

# **Dual operation Flash memory**

The program/erase operation and the read operation can be executed in different banks (upper bank/lower bank) simultaneously.

# Flash memory security function

Protects the content of the Flash memory

Document Number: 002-07475 Rev. \*A Page 2 of 85

# 4. Differences among Products and Notes on Product Selection

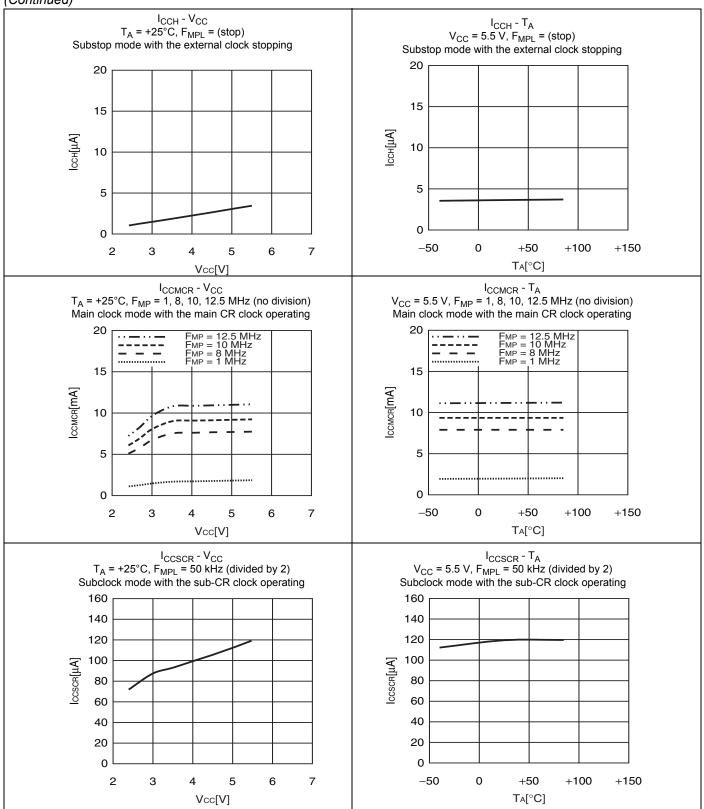

## **Current consumption**

When using the on-chip debug function, take account of the current consumption of flash erase/write.

For details of current consumption, see "17. Electrical Characteristics".

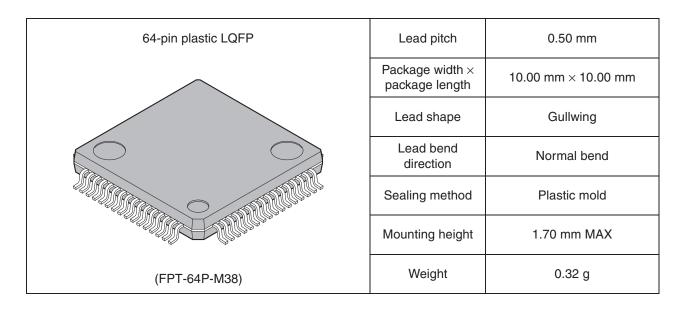

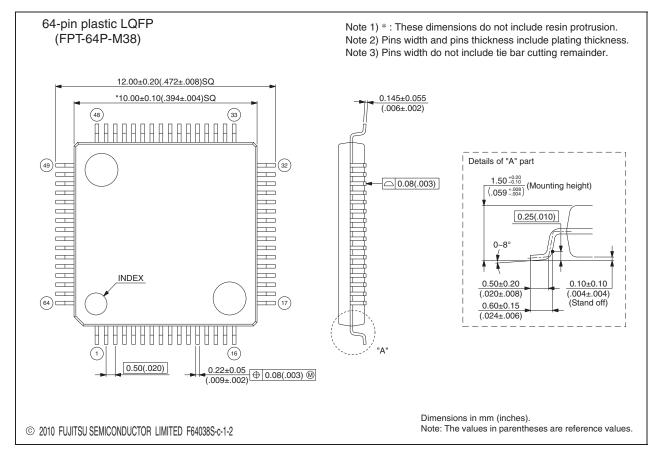

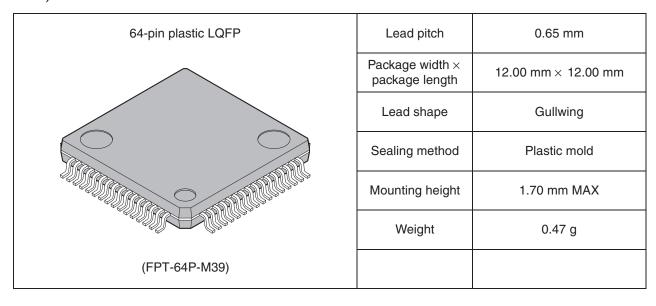

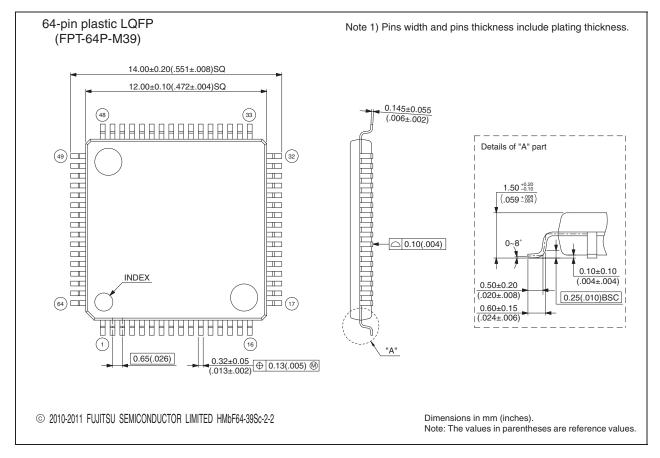

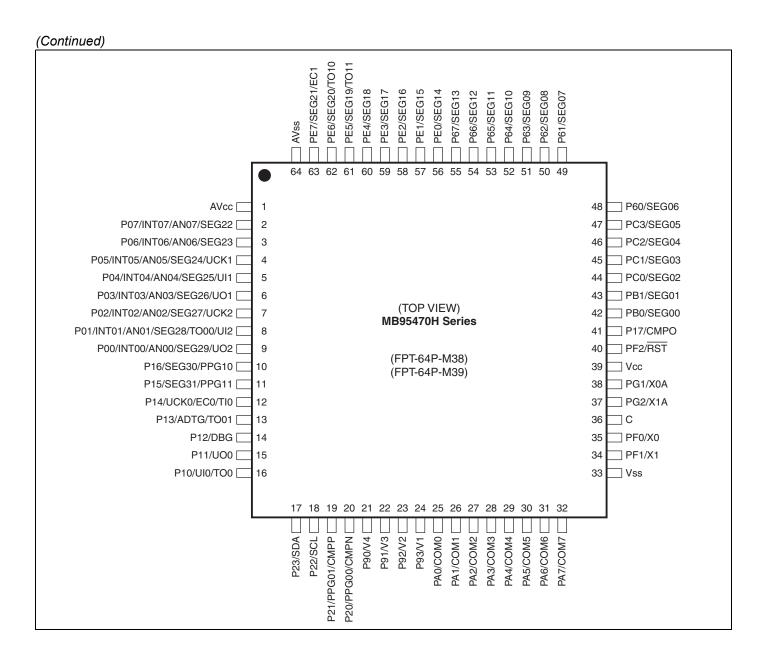

#### **Package**

For details of information on each package, see "3. Packages And Corresponding Products" and "21. Package Dimension".

## Operating voltage

The operating voltage varies, depending on whether the on-chip debug function is used or not.

For details of the operating voltage, see "17. Electrical Characteristics".

#### On-chip debug function

The on-chip debug function requires that  $V_{CC}$ ,  $V_{SS}$  and 1 serial-wire be connected to an evaluation tool. For details of the connection method, refer to "Chapter 31 Example Of Serial Programming Connection" in the hardware manual of the MB95410H/470H Series.

Document Number: 002-07475 Rev. \*A Page 9 of 85

| Pin no. | Pin name | I/O circuit type* | Function                                       |  |  |  |

|---------|----------|-------------------|------------------------------------------------|--|--|--|

|         | P00      |                   | General-purpose I/O port                       |  |  |  |

| 0       | INT00    | W                 | External interrupt input pin                   |  |  |  |

| 9       | AN00     | VV                | A/D analog input pin                           |  |  |  |

|         | UO2      |                   | UART/SIO ch. 2 data output pin                 |  |  |  |

| 10      | P16      | Y                 | General-purpose I/O port                       |  |  |  |

| 10      | PPG10    | Ť                 | 8/16-bit PPG ch. 1 output pin                  |  |  |  |

| 11      | P15      | Y                 | General-purpose I/O port                       |  |  |  |

| 11      | PPG11    | Ť                 | 8/16-bit PPG ch. 1 output pin                  |  |  |  |

| 12      | P14      | Н                 | General-purpose I/O port                       |  |  |  |

| 12      | UCK0     | П                 | UART/SIO ch. 0 clock I/O pin                   |  |  |  |

| 13      | P13      | Ш                 | General-purpose I/O port                       |  |  |  |

| 13      | ADTG     | Н                 | A/D trigger input (ADTG) pin                   |  |  |  |

| 1.1     | P12      | D                 | General-purpose I/O port                       |  |  |  |

| 14      | DBG      | D                 | DBG input pin                                  |  |  |  |

| 15      | P11      | Н                 | General-purpose I/O port                       |  |  |  |

| 15      | UO0      | П                 | UART/SIO ch. 0 data output pin                 |  |  |  |

| 16      | P10      | G                 | General-purpose I/O port                       |  |  |  |

| 10      | UI0      | G                 | UART/SIO ch. 0 data input pin                  |  |  |  |

| 17      | P53      | Н                 | General-purpose I/O port                       |  |  |  |

| 17      | TO0      | П                 | 16-bit reload timer output pin                 |  |  |  |

|         | P52      |                   | General-purpose I/O port                       |  |  |  |

| 18      | TI0      | Н                 | 16-bit reload timer input pin                  |  |  |  |

|         | TO00     |                   | 8/16-bit composite timer ch. 0 output pin      |  |  |  |

| 19      | P51      | Н                 | General-purpose I/O port                       |  |  |  |

| 19      | EC0      | П                 | 8/16-bit composite timer ch. 0 clock input pin |  |  |  |

| 20      | P50      | Н                 | General-purpose I/O port                       |  |  |  |

| 20      | TO01     | П                 | 8/16-bit composite timer ch. 0 output pin      |  |  |  |

| 21      | P23      | 1                 | General-purpose I/O port                       |  |  |  |

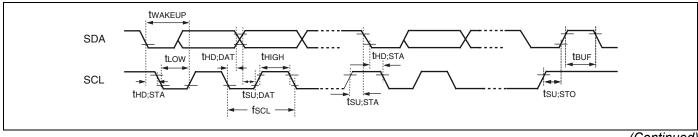

| 21      | SDA      | '                 | I <sup>2</sup> C data I/O pin                  |  |  |  |

| 22      | P22      | 1                 | General-purpose I/O port                       |  |  |  |

| 22      | SCL      | I                 | I <sup>2</sup> C clock I/O pin                 |  |  |  |

|         | P21      |                   | General-purpose I/O port                       |  |  |  |

| 23      | PPG01    | Т                 | 8/16-bit PPG ch. 0 output pin                  |  |  |  |

|         | CMPP     |                   | Voltage comparator input pin                   |  |  |  |

|         | P20      |                   | General-purpose I/O port                       |  |  |  |

| 24      | PPG00    | Т                 | 8/16-bit PPG ch. 0 output pin                  |  |  |  |

|         | CMPN     |                   | Voltage comparator input pin                   |  |  |  |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pin no.    | Pin name        | I/O circuit type* | Function                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|-------------------|-----------------------------------|

| Subclock oscillation pin (32 kHz)                                                                                                                                                                                                                                                                                                                                                                                                                  | 44         | С               | _                 | Capacitor connection pin          |

| X1A                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45         | PG2             | C                 | General-purpose I/O port          |

| ACO   Subclock oscillation pin (32 kHz)                                                                                                                                                                                                                                                                                                                                                                                                            | 45         | X1A             |                   | Subclock oscillation pin (32 kHz) |

| Subclock oscillation pin (32 kHz)                                                                                                                                                                                                                                                                                                                                                                                                                  | 46         | PG1             |                   | General-purpose I/O port          |

| PF2                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40         | X0A             |                   | Subclock oscillation pin (32 kHz) |

| RST                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47         | V <sub>CC</sub> | _                 | Power supply pin                  |

| RST                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | PF2             |                   | General-purpose I/O port          |

| CMPO                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48         | RST             | А                 |                                   |

| CMPO                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40         | P17             | ш                 | General-purpose I/O port          |

| SEG00   M                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49         | CMPO            |                   | Voltage comparator output pin     |

| SEG00   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                        | 50         | PB0             | N.4               | General-purpose I/O port          |

| SEG01                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50         | SEG00           | IVI               | LCDC SEG output pin               |

| SEG01   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>5</b> 1 | PB1             | N4                | General-purpose I/O port          |

| SEG02   M   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                    | 51         | SEG01           | IVI               | LCDC SEG output pin               |

| SEG02   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                        | F2         | PC0             | N.4               | General-purpose I/O port          |

| SEG03   M   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                    | 52         | SEG02           | IVI               | LCDC SEG output pin               |

| SEG03   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                        | 52         | PC1             | M                 | General-purpose I/O port          |

| SEG04   SEG04   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                | 33         | SEG03           | IVI               | LCDC SEG output pin               |

| SEG04   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.1        | PC2             | M                 | General-purpose I/O port          |

| SEG05   M   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                    | 54         | SEG04           | IVI               | LCDC SEG output pin               |

| SEG05   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                        | 55         | PC3             | M                 | General-purpose I/O port          |

| SEG06   M                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33         | SEG05           | IVI               | LCDC SEG output pin               |

| SEG06                                                                                                                                                                                                                                                                                                                                                                                                                                              | 56         | PC4             | M                 | General-purpose I/O port          |

| SEG07   M   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                    | 30         | SEG06           | IVI               | LCDC SEG output pin               |

| SEG07                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57         | PC5             | M                 | General-purpose I/O port          |

| 58         SEG08         M         LCDC SEG output pin           59         PC7         M         General-purpose I/O port           LCDC SEG output pin         LCDC SEG output pin           60         SEG10         M         General-purpose I/O port           LCDC SEG output pin         General-purpose I/O port           BEG11         M         General-purpose I/O port           CDC SEG output pin         General-purpose I/O port | 37         | SEG07           | IVI               | LCDC SEG output pin               |

| SEG08                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.9        | PC6             | M                 | General-purpose I/O port          |

| 59         M         LCDC SEG output pin           60         P60         M         General-purpose I/O port           LCDC SEG output pin         LCDC SEG output pin           61         P61         M         General-purpose I/O port           LCDC SEG output pin         LCDC SEG output pin           62         P62         M                                                                                                            | 30         | SEG08           | IVI               | LCDC SEG output pin               |

| SEG09         LCDC SEG output pin           60         P60         M         General-purpose I/O port           LCDC SEG output pin         LCDC SEG output pin           61         P61         M         General-purpose I/O port           LCDC SEG output pin         LCDC SEG output pin           62         P62         M                                                                                                                   | 50         | PC7             | M                 | General-purpose I/O port          |

| 60 SEG10 M LCDC SEG output pin  61 P61 M General-purpose I/O port LCDC SEG output pin  62 P62 M General-purpose I/O port                                                                                                                                                                                                                                                                                                                           | 33         | SEG09           | IVI               | LCDC SEG output pin               |

| SEG10         LCDC SEG output pin           61         P61         M         General-purpose I/O port           LCDC SEG output pin         LCDC SEG output pin           62         P62         M         General-purpose I/O port                                                                                                                                                                                                                | 60         | P60             | M                 | General-purpose I/O port          |

| 61 SEG11 M LCDC SEG output pin  62 P62 M General-purpose I/O port                                                                                                                                                                                                                                                                                                                                                                                  | - 50       | SEG10           | 171               | LCDC SEG output pin               |

| SEG11 LCDC SEG output pin  P62 M General-purpose I/O port                                                                                                                                                                                                                                                                                                                                                                                          | 61         | P61             |                   | General-purpose I/O port          |

| 62 M                                                                                                                                                                                                                                                                                                                                                                                                                                               | 01         | SEG11           | 171               | LCDC SEG output pin               |

| SEG12 LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                          | 62         | P62             |                   | General-purpose I/O port          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 02         | SEG12           | IVI               | LCDC SEG output pin               |

| P17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin no. | Pin name | I/O circuit type* | Function                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-------------------|-------------------------------|

| CMPO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44      | P17      | 11                | General-purpose I/O port      |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41      | CMPO     | П                 | Voltage comparator output pin |

| SEG00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42      | PB0      | M                 | General-purpose I/O port      |

| A3   SEG01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42      | SEG00    | IVI               | LCDC SEG output pin           |

| SEG01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43      | PB1      | M                 | General-purpose I/O port      |

| SEG02   M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43      | SEG01    | IVI               | LCDC SEG output pin           |

| SEG02   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44      | PC0      | M                 | General-purpose I/O port      |

| SEG03   M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 44      | SEG02    | IVI               | LCDC SEG output pin           |

| SEG03   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45      | PC1      | M                 | General-purpose I/O port      |

| A6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43      | SEG03    | IVI               | LCDC SEG output pin           |

| SEG04   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46      | PC2      | M                 | General-purpose I/O port      |

| AF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40      | SEG04    | IVI               | LCDC SEG output pin           |

| SEG05   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47      | PC3      | M                 | General-purpose I/O port      |

| SEG06   M   CDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47      | SEG05    | IVI               | LCDC SEG output pin           |

| SEG06   LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18      | P60      | M                 | General-purpose I/O port      |

| SEG07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40      | SEG06    | IVI               | LCDC SEG output pin           |

| SEG07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40      | P61      | M                 | General-purpose I/O port      |

| SEG08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45      | SEG07    | IVI               | LCDC SEG output pin           |

| SEG08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50      | P62      | M                 | General-purpose I/O port      |

| SEG09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30      | SEG08    | IVI               | LCDC SEG output pin           |

| SEG09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51      | P63      | M                 | General-purpose I/O port      |

| 52         SEG10         LCDC SEG output pin           53         P65         M         General-purpose I/O port           54         P66         M         General-purpose I/O port           54         SEG12         M         General-purpose I/O port           55         P67         M         General-purpose I/O port           LCDC SEG output pin         LCDC SEG output pin           56         PE0         M         General-purpose I/O port           LCDC SEG output pin         General-purpose I/O port           LCDC SEG output pin         General-purpose I/O port | 31      | SEG09    | IVI               | LCDC SEG output pin           |

| SEG10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52      | P64      | M                 | General-purpose I/O port      |

| SEG11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32      | SEG10    | IVI               | LCDC SEG output pin           |

| SEG11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53      | P65      | M                 | General-purpose I/O port      |

| 54         SEG12         M         LCDC SEG output pin           55         P67         M         General-purpose I/O port           LCDC SEG output pin         LCDC SEG output pin           56         PE0         M         General-purpose I/O port           LCDC SEG output pin         LCDC SEG output pin           57         PE1         M                                                                                                                                                                                                                                      | 33      | SEG11    | IVI               | LCDC SEG output pin           |

| SEG12         LCDC SEG output pin           55         P67           SEG13         M           LCDC SEG output pin           LCDC SEG output pin           General-purpose I/O port           LCDC SEG output pin           LCDC SEG output pin           General-purpose I/O port                                                                                                                                                                                                                                                                                                         | 54      | P66      | M                 | General-purpose I/O port      |

| SEG13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | J-1     | SEG12    | IVI               | LCDC SEG output pin           |

| SEG13         LCDC SEG output pin           FE0         M           SEG14         M           General-purpose I/O port           LCDC SEG output pin           General-purpose I/O port                                                                                                                                                                                                                                                                                                                                                                                                    | 55      | P67      | M                 | General-purpose I/O port      |

| 56 SEG14 M LCDC SEG output pin  FE1 M General-purpose I/O port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | SEG13    | 101               | LCDC SEG output pin           |

| SEG14 LCDC SEG output pin  PE1 General-purpose I/O port  M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56      | PE0      | M                 | General-purpose I/O port      |

| 57 H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30      | SEG14    | 171               | <u> </u>                      |

| SEG15 LCDC SEG output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57      | PE1      | M                 | General-purpose I/O port      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | SEG15    | 171               | LCDC SEG output pin           |

| Туре | Circuit                                                                                                           | Remarks                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| D    | Standby control  Hysteresis input  N-ch                                                                           | <ul><li>N-ch open drain output</li><li>Hysteresis input</li></ul>                                                  |

| G    | Pull-up control  P-ch  Digital output  N-ch  Standby control  Hysteresis input  CMOS input                        | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>CMOS input</li> <li>Pull-up control available</li> </ul>   |

| н    | Pull-up control  P-ch  Digital output  N-ch  Standby control  Hysteresis input                                    | <ul><li>CMOS output</li><li>Hysteresis input</li><li>Pull-up control available</li></ul>                           |

| ı    | Standby control CMOS input Hysteresis input N-ch                                                                  | <ul><li>N-ch open drain output</li><li>CMOS input</li><li>Hysteresis input</li></ul>                               |

| J    | Pull-up control  P-ch  Digital output  Digital output  Analog input  A/D control Standby control Hysteresis input | <ul> <li>CMOS output</li> <li>Hysteresis input</li> <li>Analog input</li> <li>Pull-up control available</li> </ul> |

# 9. Notes on Device Handling

# **Preventing latch-ups**

When using the device, ensure that the voltage applied does not exceed the maximum voltage rating.

In a CMOS IC, if a voltage higher than  $V_{CC}$  or a voltage lower than  $V_{SS}$  is applied to an input/output pin that is neither a medium-withstand voltage pin nor a high-withstand voltage pin, or if a voltage out of the rating range of power supply voltage mentioned in "17.1 Absolute Maximum Ratings" of "17. Electrical Characteristics" is applied to the  $V_{CC}$  pin or the  $V_{SS}$  pin, a latch-up may occur.

When a latch-up occurs, power supply current increases significantly, which may cause a component to be thermally destroyed.

# Stabilizing supply voltage

Supply voltage must be stabilized.

A malfunction may occur when power supply voltage fluctuates rapidly even though the fluctuation is within the guaranteed operating range of the  $V_{CC}$  power supply voltage.

As a rule of voltage stabilization, suppress voltage fluctuation so that the fluctuation in  $V_{CC}$  ripple (p-p value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the standard  $V_{CC}$  value, and the transient fluctuation rate does not exceed 0.1 V/ms at a momentary fluctuation such as switching the power supply.

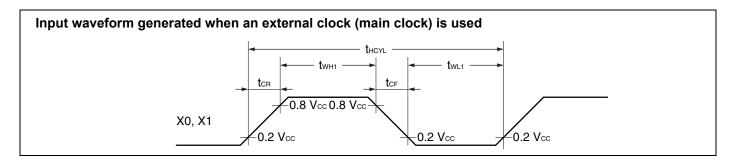

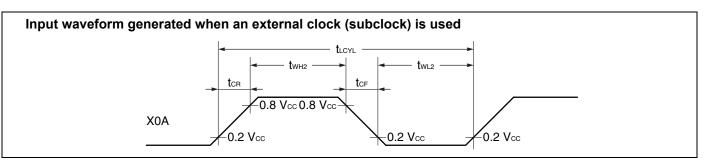

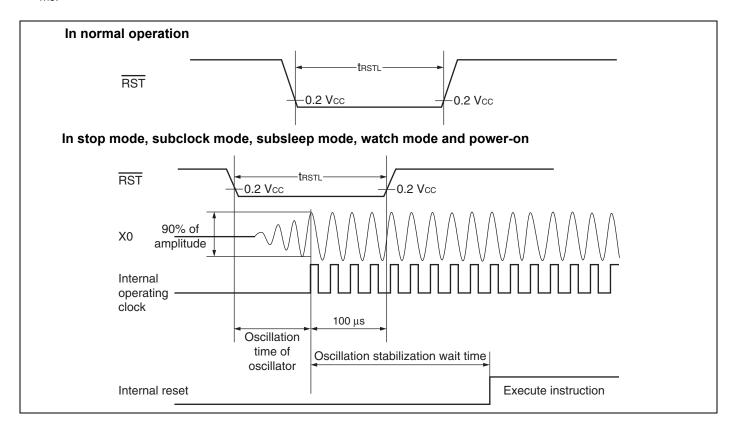

## Notes on using the external clock

When an external clock is used, oscillation stabilization wait time is required for power-on reset, wake-up from subclock mode or stop mode.

### 10. Pin Connection

## Treatment of unused input pins

If an unused input pin is left unconnected, a component may be permanently damaged due to malfunctions or latch-ups. Always pull up or pull down an unused input pin through a resistor of at least 2 k $\Omega$ . Set an unused input/output pin to the output state and leave it unconnected, or set it to the input state and treat it the same as an unused input pin. If there is an unused output pin, leave it unconnected.

#### Power supply pins

To reduce unnecessary electro-magnetic emission, prevent malfunctions of strobe signals due to an increase in the ground level, and conform to the total output current standard, always connect the  $V_{CC}$  pin and the  $V_{SS}$  pin to the power supply and ground outside the device. In addition, connect the current supply source to the  $V_{CC}$  pin and the  $V_{SS}$  pin with low impedance.

It is also advisable to connect a ceramic capacitor of approximately 0.1  $\mu F$  as a bypass capacitor between the  $V_{CC}$  pin and the  $V_{SS}$  pin at a location close to this device.

#### DBG pin

Connect the DBG pin directly to an external pull-up resistor.

To prevent the device from unintentionally entering the debug mode due to noise, minimize the distance between the DBG pin and the  $V_{CC}$  or  $V_{SS}$  pin when designing the layout of the printed circuit board.

The DBG pin should not stay at "L" level after power-on until the reset output is released.

### RST pin

Connect the RST pin directly to an external pull-up resistor.

To prevent the device from unintentionally entering the reset mode due to noise, minimize the distance between the RST pin and the  $V_{CC}$  or  $V_{SS}$  pin when designing the layout of the printed circuit board.

The PF2/RST pin functions as the reset input/output pin after power-on. In addition, the reset output function of the PF2/RST pin can be enabled by the RSTOE bit in the SYSC register, and the reset input function or the general purpose I/O function can be selected by the RSTEN bit in the SYSC register.

## Analog power supply

Always set the same potential to  $AV_{CC}$  and  $V_{CC}$  pins. When  $V_{CC}$  is larger than  $AV_{CC}$ , the current may flow through the AN00 to AN07 pins.

# 14. I/O Map (MB95410H Series)

| Address                                   | Register abbreviation | egister reviation Register name                      |     |                       |  |

|-------------------------------------------|-----------------------|------------------------------------------------------|-----|-----------------------|--|

| 0000 <sub>H</sub>                         | PDR0                  | Port 0 data register                                 | R/W | 00000000 <sub>B</sub> |  |

| 0001 <sub>H</sub>                         | DDR0                  | Port 0 direction register                            |     | 00000000 <sub>B</sub> |  |

| 0002 <sub>H</sub>                         | PDR1                  | Port 1 data register                                 | R/W | 00000000 <sub>B</sub> |  |

| 0003 <sub>H</sub>                         | DDR1                  | Port 1 direction register                            | R/W | 00000000 <sub>B</sub> |  |

| 0004 <sub>H</sub>                         | _                     | (Disabled)                                           |     | _                     |  |

| 0005 <sub>H</sub>                         | WATR                  | Oscillation stabilization wait time setting register | R/W | 11111111 <sub>B</sub> |  |

| 0006 <sub>H</sub>                         | PLLC                  | PLL control register                                 | R/W | 00000000 <sub>B</sub> |  |

| 0007 <sub>H</sub>                         | SYCC                  | System clock control register                        | R/W | XXXXXX11 <sub>B</sub> |  |

| 0008 <sub>H</sub>                         | STBC                  | Standby control register                             | R/W | 00000XXX <sub>B</sub> |  |

| 0009 <sub>H</sub>                         | RSRR                  | Reset source register                                | R/W | 000XXXXX <sub>B</sub> |  |

| 000A <sub>H</sub>                         | TBTC                  | Time-base timer control register                     | R/W | 00000000 <sub>B</sub> |  |

| 000B <sub>H</sub>                         | WPCR                  | Watch prescaler control register                     | R/W | 00000000 <sub>B</sub> |  |

| 000C <sub>H</sub>                         | WDTC                  | Watchdog timer control register                      | R/W | 00000000 <sub>B</sub> |  |

| 000D <sub>H</sub>                         | SYCC2                 | System clock control register 2                      | R/W | XX100011 <sub>B</sub> |  |

| 000E <sub>H</sub>                         | PDR2                  | Port 2 data register                                 |     | 00000000 <sub>B</sub> |  |

| 000F <sub>H</sub>                         | DDR2                  | Port 2 direction register                            |     | 00000000 <sub>B</sub> |  |

| 0010 <sub>H</sub> ,<br>0011 <sub>H</sub>  | _                     | (Disabled)                                           |     | _                     |  |

| 0012 <sub>H</sub>                         | PDR4                  | Port 4 data register                                 | R/W | 00000000 <sub>B</sub> |  |

| 0013 <sub>H</sub>                         | DDR4                  | Port 4 direction register                            | R/W | 00000000 <sub>B</sub> |  |

| 0014 <sub>H</sub>                         | PDR5                  | Port 5 data register                                 | R/W | 00000000 <sub>B</sub> |  |

| 0015 <sub>H</sub>                         | DDR5                  | Port 5 direction register                            | R/W | 00000000 <sub>B</sub> |  |

| 0016 <sub>H</sub>                         | PDR6                  | Port 6 data register                                 | R/W | 00000000 <sub>B</sub> |  |

| 0017 <sub>H</sub>                         | DDR6                  | Port 6 direction register                            | R/W | 00000000 <sub>B</sub> |  |

| 0018 <sub>H</sub> to<br>001B <sub>H</sub> | _                     | (Disabled)                                           |     | _                     |  |

| 001C <sub>H</sub>                         | PDR9                  | Port 9 data register                                 | R/W | 00000000 <sub>B</sub> |  |

| 001D <sub>H</sub>                         | DDR9                  | Port 9 direction register                            | R/W | 00000000 <sub>B</sub> |  |

| 001E <sub>H</sub>                         | PDRA                  | Port A data register                                 | R/W | 00000000 <sub>B</sub> |  |

| 001F <sub>H</sub>                         | DDRA                  | Port A direction register                            | R/W | 00000000 <sub>B</sub> |  |

| 0020 <sub>H</sub>                         | PDRB                  | Port B data register                                 | R/W | 00000000 <sub>B</sub> |  |

| 0021 <sub>H</sub>                         | DDRB                  | Port B direction register                            | R/W | 00000000 <sub>B</sub> |  |

| 0022 <sub>H</sub>                         | PDRC                  | Port C data register                                 | R/W | 00000000 <sub>B</sub> |  |

| 0023 <sub>H</sub>                         | DDRC                  | Port C direction register                            | R/W | 00000000 <sub>B</sub> |  |

| 0024 <sub>H</sub> ,<br>0025 <sub>H</sub>  | _                     | (Disabled)                                           |     |                       |  |

# 17. Electrical Characteristics

# 17.1 Absolute Maximum Ratings

| Parameter                              | Symbol               | Rat                   | Rating              |      | Remarks                                                                                   |

|----------------------------------------|----------------------|-----------------------|---------------------|------|-------------------------------------------------------------------------------------------|

| Parameter                              | Зушьог               | Min                   | Max                 | Unit | Remarks                                                                                   |

| Power supply voltage*1                 | V <sub>CC</sub>      | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 6 | V    |                                                                                           |

| Input voltage*1                        | V <sub>I</sub>       | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 6 | V    | *2                                                                                        |

| Output voltage*1                       | Vo                   | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 6 | V    | *2                                                                                        |

| Maximum clamp current                  | I <sub>CLAMP</sub>   | -2                    | +2                  | mA   | Applicable to specific pins*3                                                             |

| Total maximum clamp current            | $\Sigma  I_{CLAMP} $ | _                     | 20                  | mA   | Applicable to specific pins*3                                                             |

| "L" level maximum output current       | I <sub>CL</sub>      | _                     | 15                  | mA   |                                                                                           |

| "L" level average current              | I <sub>CLAV</sub>    | _                     | 4                   | mA   | Average output current = operating current × operating ratio (1 pin)                      |

| "L" level total maximum output current | $\Sigma I_{OL}$      | _                     | 100                 | mA   |                                                                                           |

| "L" level total average output current | $\Sigma I_{OLAV}$    | _                     | 50                  | mA   | Total average output current = operating current × operating ratio (Total number of pins) |

| "H" level maximum output current       | I <sub>CH</sub>      | _                     | -15                 | mA   |                                                                                           |

| "H" level average current              | I <sub>CHAV</sub>    | _                     | -4                  | mA   | Average output current = operating current × operating ratio (1 pin)                      |

| "H" level total maximum output current | ΣΙΟΗ                 | _                     | -100                | mA   |                                                                                           |

| "H" level total average output current | $\Sigma I_{OHAV}$    | _                     | -50                 | mA   | Total average output current = operating current × operating ratio (Total number of pins) |

| Power consumption                      | P <sub>d</sub>       | _                     | 320                 | mW   |                                                                                           |

| Operating temperature                  | T <sub>A</sub>       | -40                   | +85                 | °C   |                                                                                           |

| Storage temperature                    | T <sub>stg</sub>     | -55                   | +150                | °C   |                                                                                           |

<sup>\*1:</sup> These parameters are based on the condition that  $V_{SS}$  = 0.0 V.

(Continued)

Document Number: 002-07475 Rev. \*A

<sup>\*2:</sup>  $V_I$  and  $V_O$  must not exceed  $V_{CC}$  + 0.3 V.  $V_I$  must not exceed the rated voltage. However, if the maximum current to/from an input is limited by means of an external component, the  $I_{CLAMP}$  rating is used instead of the  $V_I$  rating.

$(V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| _ ,                    |                    |                                    |                                                                                                                                                | (100 5                                                                                        | Value |      |      |                                        |  |

|------------------------|--------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|------|------|----------------------------------------|--|

| Parameter              | Symbol             | Pin name                           | Condition                                                                                                                                      | Min                                                                                           | Typ*4 | Max  | Unit | Remarks                                |  |

|                        | Jacobs             | V <sub>CC</sub><br>(External clock | $V_{CC}$ = 5.5 V<br>$F_{CH}$ = 4 MHz<br>$F_{MP}$ = 10 MHz<br>Main PLL mode<br>(multiplied by 2.5)<br>$T_A$ = +25°C                             | ı                                                                                             | 9.7   | 12.5 | mA   |                                        |  |

|                        | ICCMPLL            | operation)                         | $V_{CC} = 5.5 \text{ V}$ $F_{CH} = 6.44 \text{ MHz}$ $F_{MP} = 16 \text{ MHz}$ Main PLL mode (multiplied by 2.5) $T_{A} = +25^{\circ}\text{C}$ | l                                                                                             | 13.9  | 20   | mA   |                                        |  |

|                        | I <sub>CCMCR</sub> | V                                  | $V_{CC}$ = 5.5 V<br>$F_{CRH}$ = 12.5 MHz<br>$F_{MP}$ = 12.5 MHz<br>Main CR clock mode                                                          | _                                                                                             | 11    | 13.2 | mA   |                                        |  |

| Power supply current*3 | I <sub>CCSCR</sub> | V <sub>CC</sub>                    | vcc                                                                                                                                            | V <sub>CC</sub> = 5.5 V<br>Sub-CR clock mode<br>(multiplied by 2.5)<br>T <sub>A</sub> = +25°C | _     | 112  | 410  | μА                                     |  |

|                        | I <sub>CCTS</sub>  | V <sub>CC</sub><br>(External clock | $V_{CC}$ = 5.5 V<br>$F_{CH}$ = 32 MHz<br>Time-base timer mode<br>$T_A$ = +25°C                                                                 | I                                                                                             | 1     | 3    | mA   |                                        |  |

|                        | Іссн               | operation)                         | $V_{CC}$ = 5.5 V<br>Substop mode<br>$T_A$ = +25°C                                                                                              | _                                                                                             | 3.1   | 22.5 | μA   | Main stop mode with one clock selected |  |

|                        | I <sub>A</sub>     |                                    | Current consumption<br>for<br>A/D conversion at<br>16 MHz                                                                                      | _                                                                                             | 1.5   | 4.7  | mA   |                                        |  |

|                        | I <sub>AH</sub>    | AV <sub>CC</sub>                   | Current consumption<br>for stopping<br>A/D conversion at<br>16 MHz                                                                             | _                                                                                             | 1     | 5    | μA   |                                        |  |

|                        | I <sub>V</sub>     |                                    | Current consumption of voltage comparator at 16 MHz                                                                                            | _                                                                                             | 113   | 350  | μA   |                                        |  |

$(V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                             | Symbol            | Din nama                                     | Condition                                                                 |    | Value |     |      | Remarks |

|---------------------------------------|-------------------|----------------------------------------------|---------------------------------------------------------------------------|----|-------|-----|------|---------|

| Parameter                             | Syllibol          | Pili lialile                                 | Pin name Condition                                                        |    | Typ*4 | Max | Unit | Remarks |

|                                       | I <sub>LVD</sub>  |                                              | Current consumption of the low-voltage detection circuit                  | _  | 31    | 54  | μΑ   |         |

| Power supply current*3                | I <sub>CRH</sub>  | V <sub>CC</sub>                              | Current consumption of the main CR oscillator                             | _  | 0.5   | 0.6 | mA   |         |

|                                       | I <sub>CRL</sub>  |                                              | Current consumption of<br>the sub-CR oscillator<br>oscillating at 100 kHz | _  | 20    | 72  | μΑ   |         |

| LCD internal                          | 1                 |                                              | D.1                                                                       |    | 400   | _   | kΩ   |         |

| division resis-<br>tance              | $R_{LCD}$         | _                                            | Between V4 and V <sub>SS</sub>                                            | _  | 40    | _   | kΩ   |         |

| COM0 to COM7 output impedance         | R <sub>VCOM</sub> | COM0 to COM7                                 | V1 to V4 = 4.1 V                                                          | _  | _     | 5   | kΩ   |         |

| SEG00 to<br>SEG39 output<br>impedance | R <sub>VSEG</sub> | SEG00 to SEG39                               | V 1 to V4 - 4.1 V                                                         | _  | _     | 7   | kΩ   |         |

| LCD leakage<br>current                | I <sub>LCDL</sub> | V0 to V4, COM0 to<br>COM7,<br>SEG00 to SEG39 | _                                                                         | -1 | _     | +1  | μΑ   |         |

<sup>\*1:</sup> The input levels of P01, P04, P10, P22 and P23 can be switched between "CMOS input level" and "hysteresis input level". The input level selection register (ILSR) is used to switch between the two input levels.

- See "17.4. AC Characteristics: 17.4.1. Clock Timing" for  $F_{CH}$  and  $F_{CL}$ .

- See "17.4. AC Characteristics: 17.4.2. Source Clock/Machine Clock" for F<sub>MP</sub> and F<sub>MPL</sub>.

<sup>\*2:</sup> P40 to P43, P50 to P53, P94, PB2 to PB4 and PC4 to PC7 are only available on the MB95410H Series.

<sup>\*3: •</sup> The power supply current is determined by the external clock. When the low-voltage detection option is selected, the power-supply current will be the sum of adding the current consumption of the low-voltage detection circuit (I<sub>LVD</sub>) to one of the value from I<sub>CC</sub> to I<sub>CCH</sub>. In addition, when both the low-voltage detection option and the CR oscillator are selected, the power supply current will be the sum of adding up the current consumption of the low-voltage detection circuit, the current consumption of the CR oscillators (I<sub>CRH</sub>, I<sub>CRL</sub>) and a specified value. In on-chip debug mode, the CR oscillator (I<sub>CRH</sub>) and the low-voltage detection circuit are always enabled, and current consumption therefore increases accordingly.

<sup>\*4:</sup>  $V_{CC} = 5.0 \text{ V}, T_A = +25^{\circ}\text{C}$

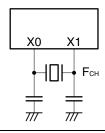

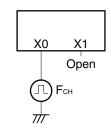

# Figure of main clock input port external connection

When a crystal oscillator or When the external clock is used a ceramic oscillator is used (X1 is open)

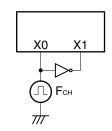

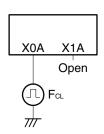

# Figure of subclock input port external connection

When a crystal oscillator or a ceramic oscillator is used

XOA X1A

When the external clock is used

# 17.4.2 Source Clock/Machine Clock

$(V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| B                                                     | 0                 | Pin  |        | Value  |        | 11!4 | Barranda                                                                                                                                                   |

|-------------------------------------------------------|-------------------|------|--------|--------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                             | Symbol            | name | Min    | Тур    | Max    | Unit | Remarks                                                                                                                                                    |

|                                                       |                   |      | 61.5   | _      | 2000   | ns   | When the main oscillation clock is used Min: F <sub>CH</sub> = 32.5 MHz, divided by 2 Max: F <sub>CH</sub> = 1 MHz, divided by 2                           |

| Source clock                                          |                   |      | 61.5   | _      | 2000   | ns   | When the main oscillation clock is used Min: F <sub>CH</sub> = 8.125 MHz, multiplied by the PLL multiplier of 2 Max: F <sub>CH</sub> = 1 MHz, divided by 2 |

| cycle time*1                                          | t <sub>SCLK</sub> | _    | 80     | _      | 1000   | ns   | When the main CR clock is used Min: F <sub>CRH</sub> = 12.5 MHz Max: F <sub>CRH</sub> = 1 MHz                                                              |