Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | F <sup>2</sup> MC-8FX                                                           |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 16MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, SIO, UART/USART                                               |

| Peripherals                | LCD, POR, PWM, WDT                                                              |

| Number of I/O              | 58                                                                              |

| Program Memory Size        | 60KB (60K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1.98K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/10b                                                                     |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

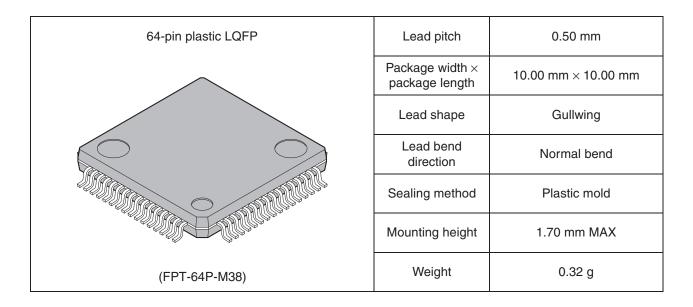

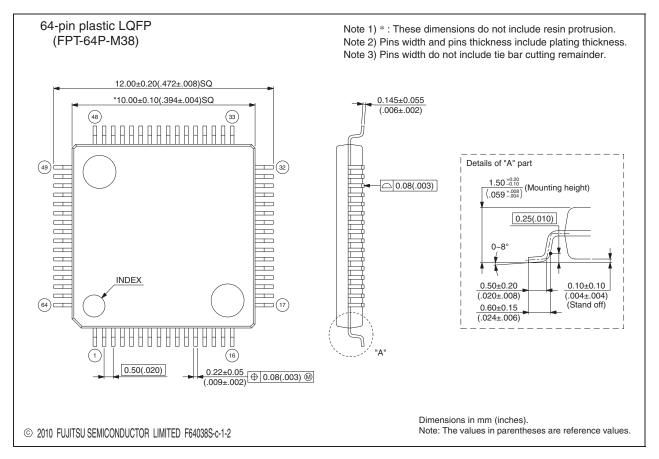

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb95f478hpmc1-g-sne2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part number                 |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |                                                                                      |                               |                                         |                                                   |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|---------------------------------------------------|--|--|

|                             | MB95F414H                                                                                                                                                                                                                                                                                          | MB95F416H                                                                                                                                                                           | MB95F418H                                                                            | MB95F414K                     | MB95F416K                               | MB95F418K                                         |  |  |

| Package                     |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |                                                                                      |                               |                                         |                                                   |  |  |

|                             | 2 channels                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     |                                                                                      |                               |                                         |                                                   |  |  |

| 8/16-bit composite<br>timer |                                                                                                                                                                                                                                                                                                    | er function, PWC f<br>an be selected fror                                                                                                                                           | unction, PWM fund                                                                    | ction and input cap           |                                         | ) <b> </b> ".                                     |  |  |

| LCD controller<br>(LCDC)    | <ul> <li>If the number of pixels that</li> <li>If the number</li> </ul>                                                                                                                                                                                                                            | or 40 (selectable)<br>or of COM outputs is<br>can be displayed<br>r of COM outputs is<br>can be displayed<br>r supply (bias) pins<br>ode<br>esistor whose resis<br>with the LCD mod | 160 (4×40).<br>s 8, the maximum r<br>288 (8×36).<br>s: 5 (Max)<br>stance value can b | number of SEG out             | puts is 36, and the                     | maximum number<br>maximum number<br>pugh software |  |  |

|                             | 1 channel                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                     |                                                                                      |                               |                                         |                                                   |  |  |

| 16-bit reload timer         | <ul> <li>Two clock modes and two counter operating modes can be selected</li> <li>Square waveform output</li> <li>Count clock: it can be selected from internal clocks (seven types) and external clocks.</li> <li>Counter operating mode: reload mode or one-shot mode can be selected</li> </ul> |                                                                                                                                                                                     |                                                                                      |                               |                                         |                                                   |  |  |

| Event counter               |                                                                                                                                                                                                                                                                                                    | en the event counter                                                                                                                                                                |                                                                                      |                               | 1, event counter further and the 8/16-b | unction can be<br>bit composite timer             |  |  |

|                             | 2 channels                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     |                                                                                      |                               |                                         |                                                   |  |  |

| 8/16-bit PPG                | <ul> <li>Each channel of</li> <li>Counter operatir</li> </ul>                                                                                                                                                                                                                                      |                                                                                                                                                                                     |                                                                                      |                               | 6-bit PPG × 1 chan                      | nel"                                              |  |  |

| Watch counter               | <ul> <li>Count clock: For</li> <li>Counter value ca<br/>and the counter</li> </ul>                                                                                                                                                                                                                 | an be set from 0 to                                                                                                                                                                 | sources (125 ms, 63. (Capable of co                                                  |                               |                                         | ource is 1 second                                 |  |  |

|                             | 8 channels                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     |                                                                                      |                               |                                         |                                                   |  |  |

| External interrupt          | <ul> <li>Interrupt by edge</li> <li>It can be used to</li> </ul>                                                                                                                                                                                                                                   | e detection (The ris<br>wake up the device                                                                                                                                          | sing edge, falling e<br>ce from the standb                                           | dge, or both edges<br>y mode. | can be selected.)                       |                                                   |  |  |

| On-chip debug               |                                                                                                                                                                                                                                                                                                    | writing. (asynchro                                                                                                                                                                  |                                                                                      |                               |                                         |                                                   |  |  |

| Watch prescaler             | Eight different time<br>(62.5 ms, 125 ms,                                                                                                                                                                                                                                                          | 250 ms, 500 ms, 1                                                                                                                                                                   | 1 s, 2 s, 4 s, 8 s)                                                                  |                               |                                         |                                                   |  |  |

| Flash memory                | commands. <ul> <li>It has a flag indic</li> </ul>                                                                                                                                                                                                                                                  | cating the completi<br>am/erase cycles: 1<br>me: 20 years                                                                                                                           | on of the operatior<br>100000                                                        | of Embedded Alg               | se/erase-suspend/e                      | erase-resume                                      |  |  |

| Standby mode                |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     | e, time-base timer                                                                   |                               |                                         |                                                   |  |  |

| Package                     |                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     | EPT-8                                                                                | )P-M37                        |                                         |                                                   |  |  |

## MB95470H Series

| Part number                         | MB95F474H                                                                                                                                                                                 | MB95F476H                                                                                                                                                                                                                                                              | MB95F478H                                          | MB95F474K                                                         | MB95F476K           | MB95F478K   |  |  |  |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------|---------------------|-------------|--|--|--|--|

| Package                             |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                        | Elach mor                                          | hory product                                                      |                     |             |  |  |  |  |

| Clock supervisor                    | It supervises the n                                                                                                                                                                       | nain clock oscillatio                                                                                                                                                                                                                                                  |                                                    |                                                                   |                     |             |  |  |  |  |

| Program ROM<br>capacity             | 20 Kbyte                                                                                                                                                                                  | 20 Kbyte 36 Kbyte 60 Kbyte 20 Kbyte 36 Kbyte 6                                                                                                                                                                                                                         |                                                    |                                                                   |                     |             |  |  |  |  |

| RAM capacity                        | 496 bytes                                                                                                                                                                                 | 1008 bytes                                                                                                                                                                                                                                                             | 2032 bytes                                         | 496 bytes                                                         | 1008 bytes          | 2032 bytes  |  |  |  |  |

| Low-voltage<br>detection reset      |                                                                                                                                                                                           | No                                                                                                                                                                                                                                                                     |                                                    |                                                                   | Yes                 |             |  |  |  |  |

| Reset input                         |                                                                                                                                                                                           | Dedicated                                                                                                                                                                                                                                                              |                                                    | Sel                                                               | ected through softw | vare        |  |  |  |  |

| CPU functions                       | <ul> <li>Instruction bit let</li> <li>Instruction lengt</li> <li>Data bit length</li> <li>Minimum instruction</li> </ul>                                                                  | Number of basic instructions       : 136         Instruction bit length       : 8 bits         Instruction length       : 1 to 3 bytes                                                                                                                                 |                                                    |                                                                   |                     |             |  |  |  |  |

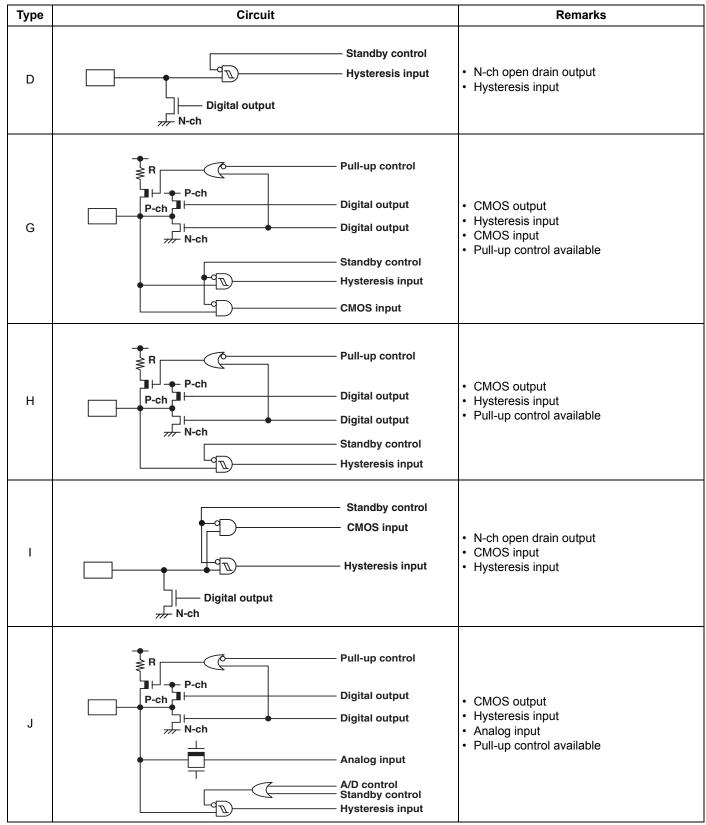

| General-purpose<br>I/O              | I/O ports (Max)       : 58       • I/O ports (Max)       : 59         CMOS I/O       : 55       • CMOS I/O       : 55         N-ch open drain       : 3       • N-ch open drain       : 4 |                                                                                                                                                                                                                                                                        |                                                    |                                                                   |                     |             |  |  |  |  |

| Time-base timer                     | Interval time: 0.25                                                                                                                                                                       | 6 ms - 8.3 s (exteri                                                                                                                                                                                                                                                   | nal clock frequency                                | / = 4 MHz)                                                        |                     |             |  |  |  |  |

| Hardware/software<br>watchdog timer |                                                                                                                                                                                           | clock at 10 MHz: 1                                                                                                                                                                                                                                                     |                                                    | f the hardware wate                                               | chdog timer.        |             |  |  |  |  |

| Wild register                       | It can be used to r                                                                                                                                                                       | eplace three bytes                                                                                                                                                                                                                                                     | of data.                                           |                                                                   | -                   |             |  |  |  |  |

|                                     | 1 channel                                                                                                                                                                                 |                                                                                                                                                                                                                                                                        |                                                    |                                                                   |                     |             |  |  |  |  |

| I <sup>2</sup> C                    | <ul> <li>Bus error function</li> <li>Detecting transmoster</li> <li>Start condition response</li> </ul>                                                                                   | <ul> <li>Master/Slave sending and receiving</li> <li>Bus error function and arbitration function</li> <li>Detecting transmitting direction function</li> <li>Start condition repeated generation and detection functions</li> <li>Built-in wake-up function</li> </ul> |                                                    |                                                                   |                     |             |  |  |  |  |

|                                     | 3 channels                                                                                                                                                                                |                                                                                                                                                                                                                                                                        |                                                    |                                                                   |                     |             |  |  |  |  |

| UART/SIO                            | <ul> <li>It has a full duple<br/>detection functio</li> <li>It uses the NRZ</li> <li>LSB-first data tra</li> </ul>                                                                        | n.<br>type transfer forma<br>ansfer and MSB-fir                                                                                                                                                                                                                        | ariable data length<br>at.<br>st data transfer are | (5/6/7/8 bits), a bui<br>e available to use.<br>clock-synchronous | -                   |             |  |  |  |  |

| 8/10-bit A/D                        | 8 channels                                                                                                                                                                                |                                                                                                                                                                                                                                                                        |                                                    |                                                                   |                     |             |  |  |  |  |

| converter                           | 8-bit or 10-bit reso                                                                                                                                                                      | lution can be seled                                                                                                                                                                                                                                                    | cted.                                              |                                                                   |                     |             |  |  |  |  |

|                                     | 2 channels                                                                                                                                                                                |                                                                                                                                                                                                                                                                        |                                                    |                                                                   |                     |             |  |  |  |  |

| 8/16-bit composite<br>timer         | <ul> <li>It has built-in tim</li> </ul>                                                                                                                                                   | er function, PWC f<br>an be selected fror                                                                                                                                                                                                                              | function, PWM fun                                  | hannels" or a "16-b<br>ction and input cap<br>seven types) and ex | ture function.      | (Continued) |  |  |  |  |

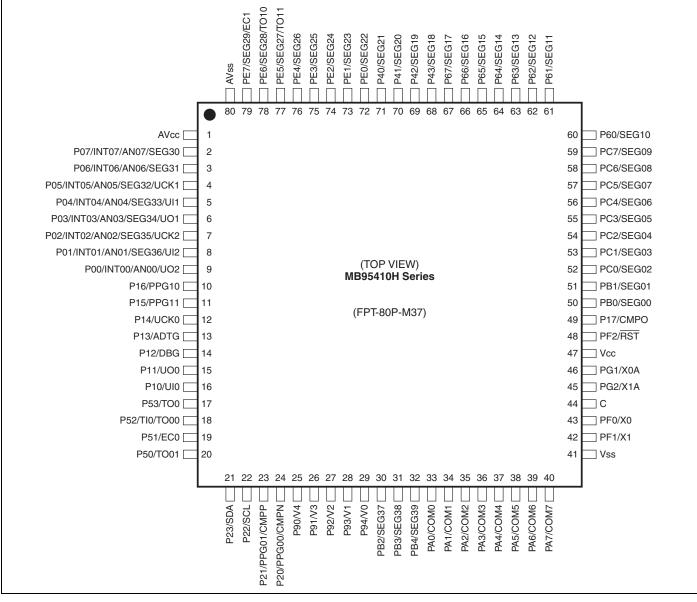

# 5. Pin Assignment

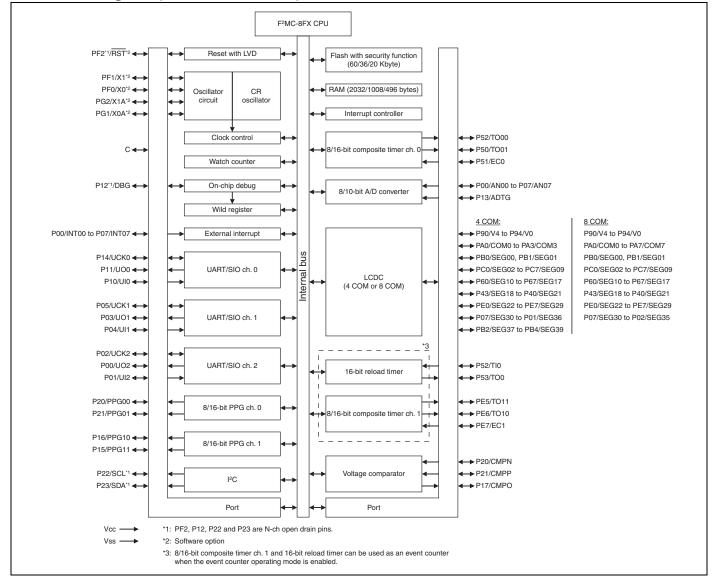

# 11. Block Diagram (MB95410H Series)

| Address           | Register<br>abbreviation | Register name                                                     | R/W | Initial value         |

|-------------------|--------------------------|-------------------------------------------------------------------|-----|-----------------------|

| 005F <sub>H</sub> | RDR1                     | UART/SIO serial input data register ch. 1                         | R   | 00000000 <sub>B</sub> |

| 0060 <sub>H</sub> | IBCR00                   | I <sup>2</sup> C bus control register 0                           | R/W | 00000001 <sub>B</sub> |

| 0061 <sub>H</sub> | IBCR10                   | I <sup>2</sup> C bus control register 1                           | R/W | 00000000 <sub>B</sub> |

| 0062 <sub>H</sub> | IBCR0                    | I <sup>2</sup> C bus status register                              | R   | 00000000 <sub>B</sub> |

| 0063 <sub>H</sub> | IDDR0                    | I <sup>2</sup> C data register                                    | R/W | 00000000 <sub>B</sub> |

| 0064 <sub>H</sub> | IAAR0                    | I <sup>2</sup> C address register                                 | R/W | 00000000 <sub>B</sub> |

| 0065 <sub>H</sub> | ICCR0                    | I <sup>2</sup> C clock control register                           | R/W | 00000000 <sub>B</sub> |

| 0066 <sub>H</sub> | SMC12                    | UART/SIO serial mode control register 1 ch. 2                     | R/W | 00000000 <sub>B</sub> |

| 0067 <sub>H</sub> | SMC22                    | UART/SIO serial mode control register 2 ch. 2                     | R/W | 00100000 <sub>B</sub> |

| 0068 <sub>H</sub> | SSR2                     | UART/SIO serial status register ch. 2                             | R/W | 00000001 <sub>B</sub> |

| 0069 <sub>H</sub> | TDR2                     | UART/SIO serial output data register ch. 2                        | R/W | 00000000 <sub>B</sub> |

| 006A <sub>H</sub> | RDR2                     | UART/SIO serial input data register ch. 2                         | R   | 00000000 <sub>B</sub> |

| 006B <sub>H</sub> | —                        | (Disabled)                                                        | —   | _                     |

| 006C <sub>H</sub> | ADC1                     | 8/10-bit A/D converter control register 1                         | R/W | 00000000 <sub>B</sub> |

| 006D <sub>H</sub> | ADC2                     | 8/10-bit A/D converter control register 2                         | R/W | 00000000 <sub>B</sub> |

| 006E <sub>H</sub> | ADDH                     | 8/10-bit A/D converter data register upper                        | R/W | 00000000 <sub>B</sub> |

| 006F <sub>H</sub> | ADDL                     | 8/10-bit A/D converter data register lower                        | R/W | 00000000 <sub>B</sub> |

| 0070 <sub>H</sub> | WCSR                     | Watch counter status register                                     | R/W | 00000000 <sub>B</sub> |

| 0071 <sub>H</sub> | FSR2                     | Flash memory status register 2                                    | R/W | 00000000 <sub>B</sub> |

| 0072 <sub>H</sub> | FSR                      | Flash memory status register                                      | R/W | 000X0000 <sub>B</sub> |

| 0073 <sub>H</sub> | SWRE0                    | Flash memory sector write control register 0                      | R/W | 00000000 <sub>B</sub> |

| 0074 <sub>H</sub> | FSR3                     | Flash memory status register 3                                    | R   | 00000000 <sub>B</sub> |

| 0075 <sub>H</sub> | —                        | (Disabled)                                                        | —   | _                     |

| 0076 <sub>H</sub> | WREN                     | Wild register address compare enable register                     | R/W | 00000000 <sub>B</sub> |

| 0077 <sub>H</sub> | WROR                     | Wild register data test setting register                          | R/W | 00000000 <sub>B</sub> |

| 0078 <sub>H</sub> | —                        | Mirror of register bank pointer (RP) and direct bank pointer (DP) | —   | _                     |

| 0079 <sub>H</sub> | ILR0                     | Interrupt level setting register 0                                | R/W | 11111111 <sub>B</sub> |

| 007A <sub>H</sub> | ILR1                     | Interrupt level setting register 1                                | R/W | 11111111 <sub>B</sub> |

| 007B <sub>H</sub> | ILR2                     | Interrupt level setting register 2                                | R/W | 11111111 <sub>B</sub> |

| 007C <sub>H</sub> | ILR3                     | Interrupt level setting register 3                                | R/W | 11111111 <sub>B</sub> |

| 007D <sub>H</sub> | ILR4                     | Interrupt level setting register 4                                | R/W | 11111111 <sub>B</sub> |

| 007E <sub>H</sub> | ILR5                     | Interrupt level setting register 5                                | R/W | 11111111 <sub>B</sub> |

| 007F <sub>H</sub> |                          | (Disabled)                                                        | —   | _                     |

| 0F80 <sub>H</sub> | WRARH0                   | Wild register address setting register (upper) ch. 0              | R/W | 00000000 <sub>B</sub> |

| 0F81 <sub>H</sub> | WRARL0                   | Wild register address setting register (lower) ch. 0              | R/W | 00000000 <sub>B</sub> |

| 0F82 <sub>H</sub> | WRDR0                    | Wild register data setting register ch. 0                         | R/W | 00000000 <sub>B</sub> |

# 17. Electrical Characteristics

# 17.1 Absolute Maximum Ratings

| Parameter                                 | Symphol              | Rat                   | ting                | Unit | Remarks                                                                                         |

|-------------------------------------------|----------------------|-----------------------|---------------------|------|-------------------------------------------------------------------------------------------------|

| Parameter                                 | Symbol               | Min                   | Мах                 | Unit | Remarks                                                                                         |

| Power supply voltage*1                    | V <sub>CC</sub>      | V <sub>SS</sub> - 0.3 | V <sub>SS</sub> + 6 | V    |                                                                                                 |

| Input voltage*1                           | VI                   | $V_{SS} - 0.3$        | $V_{SS} + 6$        | V    | *2                                                                                              |

| Output voltage*1                          | V <sub>O</sub>       | $V_{SS} - 0.3$        | $V_{SS} + 6$        | V    | *2                                                                                              |

| Maximum clamp current                     | ICLAMP               | -2                    | +2                  | mA   | Applicable to specific pins <sup>*3</sup>                                                       |

| Total maximum clamp current               | $\Sigma  I_{CLAMP} $ | —                     | 20                  | mA   | Applicable to specific pins <sup>*3</sup>                                                       |

| "L" level maximum output current          | I <sub>CL</sub>      | —                     | 15                  | mA   |                                                                                                 |

| "L" level average current                 | I <sub>CLAV</sub>    | —                     | 4                   | mA   | Average output current =<br>operating current × operating ratio (1 pin)                         |

| "L" level total maximum output current    | $\Sigma I_{OL}$      | _                     | 100                 | mA   |                                                                                                 |

| "L" level total average output current    | $\Sigma I_{OLAV}$    | _                     | 50                  | mA   | Total average output current =<br>operating current × operating ratio<br>(Total number of pins) |

| "H" level maximum output current          | I <sub>CH</sub>      | —                     | -15                 | mA   |                                                                                                 |

| "H" level average current                 | I <sub>CHAV</sub>    | —                     | -4                  | mA   | Average output current =<br>operating current × operating ratio (1 pin)                         |

| "H" level total maximum<br>output current | $\Sigma I_{OH}$      | _                     | -100                | mA   |                                                                                                 |

| "H" level total average output current    | $\Sigma I_{OHAV}$    | _                     | -50                 | mA   | Total average output current =<br>operating current × operating ratio<br>(Total number of pins) |

| Power consumption                         | Pd                   | —                     | 320                 | mW   |                                                                                                 |

| Operating temperature                     | T <sub>A</sub>       | -40                   | +85                 | °C   |                                                                                                 |

| Storage temperature                       | T <sub>stg</sub>     | -55                   | +150                | °C   |                                                                                                 |

\*1: These parameters are based on the condition that  $V_{SS}$  = 0.0 V.

\*2: V<sub>I</sub> and V<sub>O</sub> must not exceed V<sub>CC</sub> + 0.3 V. V<sub>I</sub> must not exceed the rated voltage. However, if the maximum current to/from an input is limited by means of an external component, the I<sub>CLAMP</sub> rating is used instead of the V<sub>I</sub> rating.

## **17.3 DC Characteristics**

| $(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{ V}_{SS} = 0.0 \text{ V}, \text{ T}_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$ | $(V_{CC} = 5.0)$ | V ±10%, V <sub>SS</sub> = | = 0.0 V, T <sub>A</sub> | = -40°C to +85°C |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|-------------------------|------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|-------------------------|------------------|

| Domoniation                                    | Cumhal           | Din nome                                                                                                                                                                                                                                                                                                              | Condition               |                       | Value |                       | Unit | Bomorko                                                    |  |

|------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------|-------|-----------------------|------|------------------------------------------------------------|--|

| Parameter                                      | Symbol           | Pin name                                                                                                                                                                                                                                                                                                              | Condition               | Min                   | Тур   | Max                   | Unit | Remarks                                                    |  |

|                                                | V <sub>IHI</sub> | P01, P04, P10,<br>P22, P23                                                                                                                                                                                                                                                                                            | *1                      | 0.7 V <sub>CC</sub>   | _     | V <sub>CC</sub> + 0.3 | V    | When CMOS input<br>level (hysteresis<br>input) is selected |  |

| "H" level input<br>voltage                     | V <sub>IHS</sub> | P00 to P07, P10 to<br>P17,<br>P20 to P23, P40 to<br>P43 <sup>*2</sup> ,<br>P50 to P53 <sup>*2</sup> , P60<br>to P67,<br>P90 to P93, P94 <sup>*2</sup> ,<br>PA0 to PA7,<br>PB0, PB1,<br>PB2 to PB4 <sup>*2</sup> ,<br>PC0 to PC3,<br>PC4 to PC7 <sup>*2</sup> ,<br>PE0 to PE7,<br>PE0 to PE7,<br>PF0, PF1, PG1,<br>PG2 | *1                      | 0.8 V <sub>CC</sub>   |       | V <sub>CC</sub> + 0.3 | V    | Hysteresis input                                           |  |

|                                                | V <sub>IHM</sub> | PF2                                                                                                                                                                                                                                                                                                                   | —                       | 0.7 V <sub>CC</sub>   |       | $V_{CC} + 0.3$        | V    | Hysteresis input                                           |  |

|                                                | V <sub>IL</sub>  | P01, P04, P10,<br>P22, P23                                                                                                                                                                                                                                                                                            | *1                      | V <sub>SS</sub> - 0.3 | _     | 0.3 V <sub>CC</sub>   | V    | When CMOS input<br>level (hysteresis<br>input) is selected |  |

| "L" level input<br>voltage                     | V <sub>ILS</sub> | P00 to P07, P10 to<br>P17,<br>P20 to P23, P40 to<br>P43 <sup>*2</sup> ,<br>P50 to P53 <sup>*2</sup> , P60<br>to P67,<br>P90 to P93, P94 <sup>*2</sup> ,<br>PA0 to PA7,<br>PB0, PB1,<br>PB2 to PB4 <sup>*2</sup> ,<br>PC0 to PC3,<br>PC4 to PC7 <sup>*2</sup> ,<br>PE0 to PE7,<br>PF0, PF1, PG1,<br>PG2                | *1                      | V <sub>SS</sub> – 0.3 |       | 0.2 V <sub>CC</sub>   | V    | Hysteresis input                                           |  |

|                                                | V <sub>ILM</sub> | PF2                                                                                                                                                                                                                                                                                                                   | _                       | $V_{SS}-0.3$          | _     | 0.3 V <sub>CC</sub>   | V    | Hysteresis input                                           |  |

| Open-drain<br>output<br>application<br>voltage | V <sub>D</sub>   | P12, P22, P23,<br>PF2                                                                                                                                                                                                                                                                                                 | _                       | V <sub>SS</sub> – 0.3 | _     | V <sub>SS</sub> + 5.5 | V    |                                                            |  |

| "H" level<br>output voltage                    | V <sub>OH1</sub> | Output pins other<br>than P12, P22,<br>P23, PF2                                                                                                                                                                                                                                                                       | I <sub>OH</sub> = -4 mA | V <sub>CC</sub> - 0.5 | _     | _                     | V    | Continued                                                  |  |

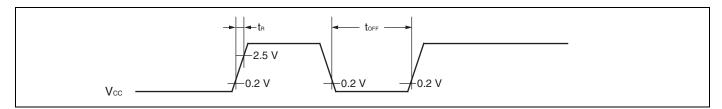

#### 17.4.4 Power-on Reset

$(V_{SS} = 0.0 \text{ V}, \text{ } \text{T}_{\text{A}} = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                | Symbol           | Condition | Val | lue | Unit | Remarks                  |

|--------------------------|------------------|-----------|-----|-----|------|--------------------------|

| Falailletei              | Symbol           | Condition | Min | Мах | Unit | Remarks                  |

| Power supply rising time | t <sub>R</sub>   | _         | —   | 50  | ms   |                          |

| Power supply cutoff time | t <sub>OFF</sub> | —         | 1   |     | ms   | Wait time until power-on |

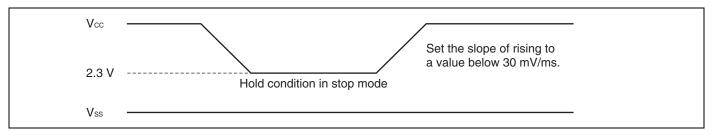

# Note: A sudden change of power supply voltage may activate the power-on reset function. When changing the power supply voltage during the operation, set the slope of rising to a value below within 30 mV/ms as shown below.

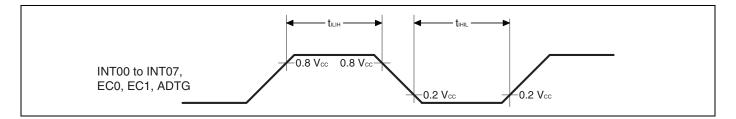

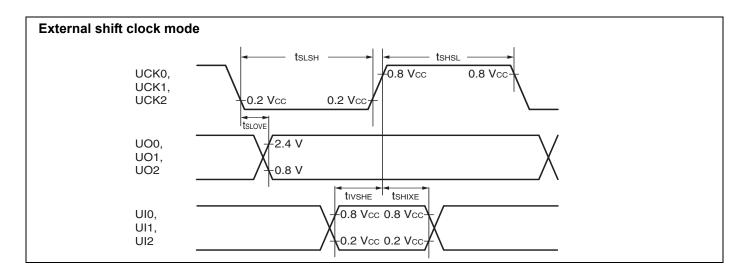

17.4.5 Peripheral Input Timing

$(V_{CC} = 5.0 \text{ V} \pm 10\%, V_{SS} = 0.0 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C})$

| Parameter                        | Symbol Pin name   |                                  | Va                    | Unit |      |

|----------------------------------|-------------------|----------------------------------|-----------------------|------|------|

| Falameter                        | Symbol            | Finname                          | Min                   | Max  | Unit |

| Peripheral input "H" pulse width | t <sub>ILIH</sub> | INT00 to INT07, EC0, EC1, ADTG   | 2 t <sub>MCLK</sub> * | —    | ns   |

| Peripheral input "L" pulse width | t <sub>IHIL</sub> | 111100 10 111107, ECO, ECT, ADTO | 2 t <sub>MCLK</sub> * | —    | ns   |

\*: See "17.4.2. Source Clock/Machine Clock" for t<sub>MCLK</sub>.

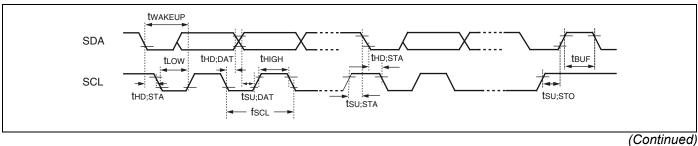

## 17.4.8 I<sup>2</sup>C Timing

|                                                                                  |                     |          | Conditions              | Value   |                    |           |                   |      |

|----------------------------------------------------------------------------------|---------------------|----------|-------------------------|---------|--------------------|-----------|-------------------|------|

| Parameter                                                                        | Symbol              | Pin name |                         | Standar | d-mode             | Fast-mode |                   | Unit |

|                                                                                  |                     |          |                         | Min     | Max                | Min       | Max               |      |

| SCL clock frequency                                                              | f <sub>SCL</sub>    | SCL      |                         | 0       | 100                | 0         | 400               | kHz  |

| (Repeat) Start condition hold time SDA $\downarrow \rightarrow$ SCL $\downarrow$ | t <sub>HD;STA</sub> | SCL, SDA |                         | 4.0     | _                  | 0.6       | _                 | μs   |

| SCL clock "L" width                                                              | t <sub>LOW</sub>    | SCL      |                         | 4.7     | —                  | 1.3       | _                 | μs   |

| SCL clock "H" width                                                              | t <sub>HIGH</sub>   | SCL      |                         | 4.0     | —                  | 0.6       | _                 | μs   |

| (Repeat) Start condition setup time SCL $\uparrow \rightarrow$ SDA $\downarrow$  | t <sub>SU;STA</sub> | SCL, SDA | R = 1.7 kΩ,             | 4.7     | _                  | 0.6       | _                 | μs   |

| Data hold time SCL $\downarrow \rightarrow$ SDA $\downarrow \uparrow$            | t <sub>HD;DAT</sub> | SCL, SDA | C = 50 pF* <sup>1</sup> | 0       | 3.45* <sup>2</sup> | 0         | 0.9* <sup>3</sup> | μs   |

| Data setup time SDA $\downarrow \uparrow \rightarrow$ SCL $\uparrow$             | t <sub>SU;DAT</sub> | SCL, SDA |                         | 0.25    | _                  | 0.1       | _                 | μs   |

| Stop condition setup time SCL $\uparrow \rightarrow$ SDA $\uparrow$              | t <sub>su;sто</sub> | SCL, SDA |                         | 4.0     | _                  | 0.6       | _                 | μs   |

| Bus free time between stop condition and start condition                         | t <sub>BUF</sub>    | SCL, SDA |                         | 4.7     | _                  | 1.3       |                   | μs   |

$(V_{CC} = 5.0 \text{ V} \pm 10\%, \text{AV}_{SS} = V_{SS} = 0.0 \text{ V}, \text{T}_{A} = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C})$

\*1: R represents the pull-up resistor of the SCL and SDA lines, and C the load capacitor of the SCL and SDA lines.

\*2: The maximum t<sub>HD;DAT</sub> in the Standard-mode is applicable only when the time during which the device is holding the SCL signal at "L" (t<sub>I OW</sub>) does not extend.

\*3: A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, provided that the condition of t<sub>SU;DAT</sub> ≥ 250 ns is fulfilled.

| Symbol              | Pin<br>name                                                            | Conditions                                                                                                                                                                |                                                                                                                                                                             | Value* <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                              |

|---------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                                                                        |                                                                                                                                                                           | Min                                                                                                                                                                         | Мах                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Remarks                                                                                                                                                                                      |

| t <sub>LOW</sub>    | SCL                                                                    |                                                                                                                                                                           | (2 + nm / 2)t <sub>MCLK</sub> – 20                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Master mode                                                                                                                                                                                  |

| t <sub>HIGH</sub>   | SCL                                                                    |                                                                                                                                                                           | (nm / 2)t <sub>MCLK</sub> – 20                                                                                                                                              | (nm / 2)t <sub>MCLK</sub> + 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Master mode                                                                                                                                                                                  |

| t <sub>hd;sta</sub> | SCL,<br>SDA                                                            |                                                                                                                                                                           | (– 1 + nm / 2)t <sub>MCLK</sub> – 20                                                                                                                                        | (- 1 + nm)t <sub>MCLK</sub> + 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Master mode<br>Maximum value is<br>applied when<br>m, n = 1, 8.<br>Otherwise, the<br>minimum value is<br>applied.                                                                            |

| t <sub>SU;STO</sub> | SCL,<br>SDA                                                            |                                                                                                                                                                           | (1 + nm / 2)t <sub>MCLK</sub> - 20                                                                                                                                          | (1 + nm / 2)t <sub>MCLK</sub> + 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Master mode                                                                                                                                                                                  |