#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                         |

|----------------------------|---------------------------------------------------------|

| Product Status             | Obsolete                                                |

| Core Processor             | ARM® Cortex®-M3                                         |

| Core Size                  | 32-Bit Single-Core                                      |

| Speed                      | 80MHz                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT         |

| Number of I/O              | 86                                                      |

| Program Memory Size        | 384KB (384K x 8)                                        |

| Program Memory Type        | FLASH                                                   |

| EEPROM Size                | -                                                       |

| RAM Size                   | 16K x 8                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                               |

| Data Converters            | A/D 16x12b                                              |

| Oscillator Type            | Internal                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                       |

| Mounting Type              | Surface Mount                                           |

| Package / Case             | 100-LQFP                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z32f38412als |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in this document's revision history reflects a change from its previous edition. For more details, refer to the corresponding page(s) or appropriate links furnished in the table below.

| Date        | Revision<br>Level | Description                                                                                                                | Page |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------|------|

| Jun<br>2017 | 03                | Updated part numbers to include the Cortex M identifier.                                                                   | All  |

| Mar<br>2016 | 02                | Update to reflect new part, revision B (0x0002);<br>Added timing information for most of the peripherals; corrected typos. | All  |

| Dec<br>2015 | 01                | Original issue.                                                                                                            |      |

### MCCR4

Miscellaneous Clock Control Register 4

The Miscellaneous Clock Control Register 4 is the alterntative ADC and NMI Debounce Clock Control register.

|    |    |    |    |    |    |         |    |             |    |    |                   |             |    |    |                                                                    |                                                                                                         |      |                                                                                        |                                                                                                      |                                                                                            |                             |                  |   |      |       |   |    | 0  | x40 | 00_0 | 0A8 |

|----|----|----|----|----|----|---------|----|-------------|----|----|-------------------|-------------|----|----|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------|------------------|---|------|-------|---|----|----|-----|------|-----|

| 31 | 30 | 29 | 28 | 27 | 26 | 25      | 24 | 23          | 22 | 21 | 20                | 19          | 18 | 17 | 16                                                                 | 15                                                                                                      | 14   | 13                                                                                     | 12                                                                                                   | 11                                                                                         | 10                          | 9                | 8 | 7    | 6     | 5 | 4  | 3  | 2   | 1    | 0   |

|    |    |    |    |    |    | ADCCSEL |    |             |    |    |                   | ADUCUIN     |    |    |                                                                    |                                                                                                         |      |                                                                                        |                                                                                                      |                                                                                            |                             | NMICSEL          |   |      |       |   |    |    |     |      |     |

| 0  | 0  | 0  | 0  | 0  |    | 000     |    |             |    |    | 0x                | 00          |    |    |                                                                    | 0                                                                                                       | 0    | 0                                                                                      | 0                                                                                                    | 0                                                                                          |                             | 000              |   |      |       |   | 0> | 01 |     |      |     |

|    |    |    |    |    |    | RW      |    |             |    |    | R١                | N           |    |    |                                                                    |                                                                                                         |      |                                                                                        |                                                                                                      |                                                                                            |                             | RW               |   |      |       |   | R  | w  |     |      |     |

|    |    |    |    |    |    |         |    | 2<br>2<br>1 |    | A  | DCC<br>DCC<br>MID | DIV<br>CSEI | L  |    | 0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | Dax   00   01   10   11   ADC   Deboo   Dax   00   01   10   11   ADC   Deboo   Dax   00   01   10   11 | Cloc | RINO<br>MCL<br>INT<br>Exte<br>PLL<br>k N<br>e Clo<br>RINO<br>MCL<br>INT<br>Exte<br>PLL | G OSC<br>K (t<br>OSC<br>rnal<br>Cloc<br>divi<br>divi<br>divi<br>G OSC<br>K (t<br>OSC<br>rnal<br>Cloc | GC 11<br>DUS (<br>20N<br>I Ma<br>Ck<br>der<br>for N<br>GC 11<br>DUS (<br>20N<br>I Ma<br>Ck | MHz<br>clock<br>MHz<br>in O | s)<br>SC<br>sour |   | elec | t bit |   |    |    |     |      |     |

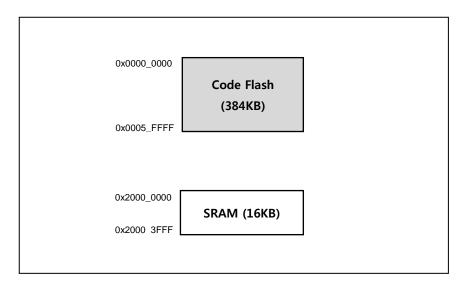

# 8. Internal SRAM

# Overview

The Z32F3841 MCU implements zero-wait on the chip's SRAM. The size of the SRAM is 16 KB. The SRAM base address is  $0 \times 2000 \_ 0000$ .

3

# Registers

The base address of the watchdog timer is  $0 \times 4000_{0200}$  and the register map is listed in Table 10.1. Initial watchdog time-out period is set to 2000-miliseconds.

| Name    | Offset | R/W | Description                  | Reset      |

|---------|--------|-----|------------------------------|------------|

| WDT.LR  | 0x0000 | W   | WDT Load register            | 0x00000000 |

| WDT.CNT | 0x0004 | R   | WDT Current counter register | 0x0000FFFF |

| WDT.CON | 0x0008 | R/W | WDT Control register         | 0x0000805C |

#### Table 10.1. Watchdog Timer Register Map

### WDT.LR Watchdog Timer Load Register

The Watchdog Timer Load register is used to update the WDTCNT register. To update the WDTCNT register, the WEN bit of WDTCON should be set to 1 and written into the WDTLR register with a target value of WDTCNT.

|    |    |    |    |    |    |    |    |    |         |    |     |    |    |    |     |      |      |    |      |      |                          |       |      |      |       | w     | DT.L  | .R=0   | )x40 | 00_( | 0200 | ) |

|----|----|----|----|----|----|----|----|----|---------|----|-----|----|----|----|-----|------|------|----|------|------|--------------------------|-------|------|------|-------|-------|-------|--------|------|------|------|---|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22      | 21 | 20  | 19 | 18 | 17 | 16  | 15   | 14   | 13 | 12   | 11   | 10                       | 9     | 8    | 7    | 6     | 5     | 4     | 3      | 2    | 1    | 0    |   |

|    |    |    |    |    |    |    |    |    |         |    |     |    |    |    | WD  | TLR  |      |    |      |      |                          |       |      |      |       |       |       |        |      |      |      |   |

|    |    |    |    |    |    |    |    |    |         |    |     |    |    | 0x | 000 | )_00 | 00   |    |      |      |                          |       |      |      |       |       |       |        |      |      |      | 1 |

|    |    |    |    |    |    |    |    |    |         |    |     |    |    |    | R   | w    |      |    |      |      |                          |       |      |      |       |       |       |        |      |      |      |   |

|    |    |    |    |    |    |    |    | 3  | 31<br>) | 1  | WDI | LR |    |    | ]   | Keep | oing | WE | N bi | t as | d val<br>'1', w<br>1 wri | vrite | e WI | DTLI | R reg | giste | er wi | ill up | odat | e    |      |   |

# WDT.CNT Watchdog Timer Current Counter Register

The Watchdog Timer Current Counter register represents the current count value of the 32-bit down counter .When the counter value reaches 0, the interrupt or reset is awoken.

|    |    |    |    |    |    |    |    |    |    |    |      |     |    |    |      |      |       |    |      |      |      |     |     |      |     | WD    | T.CI | NT=O | )x40 | 00_( | 0204 |

|----|----|----|----|----|----|----|----|----|----|----|------|-----|----|----|------|------|-------|----|------|------|------|-----|-----|------|-----|-------|------|------|------|------|------|

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20   | 19  | 18 | 17 | 16   | 15   | 14    | 13 | 12   | 11   | 10   | 9   | 8   | 7    | 6   | 5     | 4    | 3    | 2    | 1    | 0    |

|    |    |    |    |    |    |    |    |    |    |    |      |     |    | ١  | WDT  | CN   | г     |    |      |      |      |     |     |      |     |       |      |      |      |      |      |

|    |    |    |    |    |    |    |    |    |    |    |      |     |    | 0x | 0000 | )_FF | FF    |    |      |      |      |     |     |      |     |       |      |      |      |      |      |

|    |    |    |    |    |    |    |    |    |    |    |      |     |    |    | R    | w    |       |    |      |      |      |     |     |      |     |       |      |      |      |      |      |

|    |    |    |    |    |    |    |    | 3  | 1  | W  | /DT( | CNT |    |    |      |      |       | 0  |      |      | ent  |     |     | 0    |     |       |      |      |      |      |      |

|    |    |    |    |    |    |    |    | 0  |    |    |      |     |    |    | 3    | 2-b  | it do | wn | coui | nter | will | run | fro | m th | e w | ritte | n va | lue. |      |      |      |

# **Functional Description**

The MCCR3 register must be configured to enable the clock source and divider for the Watch Dog Timer (WDT) to run. To prevent the WDT from resetting or interrupting, load a new value into the WDTLR register before the WDTCNT reaches 0.

The watchdog timer count is enabled by setting WDTEN (WDT.CON[4]) to 1. When the watchdog timer is enabled, the down counter starts counting from the load value. If WDTRE (WDT.CON[6]) is set to 1, WDT reset is asserted when the WDT counter value reaches 0 (underflow event) from the WDTLR value. Before the WDT counter goes down to 0, the software can write a certain value to the WDTLR register to reload the WDT counter.

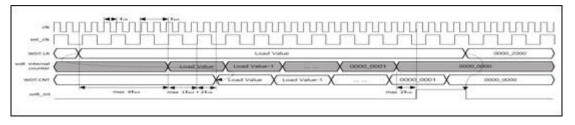

# **Timing Diagram**

Figure 10.2. Timing Diagram in Interrupt Mode Operation when WDT Clock is External Clock

In WDT interrupt mode, after the WDT underflow occurs, a certain count value is reloaded to prevent the next WDT interrupt in a short time period. This reloading action can only be activated when the watchdog timer counter is set to Interrupt mode (set WDTIE of WDT.CON). It takes up to 5 cycles from the load value to the CNT value. The WDT interrupt signal and CNT value data might be delayed by a maximum of 2 system bus clocks in synchronous logic.

### Prescale Table

The WDT includes a 32-bit down counter with programmable prescaler to define different time-out intervals.

The clock sources of the watchdog timer can include the peripheral clock (PCLK) or one of 3 external clock sources. An external clock source can be enabled by CKSEL (WDT.CON[3]) set to '1' and external clock source chosen in MCCR3 register of the System Control Unit block.

To make the WDT counter base clock, users can control the 3-bit prescaler WPRS [2:0] in the WDT.CON register and the maximum prescaled value is "clock source frequency/256". The prescaled WDT counter clock frequency values are listed in Table 10.2.

### Selectable clock source (40 kHz ~ 16 MHz) and the time out interval when 1 count

Time out period = {(Load Value) \* (1/pre-scaled WDT counter clock frequency) + max 5T<sub>ext</sub>} + max 4T<sub>clk</sub>

\*Time out period (time out period from load Value to interrupt set '1')

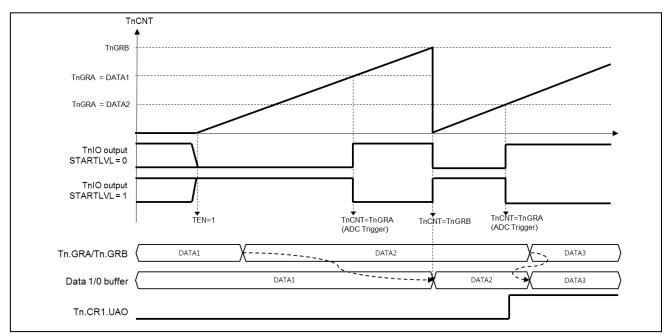

# **PWM Timer Output**

Figure 11.5 shows the timing diagram in PWM output mode. The Tn.GRB value decides the PWM pulse period. An additional comparison point is provided with the Tn.GRA register value which defines the pulse width of PWM output.

### Figure 11.5. PWM Output Operation

The period of PWM pulse can be calculated as shown in the following equation:

### The period = TMCLK Period \* Tn.GRB value Match A interrupt time = TMCLK Period \* Tn.GRA value

If Tn.GRB = 0, the timer cannot be started even if TnCR2.TEN is "1" because the period is "0".

The value in Tn.GRA and Tn.GRB is loaded into the internal compare data buffer 0 and 1 when the loading condition occurs. In this periodic mode with TnCR1.UAO =0, the Tn.CR2.TCLR write operation and the GRB match event will load the compare data buffers.

When TnCR1.UAO is 1, the internal compare data buffer is updated when the Tn.GRA or Tn.GRB data is updated.

The TnIO output signal generates a PWM pulse. The Tn.GRB value defines the output pulse period and the Tn.GRA value defines the pulse width of one shot pulse. The active level of the PWM pulse can be controlled by the Tn.CR1.STARTLVL bit value.

ADC Trigger generation is available at Match A interrupt time.

#### Imer

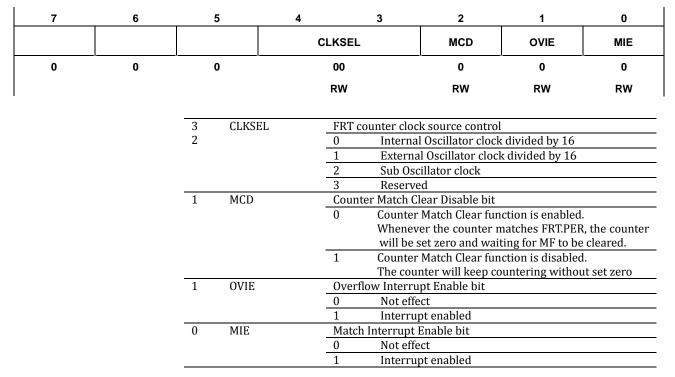

### FRT.MR FRT Mode Register

FRT is a 32-bit up counter. It can be used in power down mode. The SUB OSC clock is directly connected to FRT. The clock is uncontrollable in the SCU block. The FRT Mode Register is an 8-bit register.

#### FRTMR=0x4000\_0600

# FRT.CR FRT Control Register

The FRT Control register is an 8-bit register.

#### FRTCR=0x4000\_3E04

| 7 | 6 | 5 | 4 | 3      | 2    | 1     | 0   |

|---|---|---|---|--------|------|-------|-----|

|   |   |   |   | CNTREQ | FCLR | FHOLD | FEN |

| 0 | 0 | 0 | 0 | 0      | 0    | 0     | 0   |

|   |   |   |   | RW     | wo   | R/W   | R/W |

| 3 | CNTREQ | FRT Counter read request bit                                 |

|---|--------|--------------------------------------------------------------|

|   |        | 0 No                                                         |

|   |        | 1 Request to read FCNT (cleared when CNTACK(FSR[1]) is high) |

| 2 | FCLR   | FRT Counter register clear bit                               |

|   |        | 0 No                                                         |

|   |        | 1 Clear the counter                                          |

| 1 | FHOLD  | FRT Counter register hold bit                                |

|   |        | 0 No                                                         |

|   |        | 1 Hold the counter                                           |

| 0 | FEN    | FRT enable bit                                               |

|   |        | 0 FRT Disabled                                               |

|   |        | 1 FRT Enabled                                                |

#### .....

# FRT.PER FRT Period Match Register

The FRT Period Match register is a 32-bit register.

### FRTPER=0x4000\_3E08

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20  | 19 | 18 | 17 | 16  | 15   | 14   | 13    | 12  | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|-----|------|------|-------|-----|----|----|---|---|---|---|---|---|---|---|---|---|

|    |    |    |    |    |    |    |    |    |    |    |     |    |    |    | DA  | TA   |      |       |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |     |    |    | 0x | 000 | 0_00 | 00   |       |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |     |    |    |    | R   | W    |      |       |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |     |      |      |       |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    | 3  | 2  | D  | ATA |    |    |    | F   | RT 1 | mate | ch da | ata |    |    |   |   |   |   |   |   |   |   |   |   |

# FRT.CNT FRT Counter Register

0

The FRT Counter Register is a 32-bit register.

#### FRTCNT=0x4000\_3E0C

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23     | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15   | 14   | 13   | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|--------|----|----|----|----|----|----|-----|------|------|------|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    |    |    |    |    |    |    |    |        |    |    |    |    |    |    | CI  | Т    |      |      |    |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    |        |    |    |    |    |    | 0x | 000 | 0_00 | 00   |      |    |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    |        |    |    |    |    |    |    | R   | 0    |      |      |    |    |    |   |   |   |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    | 3<br>0 | 2  | C  | NT |    |    |    | F   | RT ( | Coui | nter |    |    |    |   |   |   |   |   |   |   |   |   |   |

# **FRT.SRFRT Status Register**

|   |   |     |     | FRT Status                 | Register is an 8-                                                                       | bit register.FRTS | SR=0x4000_06  |

|---|---|-----|-----|----------------------------|-----------------------------------------------------------------------------------------|-------------------|---------------|

| 7 | 6 | 5   | 4   | 3                          | 2                                                                                       | 1                 | 0             |

|   |   |     |     |                            | RACK                                                                                    | OVIF              | MIF           |

| 0 | 0 | 0   | 0   | 0                          | 0                                                                                       | 0                 | 0             |

|   |   |     |     |                            | WC1                                                                                     | WC1               | WC1           |

|   |   | 2 R | АСК | Read Counter A             | 0                                                                                       |                   |               |

|   |   |     |     |                            | to read CNT value<br>ead CNT value                                                      | е                 |               |

|   |   | 1 0 | VIF |                            | upt flag bit<br>nterrupt did not<br>nterrupt occurre                                    |                   |               |

|   |   | 0 M | IIF | 1 Match Inte<br>In Counter | flag bit<br>prrupt did not occ<br>rrupt occurred<br>Match Clear mo<br>cing the counter. |                   | ld be cleared |

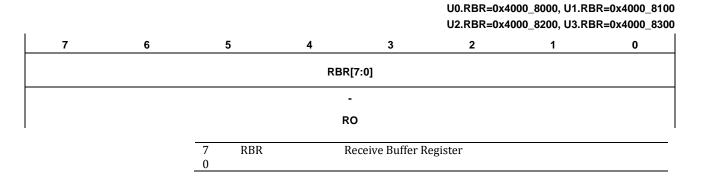

# Un.RBR

# **Receive Buffer Register**

The UART Receive Buffer Register is an 8-bit read-only register.

# Un.THR Transmit Data Hold Register

The UART Transmit Data Hold Register is an 8-bit write-only register.

### U0.THR=0x4000\_8000, U1.THR=0x4000\_8100 U2.THR=0x4000\_8200, U3.THR=0x4000\_8300

| 7 | 6 | 5   | 4  | 3               | 2            | 1 | 0 |

|---|---|-----|----|-----------------|--------------|---|---|

|   |   |     | т  | HR              |              |   |   |

|   |   |     |    |                 |              |   |   |

|   |   |     |    | -               |              |   |   |

|   |   |     | v  | 10              |              |   |   |

|   |   | 7 T | HR | Fransmit Data H | old Register |   |   |

|   |   | 0   |    |                 | -            |   |   |

# Un.LCR UART Line Control Register

The UART Line Control Register is an 8-bit register.

| U0.LCR=0x4000_800C, U1.LCR=0x4000_810C | • |

|----------------------------------------|---|

| U2.LCR=0x4000_820C, U3.LCR=0x4000_830C | ; |

| 7 | 6      | 5       | 4                                     | 3                                                                             | 2                                        | 1                 | 0               |  |  |

|---|--------|---------|---------------------------------------|-------------------------------------------------------------------------------|------------------------------------------|-------------------|-----------------|--|--|

|   | BREAK  | STICKP  | PARITY                                | PEN                                                                           | STOPBIT                                  | DL                | EN              |  |  |

| 0 | 0      | 0       | 0                                     | 0                                                                             | 0                                        | 0                 | 0               |  |  |

|   | R/W    | R/W     | R/W                                   | R/W                                                                           | R/W                                      | R/W               | R/W             |  |  |

|   | 6      | BREAK   | notice the                            | bit is set, TxD p<br>alert to the reco<br>ormal transfer m<br>eak transmit mo | ode                                      | at low state in c | order to        |  |  |

|   | 5      | STICKP  | Force pari<br>0 Pa                    | ty and it will be<br>rity stuck is disa                                       | effective when P                         |                   | DADITY          |  |  |

|   | 4      | PARITY  | Parity mo<br>0 Od                     |                                                                               | and stuck parity s                       |                   | JIL OF PARTY I. |  |  |

|   | 3      | PEN     | Parity bit<br>0 Th                    | transfer enable<br>e parity bit disa<br>e parity bit enab                     |                                          |                   |                 |  |  |

|   | 2      | STOPBIT | The numb   0 1 s   1 1.5   In In      | er of stop bit fol<br>stop bit<br>5 / 2 stop bit                              | lowed by data bit<br>a case, 1.5 stop bi |                   | se of 6,7 or    |  |  |

|   | 1<br>0 | DLEN    | The data l   00 5 k   01 6 k   10 7 k | ength in one tra<br>pit data<br>pit data<br>pit data<br>pit data<br>pit data  |                                          |                   |                 |  |  |

The parity bit is generated according to bits 3,4,5 of the UnLCR register. Table 13.4 shows the variation of parity bit generation.

|        | Table 13.4. Parity Bit Generation |     |                     |  |  |  |  |  |  |  |

|--------|-----------------------------------|-----|---------------------|--|--|--|--|--|--|--|

| STICKP | PARITY                            | PEN | Parity              |  |  |  |  |  |  |  |

| Х      | Х                                 | 0   | No Parity           |  |  |  |  |  |  |  |

| 0      | 0                                 | 1   | Odd Parity          |  |  |  |  |  |  |  |

| 0      | 1                                 | 1   | Even Parity         |  |  |  |  |  |  |  |

| 1      | 0                                 | 1   | Force parity as "1" |  |  |  |  |  |  |  |

| 1      | 1                                 | 1   | Force parity as "0" |  |  |  |  |  |  |  |

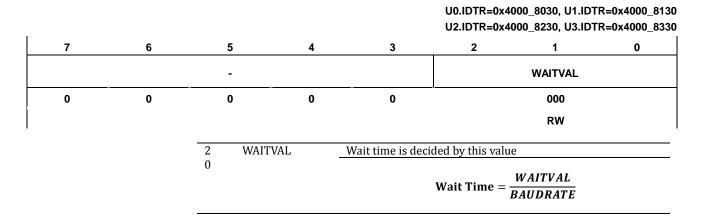

# Un.IDTR

### Inter-frame Delay Time Register

The UART Inter-frame Time Register is an 8-bit register. A dummy delay can be inserted between two continuous transmits.

# **Functional Description**

The UART module is compatible with the 16450 UART. Additionally, dedicated DMA channels and fractional baud rate compensation logic are provided. The UART does not have an internal FIFO block. Therefore, data transfers are established interactively or with DMA support.

Two DMA channels are provided for each UART module – one channel for TX transfer and the other channel for RX transfer. Each channel has a 32-bit memory address register and a 16-bit transfer counter register. Prior to the DMA operation, the DMA memory address register and transfer count register should be configured. For the RX operation, the memory address is the destination memory address and for the TX operation, the memory address.

The transfer counter register stores the number of data transfers. When a single transfer is done, the counter is decremented by 1. When the counter reaches zero, the DMA done flag is delivered to the UART control block. If the interrupt is enabled, this flag generates the interrupt.

# **Receiver Sampling Timing**

The UART operates per the following timing:

If the falling edge is on the receive line, the UART judges it as the start bit. From the start timing, the UART oversamples 16 times of 1-bit and detects the bit value at the 7th sample of 16 samples.

# **Pin Description**

| PIN NAME | NAME TYPE DESCRIPTION |                                                               |  |  |  |  |

|----------|-----------------------|---------------------------------------------------------------|--|--|--|--|

| SCL0     | I/O                   | I <sup>2</sup> C channel 0 Serial clock bus line (open-drain) |  |  |  |  |

| SDA0     | I/O                   | I <sup>2</sup> C channel 0 Serial data bus line (open-drain)  |  |  |  |  |

| SCL1     | I/O                   | I <sup>2</sup> C channel 1 Serial clock bus line (open-drain) |  |  |  |  |

| SDA1     | I/O                   | l <sup>2</sup> C channel 1 Serial data bus line (open-drain)  |  |  |  |  |

### Table 15.1. I<sup>2</sup>C Interface External Pins

# Registers

The base address of  $I^2C0$  is  $0x4000\_A000$  and the base address of  $I^2C1$  is  $0x4000\_A100$ . The register map is described in Tables 15.2 and 15.3.

| Table 15.2. I <sup>2</sup> C Interface Base Address |             |  |  |  |  |  |

|-----------------------------------------------------|-------------|--|--|--|--|--|

| Channel Base address                                |             |  |  |  |  |  |

| l <sup>2</sup> C0                                   | 0x4000_A000 |  |  |  |  |  |

| l <sup>2</sup> C1                                   | 0x4000_A100 |  |  |  |  |  |

| Name     | Offset | R/W    | Description                                      | Reset  |  |

|----------|--------|--------|--------------------------------------------------|--------|--|

| IC0.DR   | 0xA000 | R/W    | I <sup>2</sup> C0 Data Register                  | 0xFF   |  |

| IC0.SR   | 0xA008 | R, R/W | I <sup>2</sup> C0 Status Register                | 0x00   |  |

| IC0.SAR  | 0xA00C | R/W    | I <sup>2</sup> C0 Slave Address Register         | 0x00   |  |

| IC0.CR   | 0xA014 | R/W    | I <sup>2</sup> C0 Control Register               | 0x00   |  |

| IC0.SCLL | 0xA018 | R/W    | I <sup>2</sup> C0 SCL LOW duration Register      | 0xFFFF |  |

| IC0.SCLH | 0xA01C | R/W    | I <sup>2</sup> C0 SCL HIGH duration Register     | 0xFFFF |  |

| IC0.SDH  | 0xA020 | R/W    | I <sup>2</sup> C0 SDA Hold Register              | 0x7F   |  |

| IC1.DR   | 0xA100 | R/W    | I <sup>2</sup> C1 Data Register                  | 0xFF   |  |

| IC1.SR   | 0xA108 | R, R/W | I <sup>2</sup> C1 Status Register                | 0x00   |  |

| IC1.SAR  | 0xA10C | R/W    | I <sup>2</sup> C1 Slave Address Register         | 0x00   |  |

| IC1.CR   | 0xA114 | R/W    | I <sup>2</sup> C1 Control Register               | 0x00   |  |

| IC1.SCLL | 0xA118 | R/W    | I <sup>2</sup> C1 SCL LOW duration Register      | 0xFFFF |  |

| IC1.SCLH | 0xA11C | R/W    | I <sup>2</sup> C1 SCL HIGH duration Register 0xf |        |  |

| IC1.SDH  | 0xA120 | R/W    | I <sup>2</sup> C1 SDA Hold Register 0x0          |        |  |

### Table 15.3. I<sup>2</sup>C Register Map

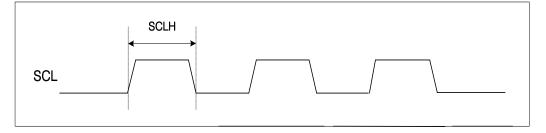

# ICn.SCLH

# I<sup>2</sup>C SCL HIGH Duration Register

ICnSCLH is a 16-bit read/write register. The SCL HIGH time is set by writing this register in master mode.

|    |    |    |    |      |     |         |          |         | IC     | CO.SDLH | =0x400 | D_A01C, | IC1.SDL | .H=0x40 | 00_A11C |

|----|----|----|----|------|-----|---------|----------|---------|--------|---------|--------|---------|---------|---------|---------|

| 15 | 14 | 13 | 12 | 11   | 10  | 9       | 8        | 7       | 6      | 5       | 4      | 3       | 2       | 1       | 0       |

|    |    |    |    |      |     |         | sc       | LH      |        |         |        |         |         |         |         |

|    |    |    |    |      |     |         | 0xF      | FFF     |        |         |        |         |         |         |         |

|    |    |    |    |      |     |         | R        | w       |        |         |        |         |         |         |         |

|    |    |    |    |      |     |         |          |         |        |         |        |         |         |         |         |

|    |    |    | 15 | SCLH |     |         | uration  |         |        |         |        |         |         |         |         |

|    |    |    |    |      | SCL | H = (P) | CLK * SC | LH[15:0 | )])+3I | PCLKs   |        |         |         |         |         |

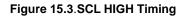

A message which starts with such an address can be terminated by generation of a STOP conditions, even during the transmission of a byte. In this case, no acknowledge is generated.

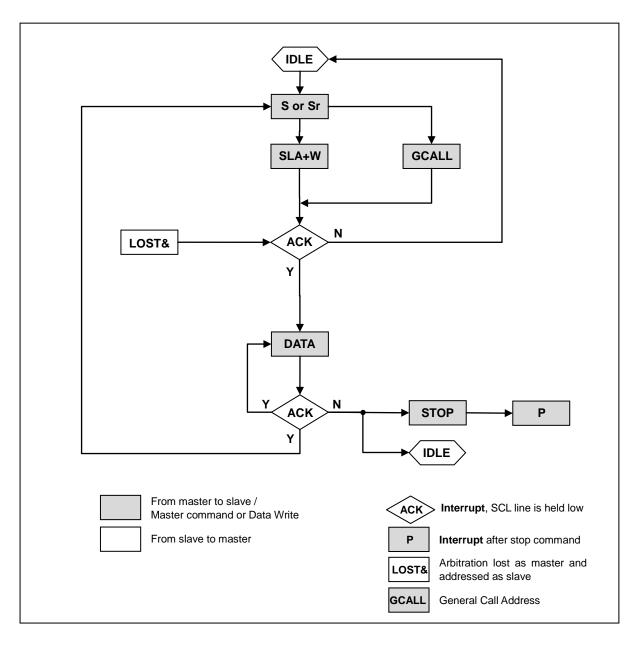

Figure 15.7. I<sup>2</sup>C Bus Data Transfer

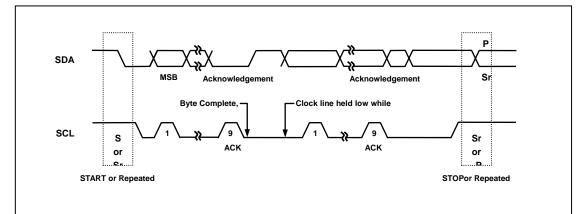

# **Slave Transmitter**

The slave transmitter shows the flow of the transmitter in Slave mode, as shown in Figure 15.13.

Figure 15.13. Transmitter Flowchart in Slave Mode

### Slave Receiver

The slave receiver shows the flow of the receiver in Slave mode, as shown in Figure 15.14.

Figure 15.14. Receiver Flowchart in Slave Mode

#### Z32F3841 Product Specification

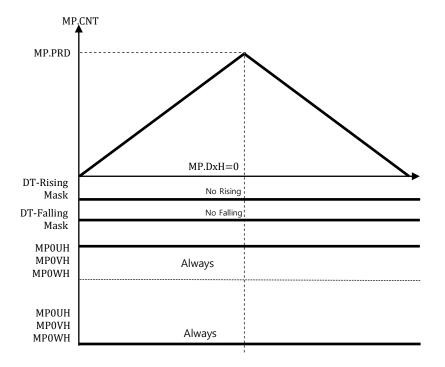

|            | Table 16.1. MPWM Register Map |         |             |            |  |  |  |  |  |  |

|------------|-------------------------------|---------|-------------|------------|--|--|--|--|--|--|

|            | Level                         | NORM    | IAL mode    | MOTOR mode |  |  |  |  |  |  |

| PWM Output | Levei                         | UP mode | UPDOWN mode | MOTOR mode |  |  |  |  |  |  |

| WH         | Default level                 | LOW     | HIGH        | LOW        |  |  |  |  |  |  |

| VVI        | Active level                  | HIGH    | LOW         | HIGH       |  |  |  |  |  |  |

| WL         | Default level                 | LOW     | LOW         | HIGH       |  |  |  |  |  |  |

| VVL        | Active level                  | HIGH    | HIGH        | LOW        |  |  |  |  |  |  |

| VH         | Default level                 | LOW     | HIGH        | LOW        |  |  |  |  |  |  |

| VП         | Active level                  | HIGH    | LOW         | HIGH       |  |  |  |  |  |  |

| VL         | Default level                 | LOW     | LOW         | HIGH       |  |  |  |  |  |  |

| VL         | Active level                  | HIGH    | HIGH        | LOW        |  |  |  |  |  |  |

| UH         | Default level                 | LOW     | HIGH        | LOW        |  |  |  |  |  |  |

| ОП         | Active level                  | HIGH    | LOW         | HIGH       |  |  |  |  |  |  |

| UL         | Default level                 | LOW     | LOW         | HIGH       |  |  |  |  |  |  |

| UL         | Active level                  | HIGH    | HIGH        | LOW        |  |  |  |  |  |  |

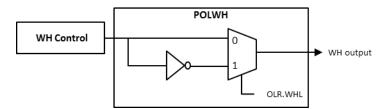

Figure 16.2 shows the polarity control block. This is an example of WH signal polarity control.

Figure 16.2 Polarity Control Block

#### **MPn.FOR MPWM Force Output Level Register**

The PWM force output register is an 8-bit register. The PWM output level can be forced by an abnormal event from an external or user-intended condition. When the forced condition occurs, each PWM output level which is programmed in the FOLR register will be forced.

| 7 | 6 |   | 5    | 4    | 3               | 2                | 1    | 0    |

|---|---|---|------|------|-----------------|------------------|------|------|

|   |   | W | HFL  | VHFL | UHFL            | WLFL             | VLFL | ULFL |

| 0 | 0 |   | 0    | 0    | 0               | 0                | 0    | 0    |

|   |   | F | w    | RW   | RW              | RW               | RW   | RW   |

|   |   | 5 | WHFL |      | Select WH Outp  | ut Force Level   |      |      |

|   |   |   |      |      |                 | rce Level is 'L' |      |      |

|   |   |   |      |      | 1 Output For    | rce Level is 'H' |      |      |

|   |   | 4 | VHFL |      | Select VH Outpu | it Force Level   |      |      |

|   |   |   |      |      | ) Output For    | rce Level is 'L' |      |      |

|   |   |   |      |      | 1 Output For    | rce Level is 'H' |      |      |

|   |   | 3 | UHFL |      | Select UH Outpu | ıt Force Level   |      |      |

|   |   |   |      |      | ) Output For    | rce Level is 'L' |      |      |

### MP0.FOR=0x4000\_4008, MP1.FOR=0x4000\_5008,

Figure 16.17. L-side Always On (T<sub>DUTY</sub>='0': Dead-time Disabled)

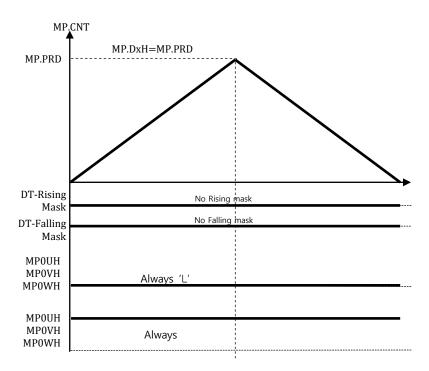

# Symmetrical Mode vs Asymmetrical Mode

In symmetrical mode, the wave form is symmetrical on both sides of the mid-point of the period. The duty comparison is performed twice in both up and down count periods.

### ADn.SR

# ADCn Status Register

The ADC Status Register is a 32-bit register.

AD0.SR=0x4000\_B024, AD1.SR=0x4000\_B124

| 7   | 6     | 5                                                                                              | 4         | 3              | 2                                     | 1                | 0             |

|-----|-------|------------------------------------------------------------------------------------------------|-----------|----------------|---------------------------------------|------------------|---------------|

| EOC | ABUSY | DOVR                                                                                           | JN DMAIRQ | TRGIRQ         | EOSIRQ                                | -                | EOCIRC        |

| 0   | 0     | 0                                                                                              | 0         | 0              | 0                                     | -                | 0             |

| RO  | RO    | RO                                                                                             | RO        | RC             | RC                                    | -                | RC            |

|     |       | 7                                                                                              | EOC       |                | -of-Conversion fla<br>Conversion made | 0                | lears this bi |

|     |       | 6 ABUSY ADC conversion busy flag                                                               |           |                |                                       |                  |               |

|     |       | 5 DOVRUN DMA overrun flag (not interrupt)<br>(DMA ACK didn't come until end of next conversion |           |                |                                       |                  | onversion)    |

|     |       | 4                                                                                              | DMAIRQ    |                | e received (DMA                       |                  |               |

|     |       | 3                                                                                              | TRGIRQ    |                | ger interrupt flag                    |                  | ear flag)     |

|     |       | 2                                                                                              | EOSIRQ    |                | will be set up<br>" to clear flag)    | on final end o   | f a sequend   |

|     |       |                                                                                                |           | 0 Nor<br>1 End | ne.<br>I-of-Sequence(bu               | rst) Interrupt o | occurred      |

|     |       | 0                                                                                              | EOCIRQ    |                | g will be set u<br>is occurred(Wri    |                  |               |

|     |       |                                                                                                |           | 0 Nor<br>1 End | ne.<br>I-of-Conversion I              | nterrupt occurr  | ed            |

AD*n.*IER

# Interrupt Enable Register

### AD0.IER=0x4000\_B028, AD1.IER=0x4000\_B128

| 7 | 6 | 5 | 4       | 3       | 2       | 1 | 0       |

|---|---|---|---------|---------|---------|---|---------|

|   |   |   | DMAIRQE | TRGIRQE | EOSIRQE | - | EOCIRQE |

|   |   |   | 0       | 0       | 0       | - | 0       |

|   |   |   | RW      | RW      | RW      | - | RW      |

| 4 | DMAIRQE | DMA done interrupt enable<br>0: interrupt disable<br>1: interrupt enable |

|---|---------|--------------------------------------------------------------------------|

| 3 | TRGIRQE | ADC trigger conversion interrupt enable                                  |

| 2 | EOSIRQE | ADC sequence conversion interrupt enable                                 |

| 0 | EOCIRQE | ADC single conversion interrupt enable                                   |

### **General ADC Setup Procedure**

- 1. Allow the modification of the I/O pins to use the ADC inputs needed by writing the unlock sequence as described in PORT CONTROL UNIT (PCU), no pullups enabled.

- 2. Enable the ADC peripherals needed in PER2 register.

- 3. Enable the ADC peripheral clock in the PCER2 register.

- 4. Select the alternating function for the ADC inputs (Port n MUX registers).

- 5. Configure the ADC Pins to Analog

- 6. Configure the ADC mode in the ADCnMODE register and enabled the channel ADCn.

- 7. Configure the ADCnCR1 register and write an appropriate clock divider value.

- 8. Configure any special features such as triggers, sequencing, etc.

- 9. Start ADC conversion

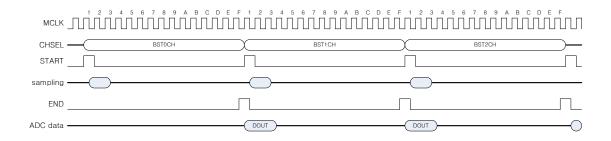

### ADC Single Mode Timing Diagram

| MCLK       |        |

|------------|--------|

| START      |        |

| sampling - | sample |

| END        |        |

| ADC data - | DOUT   |

# ADC Sequencing Mode Timing Diagram