### Silicon Labs - C8051F350 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 50MHz                                                       |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART            |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                  |

| Number of I/O              | 17                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                |                                                             |

| RAM Size                   | 768 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | A/D 8x24b; D/A 2x8b                                         |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-LQFP                                                     |

| Supplier Device Package    | 32-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f350 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. System Overview

C8051F350/1/2/3 devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 50 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- 24 or 16-bit single-ended/differential ADC with analog multiplexer

- Two 8-bit Current Output DACs

- Precision programmable 24.5 MHz internal oscillator

- 8 kB of on-chip Flash memory

- 768 bytes of on-chip RAM

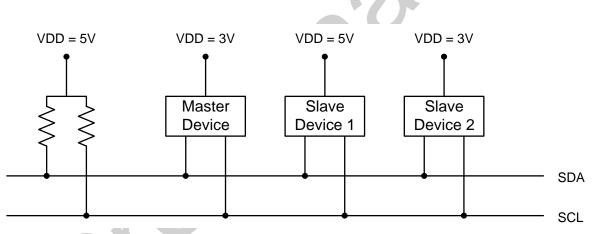

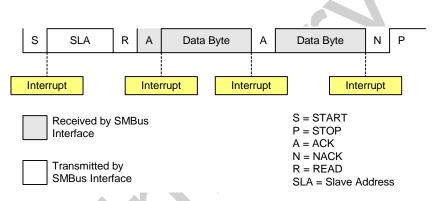

- SMBus/I2C, Enhanced UART, and SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

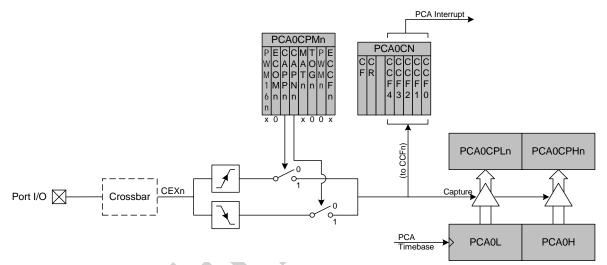

- Programmable counter/timer array (PCA) with three capture/compare modules and watchdog timer function

- On-chip power-on reset, V<sub>DD</sub> monitor, and temperature sensor

- On-chip voltage comparator

- 17 Port I/O (5 V tolerant)

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051F350/1/2/3 devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 2.7 V-to-3.6 V operation over the industrial temperature range (-45 to +85 °C). The Port I/O and /RST pins are tolerant of input signals up to 5 V. The C8051F350/1/2/3 are available in 28-pin MLP or 32-pin LQFP packaging, as shown in Figure 1.1 through Figure 1.4.

## 1.2. On-Chip Debug Circuitry

The C8051F350/1/2/3 devices include on-chip Silicon Labs 2-Wire (C2) debug circuitry that provides non-intrusive, full speed, in-circuit debugging of the production part *installed in the end application*.

Silicon Labs' debugging system supports inspection and modification of memory and registers, breakpoints, and single stepping. No additional target RAM, program memory, timers, or communications channels are required. All the digital and analog peripherals are functional and work correctly while debugging. All the peripherals (except for the ADC and SMBus) are stalled when the MCU is halted, during single stepping, or at a breakpoint in order to keep them synchronized.

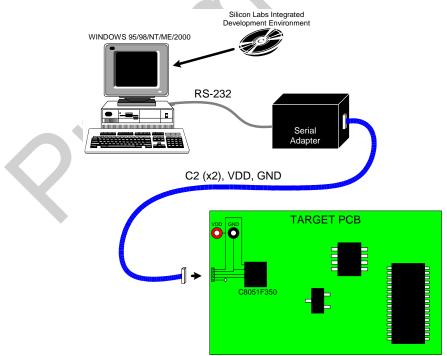

The C8051F350DK development kit provides all the hardware and software necessary to develop application code and perform in-circuit debugging with the C8051F350/1/2/3 MCUs. The kit includes software with a developer's studio and debugger, an integrated 8051 assembler, and an RS-232 to C2 serial adapter. It also has a target application board with the associated MCU installed and prototyping area, plus the RS-232 and C2 cables, and wall-mount power supply. The Development Kit requires a Windows 95/98/NT/ME/2000 computer with one available RS-232 serial port. As shown in Figure 1.5, the PC is connected via RS-232 to the Serial Adapter. A six-inch ribbon cable connects the Serial Adapter to the user's application board, picking up the two C2 pins,  $V_{DD}$ , and GND. The Serial Adapter takes its power from the application board. For applications where there is not sufficient power available from the target board, the provided power supply can be connected directly to the Serial Adapter.

The Silicon Labs IDE interface is a vastly superior developing and debugging configuration, compared to standard MCU emulators that use on-board "ICE Chips" and require the MCU in the application board to be socketed. Silicon Labs' debug paradigm increases ease of use and preserves the performance of the precision analog peripherals.

Figure 1.5. Development/In-System Debug Diagram

| Figure 5.20. / | ADC0H: ADC0 C | conversion Regis | ster (SINC3 Filter | ) High Byte |

|----------------|---------------|------------------|--------------------|-------------|

|                |               | <u> </u>         |                    | /           |

| R/W       | R/W       | R/W        | R/W          | R/W         | R/W           | R/W   | R/W        | Reset Value |

|-----------|-----------|------------|--------------|-------------|---------------|-------|------------|-------------|

|           |           |            | AD           | C0H         |               |       |            | 0000000     |

| Bit7      | Bit6      | Bit5       | Bit4         | Bit3        | Bit2          | Bit1  | Bit0       |             |

|           |           |            |              |             |               |       | SFR Addres | s: 0xC5     |

| Bits 7-0: | ADC0H: AD | C0 Convers | sion Registe | er (SINC3 F | ilter) Hiah B | svte. |            |             |

## Figure 5.21. ADC0M: ADC0 Conversion Register (SINC3 Filter) Middle Byte

| 5.44      | <b>5</b> 444                                                  | 5.44         | -            | 5.44          |               | 5.4.4   | -          | 5           |

|-----------|---------------------------------------------------------------|--------------|--------------|---------------|---------------|---------|------------|-------------|

| R/W       | R/W                                                           | R/W          | R/W          | R/W           | R/W           | R/W     | R/W        | Reset Value |

|           |                                                               |              | AD           | COM           |               |         |            | 00000000    |

| Bit7      | Bit6                                                          | Bit5         | Bit4         | Bit3          | Bit2          | Bit1    | Bit0       |             |

|           |                                                               |              |              |               |               |         | SFR Addres | s: 0xC4     |

| Bits 7-0: | ADC0M: AD0<br>C8051F350/<br>result.<br>C8051F352/3<br>result. | 1: This regi | ster contain | s bits 15-8 d | of the 24-bit | ADC SIN |            |             |

## Figure 5.22. ADC0L: ADC0 Conversion Register (SINC3 Filter) Low Byte

| R/W       | R/W                                               | R/W          | R/W          | R/W          | R/W          | R/W      | R/W           | Reset Value |

|-----------|---------------------------------------------------|--------------|--------------|--------------|--------------|----------|---------------|-------------|

|           |                                                   |              | AD           | COL          |              |          |               | 0000000     |

| Bit7      | Bit6                                              | Bit5         | Bit4         | Bit3         | Bit2         | Bit1     | Bit0          |             |

|           |                                                   |              |              |              |              |          | SFR Addres    | s: 0xC3     |

| Bits 7-0: | ADC0L: ADC<br>C8051F350/<br>result.<br>C8051F352/ | 1: This regi | ster contair | s bits 7-0 o | f the 24-bit | ADC SINC | 3 filter conv | version     |

| R/W       | R/W         | R/W                       | R/W         | R/W     | R         | R/W  | R/W        | Reset Value |

|-----------|-------------|---------------------------|-------------|---------|-----------|------|------------|-------------|

| IDA0EN    |             | IDA0CM                    |             | IDA0CSC | -         | -    |            | 01110000    |

| Bit7      | Bit6        | Bit5                      | Bit4        | Bit3    | Bit2      | Bit1 | Bit0       |             |

|           |             |                           |             |         |           |      | SFR Addres | s: 0xB9     |

|           |             |                           |             |         |           |      |            |             |

| Bit 7:    | IDA0EN: ID  | A0 Enable.                |             |         |           |      |            |             |

|           | 0: IDA0 Dis | abled.                    |             |         |           |      |            |             |

|           | 1: IDA0 Ena | abled.                    |             |         |           |      |            |             |

| Bits 6-4: |             | 0]: IDA0 Upda             |             |         |           |      |            |             |

|           |             | utput update              |             |         |           |      |            |             |

|           |             | utput update              |             |         |           |      |            |             |

|           |             | utput update              |             |         |           |      |            |             |

|           |             | utput update              |             |         |           |      |            |             |

|           |             | utput update              | •           | •       |           |      |            |             |

|           |             | utput update              |             |         |           |      |            |             |

|           |             | utput updates             |             |         | STR.      |      |            |             |

| D'' O     |             | utput updates             |             |         |           |      |            |             |

| Bit 3:    |             | DA0 Constar               |             |         |           | I    |            |             |

|           |             | draw on V <sub>DD</sub> i |             |         |           |      |            |             |

|           |             | draw on V <sub>DD</sub> i |             |         | Output We | ord. |            |             |

| Bit 2:    |             | ead = 0b, Wri             |             |         |           |      |            |             |

| Bits 1:0: |             | 1:0]: IDA0 Ou             |             |         |           |      |            |             |

|           |             | A full-scale ou           |             |         |           |      |            |             |

|           |             | full-scale out            |             |         |           |      |            |             |

|           |             | full-scale out            |             |         |           |      |            |             |

|           | 11: 2.0 mA  | full-scale out            | out current | t.      |           |      |            |             |

|           |             |                           |             |         |           |      |            |             |

## Figure 6.3. IDA0CN: IDA0 Control Register

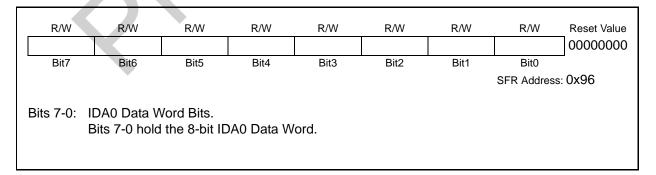

## Figure 6.4. IDA0: IDA0 Data Word Register

| Mnemonic            | Description                                    | Bytes | Clock       |

|---------------------|------------------------------------------------|-------|-------------|

| MOV @Ri, direct     | Move direct byte to indirect RAM               | 2     | Cycles<br>2 |

| MOV @Ri, #data      | Move immediate to indirect RAM                 | 2     | 2           |

| MOV DPTR, #data16   | Load DPTR with 16-bit constant                 | 3     | 3           |

| MOVC A, @A+DPTR     | Move code byte relative DPTR to A              | 1     | 3           |

| MOVC A, @A+PC       | Move code byte relative PC to A                | 1     | 3           |

| MOVX A, @Ri         | Move external data (8-bit address) to A        | 1     | 3           |

| MOVX @Ri, A         | Move A to external data (8-bit address)        | 1     | 3           |

| MOVX A, @DPTR       | Move external data (16-bit address) to A       | 1     | 3           |

| MOVX @DPTR, A       | Move A to external data (16-bit address)       | 1     | 3           |

| PUSH direct         | Push direct byte onto stack                    | 2     | 2           |

| POP direct          | Pop direct byte from stack                     | 2     | 2           |

| XCH A, Rn           | Exchange Register with A                       | 1     | 1           |

| XCH A, direct       | Exchange direct byte with A                    | 2     | 2           |

| XCH A, @Ri          | Exchange indirect RAM with A                   | 1     | 2           |

| XCHD A, @Ri         | Exchange low nibble of indirect RAM with A     | 1     | 2           |

|                     | Boolean Manipulation                           |       |             |

| CLR C               | Clear Carry                                    | 1     | 1           |

| CLR bit             | Clear direct bit                               | 2     | 2           |

| SETB C              | Set Carry                                      | 1     | 1           |

| SETB bit            | Set direct bit                                 | 2     | 2           |

| CPL C               | Complement Carry                               | 1     | 1           |

| CPL bit             | Complement direct bit                          | 2     | 2           |

| ANL C, bit          | AND direct bit to Carry                        | 2     | 2           |

| ANL C, /bit         | AND complement of direct bit to Carry          | 2     | 2           |

| ORL C, bit          | OR direct bit to carry                         | 2     | 2           |

| ORL C, /bit         | OR complement of direct bit to Carry           | 2     | 2           |

| MOV C, bit          | Move direct bit to Carry                       | 2     | 2           |

| MOV bit, C          | Move Carry to direct bit                       | 2     | 2           |

| JC rel              | Jump if Carry is set                           | 2     | 2/3         |

| JNC rel             | Jump if Carry is not set                       | 2     | 2/3         |

| JB bit, rel         | Jump if direct bit is set                      | 3     | 3/4         |

| JNB bit, rel        | Jump if direct bit is not set                  | 3     | 3/4         |

| JBC bit, rel        | Jump if direct bit is set and clear bit        | 3     | 3/4         |

|                     | Program Branching                              |       |             |

| ACALL addr11        | Absolute subroutine call                       | 2     | 3           |

| LCALL addr16        | Long subroutine call                           | 3     | 4           |

| RET                 | Return from subroutine                         | 1     | 5           |

| RETI                | Return from interrupt                          | 1     | 5           |

| AJMP addr11         | Absolute jump                                  | 2     | 3           |

| LJMP addr16         | Long jump                                      | 3     | 4           |

|                     | Short jump (relative address)                  | 2     | 3           |

| JMP @A+DPTR         | Jump indirect relative to DPTR                 | 1     | 3           |

| JZ rel              | Jump if A equals zero                          | 2     | 2/3         |

| JNZ rel             | Jump if A does not equal zero                  | 2     | 2/3         |

| CJNE A, direct, rel | Compare direct byte to A and jump if not equal | 3     | 3/4         |

### Table 10.1. CIP-51 Instruction Set Summary (Continued)

| R/W       | R/W                           | R/W         | R/W          | R/W           | R/W         | R/W           | R/W         | Reset Value |

|-----------|-------------------------------|-------------|--------------|---------------|-------------|---------------|-------------|-------------|

| ET3       | Reserved                      | ECP0        | EPCA0        | EADC0         | Reserved    | Reserved      | ESMB0       | 00000000    |

| Bit7      | Bit6                          | Bit5        | Bit4         | Bit3          | Bit2        | Bit1          | Bit0        |             |

|           |                               |             |              |               |             |               | SFR Address | : 0xE6      |

|           |                               |             |              |               |             |               |             |             |

| Bit 7:    | ET3: Enable                   | Timer 3 In  | terrupt.     |               |             |               |             |             |

|           | This bit sets                 | the maskin  | g of the Tim | ner 3 interru | ıpt.        |               |             |             |

|           | 0: Disable Tir                |             |              |               |             |               |             |             |

|           | 1: Enable inte                |             |              |               | TF3L or TF  | 3H flags.     |             |             |

| Bit 6:    | RESERVED.                     |             |              | -             |             |               |             |             |

| Bit 5:    | ECP0: Enabl                   |             | · · ·        |               |             |               |             |             |

|           | This bit sets                 |             | •            | 0 interrupt.  |             |               |             |             |

|           | 0: Disable Cl                 |             |              | atod by the   |             |               |             |             |

| Bit 4:    | 1: Enable inte<br>EPCA0: Enal |             |              |               |             |               | 5.          |             |

| DIL 4.    | This bit sets                 |             |              |               |             | snupt.        |             |             |

|           | 0: Disable all                |             |              | Ao interiup   |             |               |             |             |

|           | 1: Enable inte                |             |              | ated by PC/   | AO.         |               |             |             |

| Bit 3:    | EADC0: Ena                    |             | •            | -             |             |               |             |             |

|           | This bit sets                 |             |              |               |             | ete interrupt |             |             |

|           | 0: Disable A                  | DC0 Conve   | ersion Comp  | olete interru | pt.         |               |             |             |

|           | 1: Enable inte                | errupt requ | ests genera  | ated by the   | AD0INT flag | J.            |             |             |

| Bits 2-1: | RESERVED.                     |             |              |               |             |               |             |             |

| Bit 0:    | ESMB0: Ena                    |             |              |               |             |               |             |             |

|           | This bit sets                 |             |              | IB0 interrup  | t.          |               |             |             |

|           | 0: Disable all                |             |              |               |             |               |             |             |

|           | 1: Enable inte                | errupt requ | ests genera  | ated by SMI   | 30.         |               |             |             |

|           |                               |             |              |               |             |               |             |             |

## Figure 12.3. EIE1: Extended Interrupt Enable 1

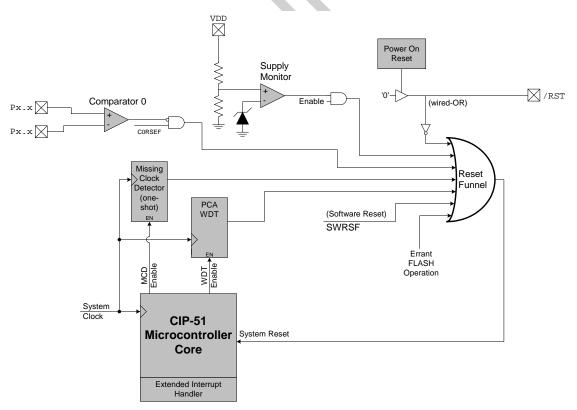

## 14. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pull-ups are enabled during and after the reset. For V<sub>DD</sub> Monitor and power-on resets, the /RST pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. Refer to Section "17. Oscillators" on page 125 for information on selecting and configuring the system clock source. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source (Section "23.3. Watchdog Timer Mode" on page 216 details the use of the Watchdog Timer). Program execution begins at location 0x0000.

Figure 14.1. Reset Sources

| -         FERROR         CORSEF         SWRSF         WDTRSF         MCDRSF         PORSF         PINRSF         Variable           Bit7         Bit6         Bit5         Bit4         Bit3         Bit2         Bit1         Bit0         SFR Address: 0xEF           Bit6         FERROR: Flash Error Indicator.         0: Source of last reset was not a Flash read/write/erase error.         1: Source of last reset was not a Flash read/write/erase error.         1: Source of last reset was not Comparator0.         Write: Comparator0 is not a reset source.           Bit5         CORSEF: Comparator0 Reset Enable and Flag.         0: Read: Source of last reset was not Comparator0.         Write: Comparator0 is not a reset source.           1: Read: Source of last reset was comparator0.         Write: Comparator0 is a reset source (active-low).         Bit4         SWRSF: Software Reset Force and Flag.         0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.         1: Read: Source of last reset was not a WDT timeout.         1: Source of last reset was not a WDT timeout.         1: Source of last reset was a WDT timeout.         1: Source of last reset was a WDT timeout.         1: Source of last reset was a wite to the SWRSF bit. Write: Missing Clock Detector disabled.         1: Read: Source of last reset was a Missing Clock Condition is detected.           Bit2         MCDRSF: Missing Clock Detector Flag.         0: Read: Source of last reset was a mot a Missing Clock condition is detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R       | R                        | R/W          | R/W          | R                       | R/W            | R/W           | R             | Reset Value         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------|--------------|--------------|-------------------------|----------------|---------------|---------------|---------------------|

| <ul> <li>SFR Address: 0xEF</li> <li>Bit7: UNUSED. Read = 0. Write = don't care.</li> <li>Bit6: FERROR: Flash Error Indicator.</li> <li>D: Source of last reset was not a Flash read/write/erase error.</li> <li>1: Source of last reset was a Flash read/write/erase error.</li> <li>Bit5: CORSEF: Comparator0 Reset Enable and Flag.</li> <li>D: Read: Source of last reset was not Comparator0. Write: Comparator0 is not a reset source.</li> <li>1: Read: Source of last reset was Comparator0. Write: Comparator0 is a reset source (active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>D: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a write to the SWRSF bit. Write: Forces a system reset.</li> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>D: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was not a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>D: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset of a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is not a a and stabilized may cause a system reset. See register VDMOCN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                              | -       | FERROR                   | CORSEF       | SWRSF        | WDTRSF                  | MCDRSF         | PORSF         | PINRSF        | Variable            |

| <ul> <li>Bit7: UNUSED. Read = 0. Write = don't care.</li> <li>Bit6: FERROR: Flash Error Indicator.</li> <li>O: Source of last reset was not a Flash read/write/erase error.</li> <li>1: Source of last reset was a Flash read/write/erase error.</li> <li>Bit5: CORSEF: Comparator0 Reset Enable and Flag.</li> <li>O: Read: Source of last reset was not Comparator0. Write: Comparator0 is not a reset source.</li> <li>1: Read: Source of last reset was Comparator0. Write: Comparator0 is a reset source (active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>O: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a WDT timeout.</li> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>O: Source of last reset was a WDT timeout.</li> <li>Bit4: MCDRSF: Missing Clock Detector Flag.</li> <li>O: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>Dit5: Bowre on flast reset was a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>Dit5: Power-On Reset Force and Flag.</li> <li>Dit6: Source of last reset was a Missing Clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>Dit5: Bowre-On Reset Force and Flag.</li> <li>Dit6: Still set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDMOCN (Figure 14.3)</li> <li>D: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>D</sub></li></ul> | Bit7    | Bit6                     | Bit5         | Bit4         | Bit3                    | Bit2           | Bit1          | Bit0          | _<br>_              |

| <ul> <li>Bit6: FERROR: Flash Error Indicator.</li> <li>0: Source of last reset was not a Flash read/write/erase error.</li> <li>1: Source of last reset was a Flash read/write/erase error.</li> <li>Bit5: CORSEF: Comparator0 Reset Enable and Flag.</li> <li>0: Read: Source of last reset was not Comparator0. Write: Comparator0 is not a reset source.</li> <li>1: Read: Source of last reset was Comparator0. Write: Comparator0 is a reset source (active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>Dit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                          |              |              |                         |                |               | SFR Address   | 0xEF                |

| <ul> <li>Bit6: FERROR: Flash Error Indicator.</li> <li>0: Source of last reset was not a Flash read/write/erase error.</li> <li>1: Source of last reset was a Flash read/write/erase error.</li> <li>Bit5: CORSEF: Comparator0 Reset Enable and Flag.</li> <li>0: Read: Source of last reset was not Comparator0. Write: Comparator0 is not a reset source.</li> <li>1: Read: Source of last reset was Comparator0. Write: Comparator0 is a reset source (active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>Dit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                          |              |              |                         |                |               |               |                     |

| <ul> <li>Bit6: FERROR: Flash Error Indicator.</li> <li>0: Source of last reset was not a Flash read/write/erase error.</li> <li>1: Source of last reset was a Flash read/write/erase error.</li> <li>Bit5: CORSEF: Comparator0 Reset Enable and Flag.</li> <li>0: Read: Source of last reset was not Comparator0. Write: Comparator0 is not a reset source.</li> <li>1: Read: Source of last reset was Comparator0. Write: Comparator0 is a reset source (active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>Dit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b></b> |                          |              |              |                         |                |               |               |                     |

| <ul> <li>0: Source of last reset was not a Flash read/write/erase error.</li> <li>1: Source of last reset was a Flash read/write/erase error.</li> <li>Bit5: CORSEF: Comparator0 Reset Enable and Flag.</li> <li>0: Read: Source of last reset was not Comparator0. Write: Comparator0 is not a reset source.</li> <li>1: Read: Source of last reset was Comparator0. Write: Comparator0 is a reset source (active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was not a WIDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was a Nissing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDMOCN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                 |         |                          |              |              | care.                   |                |               |               |                     |

| <ul> <li>1: Source of last reset was a Flash read/write/erase error.</li> <li>Bit5: CORSEF: Comparator0 Reset Enable and Flag.</li> <li>0: Read: Source of last reset was not Comparator0. Write: Comparator0 is not a reset source.</li> <li>1: Read: Source of last reset was Comparator0. Write: Comparator0 is a reset source (active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a WRSF bit. Write: Forces a system reset.</li> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>0: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     | DILO.   |                          |              |              | lach road/w             | rita/arasa ar  | ror           |               |                     |

| <ul> <li>Bit5: CORSEF: Comparator0 Reset Enable and Flag.</li> <li>0: Read: Source of last reset was not Comparator0. Write: Comparator0 is not a reset source.</li> <li>1: Read: Source of last reset was Comparator0. Write: Comparator0 is a reset source (active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was not a WDT timeout.</li> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>0: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDMOCN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                          |              |              |                         |                | 101.          |               |                     |

| <ul> <li>0: Read: Source of last reset was not Comparator0. Write: Comparator0 is not a reset source.</li> <li>1: Read: Source of last reset was Comparator0. Write: Comparator0 is a reset source (active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was a write to the SWRSF bit. Write: Forces a system reset.</li> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>0: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDMOCN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit5:   |                          |              |              |                         |                |               |               |                     |

| <ul> <li>1: Read: Source of last reset was Comparator0. Write: Comparator0 is a reset source (active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last reset was a write to the SWRSF bit. Write: Forces a system reset.</li> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>0: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDMOCN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on rV<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                          |              |              |                         |                | : Compara     | tor0 is not a | reset               |

| <ul> <li>(active-low).</li> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last was a write to the SWRSF bit. Write: Forces a system reset.</li> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>0: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                          |              |              |                         |                |               |               |                     |

| <ul> <li>Bit4: SWRSF: Software Reset Force and Flag.</li> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last was a write to the SWRSF bit. Write: Forces a system reset.</li> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>0: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                          |              | reset was    | Comparator              | 0. Write: Co   | omparator0    | is a reset s  | ource               |

| <ul> <li>0: Read: Source of last reset was not a write to the SWRSF bit. Write: No Effect.</li> <li>1: Read: Source of last was a write to the SWRSF bit. Write: Forces a system reset.</li> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>0: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D'14    | ```                      |              |              |                         |                |               | ×             |                     |

| <ul> <li>1: Read: Source of last was a write to the SWRSF bit. Write: Forces a system reset.</li> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>0: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit4:   |                          |              |              |                         | o the SM/DS    |               |               |                     |

| <ul> <li>Bit3: WDTRSF: Watchdog Timer Reset Flag.</li> <li>0: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                          |              |              |                         |                |               |               |                     |

| <ul> <li>0: Source of last reset was not a WDT timeout.</li> <li>1: Source of last reset was a WDT timeout.</li> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit3:   |                          |              |              |                         |                |               | a system it   |                     |

| <ul> <li>Bit2: MCDRSF: Missing Clock Detector Flag.</li> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                          | •            |              | -                       |                |               |               |                     |

| <ul> <li>0: Read: Source of last reset was not a Missing Clock Detector timeout. Write: Missing Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | 1: Source of             | last reset w | vas a WDT    | timeout.                |                |               |               |                     |

| <ul> <li>Clock Detector disabled.</li> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.<br/>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit2:   |                          |              |              |                         |                |               |               |                     |

| <ul> <li>1: Read: Source of last reset was a Missing Clock Detector timeout. Write: Missing Clock Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.<br/>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                          |              |              | not a Missin            | g Clock Det    | ector timed   | out. Write: N | lissing             |

| <ul> <li>Detector enabled; triggers a reset if a missing clock condition is detected.</li> <li>Bit1: PORSF: Power-On Reset Force and Flag.</li> <li>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                          |              |              | n Minning C             | look Dotoot    | or timoout    | Mrite Mice    | ing Clock           |

| <ul> <li>Bit1: PORSF: Power-On Reset Force and Flag.<br/>This bit is set anytime a power-on reset occurs. Writing this bit enables/disables the V<sub>DD</sub> monitor as a reset source. Note: writing '1' to this bit before the V<sub>DD</sub> monitor is enabled and stabilized may cause a system reset. See register VDM0CN (Figure 14.3)</li> <li>0: Read: Last reset was not a power-on or V<sub>DD</sub> monitor reset. Write: V<sub>DD</sub> monitor is not a</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                          |              |              |                         |                |               |               |                     |