Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | 8051                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 50MHz                                                        |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART             |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                   |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 768 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x16b; D/A 2x8b                                          |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-VFQFN Exposed Pad                                         |

| Supplier Device Package    | 28-MLP (5x5)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f353r |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Figures and Tables

| 1. | System Overview                                                | 13 |

|----|----------------------------------------------------------------|----|

|    | Table 1.1. Product Selection Guide                             | 14 |

|    | Figure 1.1. C8051F350 Block Diagram                            | 15 |

|    | Figure 1.2. C8051F351 Block Diagram                            |    |

|    | Figure 1.3. C8051F352 Block Diagram                            | 17 |

|    | Figure 1.4. C8051F353 Block Diagram                            | 18 |

|    | Figure 1.5. Development/In-System Debug Diagram                | 20 |

|    | Figure 1.6. Memory Map                                         | 21 |

|    | Figure 1.7. ADC0 Block Diagram                                 | 22 |

|    | Figure 1.8. IDAC Block Diagram                                 |    |

|    | Figure 1.9. Comparator0 Block Diagram                          | 24 |

|    | Figure 1.10. Port I/O Functional Block Diagram                 |    |

|    | Figure 1.11. PCA Block Diagram                                 |    |

| 2. | Absolute Maximum Ratings                                       |    |

|    | Table 2.1. Absolute Maximum Ratings*                           |    |

| 3. | Global DC Electrical Characteristics                           |    |

|    | Table 3.1. Global DC Electrical Characteristics                |    |

| 4. | Pinout and Package Definitions                                 |    |

|    | Table 4.1. Pin Definitions for the C8051F350/1/2/3             |    |

|    | Figure 4.1. LQFP-32 Pinout Diagram (Top View)                  |    |

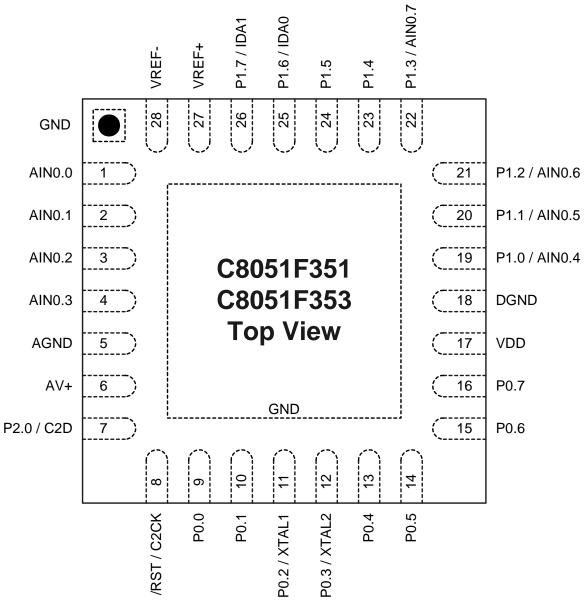

|    | Figure 4.2. MLP-28 Pinout Diagram (Top View)                   |    |

|    | Figure 4.3. LQFP-32 Package Diagram                            |    |

|    | Table 4.2. LQFP-32 Package Dimensions                          | 34 |

|    | Figure 4.4. MLP-28 Package Drawing                             | 35 |

|    | Table 4.3. MLP-28 Package Dimensions                           |    |

|    | Figure 4.5. Typical MLP-28 Landing Diagram                     | 36 |

|    | Figure 4.6. Typical MLP-28 Solder Paste Diagram                |    |

| 5. | 24 or 16-Bit Analog to Digital Converter (ADC0)                |    |

|    | Figure 5.1. ADC0 Block Diagram                                 |    |

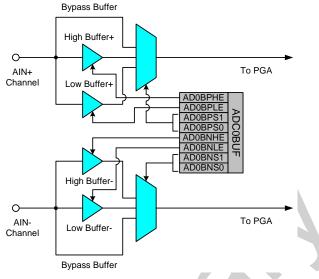

|    | Figure 5.2. ADC0 Buffer Control                                |    |

|    | Figure 5.3. ADC0 Offset Calibration Register Coding            |    |

|    | Figure 5.4. ADC0 Gain Calibration Register Coding              |    |

|    | Table 5.1. ADC0 Unipolar Output Word Coding (AD0POL = 0)       |    |

|    | Table 5.2. ADC0 Bipolar Output Word Coding (AD0POL = 1)        |    |

|    | Figure 5.5. ADC0CN: ADC0 Control Register                      | 46 |

|    | Figure 5.6. ADC0CF: ADC0 Configuration Register                | 47 |

|    | Figure 5.7. ADC0MD: ADC0 Mode Register                         | 48 |

|    | Figure 5.8. ADC0CLK: ADC0 Modulator Clock Divisor              |    |

|    | Figure 5.9. ADC0DECH: ADC0 Decimation Ratio Register High Byte |    |

|    | Figure 5.10. ADC0DECL: ADC0 Decimation Ratio Register Low Byte |    |

|    | Figure 5.11. ADC0DAC: ADC0 Offset DAC Register                 |    |

|    | Figure 5.12. ADC0BUF: ADC0 Input Buffer Control Register       |    |

|    | Figure 5.13. ADC0STA: ADC0 Status Register                     | 52 |

| Table 20.6. Timer Settings for Standard Baud Rates Using an External Oscillato | or 176 |

|--------------------------------------------------------------------------------|--------|

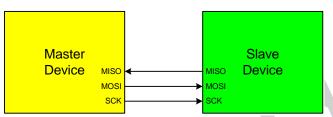

| 21. Serial Peripheral Interface (SPI0)                                         |        |

| Figure 21.1. SPI Block Diagram                                                 |        |

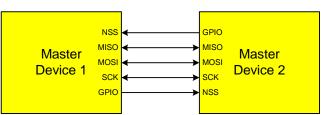

| Figure 21.2. Multiple-Master Mode Connection Diagram                           |        |

| Figure 21.3. 3-Wire Single Master and Single Slave Mode Connection Diagram     |        |

| Figure 21.4. 4-Wire Single Master and Slave Mode Connection Diagram            |        |

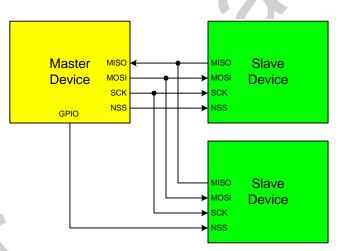

| Figure 21.5. Data/Clock Timing Relationship                                    |        |

| Figure 21.6. SPI0CFG: SPI0 Configuration Register                              |        |

| Figure 21.7. SPI0CN: SPI0 Control Register                                     |        |

| Figure 21.8. SPI0CKR: SPI0 Clock Rate Register                                 |        |

| Figure 21.9. SPI0DAT: SPI0 Data Register                                       |        |

| Figure 21.10. SPI Master Timing (CKPHA = 0)                                    | 187    |

| Figure 21.11. SPI Master Timing (CKPHA = 1)                                    |        |

| Figure 21.12. SPI Slave Timing (CKPHA = 0)                                     |        |

| Figure 21.13. SPI Slave Timing (CKPHA = 1)                                     |        |

| Table 21.1. SPI Slave Timing Parameters                                        | 189    |

| 22. Timers                                                                     | 191    |

| 22. Timers<br>Figure 22.1. T0 Mode 0 Block Diagram                             | 192    |

| Figure 22.2. T0 Mode 2 Block Diagram                                           | 193    |

| Figure 22.3. T0 Mode 3 Block Diagram                                           |        |

| Figure 22.4. TCON: Timer Control Register                                      |        |

| Figure 22.5. TMOD: Timer Mode Register                                         |        |

| Figure 22.6. CKCON: Clock Control Register                                     |        |

| Figure 22.7. TL0: Timer 0 Low Byte                                             |        |

| Figure 22.8. TL1: Timer 1 Low Byte                                             |        |

| Figure 22.9. TH0: Timer 0 High Byte                                            |        |

| Figure 22.10. TH1: Timer 1 High Byte                                           |        |

| Figure 22.11. Timer 2 16-Bit Mode Block Diagram                                |        |

| Figure 22.12. Timer 2 8-Bit Mode Block Diagram                                 |        |

| Figure 22.13. TMR2CN: Timer 2 Control Register                                 |        |

| Figure 22.14. TMR2RLL: Timer 2 Reload Register Low Byte                        |        |

| Figure 22.15. TMR2RLH: Timer 2 Reload Register High Byte                       |        |

| Figure 22.16. TMR2L: Timer 2 Low Byte                                          |        |

| Figure 22.17. TMR2H Timer 2 High Byte                                          |        |

| Figure 22.18. Timer 3 16-Bit Mode Block Diagram                                |        |

| Figure 22.19. Timer 3 8-Bit Mode Block Diagram                                 | 204    |

| Figure 22.20. TMR3CN: Timer 3 Control Register                                 |        |

| Figure 22.21. TMR3RLL: Timer 3 Reload Register Low Byte                        |        |

| Figure 22.22. TMR3RLH: Timer 3 Reload Register High Byte                       |        |

| Figure 22.23. TMR3L: Timer 3 Low Byte                                          |        |

| Figure 22.24. TMR3H Timer 3 High Byte                                          |        |

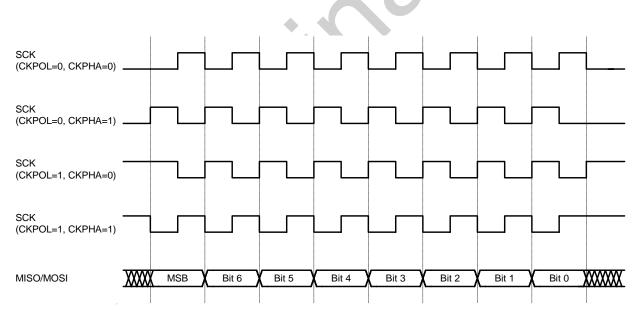

| 23. Programmable Counter Array                                                 |        |

| Figure 23.1. PCA Block Diagram                                                 |        |

| Figure 23.2. PCA Counter/Timer Block Diagram                                   |        |

| Table 23.1. PCA Timebase Input Options                                         |        |

|                                                                                | 200    |

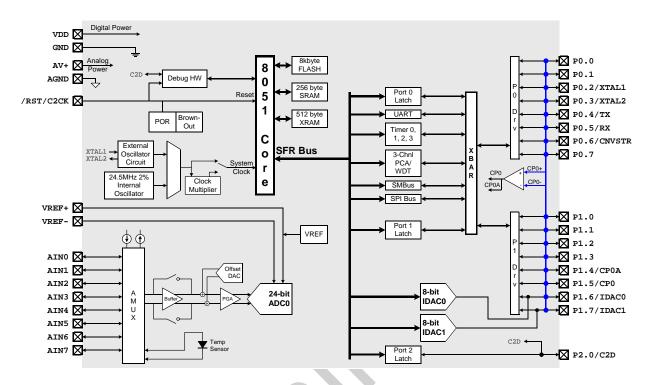

### 1. System Overview

C8051F350/1/2/3 devices are fully integrated mixed-signal System-on-a-Chip MCUs. Highlighted features are listed below. Refer to Table 1.1 for specific product feature selection.

- High-speed pipelined 8051-compatible microcontroller core (up to 50 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- 24 or 16-bit single-ended/differential ADC with analog multiplexer

- Two 8-bit Current Output DACs

- Precision programmable 24.5 MHz internal oscillator

- 8 kB of on-chip Flash memory

- 768 bytes of on-chip RAM

- SMBus/I2C, Enhanced UART, and SPI serial interfaces implemented in hardware

- Four general-purpose 16-bit timers

- Programmable counter/timer array (PCA) with three capture/compare modules and watchdog timer function

- On-chip power-on reset, V<sub>DD</sub> monitor, and temperature sensor

- On-chip voltage comparator

- 17 Port I/O (5 V tolerant)

With on-chip power-on reset,  $V_{DD}$  monitor, watchdog timer, and clock oscillator, the C8051F350/1/2/3 devices are truly stand-alone System-on-a-Chip solutions. The Flash memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing field upgrades of the 8051 firmware. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings.

The on-chip Silicon Labs 2-Wire (C2) Development Interface allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production MCU installed in the final application. This debug logic supports inspection and modification of memory and registers, setting breakpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

Each device is specified for 2.7 V-to-3.6 V operation over the industrial temperature range (-45 to +85 °C). The Port I/O and /RST pins are tolerant of input signals up to 5 V. The C8051F350/1/2/3 are available in 28-pin MLP or 32-pin LQFP packaging, as shown in Figure 1.1 through Figure 1.4.

Figure 1.1. C8051F350 Block Diagram

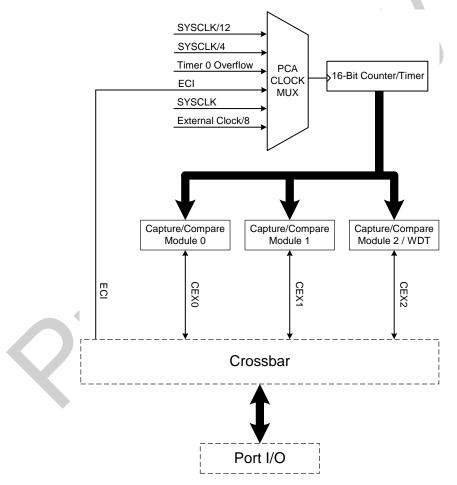

### 1.9. Programmable Counter Array

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflow, or an external clock signal on the External Clock nput (ECI) input pin.

Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM. Additionally, PCA Module 2 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. The PCA Capture/Compare Module I/O and the External Clock Input may be routed to Port I/O using the digital crossbar.

Figure 1.11. PCA Block Diagram

|        | Pin Numbers    |                |                  |                                                                                     |  |  |

|--------|----------------|----------------|------------------|-------------------------------------------------------------------------------------|--|--|

| Name   | 'F350<br>'F352 | 'F351<br>'F353 | Туре             | Description                                                                         |  |  |

| P0.6/  | 19             | 15             | D I/O or<br>A In | Port 0.6. See Port I/O Section for a complete description.                          |  |  |

| CNVSTR | 15             | 19             | D In             | External Convert Start Input for IDACs (See IDAC Section for complete description). |  |  |

| P0.7   | 20             | 16             | D I/O or<br>A In | Port 0.7. See Port I/O Section for a complete description.                          |  |  |

| P1.0/  | 00             | 40             | D I/O or<br>A In | Port 1.0. See Port I/O Section for a complete description.                          |  |  |

| AIN0.4 | 23             | 19             | A In             | ADC0 Input Channel 4 (C8051F351/3 - See ADC0 Section for complete description).     |  |  |

| P1.1/  | 24 20          |                | D I/O or<br>A In | Port 1.1. See Port I/O Section for a complete description.                          |  |  |

| AIN0.5 | 24             | 20             | A In             | ADC0 Input Channel 5 (C8051F351/3 - See ADC0 Section for complete description).     |  |  |

| P1.2/  | 05             |                | D I/O or<br>A In | Port 1.2. See Port I/O Section for a complete description.                          |  |  |

| AIN0.6 | 25             | 21             | A In             | ADC0 Input Channel 6 (C8051F351/3 - See ADC0 Section for complete description).     |  |  |

| P1.3/  | 26             | 22             | D I/O or<br>A In | Port 1.3. See Port I/O Section for a complete description.                          |  |  |

| AIN0.7 | 20             | 22             | A In             | ADC0 Input Channel 7 (C8051F351/3 - See ADC0 Section for complete description).     |  |  |

| P1.4   | 27             | 23             | D I/O or<br>A In | Port 1.4. See Port I/O Section for a complete description.                          |  |  |

| P1.5   | 28             | 24             | D I/O or<br>A In | Port 1.5. See Port I/O Section for a complete description.                          |  |  |

| P1.6/  | 29             | 25             | D I/O or<br>A In | Port 1.6. See Port I/O Section for a complete description.                          |  |  |

| IDA0   |                |                | A Out            | IDAC0 Output (See IDAC Section for complete description).                           |  |  |

| P1.7/  | 30             | 26             | D I/O or<br>A In | Port 1.7. See Port I/O Section for a complete description.                          |  |  |

| IDA1   |                |                | A Out            | IDAC1 Output (See IDAC Section for complete description).                           |  |  |

Figure 4.2. MLP-28 Pinout Diagram (Top View)

Figure 5.2. ADC0 Buffer Control

#### 5.1.3. Modulator Clock

The ADC0CLK register (Figure 5.8) holds the Modulator Clock (MDCLK) divisor value. The modulator clock determines the switching frequency for the ADC sampling capacitors. Optimal performance will be achieved when the MDCLK frequency is equal to 2.4576 MHz. The modulator samples the input at a rate of MDCLK / 128.

#### 5.1.4. Decimation Ratio

The decimation ratio of the ADC filters is selected by the DECI[10:0] bits in the ADC0DECH and ADC0DECL registers (Figure 5.9 and Figure 5.10, respectively). The decimation ratio is equal to 1 + DECI[10:0]. The decimation ratio determines how many modulator samples are used to generate a single output word. The ADC output word rate is equal to the modulator sampling rate divided by the decimation ratio. For more information on how the ADC output word rate is derived, see Figure 5.8 and Figure 5.10. Higher decimation ratios will produce lower-noise results over a longer conversion period. The minimum decimation ratio is 20. When using the fast filter output, the decimation ratio must be set to a multiple of 8.

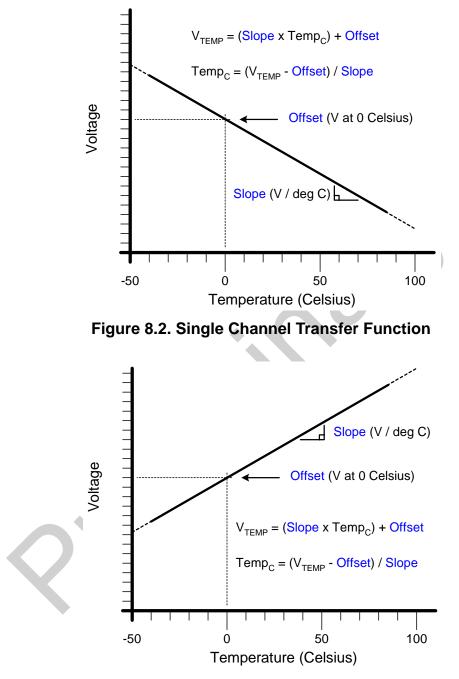

Figure 8.3. Differential Transfer Function

| Mnemonic            | Description                                    | Bytes | Clock       |  |

|---------------------|------------------------------------------------|-------|-------------|--|

| MOV @Ri, direct     | Move direct byte to indirect RAM               | 2     | Cycles<br>2 |  |

| MOV @Ri, #data      | Move immediate to indirect RAM                 | 2     | 2           |  |

| MOV DPTR, #data16   | Load DPTR with 16-bit constant                 | 3     | 3           |  |

| MOVC A, @A+DPTR     | Move code byte relative DPTR to A              | 1     | 3           |  |

| MOVC A, @A+PC       | Move code byte relative PC to A                | 1     | 3           |  |

| MOVX A, @Ri         | Move external data (8-bit address) to A        | 1     | 3           |  |

| MOVX @Ri, A         | Move A to external data (8-bit address)        | 1     | 3           |  |

| MOVX A, @DPTR       | Move external data (16-bit address) to A       | 1     | 3           |  |

| MOVX @DPTR, A       | Move A to external data (16-bit address)       | 1     | 3           |  |

| PUSH direct         | Push direct byte onto stack                    | 2     | 2           |  |

| POP direct          | Pop direct byte from stack                     | 2     | 2           |  |

| XCH A, Rn           | Exchange Register with A                       | 1     | 1           |  |

| XCH A, direct       | Exchange direct byte with A                    | 2     | 2           |  |

| XCH A, @Ri          | Exchange indirect RAM with A                   | 1     | 2           |  |

| XCHD A, @Ri         | Exchange low nibble of indirect RAM with A     | 1     | 2           |  |

|                     | Boolean Manipulation                           |       |             |  |

| CLR C               | Clear Carry                                    | 1     | 1           |  |

| CLR bit             | Clear direct bit                               | 2     | 2           |  |

| SETB C              | Set Carry                                      | 1     | 1           |  |

| SETB bit            | Set direct bit                                 | 2     | 2           |  |

| CPL C               | Complement Carry                               | 1     | 1           |  |

| CPL bit             | Complement direct bit                          | 2     | 2           |  |

| ANL C, bit          | AND direct bit to Carry                        | 2     | 2           |  |

| ANL C, /bit         | AND complement of direct bit to Carry          | 2     | 2           |  |

| ORL C, bit          | OR direct bit to carry                         | 2     | 2           |  |

| ORL C, /bit         | OR complement of direct bit to Carry           | 2     | 2           |  |

| MOV C, bit          | Move direct bit to Carry                       | 2     | 2           |  |

| MOV bit, C          | Move Carry to direct bit                       | 2     | 2           |  |

| JC rel              | Jump if Carry is set                           | 2     | 2/3         |  |

| JNC rel             | Jump if Carry is not set                       | 2     | 2/3         |  |

| JB bit, rel         | Jump if direct bit is set                      | 3     | 3/4         |  |

| JNB bit, rel        | Jump if direct bit is not set                  | 3     | 3/4         |  |

| JBC bit, rel        | Jump if direct bit is set and clear bit        | 3     | 3/4         |  |

|                     | Program Branching                              |       |             |  |

| ACALL addr11        | Absolute subroutine call                       | 2     | 3           |  |

| LCALL addr16        | Long subroutine call                           | 3     | 4           |  |

| RET                 | Return from subroutine                         | 1     | 5           |  |

| RETI                | Return from interrupt                          | 1     | 5           |  |

| AJMP addr11         | Absolute jump                                  | 2     | 3           |  |

| LJMP addr16         | Long jump                                      | 3     | 4           |  |

|                     | Short jump (relative address)                  | 2     | 3           |  |

| JMP @A+DPTR         | Jump indirect relative to DPTR                 | 1     | 3           |  |

| JZ rel              | Jump if A equals zero                          | 2     | 2/3         |  |

| JNZ rel             | Jump if A does not equal zero                  | 2     | 2/3         |  |

| CJNE A, direct, rel | Compare direct byte to A and jump if not equal | 3     | 3/4         |  |

### Table 10.1. CIP-51 Instruction Set Summary (Continued)

#### 12.4. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

| R/W    | R/W                            | R/W           | R/W           | R/W            | R/W          | R/W           | R/W          | Reset Value        |

|--------|--------------------------------|---------------|---------------|----------------|--------------|---------------|--------------|--------------------|

| EA     | ESPI0                          | ET2           | ES0           | ET1            | EX1          | ET0           | EX0          | 00000000           |

| Bit7   | Bit6                           | Bit5          | Bit4          | Bit3           | Bit2         | Bit1          | Bit0         | Bit<br>Addressable |

|        |                                |               |               |                |              |               | SFR Addres   | s: 0xA8            |

|        |                                |               |               |                |              |               |              |                    |

| Bit 7: | EA: Enable /                   |               |               | llinterrunte   | It override  | a tha indivia | luci interru | at maak aat        |

|        | This bit globa<br>tings.       | any enables   | solisables a  | ii interrupts. | it overnde:  | s the individ |              | pi mask sei-       |

|        | 0: Disable al                  | l interrupt s | ources.       |                |              |               |              |                    |

|        | 1: Enable ea                   |               |               | to its individ | lual mask s  | etting.       |              |                    |

| Bit 6: | ESPI0: Enab                    | le Serial P   | eripheral Int | terface (SPI   | 0) Interrupt |               |              |                    |

|        | This bit sets                  |               | •             | 10 interrupts  | 5.           |               |              |                    |

|        | 0: Disable al                  |               |               |                |              |               |              |                    |

| Bit 5: | 1: Enable int<br>ET2: Enable   |               |               | ated by SPIC   | J.           |               |              |                    |

| Dit J. | This bit sets                  |               |               | ner 2 interru  | pt.          |               |              |                    |

|        | 0: Disable Ti                  |               | •             |                | P            |               |              |                    |

|        | 1: Enable int                  | errupt requ   | ests genera   | ated by the    | TF2L or TF   | 2H flags.     |              |                    |

| Bit 4: | ES0: Enable                    |               | · ·           |                |              |               |              |                    |

|        | This bit sets                  |               |               | RT0 interru    | pt.          |               |              |                    |

|        | 0: Disable U                   |               |               |                |              |               |              |                    |

| Bit 3: | 1: Enable UA<br>ET1: Enable    |               |               |                |              |               |              |                    |

| Dit 0. | This bit sets                  |               |               | ner 1 interru  | pt.          |               |              |                    |

|        | 0: Disable al                  |               |               |                |              |               |              |                    |

|        | 1: Enable int                  |               | •             | ated by the    | TF1 flag.    |               |              |                    |

| Bit 2: | EX1: Enable                    |               |               |                |              |               |              |                    |

|        | This bit sets                  |               | •             | al Interrupt   | 1.           |               |              |                    |

|        | 0: Disable ex<br>1: Enable int |               |               | ated by the    | /INT1 input  |               |              |                    |

| Bit 1: | ET0: Enable                    |               |               |                | nar i input. |               |              |                    |

| 2      | This bit sets                  |               |               | ner 0 interru  | pt.          |               |              |                    |

|        | 0: Disable al                  |               |               |                |              |               |              |                    |

|        | 1: Enable int                  |               |               | ated by the    | TF0 flag.    |               |              |                    |

| Bit 0: | EX0: Enable                    |               |               | - 1. 1         | 2            |               |              |                    |

|        | This bit sets<br>0: Disable ex |               | •             | a interrupt (  | J.           |               |              |                    |

|        | 1: Enable int                  |               | •             | ated by the    | /INT0 input. |               |              |                    |

|        |                                |               | 35            |                |              |               |              |                    |

### Figure 12.1. IE: Interrupt Enable

### 13. Prefetch Engine

The C8051F350/1/2/3 family of devices incorporate a 2-byte prefetch engine. Because the access time of the Flash memory is 40 ns, and the minimum instruction time is 20 ns, the prefetch engine is necessary for full-speed code execution. Instructions are read from Flash memory two bytes at a time by the prefetch engine, and given to the CIP-51 processor core to execute. When running linear code (code without any jumps or branches), the prefetch engine allows instructions to be executed at full speed. When a code branch occurs, the processor may be stalled for up to two clock cycles while the next set of code bytes is retrieved from Flash memory. The FLRT bit (FLSCL.4) determines how many clock cycles are used to read each set of two code bytes from Flash. When operating from a system clock of 25 MHz or less, the FLRT bit should be set to '0' so that the prefetch engine takes only one clock cycle for each read. When operating with a system clock of greater than 25 MHz (up to 50 MHz), the FLRT bit should be set to '1', so that each prefetch code read lasts for two clock cycles.

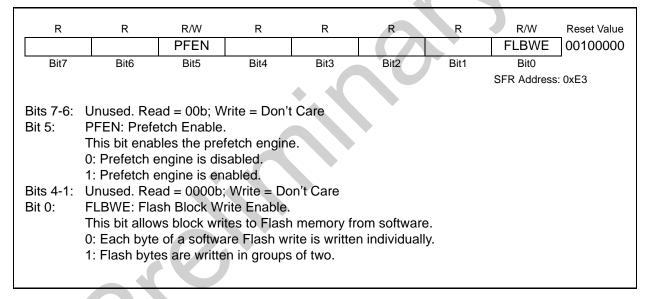

#### Figure 13.1. PFE0CN: Prefetch Engine Control Register

#### 17.3. Clock Multiplier

The Clock Multiplier generates an output clock which is 4 times the input clock frequency. The Clock Multiplier's input can be selected from the external oscillator, or 1/2 the internal or external oscillators. This produces three possible outputs: Internal Oscillator x 2, External Oscillator x 2, or External Oscillator x 4. See Section 17.4 for details on system clock selection.

The Clock Multiplier is configured via the CLKMUL register (Figure 17.5). The procedure for configuring and enabling the Clock Multiplier is as follows:

- 1. Reset the Multiplier by writing 0x00 to register CLKMUL.

- 2. Select the Multiplier input source via the MULSEL bits.

- 3. Enable the Multiplier with the MULEN bit (CLKMUL | = 0x80).

- 4. Delay for >5 µs.

- 5. Initialize the Multiplier with the MULINIT bit (CLKMUL | = 0xC0).

- 6. Poll for MULRDY = '1'.

Important Note: When using an external oscillator as the input to the Clock Multiplier, the external source must be enabled and stable before the Multiplier is initialized. See Section 17.4 for details on selecting an external oscillator source.

| DAM      | DAM                                                                                                                                         | P      | DAA        | DAM            | DAM            | DAA          | DAA          | Decet Males    |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|----------------|----------------|--------------|--------------|----------------|--|--|

| R/W      | R/W                                                                                                                                         | R      | R/W        | R/W            | R/W            | R/W          | R/W          | Reset Value    |  |  |

| MULEN    |                                                                                                                                             | MULRDY | -          | -              | -              |              | LSEL         | 00000000       |  |  |

| Bit7     | Bit6                                                                                                                                        | Bit5   | Bit4       | Bit3           | Bit2           | Bit1         | Bit0         |                |  |  |

|          |                                                                                                                                             | •      |            |                |                |              | SFR Addres   | ss: 0xBE       |  |  |

|          |                                                                                                                                             |        |            |                |                |              |              |                |  |  |

| Bit7:    | MULEN: Clo                                                                                                                                  |        |            |                |                |              |              |                |  |  |

|          | 0: Clock Mul                                                                                                                                |        |            |                |                |              |              |                |  |  |

|          | 1: Clock Mul                                                                                                                                |        |            |                |                |              |              |                |  |  |

| Bit6:    | Bit6: MULINIT: Clock Multiplier Initialize<br>This bit should be a '0' when the Clock Multiplier is enabled. Once enabled, writing a '1' to |        |            |                |                |              |              |                |  |  |

|          |                                                                                                                                             |        |            |                |                |              |              |                |  |  |

|          | this bit will in                                                                                                                            |        | lock Multi | plier. The MU  | JLRDY bit i    | reads '1' wl | nen the Clo  | ock Multiplier |  |  |

| DVE      | is stabilized.                                                                                                                              |        | <b>.</b> . |                |                |              |              |                |  |  |

| Bit5:    | MULRDY: C                                                                                                                                   | •      |            |                |                |              |              |                |  |  |

|          |                                                                                                                                             |        |            | tus of the Cl  | ock iviuitipii | ler.         |              |                |  |  |

|          | 0: Clock Mul                                                                                                                                |        |            |                |                |              |              |                |  |  |

| Bits4-2: | 1: Clock Mul                                                                                                                                |        |            | a't aara       |                |              |              |                |  |  |

|          | Unused. Rea<br>MULSEL: CI                                                                                                                   |        |            |                |                |              |              |                |  |  |

| Bits1-0: | These bits s                                                                                                                                |        |            |                |                | -            |              |                |  |  |

|          |                                                                                                                                             |        | supplie    |                |                |              |              |                |  |  |

|          | MU                                                                                                                                          | LSEL   | Sel        | ected Input    | Clock          | Clock N      | Iultipler O  | utput          |  |  |

|          | (                                                                                                                                           | 00     | Int        | ernal Oscillat | or / 2         | Interna      | al Oscillato | rx2            |  |  |

|          | (                                                                                                                                           | 01     | E          | xternal Oscil  | lator          | Externa      | al Oscillato | r x 4          |  |  |

|          |                                                                                                                                             | 10     | Ext        | ernal Oscilla  | tor / 2        | Externa      | al Oscillato | rx2            |  |  |

|          |                                                                                                                                             | 11     |            | RESERVE        | C              | R            | ESERVED      |                |  |  |

|          | L                                                                                                                                           |        |            |                |                |              |              |                |  |  |

|          |                                                                                                                                             |        |            |                |                |              |              |                |  |  |

### Figure 17.5. CLKMUL: Clock Multiplier Control Register

Figure 21.2. Multiple-Master Mode Connection Diagram

Figure 21.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection

Figure 21.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection

#### 21.5. Serial Clock Timing

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships are shown in Figure 21.5.

The SPI0 Clock Rate Register (SPI0CKR) as shown in Figure 21.8 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock.

Figure 21.5. Data/Clock Timing Relationship

### 21.6. SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following figures.

| R      | R/W                                                                                                                                          | R/W            | R/W          | R               | R            | R             | R                    | Reset Value |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|-----------------|--------------|---------------|----------------------|-------------|--|--|

| SPIBSY |                                                                                                                                              | CKPHA          | CKPOL        | SLVSEL          | NSSIN        | SRMT          | RXBMT                | 0000011     |  |  |

| Bit7   | Bit6                                                                                                                                         | Bit5           | Bit4         | Bit3            | Bit2         | Bit1          | Bit0<br>SFR Address: | ~           |  |  |

| Bit 7: | SPIBSY: SP                                                                                                                                   | l Busy (read   | d only).     |                 |              |               | SFR Address.         | UXA I       |  |  |

|        | This bit is se                                                                                                                               |                |              | l transfer is i | in progress  | (Master or    | Slave Mode           | e).         |  |  |

| Bit 6: | MSTEN: Ma                                                                                                                                    |                |              |                 |              |               |                      |             |  |  |

|        | 0: Disable m<br>1: Enable ma                                                                                                                 |                |              |                 | e.           |               |                      |             |  |  |

| Bit 5: | CKPHA: SPI                                                                                                                                   |                |              | s a master.     |              |               |                      |             |  |  |

|        | This bit cont                                                                                                                                |                |              | ase.            |              |               |                      |             |  |  |

|        | 0: Data cente                                                                                                                                |                | •            |                 |              |               |                      |             |  |  |

|        | 1: Data cent                                                                                                                                 |                | 0            | •               | od.†         |               |                      |             |  |  |

| Bit 4: | CKPOL: SPI                                                                                                                                   |                |              |                 |              |               |                      |             |  |  |

|        | This bit cont                                                                                                                                |                |              | arity.          |              |               |                      |             |  |  |

|        | 0: SCK line low in idle state.                                                                                                               |                |              |                 |              |               |                      |             |  |  |

| Bit 3: | 1: SCK line h                                                                                                                                |                |              |                 |              |               |                      |             |  |  |

| on 5.  | SLVSEL: Slave Selected Flag (read only).<br>This bit is set to logic 1 whenever the NSS pin is low indicating SPI0 is the selected slave. It |                |              |                 |              |               |                      |             |  |  |

|        | is cleared to                                                                                                                                |                |              |                 |              |               |                      |             |  |  |

|        | instantaneou                                                                                                                                 | •              |              | •               | ,            | ,             |                      |             |  |  |

| Bit 2: | NSSIN: NSS                                                                                                                                   |                |              |                 |              |               |                      |             |  |  |

|        | This bit mim                                                                                                                                 |                |              |                 |              | the NSS po    | ort pin at the       | e time that |  |  |

| Bit 1: | the register i<br>SRMT: Shift                                                                                                                |                |              | •               |              | alv)          |                      |             |  |  |

| л. т.  | This bit will b                                                                                                                              |                |              |                 |              |               | t of the shift       | register    |  |  |

|        | and there is                                                                                                                                 |                |              |                 |              |               |                      |             |  |  |

|        | receive buffe                                                                                                                                | er. It returns | to logic 0 v | vhen a data     | byte is tran | nsferred to t | he shift regi        | ister from  |  |  |

|        | the transmit                                                                                                                                 |                |              |                 |              |               |                      |             |  |  |

|        | NOTE: SRM                                                                                                                                    |                |              |                 |              |               |                      |             |  |  |

| Bit O: | RXBMT: Red<br>This bit will b                                                                                                                |                |              |                 |              |               | nd containe          |             |  |  |

|        | information.                                                                                                                                 |                |              |                 |              |               |                      |             |  |  |

|        | this bit will re                                                                                                                             |                |              |                 |              |               |                      | boonroad    |  |  |

|        | NOTE: RXB                                                                                                                                    | •              |              | r Mode.         |              |               |                      |             |  |  |

|        |                                                                                                                                              |                |              |                 |              |               |                      |             |  |  |

|        |                                                                                                                                              |                |              |                 |              |               |                      |             |  |  |

### Figure 21.6. SPI0CFG: SPI0 Configuration Register

| R/W      | R/W                                                                                                                                          | R/W                          | R/W            | R/W           | R/W          | R/W            | R/W          | Reset Value    |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|---------------|--------------|----------------|--------------|----------------|--|--|--|

| T3MH     | T3ML                                                                                                                                         | T2MH                         | T2ML           | T1M           | TOM          | SCA1           | SCA0         | 00000000       |  |  |  |

| Bit7     | Bit6                                                                                                                                         | Bit5                         | Bit4           | Bit3          | Bit2         | Bit1           | Bit0         |                |  |  |  |

|          |                                                                                                                                              |                              |                |               |              |                | SFR Addres   | s: 0x8E        |  |  |  |

|          |                                                                                                                                              |                              |                |               |              |                |              |                |  |  |  |

| Bit7:    |                                                                                                                                              | er 3 High B                  |                |               |              |                |              |                |  |  |  |

|          |                                                                                                                                              | ects the cloo                |                |               |              |                | s configure  | ed in split 8- |  |  |  |

|          | bit timer mode. T3MH is ignored if Timer 3 is in any other mode.<br>0: Timer 3 high byte uses the clock defined by the T3XCLK bit in TMR3CN. |                              |                |               |              |                |              |                |  |  |  |

|          |                                                                                                                                              | • •                          |                | •             | the I3XCL    | K dit in Tivif | K3CN.        |                |  |  |  |

| Bit6:    |                                                                                                                                              | high byte us<br>er 3 Low By  |                |               |              |                |              |                |  |  |  |

| Dito.    |                                                                                                                                              | ects the clo                 |                |               | f Timer 3 is | configured     | in split 8-b | it timer       |  |  |  |

|          |                                                                                                                                              | bit selects the              |                |               |              |                |              |                |  |  |  |

|          |                                                                                                                                              | low byte use                 |                |               |              |                | 3CN.         |                |  |  |  |

|          |                                                                                                                                              | low byte use                 |                | •             |              |                |              |                |  |  |  |

| Bit5:    |                                                                                                                                              | her 2 High B                 |                |               |              |                | ÷            |                |  |  |  |

|          |                                                                                                                                              | ects the cloo                |                |               |              |                | s configure  | ed in split 8- |  |  |  |

|          |                                                                                                                                              | ode. T2MH i                  |                |               |              |                |              |                |  |  |  |

|          |                                                                                                                                              | high byte us                 |                |               | the T2XCL    | K bit in TMF   | R2CN.        |                |  |  |  |

| Bit4:    |                                                                                                                                              | high byte us                 |                |               |              |                |              |                |  |  |  |

| DIL4.    | T2ML: Timer 2 Low Byte Clock Select.<br>This bit selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer        |                              |                |               |              |                |              |                |  |  |  |

|          |                                                                                                                                              | bit selects the              |                |               |              |                | in opiit o b |                |  |  |  |

|          |                                                                                                                                              | low byte use                 |                |               |              |                | 2CN.         |                |  |  |  |

|          |                                                                                                                                              | low byte use                 |                | -             |              |                |              |                |  |  |  |

| Bit3:    |                                                                                                                                              | r 1 Clock Se                 |                |               |              |                |              |                |  |  |  |

|          |                                                                                                                                              |                              |                |               |              |                | n C/T1 is s  | et to logic 1. |  |  |  |

|          |                                                                                                                                              | uses the clo                 |                | by the presc  | ale bits, SC | CA1-SCA0.      |              |                |  |  |  |

| Bit2:    |                                                                                                                                              | uses the sys<br>r 0 Clock Se |                |               |              |                |              |                |  |  |  |

| DILZ.    |                                                                                                                                              | ects the clock               |                | unnlied to Ti | mer () TOM   | l is ignored y | when C/TO    | is set to      |  |  |  |

|          | logic 1.                                                                                                                                     |                              |                |               |              | na ignoreu i   |              | 13 301 10      |  |  |  |

|          | 0                                                                                                                                            | /Timer 0 use                 | s the clock    | defined by t  | he prescale  | e bits, SCA1   | -SCA0.       |                |  |  |  |

|          |                                                                                                                                              | /Timer 0 use                 |                |               | •            | ,              |              |                |  |  |  |

| Bits1-0: | SCA1-SCA                                                                                                                                     | 0: Timer 0/1                 | I Prescale B   | its.          |              |                |              |                |  |  |  |

|          |                                                                                                                                              | control the o                |                | e clock sup   | plied to Tim | ner 0 and Tir  | mer 1 if co  | nfigured to    |  |  |  |

|          | use presca                                                                                                                                   | led clock inp                | outs.          |               |              |                |              |                |  |  |  |

|          | SCA1                                                                                                                                         | SCA0                         | Presc          | aled Clock    |              |                |              |                |  |  |  |

|          | 0                                                                                                                                            | 0                            | System clo     | ock divided l | oy 12        |                |              |                |  |  |  |

|          | 0                                                                                                                                            | 1                            | System cl      | ock divided   | by 4         |                |              |                |  |  |  |

|          | 1                                                                                                                                            | 0                            | •              | ock divided l | -            |                |              |                |  |  |  |

|          | 1                                                                                                                                            | 1                            |                | ock divided   |              |                |              |                |  |  |  |

|          |                                                                                                                                              | ernal clock di               | ivided by 8 is | s synchroniz  | ed with      |                |              |                |  |  |  |

|          | the systen                                                                                                                                   | n clock.                     |                |               |              |                |              |                |  |  |  |

|          |                                                                                                                                              |                              |                |               |              |                |              |                |  |  |  |

|          |                                                                                                                                              |                              |                |               |              |                |              |                |  |  |  |

### Figure 22.6. CKCON: Clock Control Register

| R/W   | R/W                                                                                                                                                                                     | R/W           | R/W         | R/W              | R/W           | R/W          | R/W          | Reset Value |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|------------------|---------------|--------------|--------------|-------------|--|--|--|

| TF3H  | TF3L                                                                                                                                                                                    | TF3LEN        | -           | T3SPLIT          | TR3           | -            | T3XCLK       | 00000000    |  |  |  |

| Bit7  | Bit6                                                                                                                                                                                    | Bit5          | Bit4        | Bit3             | Bit2          | Bit1         | Bit0         | _           |  |  |  |

|       |                                                                                                                                                                                         |               |             |                  |               |              | SFR Address  | : 0x91      |  |  |  |

| Bit7: | TF3H: Timer                                                                                                                                                                             | 3 High Byte   |             | Flag             |               |              |              |             |  |  |  |

|       | Set by hardw                                                                                                                                                                            |               |             |                  | verflows fro  | m 0xFF to    | 0x00 In 16   | hit mode    |  |  |  |

|       | this will occu                                                                                                                                                                          |               |             |                  |               |              |              |             |  |  |  |

|       | enabled, set                                                                                                                                                                            |               |             |                  |               |              |              |             |  |  |  |

|       | TF3H is not                                                                                                                                                                             | •             |             |                  |               |              |              |             |  |  |  |

| Bit6: | TF3L: Timer                                                                                                                                                                             |               |             |                  |               |              | by contrare. |             |  |  |  |

|       | Set by hardv                                                                                                                                                                            |               |             |                  | erflows fror  | n 0xFF to (  | 0x00. When   | this bit is |  |  |  |

|       | set, an interr                                                                                                                                                                          |               |             |                  |               |              |              |             |  |  |  |

|       | will set wher                                                                                                                                                                           |               |             |                  |               |              | •            |             |  |  |  |

|       | ically cleared                                                                                                                                                                          |               |             | U                |               |              |              |             |  |  |  |

| Bit5: | TF3LEN: Tin                                                                                                                                                                             | ner 3 Low B   | yte Interru | pt Enable.       |               |              |              |             |  |  |  |

|       | This bit enab                                                                                                                                                                           | oles/disables | Timer 3 L   | ow Byte inte     | rrupts. If T  | F3LEN is s   | et and Time  | r 3 inter-  |  |  |  |

|       | This bit enables/disables Timer 3 Low Byte interrupts. If TF3LEN is set and Timer 3 inter-<br>rupts are enabled, an interrupt will be generated when the low byte of Timer 3 overflows. |               |             |                  |               |              |              |             |  |  |  |

|       | This bit should be cleared when operating Timer 3 in 16-bit mode.                                                                                                                       |               |             |                  |               |              |              |             |  |  |  |

|       | 0: Timer 3 Low Byte interrupts disabled.                                                                                                                                                |               |             |                  |               |              |              |             |  |  |  |

|       | 1: Timer 3 Lo                                                                                                                                                                           |               |             |                  |               |              |              |             |  |  |  |

| Bit4: | UNUSED. R                                                                                                                                                                               |               |             |                  |               |              |              |             |  |  |  |

| Bit3: | T3SPLIT: Tir                                                                                                                                                                            |               |             |                  |               |              |              |             |  |  |  |

|       | When this bi                                                                                                                                                                            |               |             |                  |               | vith auto-re | eload.       |             |  |  |  |

|       | 0: Timer 3 of                                                                                                                                                                           |               |             |                  |               |              |              |             |  |  |  |

|       | 1: Timer 3 of                                                                                                                                                                           |               |             | ito-reload tin   | ners.         |              |              |             |  |  |  |

| Bit2: | TR3: Timer 3                                                                                                                                                                            |               |             | la O bit as a du |               | .   / . '    |              | Laubu       |  |  |  |

|       | This bit enables/disables Timer 3. In 8-bit mode, this bit enables/disables TMR3H only;                                                                                                 |               |             |                  |               |              |              |             |  |  |  |

|       | TMR3L is always enabled in this mode.                                                                                                                                                   |               |             |                  |               |              |              |             |  |  |  |

|       | 0: Timer 3 disabled.<br>1: Timer 3 enabled.                                                                                                                                             |               |             |                  |               |              |              |             |  |  |  |

| Bit1: | UNUSED. R                                                                                                                                                                               |               | rito — don' | t caro           |               |              |              |             |  |  |  |

| Bit0: | T3XCLK: Tir                                                                                                                                                                             |               |             |                  |               |              |              |             |  |  |  |

| Dito. | This bit sele                                                                                                                                                                           |               |             |                  | ner 3. If Tir | ner 3 is in  | 8-hit mode 1 | his hit     |  |  |  |

|       | selects the e                                                                                                                                                                           |               |             |                  |               |              | ,            |             |  |  |  |

|       | Select bits (                                                                                                                                                                           |               |             |                  |               |              |              |             |  |  |  |

|       | external cloc                                                                                                                                                                           |               |             |                  |               |              |              |             |  |  |  |

|       | 0: Timer 3 ex                                                                                                                                                                           |               |             |                  |               | ded bv 12.   |              |             |  |  |  |

|       | 1: Timer 3 ex                                                                                                                                                                           |               |             |                  |               |              |              | e external  |  |  |  |

|       | oscillator so                                                                                                                                                                           |               |             |                  |               |              |              |             |  |  |  |

|       |                                                                                                                                                                                         |               | 0,010,001   |                  | viin ine sys  | LETTI CIUCK. |              |             |  |  |  |

### Figure 22.20. TMR3CN: Timer 3 Control Register

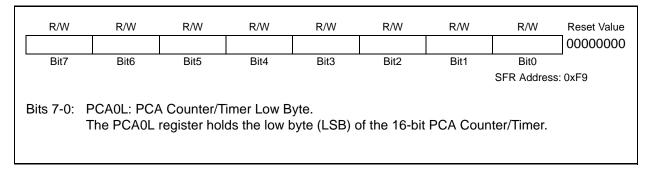

#### Figure 23.14. PCA0L: PCA Counter/Timer Low Byte

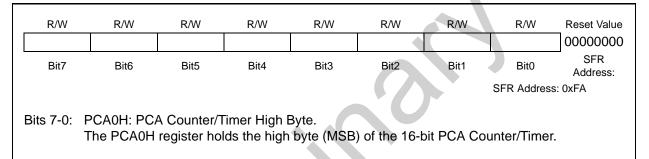

### Figure 23.15. PCA0H: PCA Counter/Timer High Byte

### **Contact Information**

#### Silicon Laboratories Inc.

4635 Boston Lane Austin, Texas 78735 Tel:1+ (512) 416-8500 Fax:1+ (512) 416-9669 Toll Free:1+ (877) 444-3032

Email: productinfo@silabs.com Internet: www.silabs.com