#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 216MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IEBus, SCI, SIO, SPI, USB                       |

| Peripherals                | DMA, POR, PWM, WDT                                                                 |

| Number of I/O              | 73                                                                                 |

| Program Memory Size        | ·                                                                                  |

| Program Memory Type        | ROMIess                                                                            |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 1.3M × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 6x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 120-LQFP                                                                           |

| Supplier Device Package    | 120-LQFP (14x14)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5s726a3p216fp-vz |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 24.13.1 | Clearing TUIR                                                                                                  | 1244 |

|------|---------|----------------------------------------------------------------------------------------------------------------|------|

|      | 24.13.2 | Frequency of Clock Input for Audio                                                                             | 1244 |

| ~    |         |                                                                                                                |      |

|      |         | D-ROM Decoder                                                                                                  |      |

| 25.1 |         |                                                                                                                |      |

|      | 25.1.1  | Formats Supported by CD-ROM Decoder                                                                            |      |

| 25.2 |         | iagrams                                                                                                        |      |

| 25.3 | e       | Descriptions                                                                                                   |      |

|      | 25.3.1  | Enable Control Register (CROMEN)                                                                               |      |

|      | 25.3.2  | Sync Code-Based Synchronization Control Register (CROMSY0)                                                     | 1255 |

|      | 25.3.3  | Decoding Mode Control Register (CROMCTL0)                                                                      |      |

|      | 25.3.4  | EDC/ECC Check Control Register (CROMCTL1)                                                                      | 1258 |

|      | 25.3.5  | Automatic Decoding Stop Control Register (CROMCTL3)                                                            | 1259 |

|      | 25.3.6  | Decoding Option Setting Control Register (CROMCTL4)                                                            | 1260 |

|      | 25.3.7  | HEAD20 to HEAD22 Representation Control Register (CROMCTL5)                                                    | 1262 |

|      | 25.3.8  | Sync Code Status Register (CROMST0)                                                                            | 1263 |

|      | 25.3.9  | Post-ECC Header Error Status Register (CROMST1)                                                                | 1264 |

|      | 25.3.10 | Post-ECC Subheader Error Status Register (CROMST3)                                                             | 1265 |

|      | 25.3.11 | Header/Subheader Validity Check Status Register (CROMST4)                                                      | 1266 |

|      | 25.3.12 | Mode Determination and Link Sector Detection Status Register                                                   |      |

|      |         | (CROMST5)                                                                                                      | 1267 |

|      | 25.3.13 | ECC/EDC Error Status Register (CROMST6)                                                                        | 1268 |

|      | 25.3.14 | Buffer Status Register (CBUFST0)                                                                               |      |

|      | 25.3.15 | Decoding Stoppage Source Status Register (CBUFST1)                                                             |      |

|      | 25.3.16 | Buffer Overflow Status Register (CBUFST2)                                                                      |      |

|      | 25.3.17 | Pre-ECC Correction Header: Minutes Data Register (HEAD00)                                                      |      |

|      | 25.3.18 | Pre-ECC Correction Header: Seconds Data Register (HEAD01)                                                      |      |

|      | 25.3.19 | Pre-ECC Correction Header: Frames (1/75 Second) Data Register                                                  |      |

|      |         | (HEAD02)                                                                                                       | 1273 |

|      | 25.3.20 | Pre-ECC Correction Header: Mode Data Register (HEAD03)                                                         |      |

|      | 25.3.21 | Pre-ECC Correction Subheader: File Number (Byte 16) Data Register                                              |      |

|      | 2010121 | (SHEAD00)                                                                                                      | 1274 |

|      | 25.3.22 | Pre-ECC Correction Subheader: Channel Number (Byte 17) Data Register                                           |      |

|      | 2010122 | (SHEAD01)                                                                                                      |      |

|      | 25.3.23 | Pre-ECC Correction Subheader: Sub-Mode (Byte 18) Data Register                                                 | 1273 |

|      | 25.5.25 | (SHEAD02)                                                                                                      | 1275 |

|      | 25.3.24 | Pre-ECC Correction Subheader: Data Type (Byte 19) Data Register                                                | 1273 |

|      | 25.5.24 | (SHEAD03)                                                                                                      | 1276 |

|      | 25.3.25 | Pre-ECC Correction Subheader: File Number (Byte 20) Data Register                                              | 1270 |

|      | 23.3.23 | (SHEAD04)                                                                                                      | 1276 |

|      |         | (אילעלאוונס, אין אילעלאוונס, אין אילעלאוונס, אין אילעלאוונס, אין אילעלאוונס, אין אילעלאוונס, אין אילעלאוונס, א | 12/0 |

## (1) Reset State

In the reset state, the CPU is reset. There are two kinds of reset, power-on reset and manual reset.

## (2) Exception Handling State

The exception handling state is a transient state that occurs when exception handling sources such as resets or interrupts alter the CPU's processing state flow.

For a reset, the initial values of the program counter (PC) (execution start address) and stack pointer (SP) are fetched from the exception handling vector table and stored; the CPU then branches to the execution start address and execution of the program begins.

For an interrupt, the stack pointer (SP) is accessed and the program counter (PC) and status register (SR) are saved to the stack area. The exception service routine start address is fetched from the exception handling vector table; the CPU then branches to that address and the program starts executing, thereby entering the program execution state.

#### (3) **Program Execution State**

In the program execution state, the CPU sequentially executes the program.

#### (4) Power-Down State

In the power-down state, the CPU stops operating to reduce power consumption. The SLEEP instruction places the CPU in sleep mode, software standby mode, or deep standby mode.

# 9.3 Operation

Operations for the operand cache are described here. Operations for the instruction cache are similar to those for the operand cache except for the address array not having the U bit, and there being no prefetch operation or write operation, or a write-back buffer.

# 9.3.1 Searching Cache

If the operand cache is enabled (OCE bit in CCR1 is 1), whenever data in a cache-enabled area is accessed, the cache will be searched to see if the desired data is in the cache. Figure 9.2 illustrates the method by which the cache is searched.

Entries are selected using bits 10 to 4 of the address used to access memory and the tag address of that entry is read. At this time, the upper three bits of the tag address are always cleared to 0. Bits 31 to 11 of the address used to access memory are compared with the read tag address. The address comparison uses all four ways. When the comparison shows a match and the selected entry is valid (V = 1), a cache hit occurs. When the comparison does not show a match or the selected entry is not valid (V = 0), a cache miss occurs. Figure 9.2 shows a hit on way 1.

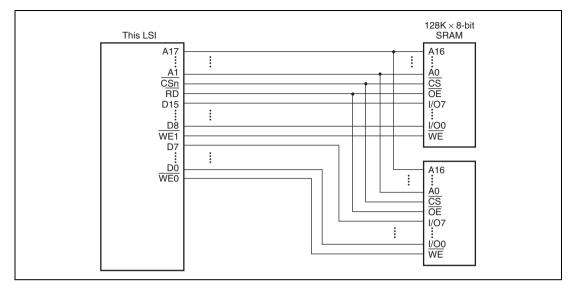

Figure 10.5 Example of 16-Bit Data-Width SRAM Connection

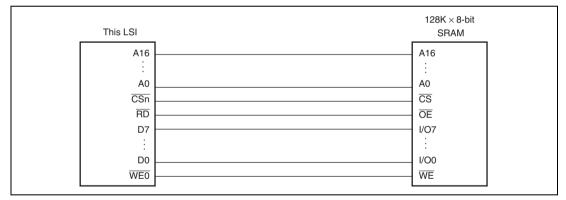

Figure 10.6 Example of 8-Bit Data-Width SRAM Connection

| Channel | Register Name                              | Abbreviation | R/W               | Initial Value | Address    | Access<br>Size |

|---------|--------------------------------------------|--------------|-------------------|---------------|------------|----------------|

| 10      | DMA source address<br>register_10          | SAR_10       | R/W               | H'00000000    | H'FFFE10A0 | 16, 32         |

|         | DMA destination<br>address register_10     | DAR_10       | R/W               | H'00000000    | H'FFFE10A4 | 16, 32         |

|         | DMA transfer count<br>register_10          | DMATCR_10    | R/W               | H'00000000    | H'FFFE10A8 | 16, 32         |

|         | DMA channel control register_10            | CHCR_10      | R/W* <sup>1</sup> | H'00000000    | H'FFFE10AC | 8, 16, 32      |

|         | DMA reload source<br>address register_10   | RSAR_10      | R/W               | H'00000000    | H'FFFE11A0 | 16, 32         |

|         | DMA reload destination address register_10 | RDAR_10      | R/W               | H'00000000    | H'FFFE11A4 | 16, 32         |

|         | DMA reload transfer<br>count register_10   | RDMATCR_10   | R/W               | H'00000000    | H'FFFE11A8 | 16, 32         |

| 11      | DMA source address<br>register_11          | SAR_11       | R/W               | H'00000000    | H'FFFE10B0 | 16, 32         |

|         | DMA destination<br>address register_11     | DAR_11       | R/W               | H'00000000    | H'FFFE10B4 | 16, 32         |

|         | DMA transfer count<br>register_11          | DMATCR_11    | R/W               | H'00000000    | H'FFFE10B8 | 16, 32         |

|         | DMA channel control register_11            | CHCR_11      | R/W* <sup>1</sup> | H'00000000    | H'FFFE10BC | 8, 16, 32      |

|         | DMA reload source<br>address register_11   | RSAR_11      | R/W               | H'00000000    | H'FFFE11B0 | 16, 32         |

|         | DMA reload destination address register_11 | RDAR_11      | R/W               | H'00000000    | H'FFFE11B4 | 16, 32         |

| _       | DMA reload transfer<br>count register_11   | RDMATCR_11   | R/W               | H'00000000    | H'FFFE11B8 | 16, 32         |

#### (2) Bus Modes

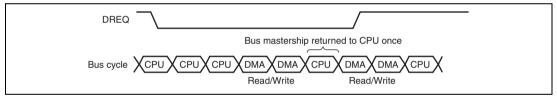

There are two bus modes; cycle steal and burst. Select the mode by the TB bits in the channel control registers (CHCR).

## (a) Cycle Steal Mode

• Normal mode

In normal mode of cycle steal, the bus mastership is given to another bus master after a onetransfer-unit (byte, word, longword, or 16-byte unit) DMA transfer. When another transfer request occurs, the bus mastership is obtained from another bus master and a transfer is performed for one transfer unit. When that transfer ends, the bus mastership is passed to another bus master. This is repeated until the transfer end conditions are satisfied.

The cycle-steal normal mode can be used for any transfer section; transfer request source, transfer source, and transfer destination.

Figure 11.7 shows an example of DMA transfer timing in cycle-steal normal mode. Transfer conditions shown in the figure are;

- Dual address mode

- DREQ low level detection

Figure 11.7 DMA Transfer Example in Cycle-Steal Normal Mode (Dual Address, DREQ Low Level Detection)

• Intermittent Mode 16 and Intermittent Mode 64

In intermittent mode of cycle steal, this module returns the bus mastership to other bus master whenever a unit of transfer (byte, word, longword, or 16 bytes) is completed. If the next transfer request occurs after that, this module obtains the bus mastership from other bus master after waiting for 16 or 64 cycles of  $B\phi$  clock. This module then transfers data of one unit and returns the bus mastership to other bus master. These operations are repeated until the transfer end condition is satisfied. It is thus possible to make lower the ratio of bus occupation by DMA transfer than the normal mode of cycle steal.

When this module obtains again the bus mastership, DMA transfer may be postponed in case of entry updating due to cache miss.

# 12.3.17 Timer Output Control Register 1 (TOCR1)

TOCR1 is an 8-bit readable/writable register that enables/disables PWM synchronized toggle output in complementary PWM mode/reset synchronized PWM mode, and controls output level inversion of PWM output.

| Bit:           | 7 | 6    | 5 | 4 | 3       | 2                | 1    | 0    |

|----------------|---|------|---|---|---------|------------------|------|------|

|                | - | PSYE | - | - | TOCL    | TOCS             | OLSN | OLSP |

| Initial value: | 0 | 0    | 0 | 0 | 0       | 0                | 0    | 0    |

| R/W:           | R | R/W  | R | R | R/(W)*3 | <sup>3</sup> R/W | R/W  | R/W  |

| Bit  | Bit Name | Initial<br>value | R/W | Description                                                                            |

|------|----------|------------------|-----|----------------------------------------------------------------------------------------|

| 7    | _        | 0                | R   | Reserved                                                                               |

|      |          |                  |     | This bit is always read as 0. The write value should always be 0.                      |

| 6    | PSYE     | 0                | R/W | PWM Synchronous Output Enable                                                          |

|      |          |                  |     | This bit selects the enable/disable of toggle output synchronized with the PWM period. |

|      |          |                  |     | 0: Toggle output is disabled                                                           |

|      |          |                  |     | 1: Toggle output is enabled                                                            |

| 5, 4 | _        | All 0            | R   | Reserved                                                                               |

|      |          |                  |     | These bits are always read as 0. The write value should always be 0.                   |

#### (5) Cascaded Operation Example (d)

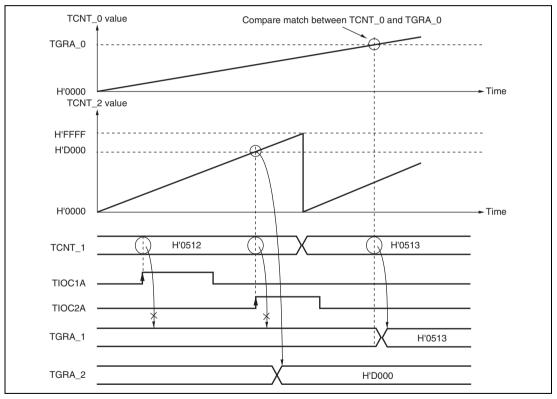

Figure 12.24 illustrates the operation when TCNT\_1 and TCNT\_2 have been cascaded and the I2AE bit in TICCR has been set to 1 to include the TIOC2A pin in the TGRA\_1 input capture conditions. In this example, the IOA0 to IOA3 bits in TIOR\_1 have selected TGRA\_0 compare match or input capture occurrence for the input capture timing while the IOA0 to IOA3 bits in TIOR\_2 have selected the TIOC2A rising edge for the input capture timing.

Under these conditions, as TIOR\_1 has selected TGRA\_0 compare match or input capture occurrence for the input capture timing, the TIOC2A edge is not used for TGRA\_1 input capture condition although the I2AE bit in TICCR has been set to 1.

Figure 12.24 Cascaded Operation Example (d)

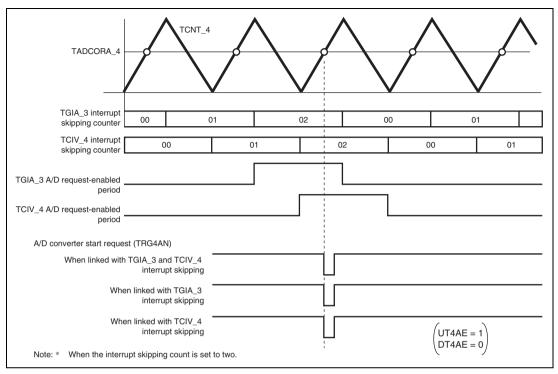

Figure 12.76 Example of A/D Converter Start Request Signal (TRG4AN) Operation Linked with Interrupt Skipping

## 16.3.11 Serial Port Register (SCSPTR)

SCSPTR controls input/output and data of pins multiplexed to the functions of this module. Bits 7 and 6 can control input/output data of  $\overline{\text{RTS}}$  pin. Bits 5 and 4 can control input/output data of  $\overline{\text{CTS}}$  pin. Bits 3 and 2 can control input/output data of SCK pin. Bits 1 and 0 can input data from RxD pin and output data to TxD pin, so they control break of serial transmitting/receiving.

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7     | 6     | 5     | 4     | 3     | 2     | 1      | 0      |

|----------------|----|----|----|----|----|----|---|---|-------|-------|-------|-------|-------|-------|--------|--------|

|                | -  | -  | -  | -  | -  | -  | - | - | RTSIO | RTSDT | CTSIO | CTSDT | SCKIO | SCKDT | SPB2IO | SPB2DT |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0     | 1     | 0     | 1     | 0     | 0     | 0      | 0      |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R/W    | R/W    |

The CPU can always read and write to SCSPTR.

| Bit     | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|----------|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 8 | —        | All 0            | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |          |                  |     | These bits are always read as 0. The write value should always be 0.                                                                                                                                                                                                                                                                                                                                         |

| 7       | RTSIO    | 0                | R/W | RTS Port Input/Output                                                                                                                                                                                                                                                                                                                                                                                        |

|         |          |                  |     | Indicates input or output of the serial port $\overline{\text{RTS}}$ pin.<br>When the $\overline{\text{RTS}}$ pin is actually used as a port outputting<br>the RTSDT bit value, the MCE bit in SCFCR should be<br>cleared to 0.                                                                                                                                                                              |

|         |          |                  |     | 0: RTSDT bit value not output to $\overline{RTS}$ pin                                                                                                                                                                                                                                                                                                                                                        |

|         |          |                  |     | 1: RTSDT bit value output to RTS pin                                                                                                                                                                                                                                                                                                                                                                         |

| 6       | RTSDT    | 1                | R/W | RTS Port Data                                                                                                                                                                                                                                                                                                                                                                                                |

|         |          |                  |     | Indicates the input/output data of the serial port $\overline{\text{RTS}}$ pin. Input/output is specified by the RTSIO bit. For output, the RTSDT bit value is output to the $\overline{\text{RTS}}$ pin. The $\overline{\text{RTS}}$ pin status is read from the RTSDT bit regardless of the RTSIO bit setting. However, $\overline{\text{RTS}}$ input/output must be set in the general purpose I/O ports. |

|         |          |                  |     | 0: Input/output data is low level                                                                                                                                                                                                                                                                                                                                                                            |

|         |          |                  |     | 1: Input/output data is high level                                                                                                                                                                                                                                                                                                                                                                           |

| Bit:           | 31        | 30        | 29        | 28        | 27        | 26        | 25        | 24        | 23        | 22        | 21        | 20        | 19        | 18        | 17        | 16        |

|----------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|                | SPD31     | SPD30     | SPD29     | SPD28     | SPD27     | SPD26     | SPD25     | SPD24     | SPD23     | SPD22     | SPD21     | SPD20     | SPD19     | SPD18     | SPD17     | SPD16     |

| Initial value: | Undefined |

| R/W:           | R/W       |

| Bit:           | 15        | 14        | 13        | 12        | 11        | 10        | 9         | 8         | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|                | SPD15     | SPD14     | SPD13     | SPD12     | SPD11     | SPD10     | SPD9      | SPD8      | SPD7      | SPD6      | SPD5      | SPD4      | SPD3      | SPD2      | SPD1      | SPD0      |

| Initial value: | Undefined |

Initial Value: Undefined U

#### 17.3.6 Sequence Control Register (SPSCR)

SPSCR sets the sequence controlled method when this module operates in master mode. If the contents of SPSCR are changed while the MSTR and SPE bits in the control register (SPCR) are 1 with the function of this module enabled in master mode, the subsequent operation cannot be guaranteed.

| Bit:           | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0          |

|----------------|---|---|---|---|---|---|------------|------------|

| [              | — | — | — | — | — | _ | SPS<br>LN1 | SPS<br>LN0 |

| Initial value: | 0 | 0 | 0 | 0 | 0 | 0 | 0          | 0          |

| R/W:           | R | R | R | R | R | R | R/W        | R/W        |

| Bit    | Bit Name | Initial<br>Value | R/W | Description                                                                    |

|--------|----------|------------------|-----|--------------------------------------------------------------------------------|

| 7 to 2 |          | All 0            | R   | Reserved                                                                       |

| _      |          |                  |     | The write value should always be 0. Otherwise, operation cannot be guaranteed. |

# 21.3.10 Receive Data Assign Register (SIRDAR)

SIRDAR specifies the position of the receive data in a frame (slot number).

| Bit: 15          | 14 | 13 | 12 | 11    | 10    | 9     | 8     | 7    | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

|------------------|----|----|----|-------|-------|-------|-------|------|---|---|---|-------|-------|-------|-------|

| RDLE             | -  | -  | -  | RDLA3 | RDLA2 | RDLA1 | RDLA0 | RDRE | - | - | - | RDRA3 | RDRA2 | RDRA1 | RDRA0 |

| Initial Value: 0 | 0  | 0  | 0  | 0     | 0     | 0     | 0     | 0    | 0 | 0 | 0 | 0     | 0     | 0     | 0     |

| R/W: R/W         | R  | R  | R  | R/W   | R/W   | R/W   | R/W   | R/W  | R | R | R | R/W   | R/W   | R/W   | R/W   |

| Bit      | Bit Name | Initial<br>Value | R/W | Description                                                                                    |

|----------|----------|------------------|-----|------------------------------------------------------------------------------------------------|

| 15       | RDLE     | 0                | R/W | Receive Left-Channel Data Enable                                                               |

|          |          |                  |     | 0: Disables left-channel data reception                                                        |

|          |          |                  |     | 1: Enables left-channel data reception                                                         |

| 14 to 12 | _        | All 0            | R   | Reserved                                                                                       |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                           |

| 11       | RDLA3    | 0                | R/W | Receive Left-Channel Data Assigns 3 to 0                                                       |

| 10       | RDLA2    | 0                | R/W | Specify the position of left-channel data in a receive                                         |

| 9        | RDLA1    | 0                | R/W | frame as B'0000 (0) to B'1110 (14).                                                            |

| 8        | RDLA0    | 0                | R/W | 1111: Setting prohibited                                                                       |

|          |          |                  |     | <ul> <li>Receive data for the left channel is stored in the<br/>SIRDL bit in SIRDR.</li> </ul> |

| 7        | RDRE     | 0                | R/W | Receive Right-Channel Data Enable                                                              |

|          |          |                  |     | 0: Disables right-channel data reception                                                       |

|          |          |                  |     | 1: Enables right-channel data reception                                                        |

| 6 to 4   | _        | All 0            | R   | Reserved                                                                                       |

|          |          |                  |     | These bits are always read as 0. The write value should always be 0.                           |

| 3        | RDRA3    | 0                | R/W | Receive Right-Channel Data Assigns 3 to 0                                                      |

| 2        | RDRA2    | 0                | R/W | Specify the position of right-channel data in a receive                                        |

| 1        | RDRA1    | 0                | R/W | frame as B'0000 (0) to B'1110 (14).                                                            |

| 0        | RDRA0    | 0                | R/W | 1111: Setting prohibited                                                                       |

|          |          |                  |     | Receive data for the right channel is stored in the SIRDR bit in SIRDR.                        |

Bit 15 to 0 — Remote Request pending flags for mailboxes 31 to 16 respectively.

| Bit[15:0]: RFPR1 | Description                                                                        |

|------------------|------------------------------------------------------------------------------------|

| 0                | [Clearing Condition] Writing '1' (Initial value)                                   |

| 1                | Corresponding Mailbox received Remote Frame                                        |

|                  | [Setting Condition]<br>Completion of remote frame receive in corresponding mailbox |

#### RFPR0

| Bit:           | 15   | 14          | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|----------------|------|-------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Γ              |      | RFPR0[15:0] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Initial value: | 0    | 0           | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W: F         | R/W* | R/W*        | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |

Note: \* Only when writing a '1' to clear.

Bit 15 to 0 — Remote Request pending flags for mailboxes 15 to 0 respectively.

| Bit[15:0]: RFPR0 | Description                                                                        |

|------------------|------------------------------------------------------------------------------------|

| 0                | [Clearing Condition] Writing '1' (Initial value)                                   |

| 1                | Corresponding Mailbox received Remote Frame                                        |

|                  | [Setting Condition]<br>Completion of remote frame receive in corresponding mailbox |

## (7) Mailbox Interrupt Mask Register (MBIMR)

The MBIMR1 and MBIMR0 are 16-bit read/write registers. The MBIMR only prevents the setting of IRR related to the Mailbox activities, that are IRR[1] – Data Frame Received Interrupt, IRR[2] – Remote Frame Receive Interrupt, IRR[8] – Mailbox Empty Interrupt, and IRR[9] – Message OverRun/OverWrite Interrupt. If a mailbox is configured as receive, a mask at the corresponding bit position prevents the generation of a receive interrupt (IRR[1] and IRR[2] and IRR[9]) but does not prevent the setting of the corresponding bit in the RXPR or RFPR or UMSR. Similarly when a mailbox has been configured for transmission, a mask prevents the generation of an Interrupt signal and setting of an Mailbox Empty Interrupt due to successful transmission or abortion of transmission (IRR[8]), however, it does not prevent this module from clearing the corresponding TXPR/TXCR bit + setting the TXACK bit for successful transmission, and it does not prevent this module from clearing the corresponding TXPR/TXCR bit + setting the Corresponding TXPR/TXCR bit + setting the ABACK bit for abortion of the transmission.

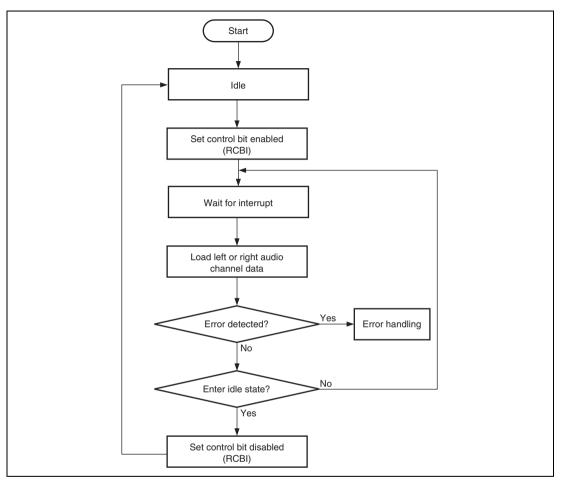

Figure 24.8 illustrates the receiver data transfer using interrupts.

Figure 24.8 Receiver Data Transfer Flow Diagram - Interrupt Driven

Interrupts to indicate that the channel status information register is full occur after frame 30 has been received and only if the information has changed. When the first four bytes have been stored an interrupt occurs.

The meanings of bits in the two-byte status field shown in figure 25.15 are given below. The values of the non-assigned bits are undefined.

|       |                                                                                      |                                               |         |         |         |         | St      | atus    |         |        |        |        |         |   |   |

|-------|--------------------------------------------------------------------------------------|-----------------------------------------------|---------|---------|---------|---------|---------|---------|---------|--------|--------|--------|---------|---|---|

| 15    | 14                                                                                   | 13                                            | 12      | 11      | 10      | 9       | 8       | 7       | 6       | 5      | 4      | 3      | 2       | 1 | 0 |

| PERR  | QERF                                                                                 | R EDCE                                        | . —     | _       | _       | _       | _       | SD      | SY      |        | FM[2   | :0]    | HD      | _ | _ |

| [Lege | end]                                                                                 |                                               |         |         |         |         |         |         |         |        |        |        |         |   |   |

| PERF  | PERR: Indicates that a P-parity error remains.                                       |                                               |         |         |         |         |         |         |         |        |        |        |         |   |   |

| QERI  | QERR: Indicates that a Q-parity error remains.                                       |                                               |         |         |         |         |         |         |         |        |        |        |         |   |   |

| EDCE  | EDCE: Indicates that a remaining error was detected in post-correction EDC checking. |                                               |         |         |         |         |         |         |         |        |        |        |         |   |   |

| SD:   | Ind                                                                                  | Indicates that a short sector was encountered |         |         |         |         |         |         |         |        |        |        |         |   |   |

| SY:   | Ind                                                                                  | dicates                                       | that a  | a sync  | code    | was in  | terpola | ated.   |         |        |        |        |         |   |   |

| FM:   | Ind                                                                                  | dicates                                       | the d   | ata for | mat     |         |         |         |         |        |        |        |         |   |   |

|       | 00                                                                                   | 1: Moo                                        | de 0    |         |         |         |         |         |         |        |        |        |         |   |   |

|       | 01                                                                                   | 0: Moo                                        | de 1    |         |         |         |         |         |         |        |        |        |         |   |   |

|       | 01                                                                                   | 1: Lon                                        | g (forr | nat wit | th no E | EDC ai  | nd EC   | C)      |         |        |        |        |         |   |   |

|       | 10                                                                                   | 0: Moo                                        | de 2 (r | ion-XA  | N)      |         |         |         |         |        |        |        |         |   |   |

|       | 10                                                                                   | 1: Moo                                        | de 2 F  | orm 1   |         |         |         |         |         |        |        |        |         |   |   |

|       | 11                                                                                   | 0: Moo                                        | de 2 F  | orm 2   |         |         |         |         |         |        |        |        |         |   |   |

| HD:   | He                                                                                   | eader c                                       | continu | uity (m | inutes  | , secoi | nds, ar | nd fram | nes (1/ | ′75) a | re non | -seque | ential) |   |   |

The value of the storage flag field in figure 25.15 is incremented every time the data for one sector are output. The value starts at H'0000 and wraps back around to H'0000 after incrementation reaches H'FFFF. Note that the upper byte and lower byte in the storage flag are swapped.

# (6) Frame Number Update Interrupt

With the host controller function selected, an interrupt is generated at the timing at which the frame number is updated. With the function controller function selected, the SOFR interrupt is generated when the frame number is updated.

When the function controller function is selected, this module updates the frame number and generates an SOFR interrupt if it detects a new SOF packet during full-speed operation.

# (7) VBUS Interrupt

If there has been a change in the VBUS pin, the VBUS interrupt is generated. The level of the VBUS pin can be checked with the VBSTS bit in INTSTS0. Whether the host controller is connected or disconnected can be confirmed using the VBUS interrupt. However, if the system is activated with the host controller connected, the first VBUS interrupt is not generated because there is no change in the VBUS pin.

## (8) **Resume Interrupt**

With the function controller function selected, the resume interrupt is generated when the USB bus state changes (from J-state to K-state, or from J-state to SE0) while the device state is the suspended state. Recovery from the suspended state is detected by means of the resume interrupt.

With the host controller function selected, the resume interrupt is not generated; use the BCHG interrupt to detect the change of the USB bus state.

# (9) BCHG Interrupt

The BCHG interrupt is generated when the USB bus state has changed. The BCHG interrupt can be used to detect whether or not the peripheral device is connected when the host controller function has been selected and can also be used to detect a remote wakeup. The BCHG interrupt is generated regardless of whether the host controller function or function controller function has been selected.

# (3) DMA Transfers (D0FIFO/D1FIFO Port)

# (a) Overview of DMA Transfers

For pipes 1 to 9, the FIFO port can be accessed using the direct memory access controller. When accessing the buffer for the pipe targeted for DMA transfer is enabled, a DMA transfer request is issued.

The unit of transfer to the FIFO port should be selected using the MBW bit in DnFIFOSEL and the pipe targeted for the DMA transfer should be selected using the CURPIPE bit. The selected pipe should not be changed during the DMA transfer.

# (b) Auto Recognition of DMA Transfer Completion

With this module, it is possible to complete FIFO data writing through DMA transfer by controlling DMA transfer end signal input. When a transfer end signal is sampled, the module enables buffer memory transmission (the same condition as when BVAL = 1).

# (c) DnFIFO Auto Clear Mode (D0FIFO/D1FIFO Port Reading Direction)

If 1 is set for the DCLRM bit in DnFIFOSEL, the module automatically clears the buffer memory of the selected pipe when reading of the data from the buffer memory has been completed.

Table 27.22 shows the packet reception and buffer memory clearing processing for each of the various settings. As shown, the buffer clear conditions depend on the value set to the BFRE bit. Using the DCLRM bit eliminates the need for the buffer to be cleared even if a situation occurs that necessitates clearing of the buffer. This makes it possible to carry out DMA transfers without involving software.

This function can be set only in the buffer memory reading direction.

# (10) Port J Port Register 0 (PJPR0: Available only in SH726B)

| Bit:           | 15 | 14         | 13         | 12         | 11         | 10         | 9         | 8         | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|----------------|----|------------|------------|------------|------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

|                | -  | PJ14<br>PR | PJ13<br>PR | PJ12<br>PR | PJ11<br>PR | PJ10<br>PR | PJ9<br>PR | PJ8<br>PR | PJ7<br>PR | PJ6<br>PR | PJ5<br>PR | PJ4<br>PR | PJ3<br>PR | PJ2<br>PR | PJ1<br>PR | PJ0<br>PR |

| Initial value: | 0  | PJ14       | PJ13       | PJ12       | PJ11       | PJ10       | PJ9       | PJ8       | PJ7       | PJ6       | PJ5       | PJ4       | PJ3       | PJ2       | PJ1       | PJ0       |

| R/W:           | R  | R          | R          | R          | R          | R          | R         | R         | R         | R         | R         | R         | R         | R         | R         | R         |

# (11) Port K Port Register 0 (PKPR0: Available only in SH726B)

| Bit:           | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1         | 0         |

|----------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|-----------|-----------|

|                | -  | -  | -  | -  | -  | -  | - | - | - | - | - | - | - | - | PK1<br>PR | PK0<br>PR |

| Initial value: | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | PK1       | PK0       |

| R/W:           | R  | R  | R  | R  | R  | R  | R | R | R | R | R | R | R | R | R         | R         |

| Module Name | Register<br>Abbreviation | Bit 31/23/15/7 | Bit 30/22/14/6 | Bit 29/21/13/5 | Bit 28/20/12/4 | Bit 27/19/11/3 | Bit 26/18/10/2 | Bit 25/17/9/1   | Bit 24/16/8/0    |

|-------------|--------------------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|------------------|

| CD-ROM      | SHEAD02                  | SHEAD02[7]     | SHEAD02[6]     | SHEAD02[5]     | SHEAD02[4]     | SHEAD02[3]     | SHEAD02[2]     | SHEAD02[1]      | SHEAD02[0]       |

| decoder     | SHEAD03                  | SHEAD03[7]     | SHEAD03[6]     | SHEAD03[5]     | SHEAD03[4]     | SHEAD03[3]     | SHEAD03[2]     | SHEAD03[1]      | SHEAD03[0]       |

|             | SHEAD04                  | SHEAD04[7]     | SHEAD04[6]     | SHEAD04[5]     | SHEAD04[4]     | SHEAD04[3]     | SHEAD04[2]     | SHEAD04[1]      | SHEAD04[0]       |

|             | SHEAD05                  | SHEAD05[7]     | SHEAD05[6]     | SHEAD05[5]     | SHEAD05[4]     | SHEAD05[3]     | SHEAD05[2]     | SHEAD05[1]      | SHEAD05[0]       |

|             | SHEAD06                  | SHEAD06[7]     | SHEAD06[6]     | SHEAD06[5]     | SHEAD06[4]     | SHEAD06[3]     | SHEAD06[2]     | SHEAD06[1]      | SHEAD06[0]       |

|             | SHEAD07                  | SHEAD07[7]     | SHEAD07[6]     | SHEAD07[5]     | SHEAD07[4]     | SHEAD07[3]     | SHEAD07[2]     | SHEAD07[1]      | SHEAD07[0]       |

|             | HEAD20                   | HEAD20[7]      | HEAD20[6]      | HEAD20[5]      | HEAD20[4]      | HEAD20[3]      | HEAD20[2]      | HEAD20[1]       | HEAD20[0]        |

|             | HEAD21                   | HEAD21[7]      | HEAD21[6]      | HEAD21[5]      | HEAD21[4]      | HEAD21[3]      | HEAD21[2]      | HEAD21[1]       | HEAD21[0]        |

|             | HEAD22                   | HEAD22[7]      | HEAD22[6]      | HEAD22[5]      | HEAD22[4]      | HEAD22[3]      | HEAD22[2]      | HEAD22[1]       | HEAD22[0]        |

|             | HEAD23                   | HEAD23[7]      | HEAD23[6]      | HEAD23[5]      | HEAD23[4]      | HEAD23[3]      | HEAD23[2]      | HEAD23[1]       | HEAD23[0]        |

|             | SHEAD20                  | SHEAD20[7]     | SHEAD20[6]     | SHEAD20[5]     | SHEAD20[4]     | SHEAD20[3]     | SHEAD20[2]     | SHEAD20[1]      | SHEAD20[0]       |

|             | SHEAD21                  | SHEAD21[7]     | SHEAD21[6]     | SHEAD21[5]     | SHEAD21[4]     | SHEAD21[3]     | SHEAD21[2]     | SHEAD21[1]      | SHEAD21[0]       |

|             | SHEAD22                  | SHEAD22[7]     | SHEAD22[6]     | SHEAD22[5]     | SHEAD22[4]     | SHEAD22[3]     | SHEAD22[2]     | SHEAD22[1]      | SHEAD22[0]       |

|             | SHEAD23                  | SHEAD23[7]     | SHEAD23[6]     | SHEAD23[5]     | SHEAD23[4]     | SHEAD23[3]     | SHEAD23[2]     | SHEAD23[1]      | SHEAD23[0]       |

|             | SHEAD24                  | SHEAD24[7]     | SHEAD24[6]     | SHEAD24[5]     | SHEAD24[4]     | SHEAD24[3]     | SHEAD24[2]     | SHEAD24[1]      | SHEAD24[0]       |

|             | SHEAD25                  | SHEAD25[7]     | SHEAD25[6]     | SHEAD25[5]     | SHEAD25[4]     | SHEAD25[3]     | SHEAD25[2]     | SHEAD25[1]      | SHEAD25[0]       |

|             | SHEAD26                  | SHEAD26[7]     | SHEAD26[6]     | SHEAD26[5]     | SHEAD26[4]     | SHEAD26[3]     | SHEAD26[2]     | SHEAD26[1]      | SHEAD26[0]       |

|             | SHEAD27                  | SHEAD27[7]     | SHEAD27[6]     | SHEAD27[5]     | SHEAD27[4]     | SHEAD27[3]     | SHEAD27[2]     | SHEAD27[1]      | SHEAD27[0]       |

|             | CBUFCTL0                 | CBUF_AUT       | CBUF_EN        |                | CBUF_MD[1]     | CBUF_MD[0]     | CBUF_TS        | CBUF_Q          | _                |

|             | CBUFCTL1                 | BS_MIN[7]      | BS_MIN[6]      | BS_MIN[5]      | BS_MIN[4]      | BS_MIN[3]      | BS_MIN[2]      | BS_MIN[1]       | BS_MIN[0]        |

|             | CBUFCTL2                 | BS_SEC[7]      | BS_SEC[6]      | BS_SEC[5]      | BS_SEC[4]      | BS_SEC[3]      | BS_SEC[2]      | BS_SEC[1]       | BS_SEC[0]        |

|             | CBUFCTL3                 | BS_FRM[7]      | BS_FRM[6]      | BS_FRM[5]      | BS_FRM[4]      | BS_FRM[3]      | BS_FRM[2]      | BS_FRM[1]       | BS_FRM[0]        |

|             | CROMSTOM                 | _              |                | ST_SYILM       | ST_SYNOM       | ST_BLKSM       | ST_BLKLM       | ST_SECSM        | ST_SECLM         |

|             | ROMDECRST                | LOGICRST       | RAMRST         |                | _              | _              | _              | _               | _                |

|             | RSTSTAT                  | RAMCLRST       |                |                | _              | _              | _              | _               | —                |

|             | SSI                      | BYTEND         | BITEND         | BUFEND0[1]     | BUFEND0[0]     | BUFEND1[1]     | BUFEND1[0]     | _               | _                |

|             | INTHOLD                  | ISEC           | ITARG          | ISY            | IERR           | IBUF           | IREADY         | _               | —                |

|             | INHINT                   | INHISEC        | INHITARG       | INHISY         | INHIERR        | INHIBUF        | INHIREADY      | PREINH<br>REQDM | PREINHI<br>READY |

|             | STRMDIN0                 | STRMDIN[31]    | STRMDIN[30]    | STRMDIN[29]    | STRMDIN[28]    | STRMDIN[27]    | STRMDIN[26]    | STRMDIN[25]     | STRMDIN[24]      |

|             |                          | STRMDIN[23]    | STRMDIN[22]    | STRMDIN[21]    | STRMDIN[20]    | STRMDIN[19]    | STRMDIN[18]    | STRMDIN[17]     | STRMDIN[16]      |

# 35.2 Power-On/Power-Off Sequence

The 1.2-V power supply ( $V_{cc}$ , PLLV<sub>cc</sub>) and 3.3-V power supply ( $PV_{cc}$ , AV<sub>cc</sub>) can be turned on and off in any order.

When turning on the power, be sure to drive both the  $\overline{\text{TRST}}$  and  $\overline{\text{RES}}$  pins low; otherwise, the output pins and input/output pins output undefined levels, resulting in system malfunction.

When turning off the power, drive the  $\overline{\text{TRST}}$  and  $\overline{\text{RES}}$  pins low if the undefined output may cause a problem.