# E·X FL Renesas Electronics America Inc - R5S726B0D216FP#V0 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                             |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | SH2A-FPU                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 216MHz                                                                             |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IEBus, SCI, SIO, SPI, USB                               |

| Peripherals                | DMA, POR, PWM, WDT                                                                 |

| Number of I/O              | 94                                                                                 |

| Program Memory Size        | -                                                                                  |

| Program Memory Type        | ROMIess                                                                            |

| EEPROM Size                |                                                                                    |

| RAM Size                   | 1.3M x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                          |

| Data Converters            | A/D 8x10b                                                                          |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 144-LQFP                                                                           |

| Supplier Device Package    | 144-LFQFP (20x20)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5s726b0d216fp-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Classification                       | Symbol                                  | I/O | Name                                               | Function                                                                               |

|--------------------------------------|-----------------------------------------|-----|----------------------------------------------------|----------------------------------------------------------------------------------------|

| Multi-function<br>timer pulse unit 2 | TCLKA,<br>TCLKB,<br>TCLKC,<br>TCLKD     | I   | Timer clock<br>input                               | External clock input pins for the timer.                                               |

|                                      | TIOCOA,<br>TIOCOB,<br>TIOCOC,<br>TIOCOD | I/O | Input capture/<br>output compare<br>(channel 0)    | The TGRA_0 to TGRD_0 input capture input/output compare output/PWM output pins.        |

|                                      | TIOC1A,<br>TIOC1B                       | I/O | Input capture/<br>output compare<br>(channel 1)    | The TGRA_1 and TGRB_1 input<br>capture input/output compare<br>output/PWM output pins. |

|                                      | TIOC2A,<br>TIOC2B                       | I/O | Input capture/<br>output compare<br>(channel 2)    | The TGRA_2 and TGRB_2 input capture input/output compare output/PWM output pins.       |

|                                      | TIOC3A,<br>TIOC3B,<br>TIOC3C,<br>TIOC3D | I/O | Input capture/<br>output compare<br>(channel 3)    | The TGRA_3 to TGRD_3 input capture input/output compare output/PWM output pins.        |

|                                      | TIOC4A,<br>TIOC4B,<br>TIOC4C,<br>TIOC4D | I/O | Input capture/<br>output compare<br>(channel 4)    | The TGRA_4 to TGRD_4 input capture input/output compare output/PWM output pins.        |

| Realtime clock                       | RTC_X1                                  | I   | Crystal                                            | Connected to 4 MHz crystal                                                             |

|                                      | RTC_X2                                  | 0   | resonator for<br>realtime clock/<br>external clock | resonator.<br>The RTC_X1 pin can also be used<br>to input an external clock.           |

| Serial                               | TxD4 to TxD0                            | 0   | Transmit data                                      | Data output pins.                                                                      |

| communication<br>interface with      | RxD4 to RxD0                            | Ι   | Receive data                                       | Data input pins.                                                                       |

| FIFO                                 | SCK4 to SCK0                            | I/O | Serial clock                                       | Clock input/output pins.                                                               |

|                                      | RTS2 to RTS0                            | 0   | Transmit<br>request                                | Modem control pin.                                                                     |

|                                      | CTS2 to CTS0                            | Ι   | Enable to transmit                                 | Modem control pin.                                                                     |

#### Table 5.5 CKOEN[1:0] Settings

| Setting | Normal Operation  | Software Standby Mode          | Deep Standby Mode*             |

|---------|-------------------|--------------------------------|--------------------------------|

| 00      | Output            | Output off (Hi-Z)              | Output off (Hi-Z)              |

| 01      | Output            | Low-level output               | Low-level output               |

| 10      | Output            | Output (unstable clock output) | Low-level or high-level output |

| 11      | Output off (Hi-Z) | Output off (Hi-Z)              | Output off (Hi-Z)              |

Note: \* When deep standby mode is canceled, the head of the first output CKIO clock pulse may be missed.

| Bit    | Bit Name   | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8 to 6 | DMAIW[2:0] | 000              | R/W | Wait states between access cycles when DMA single address transfer is performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        |            |                  |     | Specify the number of idle cycles to be inserted after<br>an access to an external device with DACK when<br>DMA single address transfer is performed. The<br>method of inserting idle cycles depends on the<br>contents of DMAIWA.                                                                                                                                                                                                                                                                                                                                                                        |

|        |            |                  |     | 000: No idle cycle inserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |            |                  |     | 001: 1 idle cycle inserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |            |                  |     | 010: 2 idle cycles inserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |            |                  |     | 011: 4 idle cycles inserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |            |                  |     | 100: 6 idle cycles inserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |            |                  |     | 101: 8 idle cycles inserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |            |                  |     | 110: 10 idle cycles inserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|        |            |                  |     | 111: 12 idle cycles inserted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5      | DMAIWA     | 0                | R/W | Method of inserting wait states between access<br>cycles when DMA single address transfer is<br>performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |            |                  |     | Specifies the method of inserting the idle cycles<br>specified by the DMAIW[2:0] bit. Clearing this bit will<br>make this LSI insert the idle cycles when another<br>device, which includes this LSI, drives the data bus<br>after an external device with DACK drove it. However,<br>when the external device with DACK drives the data<br>bus continuously, idle cycles are not inserted. Setting<br>this bit will make this LSI insert the idle cycles after an<br>access to an external device with DACK, even when<br>the continuous access cycles to an external device<br>with DACK are performed. |

|        |            |                  |     | 0: Idle cycles inserted when another device drives the data bus after an external device with DACK drove it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|        |            |                  |     | 1: Idle cycles always inserted after an access to an<br>external device with DACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4      | _          | 1                | R   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|        |            |                  |     | This bit is always read as 1. The write value should always be 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### (c) Initialization

In complementary PWM mode, there are six registers that must be initialized. In addition, there is a register that specifies whether to generate dead time (it should be used only when dead time generation should be disabled).

Before setting complementary PWM mode with bits MD3 to MD0 in the timer mode register (TMDR), the following initial register values must be set.

TGRC\_3 operates as the buffer register for TGRA\_3, and should be set with 1/2 the PWM carrier cycle + dead time Td. The timer cycle buffer register (TCBR) operates as the buffer register for the timer cycle data register (TCDR), and should be set with 1/2 the PWM carrier cycle. Set dead time Td in the timer dead time data register (TDDR).

When dead time is not needed, the TDER bit in the timer dead time enable register (TDER) should be cleared to 0, TGRC\_3 and TGRA\_3 should be set to 1/2 the PWM carrier cycle + 1, and TDDR should be set to 1.

Set the respective initial PWM duty values in buffer registers TGRD\_3, TGRC\_4, and TGRD\_4.

The values set in the five buffer registers excluding TDDR are transferred simultaneously to the corresponding compare registers when complementary PWM mode is set.

Set TCNT\_4 to H'0000 before setting complementary PWM mode.

| <b>Table 12.54</b> | <b>Registers and</b> | <b>Counters H</b> | Requiring | Initialization |

|--------------------|----------------------|-------------------|-----------|----------------|

|--------------------|----------------------|-------------------|-----------|----------------|

| Set Value                                                                                                      |

|----------------------------------------------------------------------------------------------------------------|

| 1/2 PWM carrier cycle + dead time Td (1/2 PWM carrier cycle + 1 when dead time generation is disabled by TDER) |

| Dead time Td (1 when dead time generation is disabled by TDER)                                                 |

| 1/2 PWM carrier cycle                                                                                          |

| Initial PWM duty value for each phase                                                                          |

| H'0000                                                                                                         |

|                                                                                                                |

Note: The TGRC\_3 set value must be the sum of 1/2 the PWM carrier cycle set in TCBR and dead time Td set in TDDR. When dead time generation is disabled by TDER, TGRC\_3 must be set to 1/2 the PWM carrier cycle + 1.

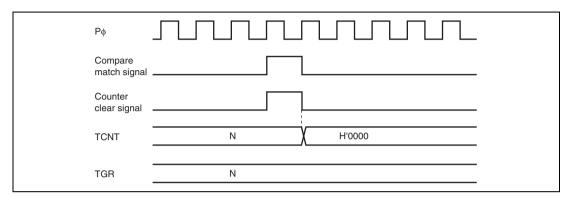

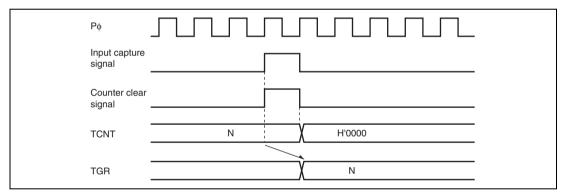

#### (4) Timing for Counter Clearing by Compare Match/Input Capture

Figure 12.84 shows the timing when counter clearing on compare match is specified, and Figure 12.85 shows the timing when counter clearing on input capture is specified.

Figure 12.84 Counter Clear Timing (Compare Match)

Figure 12.85 Counter Clear Timing (Input Capture)

#### 15.3.19 Control Register 5 (RCR5)

When the RCKSEL[1:0] bits are set to 00, the 32.768-kHz RTC\_X1 clock pulses are counted; when the RCKSEL[1:0] bits are set to 01, the EXTAL clock pulses are counted; and when the RCKSEL[1:0] bits are set to 10, the RTC\_X1 clock pulses are counted to implement the clock function.

| Bit:           | 7 | 6 | 5 | 4 | 3 | 2 | 1         | 0         |

|----------------|---|---|---|---|---|---|-----------|-----------|

|                | - | - | - | - | - | - | RCKS      | EL[1:0]   |

| Initial value: | 0 | 0 | 0 | 0 | 0 | 0 | Undefined | Undefined |

| R/W:           | R | R | R | R | R | R | R/W       | R/W       |

|        |             | Initial   |     |                                                                      |

|--------|-------------|-----------|-----|----------------------------------------------------------------------|

| Bit    | Bit Name    | Value     | R/W | Description                                                          |

| 7 to 2 |             | All 0     | R   | Reserved                                                             |

|        |             |           |     | These bits are always read as 0. The write value should always be 0. |

| 1, 0   | RCKSEL[1:0] | Undefined | R/W | Operation clock select                                               |

|        |             |           |     | Operation clock can be selected from RTC_X1 or EXTAL.                |

|        |             |           |     | The setting of these bits should not be switched during operation.   |

|        |             |           |     | 00: Selects 32.768-kHz RTC_X1.                                       |

|        |             |           |     | 01: Selects EXTAL.                                                   |

|        |             |           |     | 10: Selects RTC_X1.                                                  |

|        |             |           |     | 11: Setting prohibited.                                              |

# Section 16 Serial Communication Interface with FIFO

This LSI has an five-channel serial communication interface with FIFO that supports both asynchronous and clock synchronous serial communication. It also has 16-stage FIFO registers for both transmission and reception independently for each channel that enable this LSI to perform efficient high-speed continuous communication.

# 16.1 Features

- Asynchronous serial communication:

- Serial data communication is performed by start-stop in character units. This module can communicate with a universal asynchronous receiver/transmitter (UART), an asynchronous communication interface adapter (ACIA), or any other communications chip that employs a standard asynchronous serial system. There are eight selectable serial data communication formats.

- Data length: 7 or 8 bits

- Stop bit length: 1 or 2 bits

- Parity: Even, odd, or none

- Receive error detection: Parity, framing, and overrun errors

- Break detection: Break is detected when a framing error is followed by at least one frame at the space 0 level (low level). It is also detected by reading the RxD level directly from the serial port register when a framing error occurs.

- Clock synchronous serial communication:

- Serial data communication is synchronized with a clock signal. This module can communicate with other chips having a clock synchronous communication function. There is one serial data communication format.

- Data length: 8 bits

- Receive error detection: Overrun errors

- Full duplex communication: The transmitting and receiving sections are independent, so this module can transmit and receive simultaneously. Both sections use 16-stage FIFO buffering, so high-speed continuous data transfer is possible in both the transmit and receive directions.

- On-chip baud rate generator with selectable bit rates

- Internal or external transmit/receive clock source: From either baud rate generator (internal) or SCK pin (external)

#### 18.5.4 Data Alignment

When two serial flash memories are connected, the serial flash memory connected to the pin SPBIO3\_0-SPBIO0\_0 has the address 2n and the serial flash memory connected to the pin SPBIO3\_1-SPBIO0\_1 has the address 2n + 1. The data should be accessed in word or larger units. It cannot be accessed in byte units. Data alignment when two serial flash memories are connected is shown in table 18.5.

| <b>Table 18.5</b> | Data Alignment when Two Serial Flash Memories are Connected |  |

|-------------------|-------------------------------------------------------------|--|

|-------------------|-------------------------------------------------------------|--|

|                              |                     | Serial Flash Memory          |                              |  |  |

|------------------------------|---------------------|------------------------------|------------------------------|--|--|

| Operation                    |                     | SPBIO3_0 to<br>SPBIO0_0 Pins | SPBIO3_1 to<br>SPBIO0_1 Pins |  |  |

| Word access to address 0     |                     | Data 15 to 8                 | Data 7 to 0                  |  |  |

| Word access to address 2     |                     | Data 15 to 8                 | Data 7 to 0                  |  |  |

| Longword access to address 0 | 1 word (address 0)  | Data 31 to 24                | Data 23 to 16                |  |  |

|                              | 2 words (address 2) | Data 15 to 8                 | Data 7 to 0                  |  |  |

#### 18.5.5 Operating Modes

This module has two operating modes: external address space read mode and SPI operating mode.

In external address space read mode, a read access to the SPI multi I/O bus space is converted into SPI communication and data is received. After data acquisition, data is returned to the bus master that is the issuing source. For details, see section 18.5.6, External Address Space Read Mode.

In SPI operating mode, arbitrary SPI communication is carried out using register settings. For details, see section 18.5.8, SPI Operating Mode.

#### 18.5.6 External Address Space Read Mode

A read access to the SPI multi I/O bus space can be converted into SPI communication in external address space read mode. Further, the commands, optional commands, and option data issued for reading can be modified using registers.

In external address space read mode, either normal read operation or burst read operation can be selected. The transfer format is determined based on the common control register (CMNCR), SSL delay register (SSLDR), bit rate setting register (SPBCR), data read control register (DRCR), data read command setting register (DRCMR), data read extended address setting register (DREAR), data read option setting register (DROPR), and data read enable setting register (DRENR).

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                             |

|-----|----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 0   | RFOVF    | 0                | R/W | Receive FIFO Overflow                                                                                                   |

|     |          |                  |     | 0: No receive FIFO overflow                                                                                             |

|     |          |                  |     | 1: Receive FIFO overflow                                                                                                |

|     |          |                  |     | A receive FIFO overflow means that writing has occurred due to reception operation when the receive FIFO is full.       |

|     |          |                  |     | When an overflow of the receive FIFO occurs, the receive data which caused the overflow is lost.                        |

|     |          |                  |     | <ul> <li>When this bit is set to 1, it is cleared to 0 by this<br/>module. Writing 0 to this bit is invalid.</li> </ul> |

| Bit 9: IRR9 | Description                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------|

| 0           | No pending notification of message overrun/overwrite                                            |

|             | [Clearing condition]                                                                            |

|             | Clearing of all bit in UMSR/setting MBIMR for all UMSR set (initial value)                      |

| 1           | A receive message has been discarded due to overrun condition or a message has been overwritten |

|             | [Setting condition]                                                                             |

|             | Message is received while the corresponding RXPR and/or RFPR = 1 and MBIMR = $0$                |

**Bit 8 - Mailbox Empty Interrupt Flag (IRR8):** This bit is set when one of the messages set for transmission has been successfully sent (corresponding TXACK flag is set) or has been successfully aborted (corresponding ABACK flag is set). In Event Triggered mode the related TXPR is also cleared and this mailbox is now ready to accept a new message data for the next transmission. In Time Trigger mode TXPR for the Mailboxes from 30 to 24 is not cleared after a successful transmission in order to keep transmitting at each programmed basic cycle. In effect, this bit is set by an OR'ed signal of the TXACK and ABACK bits not masked by the corresponding MBIMR flag. Therefore, this bit is automatically cleared when all the TXACK and ABACK bits are cleared. It is also cleared by writing a '1' to all the correspondent bit position in MBIMR. Writing to this bit position has no effect.

| Bit 8: IRR8 | Description                                                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | Messages set for transmission or transmission cancellation request NOT progressed. (Initial value)                                                                       |

|             | [Clearing Condition]                                                                                                                                                     |

|             | All the TXACK and ABACK bits are cleared/setting MBIMR for all TXACK and ABACK set                                                                                       |

| 1           | Message has been transmitted or aborted, and new message can be stored<br>(in TT mode Mailbox 24 to 30 can be programmed with a new message only<br>in case of abortion) |

|             | [Setting condition]                                                                                                                                                      |

|             | When a TXACK or ABACK bit is set (if related $MBIMR = 0$ ).                                                                                                              |

| mode                       | requested setting                                                                        | function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Time Slave                 | TXPR[30] = 0<br>&<br>MBC[30]!= 3'b000                                                    | TCNTR is sampled at each SOF detected on the CAN Bus<br>and stored into an internal register. When a valid Time<br>Reference Message is received into Mailbox-31 the value of<br>TCNTR (stored at the SOF) is copied into Ref_Mark.                                                                                                                                                                                                                                                                                                                            |

|                            | &<br>CMAX!= 3'b111                                                                       | CCR embedded in the received Reference Message is<br>copied to CCR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                            | &                                                                                        | If Next_is_Gap = 1, IRR13 is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                            | MBC[31] = 3'b011                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (Potential)                | TXPR[30] = 1                                                                             | Two cases are covered:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (Potential)<br>Time Master | &<br>MBC[30] = 3'b000<br>&<br>DLC[30] > 0<br>&<br>CMAX!= 3'b111<br>&<br>MBC[31] = 3'b011 | <ol> <li>When a valid Time Reference message is received into<br/>Mailbox-31 the value of TCNTR stored into an internal<br/>register at the SOF is copied into Ref_Mark.</li> <li>CCR embedded in the received Reference Message is<br/>copied to CCR.</li> <li>If Next_is_Gap = 1, IRR13 is set.</li> <li>When a Time Reference message is transmitted from<br/>Mailbox-30 the value of TCNTR stored into an internal<br/>register at the SOF is copied into Ref_Mark.</li> <li>CCR is incremented when TTT of Mailbox-30 matches<br/>with CYCTR .</li> </ol> |

|                            |                                                                                          | CCR is embedded into the first data byte of the time reference message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                            |                                                                                          | { Data0[7:6], CCR[5:0] } .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### • Setting Tx-Trigger Time

The Tx-Trigger Time(TTT) must be set in ascending order shown below, and the difference between them has to satisfy the following expressions. TEW in the following expressions is the register value.

TTT (Mailbox-24) < TTT (Mailbox-25) < TTT (Mailbox-26) < TTT (Mailbox-27) < TTT (Mailbox-28) < TTT (Mailbox-29) < TTT (Mailbox-30)

and

TTT (Mailbox-i) – TTT (Mailbox-i-1) > TEW + the maximum frame length + 9

TTT (Mailbox-24) to TTT (Mailbox-29) correspond to Time\_Marks, and TTT (Mailbox-30) corresponds to Time\_Ref showing the length of a basic cycle, respectively when working as potential time master.

#### 24.8.4 Transmitter Module Data Transfer

Once the transmitter module has left the idle state, it is ready for data transfer. Data transfer timing can be achieved in three ways. Either the transfer is done by interrupts, DMA requests or by polling the status register. There is a shared interrupt line (for both transmit and receive) and a single transmitter DMA request line.

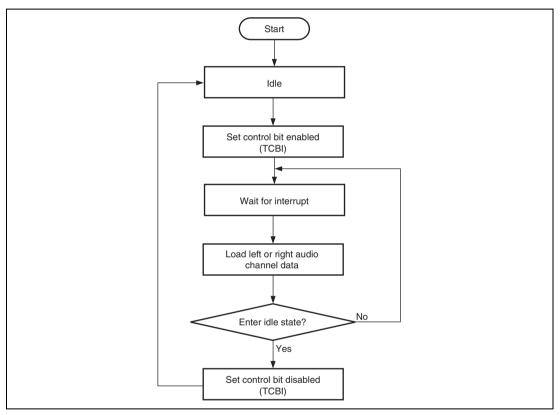

Figure 24.5 shows a data transfer with an interrupt for the transmitter.

Figure 24.5 Transmitter Data Transfer Flow Diagram - Interrupt Driven

| Bit | Bit Name      | Initial<br>Value | R/W | Description                                                                                                                                                     |

|-----|---------------|------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | LINK_DET      | 0                | R   | Indicates that a link block (run-out 1 to run-in 4) was detected.                                                                                               |

|     |               |                  |     | Since detection is based on the data before ECC correction, LINK_DET may also be set to 1 if data erroneously happens to contain the same code as a link block. |

| 1   | LINK_<br>SDET | 0                | R   | Indicates that a link block was detected within seven sectors after the start of decoding.                                                                      |

| 0   | LINK_<br>OUT1 | 0                | R   | Indicates that the sector after ECC correction has been identified as a run-out 1 sector.                                                                       |

|     |               |                  |     | This bit is only valid when an IERR interrupt is not generated (i.e. when ECC correction was successful).                                                       |

#### 25.3.13 ECC/EDC Error Status Register (CROMST6)

The ECC/EDC error status register (CROMST6) indicates ECC processing error or EDC check error before/after ECC correction.

| Bit:           | 7          | 6 | 5             | 4            | 3           | 2           | 1           | 0           |

|----------------|------------|---|---------------|--------------|-------------|-------------|-------------|-------------|

|                | ST_<br>ERR | - | ST_<br>ECCABT | ST_<br>ECCNG | ST_<br>ECCP | ST_<br>ECCQ | ST_<br>EDC1 | ST_<br>EDC2 |

| Initial value: | 0          | 0 | 0             | 0            | 0           | 0           | 0           | 0           |

| R/W:           | R          | R | R             | R            | R           | R           | R           | R           |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                             |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | ST_ERR   | 0                | R   | Indicates that the decoded block after ECC correction contains any error (even in a single byte).                                                                                                                                                                                                       |

| 6   | _        | 0                | R   | Reserved                                                                                                                                                                                                                                                                                                |

|     |          |                  |     | This bit is always read as 0 and cannot be modified.                                                                                                                                                                                                                                                    |

| 5   | 5 ST_ 0  |                  | R   | Indicates that ECC processing was discontinued.                                                                                                                                                                                                                                                         |

|     | ECCABT   |                  |     | This bit is set to 1 when a transition from sector to sector occurs while ECC correction is in progress. This does not indicate a problem for ECC correction if the BUF_NG bit in the CBUFST2 register is 0 at the same time. Whether or not this is so depends on the timing of the sector transition. |

# 26.2 Input/Output Pins

Table 26.1 shows the A/D converter pins.

#### Table 26.1 Pin Configuration

| Pin Name                       | Symbol | I/O   | Function                                              |

|--------------------------------|--------|-------|-------------------------------------------------------|

| Analog power supply pin        | AVcc   | Input | Analog power supply pin                               |

| Analog ground pin              | AVss   | Input | Analog ground pin and A/D conversion reference ground |

| Analog reference voltage pin   | AVref  | Input | A/D converter reference voltage pin                   |

| Analog input pin 0*            | AN0    | Input | Analog input                                          |

| Analog input pin 1*            | AN1    | Input | _                                                     |

| Analog input pin 2*            | AN2    | Input | _                                                     |

| Analog input pin 3*            | AN3    | Input | _                                                     |

| Analog input pin 4*            | AN4    | Input | _                                                     |

| Analog input pin 5*            | AN5    | Input | _                                                     |

| Analog input pin 6             | AN6    | Input | _                                                     |

| Analog input pin 7             | AN7    | Input | _                                                     |

| A/D external trigger input pin | ADTRG  | Input | External trigger input to start A/D conversion        |

Note: \* Only analog input pins 0 to 5 (AN0 to AN5) can be used in the SH726A Group.

| Register Name                              | Abbreviation | R/W | Address     | Access<br>Size |

|--------------------------------------------|--------------|-----|-------------|----------------|

| Interrupt status register 2                | INTSTS2      | R/W | H'FFFF C044 | 16             |

| BRDY interrupt status register             | BRDYSTS      | R/W | H'FFFF C046 | 16             |

| NRDY interrupt status register             | NRDYSTS      | R/W | H'FFFF C048 | 16             |

| BEMP interrupt status register             | BEMPSTS      | R/W | H'FFFF C04A | 16             |

| Frame number register                      | FRMNUM       | R/W | H'FFFF C04C | 16             |

| USB address register                       | USBADDR      | R   | H'FFFF C050 | 16             |

| USB request type register                  | USBREQ       | R   | H'FFFF C054 | 16             |

| USB request value register                 | USBVAL       | R   | H'FFFF C056 | 16             |

| USB request index register                 | USBINDX      | R   | H'FFFF C058 | 16             |

| USB request length register                | USBLENG      | R   | H'FFFF C05A | 16             |

| DCP configuration register                 | DCPCFG       | R/W | H'FFFF C05C | 16             |

| DCP maximum packet size register           | DCPMAXP      | R/W | H'FFFF C05E | 16             |

| DCP control register                       | DCPCTR       | R/W | H'FFFF C060 | 16             |

| Pipe window select register                | PIPESEL      | R/W | H'FFFF C064 | 16             |

| Pipe configuration register                | PIPECFG      | R/W | H'FFFF C068 | 16             |

| Pipe maximum packet size register          | PIPEMAXP     | R/W | H'FFFF C06C | 16             |

| Pipe cycle control register                | PIPEPERI     | R/W | H'FFFF C06E | 16             |

| Pipe 1 control register                    | PIPE1CTR     | R/W | H'FFFF C070 | 16             |

| Pipe 2 control register                    | PIPE2CTR     | R/W | H'FFFF C072 | 16             |

| Pipe 3 control register                    | PIPE3CTR     | R/W | H'FFFF C074 | 16             |

| Pipe 4 control register                    | PIPE4CTR     | R/W | H'FFFF C076 | 16             |

| Pipe 5 control register                    | PIPE5CTR     | R/W | H'FFFF C078 | 16             |

| Pipe 6 control register                    | PIPE6CTR     | R/W | H'FFFF C07A | 16             |

| Pipe 7 control register                    | PIPE7CTR     | R/W | H'FFFF C07C | 16             |

| Pipe 8 control register                    | PIPE8CTR     | R/W | H'FFFF C07E | 16             |

| Pipe 9 control register                    | PIPE9CTR     | R/W | H'FFFF C080 | 16             |

| Pipe 1 transaction counter enable register | PIPE1TRE     | R/W | H'FFFF C090 | 16             |

| Pipe 1 transaction counter register        | PIPE1TRN     | R/W | H'FFFF C092 | 16             |

| Pipe 2 transaction counter enable register | PIPE2TRE     | R/W | H'FFFF C094 | 16             |

| Pipe 2 transaction counter register        | PIPE2TRN     | R/W | H'FFFF C096 | 16             |

| Pipe 3 transaction counter enable register | PIPE3TRE     | R/W | H'FFFF C098 | 16             |

#### (2) DATA-PID

When the function controller function is selected, this module operates as follows in response to the received PID.

- 1. IN direction

- DATA0: Sent as data packet PID

- DATA1: Not sent

- DATA2: Not sent

- mDATA: Not sent

- 2. OUT direction

- DATA0: Received normally as data packet PID

- DATA1: Received normally as data packet PID

- DATA2: Packets are ignored

- mDATA: Packets are ignored

## (3) Interval Counter

The isochronous interval can be set using the IITV bits in PIPEPERI. The interval counter enables the functions shown in table 27.25 when the function controller function is selected. When the host controller function is selected, this module generates the token issuance timing. When the host controller function is selected, the interval counter operation is the same as the interrupt transfer operation.

| Table 27.25 | Functions of the Interval Counter when the Function Controller Function is |

|-------------|----------------------------------------------------------------------------|

|             | Selected                                                                   |

| Transfer<br>Direction | Function                                 | Conditions for Detection                                                                               |

|-----------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------|

| IN                    | IN buffer flush function                 | When an IN token cannot be normally received in the interval frame during an isochronous IN transfer   |

| OUT                   | Notifies that a token not being received | When an OUT token cannot be normally received in the interval frame during an isochronous OUT transfer |

The interval count is carried out when an SOF is received or for interpolated SOFs, so the isochronisms can be maintained even if an SOF is damaged. The frame interval that can be set is the  $2^{IITV}$  frame.

|             | Register     |                |                |                |                |                |                |               |               |

|-------------|--------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------|---------------|

| Module Name | Abbreviation | Bit 31/23/15/7 | Bit 30/22/14/6 | Bit 29/21/13/5 | Bit 28/20/12/4 | Bit 27/19/11/3 | Bit 26/18/10/2 | Bit 25/17/9/1 | Bit 24/16/8/0 |

| Bus state   | CS4WCR       | _              |                | _              | _              | —              |                | _             | _             |

| controller  |              | _              |                | _              | BAS            | —              | WW[2]          | WW[1]         | WW[0]         |

|             |              | _              |                | _              | SW[1]          | SW[0]          | WR[3]          | WR[2]         | WR[1]         |

|             |              | WR[0]          | WM             | _              | _              | _              |                | HW[1]         | HW[0]         |

|             | CS4WCR       | _              |                | _              | _              | _              |                | _             | _             |

|             |              | _              |                | BST[1]         | BST[0]         | —              |                | BW[1]         | BW[0]         |

|             |              | _              |                | _              | SW[1]          | SW[0]          | W[3]           | W[2]          | W[1]          |

|             |              | W[0]           | WM             | _              | _              | —              |                | HW[1]         | HW[0]         |

|             |              |                |                |                |                |                |                |               |               |

|             | SDCR         | _              |                | _              | _              | —              |                | _             | —             |

|             |              | _              |                | _              | A2ROW[1]       | A2ROW[0]       |                | A2COL[1]      | A2COL[0]      |

|             |              | _              |                | DEEP           | _              | RFSH           | RMODE          | PDOWN         | BACTV         |

|             |              | _              |                | _              | A3ROW[1]       | A3ROW[0]       |                | A3COL[1]      | A3COL[0]      |

|             | RTCSR        | _              | _              | _              | _              | _              | _              | _             | _             |

|             |              | _              |                | _              | _              | —              |                | _             | —             |

|             |              | _              | _              | _              | _              | —              | _              | _             | _             |

|             |              | CMF            | CMIE           | CKS[2]         | CKS[1]         | CKS[0]         | RRC[2]         | RRC[1]        | RRC[0]        |

|             | RTCNT        | —              | _              | —              | —              | —              | _              | —             | —             |

|             |              | _              | _              | _              | _              | _              | _              | _             | _             |

|             |              | _              | _              | _              | _              | _              | _              | _             | _             |

|             |              |                |                |                |                |                |                |               |               |

|             | RTCOR        | —              | _              | —              | —              | —              | _              | —             | —             |

|             |              | _              |                | _              | _              | —              |                | _             | —             |

|             |              | _              |                | _              | _              | —              |                | _             | —             |

|             |              |                |                |                |                |                |                |               |               |

| User break  | BAR_0        | BA31           | BA30           | BA29           | BA28           | BA27           | BA26           | BA25          | BA24          |

| controller  |              | BA23           | BA22           | BA21           | BA20           | BA19           | BA18           | BA17          | BA16          |

|             |              | BA15           | BA14           | BA13           | BA12           | BA11           | BA10           | BA9           | BA8           |

|             |              | BA7            | BA6            | BA5            | BA4            | ВАЗ            | BA2            | BA1           | BA0           |

| Module Name     | Register<br>Abbreviation                      | Bit 31/23/15/7     | Bit 30/22/14/6     | Bit 29/21/13/5     | Bit 28/20/12/4     | Bit 27/19/11/3     | Bit 26/18/10/2     | Bit 25/17/9/1      | Bit 24/16/8/0      |

|-----------------|-----------------------------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Controller area |                                               |                    | EXTID[14]          | EXTID[13]          | EXTID[12]          | EXTID[11]          | EXTID[10]          | EXTID[9]           | EXTID[8]           |

| network         | 0_L_0<br>(n = 0 to 31)                        | EXTID[7]           | EXTID[6]           | EXTID[5]           | EXTID[4]           | EXTID[3]           | EXTID[2]           | EXTID[1]           | EXTID[0]           |

|                 | $MBn_LAFM0_0$<br>(n = 0 to 31)* <sup>1</sup>  | —                  | STDID_<br>LAFM[10] | STDID_<br>LAFM[9]  | STDID_<br>LAFM[8]  | STDID_<br>LAFM[7]  | STDID_<br>LAFM[6]  | STDID_<br>LAFM[5]  | STDID_<br>LAFM[4]  |

|                 |                                               | STDID_<br>LAFM[3]  | STDID_<br>LAFM[2]  | STDID_<br>LAFM[1]  | STDID_<br>LAFM[0]  | _                  | IDE                | EXTID_<br>LAFM[17] | EXTID_<br>LAFM[16] |

|                 | MBn_LAFM0_0<br>$(n = 0 \text{ to } 31)^{*^2}$ | IDE                |                    |                    | STDID_<br>LAFM[10] | STDID_<br>LAFM[9]  | STDID_<br>LAFM[8]  | STDID_<br>LAFM[7]  | STDID_<br>LAFM[6]  |

|                 |                                               | STDID_<br>LAFM[5]  | STDID_<br>LAFM[4]  | STDID_<br>LAFM[3]  | STDID_<br>LAFM[2]  | STDID_<br>LAFM[1]  | STDID_<br>LAFM[0]  | EXTID_<br>LAFM[17] | EXTID_<br>LAFM[16] |

|                 | MBn_LAFM1_0<br>(n = 0 to 31)                  | EXTID_<br>LAFM[15] | EXTID_<br>LAFM[14] | EXTID<br>_LAFM[13] | EXTID_<br>LAFM[12] | EXTID_<br>LAFM[11] | EXTID_<br>LAFM[10] | EXTID_<br>LAFM[9]  | EXTID_<br>LAFM[8]  |

|                 |                                               | EXTID_<br>LAFM[7]  | EXTID_<br>LAFM[6]  | EXTID_<br>LAFM[5]  | EXTID_<br>LAFM[4]  | EXTID_<br>LAFM[3]  | EXTID_<br>LAFM[2]  | EXTID_<br>LAFM[1]  | EXTID_<br>LAFM[0]  |

|                 | MBn_DATA_01_<br>0 (n = 0 to 31)               | MSG_DATA0          |

|                 |                                               | MSG_DATA1          |

|                 | MBn_DATA_23_<br>0 (n = 0 to 31)               | MSG_DATA2          |

|                 |                                               | MSG_DATA3          |

|                 | MBn_DATA_45_                                  | MSG_DATA4          |

|                 | 0 (n = 0 to 31)                               | MSG_DATA5          |

|                 | MBn_DATA_67_<br>0 (n = 0 to 31)               | MSG_DATA6          |

|                 |                                               | MSG_DATA7          |

|                 | MBn_CONTROL                                   | _                  | _                  | NMC                | —                  | _                  | MBC[2]             | MBC[1]             | MBC[0]             |

|                 | 1_0 (n =0)                                    | _                  | _                  | _                  | _                  | DLC[3]             | DLC[2]             | DLC[1]             | DLC[0]             |

|                 | MBn_CONTROL                                   | _                  | _                  | NMC                | АТХ                | DART               | MBC[2]             | MBC[1]             | MBC[0]             |

|                 | 1_0 (n = 1 to 31)                             | _                  |                    |                    | _                  | DLC[3]             | DLC[2]             | DLC[1]             | DLC[0]             |

|                 | MBn_TIMESTA                                   | TS15               | TS14               | TS13               | TS12               | TS11               | TS10               | TS9                | TS8                |

|                 | MP_0 (n = 0 to<br>15, 30, 31)                 | TS7                | TS6                | TS5                | TS4                | TS3                | TS2                | TS1                | TS0                |

|                 | MBn_TTT_0                                     | TTT15              | TTT14              | TTT13              | TTT12              | TTT11              | TTT10              | TTT9               | TTT8               |

|                 | (n = 24 to 30)                                | TTT7               | TTT6               | TTT5               | TTT4               | тттз               | TTT2               | TTT1               | ТТТО               |

|                      | Register     |                |                |                |                |                |                |               |               |

|----------------------|--------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------|---------------|

| Module Name          | Abbreviation | Bit 31/23/15/7 | Bit 30/22/14/6 | Bit 29/21/13/5 | Bit 28/20/12/4 | Bit 27/19/11/3 | Bit 26/18/10/2 | Bit 25/17/9/1 | Bit 24/16/8/0 |

| General              | PCDR0        | _              | _              | _              | _              | _              |                | _             | PC8DR         |

| purpose I/O<br>ports |              | PC7DR          | PC6DR          | PC5DR          | PC4DR          | PC3DR          | PC2DR          | PC1DR         | PC0DR         |

|                      | PCPR0        | _              | _              | _              | _              | _              | _              | _             | PC8PR         |

|                      |              | PC7PR          | PC6PR          | PC5PR          | PC4PR          | PC3PR          | PC2PR          | PC1PR         | PC0PR         |

|                      | PDCR3        | _              |                | PD15MD1        | PD15MD0        | _              |                | PD14MD1       | PD14MD0       |

|                      |              | _              |                | PD13MD1        | PD13MD0        | _              |                | PD12MD1       | PD12MD0       |

|                      | PDCR2        | _              | _              | PD11MD1        | PD11MD0        | _              | _              | PD10MD1       | PD10MD0       |

|                      |              | _              | _              | PD9MD1         | PD9MD0         | _              | _              | PD8MD1        | PD8MD0        |

|                      | PDCR1        | _              | PD7MD2         | PD7MD1         | PD7MD0         | _              | PD6MD2         | PD6MD1        | PD6MD0        |

|                      |              | _              | PD5MD2         | PD5MD1         | PD5MD0         | _              | PD4MD2         | PD4MD1        | PD4MD0        |

|                      | PDCR0        | _              | PD3MD2         | PD3MD1         | PD3MD0         | _              | PD2MD2         | PD2MD1        | PD2MD0        |

|                      |              | _              | PD1MD2         | PD1MD1         | PD1MD0         | _              | PD0MD2         | PD0MD1        | PD0MD0        |

|                      | PDIOR0       | PD15IOR        | PD14IOR        | PD13IOR        | PD12IOR        | PD11IOR        | PD10IOR        | PD9IOR        | PD8IOR        |

|                      |              | PD7IOR         | PD6IOR         | PD5IOR         | PD4IOR         | PD3IOR         | PD2IOR         | PD1IOR        | PD0IOR        |

|                      | PDDR0        | PD15DR         | PD14DR         | PD13DR         | PD12DR         | PD11DR         | PD10DR         | PD9DR         | PD8DR         |

|                      |              | PD7DR          | PD6DR          | PD5DR          | PD4DR          | PD3DR          | PD2DR          | PD1DR         | PD0DR         |

|                      | PDPR0        | PD15PR         | PD14PR         | PD13PR         | PD12PR         | PD11PR         | PD10PR         | PD9PR         | PD8PR         |

|                      |              | PD7PR          | PD6PR          | PD5PR          | PD4PR          | PD3PR          | PD2PR          | PD1PR         | PD0PR         |

|                      | PECR1        | _              | _              | PE7MD1         | PE7MD0         | _              | _              | PE6MD1        | PE6MD0        |

|                      |              | _              | _              | PE5MD1         | PE5MD0         | _              | _              | PE4MD1        | PE4MD0        |

|                      | PECR0        | _              | _              | PE3MD1         | PE3MD0         | _              | _              | PE2MD1        | PE2MD0        |

|                      |              | _              | _              | PE1MD1         | PE1MD0         | _              | _              | PE0MD1        | PE0MD0        |

|                      | PEIOR0       | _              | _              | _              | _              | _              | _              | _             | _             |

|                      |              | PE7IOR         | PE6IOR         | PE5IOR         | PE4IOR         | PE3IOR         | PE2IOR         | PE1IOR        | PEOIOR        |

|                      | PEDR0        | _              | _              | _              | _              | _              |                | _             | _             |

|                      |              | PE7DR          | PE6DR          | PE5DR          | PE4DR          | PE3DR          | PE2DR          | PE1DR         | PE0DR         |

|                      | PEPR0        | _              | _              |                | _              | _              |                | _             | _             |

|                      |              | PE7PR          | PE6PR          | PE5PR          | PE4PR          | PE3PR          | PE2PR          | PE1PR         | PE0PR         |

|                      | PFCR1        | _              | _              | PF7MD1         | PF7MD0         | _              |                | PF6MD1        | PF6MD0        |

|                      |              | —              | _              | PF5MD1         | PF5MD0         | _              |                | PF4MD1        | PF4MD0        |

# Section 36 States and Handling of Pins

This section describes pin states in each operating mode and how to handle pins.

## 36.1 Pin States

Table 36.1 shows the pin states in each operating mode.

As for the input/output functions, input buffers are listed on the upper column and output buffers on the lower column.

| <b>Table 36.1</b> | Pin States |

|-------------------|------------|

|-------------------|------------|

| Pin Function                 |                     |                            |   | Pin State                                          |                     |                                   |                                        |                                   |                                   |                          |

|------------------------------|---------------------|----------------------------|---|----------------------------------------------------|---------------------|-----------------------------------|----------------------------------------|-----------------------------------|-----------------------------------|--------------------------|

|                              | Pin Name            |                            |   | Normal State<br>(Other than<br>States at<br>Right) | Power-On<br>Reset*1 | Pin State Retained* <sup>2</sup>  |                                        | Power-Down State                  |                                   |                          |

|                              |                     |                            |   |                                                    |                     | EBUSKEE                           | PE* <sup>3</sup> (Other<br>s at Right) | - Power-On<br>Reset <sup>∗⁴</sup> | Deep Standby<br>Mode              | Software Standby<br>Mode |

| Туре                         |                     |                            |   |                                                    |                     | 0                                 | 1                                      |                                   |                                   |                          |

| Clock                        | EXTAL* <sup>6</sup> | Clock<br>operation<br>mode | 0 | I                                                  | I                   | 1                                 |                                        | I/Z* <sup>5</sup>                 | 1                                 |                          |

|                              |                     |                            | 1 | z                                                  | z                   | Z                                 |                                        |                                   | z                                 | Z                        |

|                              | XTAL* <sup>6</sup>  |                            | • | 0                                                  | 0                   | 0                                 |                                        |                                   | 0/L*5                             | O/L* <sup>5</sup>        |

|                              | СКІО                | Boot<br>mode               | 0 | 0/Z*7                                              | 0                   | 0                                 | O/Z* <sup>7</sup>                      |                                   | 0/Z*7                             | O/Z*7                    |

|                              |                     |                            | 1 | O/Z*7                                              | 0                   |                                   | 0/Z*7                                  |                                   | 0/Z* <sup>7</sup>                 | O/Z*7                    |

|                              | AUDIO_CLK           |                            |   | I                                                  | _                   |                                   |                                        |                                   | z                                 | z                        |

|                              | AUDIO_X1*6          |                            |   | I/Z* <sup>8</sup>                                  | I                   | 1                                 |                                        |                                   | z                                 | z                        |

|                              | AUDIO_X2*6          |                            |   | 0/L*8                                              | 0                   | 0                                 |                                        |                                   | L                                 | L                        |

|                              | AUDIO_XOUT          |                            |   | O/L* <sup>8</sup>                                  | _                   | 0/Z* <sup>9</sup> * <sup>18</sup> |                                        |                                   | O/Z* <sup>9</sup> * <sup>16</sup> | L/Z* <sup>9</sup>        |

| System<br>control            | RES                 |                            |   | I                                                  | I                   | I                                 |                                        |                                   | I                                 | 1                        |

|                              | WDTOVF              |                            |   | 0                                                  | _                   | Н                                 |                                        | н                                 | н                                 |                          |

| Operation<br>mode<br>control | MD_BOOT             |                            |   | _                                                  | I                   |                                   |                                        | _                                 | _                                 |                          |

|                              | MD_CLK              |                            |   | _                                                  | I                   | _                                 |                                        |                                   | _                                 | _                        |

|                              | ASEMD               |                            |   | I                                                  | I                   | I                                 |                                        |                                   | 1                                 | 1                        |