Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, POR, PWM, WDT                         |

| Number of I/O              | 41                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 25x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151c4t6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Note: ADC1 can be served by DMA1.

## 3.10 Digital-to-analog converter (DAC)

- 12-bit DAC with output buffer

- Synchronized update capability using TIM4

- DMA capability

- External triggers for conversion

- Input reference voltage V<sub>REF+</sub> for better resolution

Note: DAC can be served by DMA1.

## 3.11 Ultra-low-power comparators

The medium-density STM8L151x4/6 and STM8L152x4/6 embed two comparators (COMP1 and COMP2) sharing the same current bias and voltage reference. The voltage reference can be internal or external (coming from an I/O).

- One comparator with fixed threshold (COMP1).

- One comparator rail to rail with fast or slow mode (COMP2). The threshold can be one of the following:

- DAC output

- External I/O

- Internal reference voltage or internal reference voltage sub multiple (1/4, 1/2, 3/4)

The two comparators can be used together to offer a window function. They can wake up from Halt mode.

# 3.12 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports. TIM4 and ADC1 DMA channels can also be remapped.

The highly flexible routing interface allows application software to control the routing of different I/Os to the TIM1 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1, COMP2, DAC and the internal reference voltage  $V_{REFINT}$ . It also provides a set of registers for efficiently managing the charge transfer acquisition sequence (*Section 3.13: Touch sensing*).

# 3.13 Touch sensing

Medium-density STM8L151x4/6 and STM8L152x4/6 devices provide a simple solution for adding capacitive sensing functionality to any application. Capacitive sensing technology is able to detect finger presence near an electrode which is protected from direct touch by a dielectric (example, glass, plastic). The capacitive variation introduced by a finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the electrode capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. In medium-density STM8L151x4/6

### 3.14.2 16-bit general purpose timers

- 16-bit autoreload (AR) up/down-counter

- 7-bit prescaler adjustable to fixed power of 2 ratios (1...128)

- 2 individually configurable capture/compare channels

- PWM mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

- Synchronization with other timers or external signals (external clock, reset, trigger and enable)

### 3.14.3 8-bit basic timer

The 8-bit timer consists of an 8-bit up auto-reload counter driven by a programmable prescaler. It can be used for timebase generation with interrupt generation on timer overflow or for DAC trigger generation.

## 3.15 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

### 3.15.1 Window watchdog timer

The window watchdog (WWDG) is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

### 3.15.2 Independent watchdog timer

The independent watchdog peripheral (IWDG) can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the internal LSI RC clock source, and thus stays active even in case of a CPU clock failure.

## 3.16 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

| n               | Pin<br>umb      | er       |         |                                                                                              |      |           |          | Input                   | t              | 0                | utpu | ıt |                                                                                      |                                                                                                                     |  |

|-----------------|-----------------|----------|---------|----------------------------------------------------------------------------------------------|------|-----------|----------|-------------------------|----------------|------------------|------|----|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

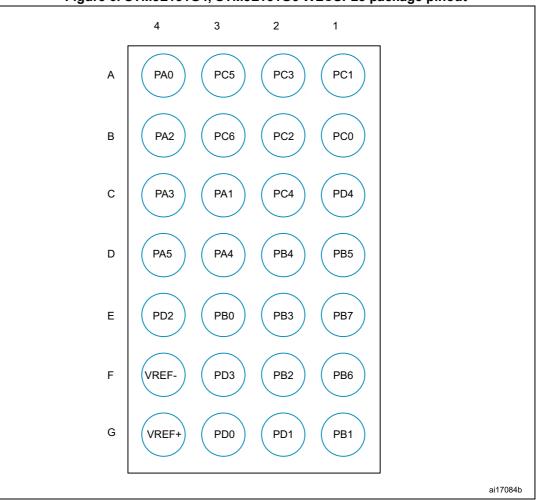

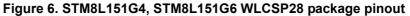

| LQFP48/UFQFPN48 | LQFP32/UFQFPN32 | UFQFPN28 | WLCSP28 | Pin name                                                                                     | Type | I/O level | floating | wpu                     | Ext. interrupt | High sink/source | OD   | ЬР | Main function<br>(after reset)                                                       | Default alternate<br>function                                                                                       |  |

| -               | 8               | 7        | G4      | V <sub>DD1</sub> /V <sub>DDA</sub> /V <sub>REF+</sub>                                        | s    | -         | -        | -                       | -              | -                | -    | -  | Digital power supply / Analog<br>supply voltage / ADC1 positive<br>voltage reference |                                                                                                                     |  |

| 9               | 7               | 6        | F4      | V <sub>SS1</sub> /V <sub>SSA/</sub> V <sub>REF-</sub>                                        | s    | -         | -        | -                       | -              | -                | -    | -  | I/O ground / Analog ground voltage<br>/<br>ADC1 negative voltage reference           |                                                                                                                     |  |

| 39              | -               | -        | -       | V <sub>DD2</sub>                                                                             | S    | -         | -        | -                       | -              | -                | -    | -  | IOs suppl                                                                            | y voltage                                                                                                           |  |

| 40              | -               | -        | -       | V <sub>SS2</sub>                                                                             | S    | -         | -        | -                       | -              | -                | -    | -  | IOs ground voltage                                                                   |                                                                                                                     |  |

| 1               | 32              | 28       | A4      | PA0 <sup>(9)</sup> / <i>[USART1_CK]</i> <sup>(4)</sup> /<br>SWIM/BEEP/IR_TIM <sup>(10)</sup> | I/O  |           | х        | <b>X</b> <sup>(9)</sup> | х              | HS<br>(10)       | х    | х  | Port A0                                                                              | [USART1 synchronous<br>clock] <sup>(4)</sup> / SWIM input<br>and output /<br>Beep output / Infrared<br>Timer output |  |

#### Table 5. Medium-density STM8L151x4/6, STM8L152x4/6 pin description (continued)

At power-up, the PA1/NRST pin is a reset input pin with pull-up. To be used as a general purpose pin (PA1), it can be configured only as output open-drain or push-pull, not as a general purpose input. Refer to Section Configuring NRST/PA1 pin as general purpose output in the STM8L15x and STM8L16x reference manual (RM0031).

2. Available on STM8L152xx devices only.

3. In the 3.6 V tolerant I/Os, protection diode to  $V_{\text{DD}}$  is not implemented.

4. [] Alternate function remapping option (if the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

- 5. In the 5 V tolerant I/Os, protection diode to  $V_{\text{DD}}$  is not implemented.

- 6. A pull-up is applied to PB0 and PB4 during the reset phase. These two pins are input floating after reset release.

- In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up and protection diode to V<sub>DD</sub> are not implemented).

- 8. Available on STM8L151xx devices only.

- 9. The PA0 pin is in input pull-up during the reset phase and after reset release.

10. High Sink LED driver capability available on PA0.

*Note:* The slope control of all GPIO pins, except true open drain pins, can be programmed. By default, the slope control is limited to 2 MHz.

|                           |        | Table 9. General hardware register map (continued) |                                                         |                 |  |  |  |  |  |  |

|---------------------------|--------|----------------------------------------------------|---------------------------------------------------------|-----------------|--|--|--|--|--|--|

| Address                   | Block  | Register label                                     | Register name                                           | Reset<br>status |  |  |  |  |  |  |

| 0x00 5084                 |        |                                                    | Reserved area (1 byte)                                  |                 |  |  |  |  |  |  |

| 0x00 5085                 |        | DMA1_C1M0ARH                                       | DMA1 memory 0 address high register<br>(channel 1)      | 0x00            |  |  |  |  |  |  |

| 0x00 5086                 |        | DMA1_C1M0ARL                                       | DMA1 memory 0 address low register<br>(channel 1)       | 0x00            |  |  |  |  |  |  |

| 0x00 5087<br>0x00 5088    |        |                                                    | Reserved area (2 bytes)                                 |                 |  |  |  |  |  |  |

| 0x00 5089                 |        | DMA1_C2CR                                          | DMA1 channel 2 configuration register                   | 0x00            |  |  |  |  |  |  |

| 0x00 508A                 |        | DMA1_C2SPR                                         | DMA1 channel 2 status & priority register               | 0x00            |  |  |  |  |  |  |

| 0x00 508B                 |        | DMA1_C2NDTR                                        | DMA1 number of data to transfer register<br>(channel 2) | 0x00            |  |  |  |  |  |  |

| 0x00 508C                 |        | DMA1_C2PARH                                        | DMA1 peripheral address high register<br>(channel 2)    | 0x52            |  |  |  |  |  |  |

| 0x00 508D                 |        | DMA1_C2PARL                                        | DMA1 peripheral address low register<br>(channel 2)     | 0x00            |  |  |  |  |  |  |

| 0x00 508E                 |        |                                                    | Reserved area (1 byte)                                  |                 |  |  |  |  |  |  |

| 0x00 508F                 |        | DMA1_C2M0ARH                                       | DMA1 memory 0 address high register<br>(channel 2)      | 0x00            |  |  |  |  |  |  |

| 0x00 5090                 | DMA1   | DMA1_C2M0ARL                                       | DMA1 memory 0 address low register<br>(channel 2)       | 0x00            |  |  |  |  |  |  |

| 0x00 5091<br>0x00 5092    |        |                                                    | Reserved area (2 bytes)                                 |                 |  |  |  |  |  |  |

| 0x00 5093                 |        | DMA1_C3CR                                          | DMA1 channel 3 configuration register                   | 0x00            |  |  |  |  |  |  |

| 0x00 5094                 |        | DMA1_C3SPR                                         | DMA1 channel 3 status & priority register               | 0x00            |  |  |  |  |  |  |

| 0x00 5095                 |        | DMA1_C3NDTR                                        | DMA1 number of data to transfer register<br>(channel 3) | 0x00            |  |  |  |  |  |  |

| 0x00 5096                 |        | DMA1_C3PARH_<br>C3M1ARH                            | DMA1 peripheral address high register<br>(channel 3)    | 0x40            |  |  |  |  |  |  |

| 0x00 5097                 |        | DMA1_C3PARL_<br>C3M1ARL                            | DMA1 peripheral address low register<br>(channel 3)     | 0x00            |  |  |  |  |  |  |

| 0x00 5098                 |        |                                                    | Reserved area (1 byte)                                  |                 |  |  |  |  |  |  |

| 0x00 5099                 |        | DMA1_C3M0ARH                                       | DMA1 memory 0 address high register<br>(channel 3)      | 0x00            |  |  |  |  |  |  |

| 0x00 509A                 |        | DMA1_C3M0ARL                                       | DMA1 memory 0 address low register<br>(channel 3)       | 0x00            |  |  |  |  |  |  |

| 0x00 509B to<br>0x00 509D |        |                                                    | Reserved area (3 bytes)                                 |                 |  |  |  |  |  |  |

| 0x00 509E                 | evecto | SYSCFG_RMPCR1                                      | Remapping register 1                                    | 0x00            |  |  |  |  |  |  |

| 0x00 509F                 | SYSCFG | SYSCFG RMPCR2                                      | Remapping register 2                                    | 0x00            |  |  |  |  |  |  |

Table 9. General hardware register map (continued)

| Address                      | Block  | Register label           | Register name                       | Reset  |  |  |

|------------------------------|--------|--------------------------|-------------------------------------|--------|--|--|

| Audress                      | BIOCK  | Register laber           |                                     | status |  |  |

| 0x00 5200                    |        | SPI1_CR1                 | SPI1 control register 1             | 0x00   |  |  |

| 0x00 5201                    | ]      | SPI1_CR2                 | SPI1 control register 2             | 0x00   |  |  |

| 0x00 5202                    | ]      | SPI1_ICR                 | SPI1 interrupt control register     | 0x00   |  |  |

| 0x00 5203                    | SPI1   | SPI1_SR                  | SPI1 status register                | 0x02   |  |  |

| 0x00 5204                    | - 3511 | SPI1_DR                  | SPI1 data register                  | 0x00   |  |  |

| 0x00 5205                    |        | SPI1_CRCPR               | SPI1 CRC polynomial register        | 0x07   |  |  |

| 0x00 5206                    |        | SPI1_RXCRCR              | SPI1 Rx CRC register                | 0x00   |  |  |

| 0x00 5207                    |        | SPI1_TXCRCR              | SPI1 Tx CRC register                | 0x00   |  |  |

| 0x00 5208<br>to<br>0x00 520F |        | I                        | Reserved area (8 bytes)             |        |  |  |

| 0x00 5210                    |        | I2C1_CR1                 | I2C1 control register 1             | 0x00   |  |  |

| 0x00 5211                    |        | I2C1_CR2                 | I2C1 control register 2             | 0x00   |  |  |

| 0x00 5212                    |        | I2C1_FREQR               | I2C1 frequency register             | 0x00   |  |  |

| 0x00 5213                    |        | I2C1_OARL                | I2C1 own address register low       | 0x00   |  |  |

| 0x00 5214                    |        | I2C1_OARH                | I2C1 own address register high      | 0x00   |  |  |

| 0x00 5215                    |        |                          | Reserved (1 byte)                   |        |  |  |

| 0x00 5216                    |        | I2C1_DR                  | I2C1 data register                  | 0x00   |  |  |

| 0x00 5217                    | I2C1   | I2C1_SR1                 | I2C1 status register 1              | 0x00   |  |  |

| 0x00 5218                    |        | I2C1_SR2                 | I2C1 status register 2              | 0x00   |  |  |

| 0x00 5219                    |        | I2C1_SR3                 | I2C1 status register 3              | 0x0x   |  |  |

| 0x00 521A                    |        | I2C1_ITR                 | I2C1 interrupt control register     | 0x00   |  |  |

| 0x00 521B                    | ]      | I2C1_CCRL                | I2C1 clock control register low     | 0x00   |  |  |

| 0x00 521C                    | ]      | I2C1_CCRH                | I2C1 clock control register high    | 0x00   |  |  |

| 0x00 521D                    | 1      | I2C1_TRISER              | I2C1 TRISE register                 | 0x02   |  |  |

| 0x00 521E                    | 1      | I2C1_PECR                | I2C1 packet error checking register | 0x00   |  |  |

| 0x00 521F<br>to<br>0x00 522F |        | Reserved area (17 bytes) |                                     |        |  |  |

|                  | h                   |                |

|------------------|---------------------|----------------|

| Table 9. General | hardware register m | ap (continued) |

| Address                      | Block  | Register label | Register name               | Reset<br>status |  |  |  |  |

|------------------------------|--------|----------------|-----------------------------|-----------------|--|--|--|--|

| 0x00 5230                    |        | USART1_SR      | USART1 status register      | 0xC0            |  |  |  |  |

| 0x00 5231                    |        | USART1_DR      | USART1 data register        | undefined       |  |  |  |  |

| 0x00 5232                    |        | USART1_BRR1    | USART1 baud rate register 1 | 0x00            |  |  |  |  |

| 0x00 5233                    |        | USART1_BRR2    | USART1 baud rate register 2 | 0x00            |  |  |  |  |

| 0x00 5234                    |        | USART1_CR1     | USART1 control register 1   | 0x00            |  |  |  |  |

| 0x00 5235                    | USART1 | USART1_CR2     | USART1 control register 2   | 0x00            |  |  |  |  |

| 0x00 5236                    |        | USART1_CR3     | USART1 control register 3   | 0x00            |  |  |  |  |

| 0x00 5237                    |        | USART1_CR4     | USART1 control register 4   | 0x00            |  |  |  |  |

| 0x00 5238                    |        | USART1_CR5     | USART1 control register 5   | 0x00            |  |  |  |  |

| 0x00 5239                    |        | USART1_GTR     | USART1 guard time register  | 0x00            |  |  |  |  |

| 0x00 523A                    |        | USART1_PSCR    | USART1 prescaler register   | 0x00            |  |  |  |  |

| 0x00 523B<br>to<br>0x00 524F |        | Я              | Reserved area (21 bytes)    |                 |  |  |  |  |

|         | -        |                 |          |     |             |  |

|---------|----------|-----------------|----------|-----|-------------|--|

| Table 9 | General  | hardware        | register | man | (continued) |  |

|         | Contorui | indi di titul c | register | map | (continued) |  |

| Address                      | Block | Register Label | Register Name                             | Reset<br>Status |  |  |  |  |  |

|------------------------------|-------|----------------|-------------------------------------------|-----------------|--|--|--|--|--|

| 0x00 7F90                    |       | DM_BK1RE       | DM breakpoint 1 register extended byte    | 0xFF            |  |  |  |  |  |

| 0x00 7F91                    |       | DM_BK1RH       | DM breakpoint 1 register high byte        | 0xFF            |  |  |  |  |  |

| 0x00 7F92                    |       | DM_BK1RL       | DM breakpoint 1 register low byte         | 0xFF            |  |  |  |  |  |

| 0x00 7F93                    |       | DM_BK2RE       | DM breakpoint 2 register extended byte    | 0xFF            |  |  |  |  |  |

| 0x00 7F94                    |       | DM_BK2RH       | DM breakpoint 2 register high byte        | 0xFF            |  |  |  |  |  |

| 0x00 7F95                    | DM    | DM_BK2RL       | DM breakpoint 2 register low byte         | 0xFF            |  |  |  |  |  |

| 0x00 7F96                    |       | DM_CR1         | DM Debug module control register 1        | 0x00            |  |  |  |  |  |

| 0x00 7F97                    |       | DM_CR2         | DM Debug module control register 2        | 0x00            |  |  |  |  |  |

| 0x00 7F98                    |       | DM_CSR1        | DM Debug module control/status register 1 | 0x10            |  |  |  |  |  |

| 0x00 7F99                    |       | DM_CSR2        | DM Debug module control/status register 2 | 0x00            |  |  |  |  |  |

| 0x00 7F9A                    |       | DM_ENFCTR      | DM enable function register               | 0xFF            |  |  |  |  |  |

| 0x00 7F9B<br>to<br>0x00 7F9F |       |                | Reserved area (5 byte)                    |                 |  |  |  |  |  |

#### Table 10. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

| •                    | Para                          |                                        | (                                                    | 4)                                  | -     |                      |                      | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |       |

|----------------------|-------------------------------|----------------------------------------|------------------------------------------------------|-------------------------------------|-------|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|

| Symbol               | meter                         |                                        | Conditions <sup>(</sup>                              | ')                                  | Тур   | 55 °C                | 85 °C <sup>(2)</sup> | 105°C <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                         | 125 °C <sup>(4)</sup> | Unit  |

|                      |                               |                                        |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.39  | 0.47                 | 0.49                 | 0.52                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.55                  |       |

|                      |                               |                                        | f <sub>CPU</sub> = 1 MHz                             | 0.48                                | 0.56  | 0.58                 | 0.61                 | 0.65                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |       |

|                      |                               | HSI RC osc.<br>(16 MHz) <sup>(6)</sup> | f <sub>CPU</sub> = 4 MHz                             | 0.75                                | 0.84  | 0.86                 | 0.91                 | 0.99                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |       |

|                      |                               |                                        |                                                      | f <sub>CPU</sub> = 8 MHz            | 1.10  | 1.20                 | 1.25                 | 1.31                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.40                  |       |

|                      | All<br>peripherals            |                                        | f <sub>CPU</sub> = 16 MHz                            | 1.85                                | 1.93  | 2.12 <sup>(8)</sup>  | 2.29 <sup>(8)</sup>  | 2.36 <sup>(8)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |       |

|                      | Supply                        | OFF,                                   |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.05  | 0.06                 | 0.09                 | 0.11                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.12                  |       |

| I <sub>DD(RUN)</sub> | current                       | code<br>executed                       | HSE external                                         | f <sub>CPU</sub> = 1 MHz            | 0.18  | 0.19                 | 0.20                 | 0.22                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.23                  | mA    |

| <i>DD</i> (RON)      | in run<br>mode <sup>(5)</sup> | from RAM,<br>V <sub>DD</sub> from      | clock                                                | f <sub>CPU</sub> = 4 MHz            | 0.55  | 0.62                 | 0.64                 | 0.71                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.77                  |       |

|                      |                               | 1.65 V to                              | (f <sub>CPU</sub> =f <sub>HSE</sub> ) <sup>(7)</sup> | f <sub>CPU</sub> = 8 MHz            | 0.99  | 1.20                 | 1.21                 | 1.22                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.24                  |       |

|                      |                               | 3.6 V                                  |                                                      | f <sub>CPU</sub> = 16 MHz           | 1.90  | 2.22                 | 2.23 <sup>(8)</sup>  | 2.24 <sup>(8)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.28 <sup>(8)</sup>   |       |

|                      |                               |                                        | LSI RC osc.<br>(typ. 38 kHz)                         | f <sub>CPU</sub> = f <sub>LSI</sub> | 0.040 | 0.045                | 0.046                | 0.048                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.050                 |       |

|                      | LSE ex<br>clock               | LSE external<br>clock<br>(32.768 kHz)  | f <sub>CPU</sub> = f <sub>LSE</sub>                  | 0.035                               | 0.040 | 0.048 <sup>(8)</sup> | 0.050                | 0.062                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |       |

|                      |                               |                                        |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.43  | 0.55                 | 0.56                 | 0.58                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.62                  |       |

|                      |                               |                                        |                                                      | f <sub>CPU</sub> = 1 MHz            | 0.60  | 0.77                 | 0.80                 | 0.82                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.87                  |       |

|                      |                               |                                        | HSI RC<br>osc. <sup>(9)</sup>                        | f <sub>CPU</sub> = 4 MHz            | 1.11  | 1.34                 | 1.37                 | 1.39                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.43                  |       |

|                      |                               |                                        |                                                      | f <sub>CPU</sub> = 8 MHz            | 1.90  | 2.20                 | 2.23                 | 2.31                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.40                  |       |

|                      |                               | All                                    |                                                      | f <sub>CPU</sub> = 16 MHz           | 3.8   | 4.60                 | 4.75                 | $86$ $0.91$ $0.99$ $25$ $1.31$ $1.40$ $2^{(8)}$ $2.29^{(8)}$ $2.36^{(8)}$ $29$ $0.11$ $0.12$ $20$ $0.22$ $0.23$ $64$ $0.71$ $0.77$ $21$ $1.22$ $1.24$ $3^{(8)}$ $2.24^{(8)}$ $2.28^{(8)}$ $46$ $0.048$ $0.050$ $48^{(8)}$ $0.050$ $0.062$ $56$ $0.58$ $0.62$ $80$ $0.82$ $0.87$ $37$ $1.39$ $1.43$ $23$ $2.31$ $2.40$ $75$ $4.87$ $4.88$ $39$ $0.44$ $0.47$ $52$ $0.55$ $0.56$ $40$ $1.45$ $1.48$ $44$ $2.56$ $2.77$ $52$ $4.59$ $4.77$ $30$ $0.140$ $0.150$ |                       |       |

|                      | Supply                        | peripherals<br>OFF, code               |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.30  | 0.36                 | 0.39                 | 0.44                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.47                  |       |

| I <sub>DD(RUN)</sub> | Supply current                | executed                               | HSE external                                         | f <sub>CPU</sub> = 1 MHz            | 0.40  | 0.50                 | 0.52                 | 0.55                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.56                  | mA    |

| 'DD(RUN)             | in Run<br>mode                | from Flash,<br>V <sub>DD</sub> from    | clock<br>(f <sub>CPU</sub> =f <sub>HSE</sub> )       | f <sub>CPU</sub> = 4 MHz            | 1.15  | 1.31                 | 1.40                 | 1.45                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.48                  | 110 \ |

|                      |                               | 1.65 V to                              | (7)                                                  | f <sub>CPU</sub> = 8 MHz            | 2.17  | 2.33                 | 2.44                 | 2.56                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.77                  |       |

|                      |                               | 3.6 V                                  |                                                      | f <sub>CPU</sub> = 16 MHz           | 4.0   | 4.46                 | 4.52                 | 4.59                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.77                  |       |

|                      |                               |                                        | LSI RC osc.                                          | f <sub>CPU</sub> = f <sub>LSI</sub> | 0.110 | 0.123                | 0.130                | 0.140                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.150                 |       |

|                      |                               |                                        | LSE ext.<br>clock<br>(32.768<br>kHz) <sup>(10)</sup> | f <sub>CPU</sub> = f <sub>LSE</sub> | 0.100 | 0.101                | 0.104                | 0.119                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.122                 |       |

1. All peripherals OFF,  $V_{DD}$  from 1.65 V to 3.6 V, HSI internal RC osc.,  $f_{CPU}\text{=}f_{SYSCLK}$

2. For devices with suffix 6

3. For devices with suffix 7

4. For devices with suffix 3

| -                    |                        | ,                                               |                         |      |    |

|----------------------|------------------------|-------------------------------------------------|-------------------------|------|----|

| Symbol               | Parameter              | Condition                                       | Тур                     | Unit |    |

|                      | Oursels summaries days |                                                 | V <sub>DD</sub> = 1.8 V | 48   |    |

| I <sub>DD(RST)</sub> |                        | All pins are externally tied to V <sub>DD</sub> | V <sub>DD</sub> = 3 V   | 76   | μΑ |

|                      |                        |                                                 | V <sub>DD</sub> = 3.6 V | 91   |    |

Table 28. Current consumption under external reset

1. All pins except PA0, PB0 and PB4 are floating under reset. PA0, PB0 and PB4 are configured with pull-up under reset.

## 9.3.4 Clock and timing characteristics

## HSE external clock (HSEBYP = 1 in CLK\_ECKCR)

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol                | Parameter                                      | Conditions                 | Min                   | Тур | Мах                   | Unit |

|-----------------------|------------------------------------------------|----------------------------|-----------------------|-----|-----------------------|------|

| f <sub>HSE_ext</sub>  | External clock source frequency <sup>(1)</sup> |                            | 1                     | -   | 16                    | MHz  |

| V <sub>HSEH</sub>     | OSC_IN input pin high level voltage            | -                          | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub>       | V    |

| V <sub>HSEL</sub>     | OSC_IN input pin low level voltage             |                            | V <sub>SS</sub>       | -   | 0.3 x V <sub>DD</sub> | v    |

| C <sub>in(HSE)</sub>  | OSC_IN input<br>capacitance <sup>(1)</sup>     | -                          | -                     | 2.6 | -                     | pF   |

| I <sub>LEAK_HSE</sub> | OSC_IN input leakage<br>current                | $V_{SS} < V_{IN} < V_{DD}$ | -                     | -   | ±1                    | μA   |

Table 29. HSE external clock characteristics

1. Data guaranteed by design.

## LSE external clock (LSEBYP=1 in CLK\_ECKCR)

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

| Table 30. LSE external clock characteristics | Table | 30. | LSE | external | clock | characteristics |

|----------------------------------------------|-------|-----|-----|----------|-------|-----------------|

|----------------------------------------------|-------|-----|-----|----------|-------|-----------------|

| Symbol                           | Parameter                                      | Min                   | Тур    | Мах                   | Unit |

|----------------------------------|------------------------------------------------|-----------------------|--------|-----------------------|------|

| f <sub>LSE_ext</sub>             | External clock source frequency <sup>(1)</sup> | -                     | 32.768 | -                     | kHz  |

| V <sub>LSEH</sub> <sup>(2)</sup> | OSC32_IN input pin high level voltage          | 0.7 x V <sub>DD</sub> | -      | V <sub>DD</sub>       | V    |

| V <sub>LSEL</sub> <sup>(2)</sup> | OSC32_IN input pin low level voltage           | V <sub>SS</sub>       | -      | 0.3 x V <sub>DD</sub> | v    |

| C <sub>in(LSE)</sub>             | OSC32_IN input capacitance <sup>(1)</sup>      | -                     | 0.6    | -                     | pF   |

| I <sub>LEAK_LSE</sub>            | OSC32_IN input leakage current                 | -                     | -      | ±1                    | μA   |

1. Data guaranteed by design.

2. Data based on characterization results.

#### **Output driving current**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified.

| l/O<br>Type | Symbol | Parameter Conditions                                                                                          |                                                      | Min                   | Max  | Unit |

|-------------|--------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------|------|------|

|             |        | <ul> <li>Output low level voltage for an I/O pin</li> <li>Output high level voltage for an I/O pin</li> </ul> | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 3.0 V  | -                     | 0.45 | V    |

| High sink   |        |                                                                                                               | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 1.8 V  | -                     | 0.45 | V    |

|             |        |                                                                                                               | I <sub>IO</sub> = +10 mA,<br>V <sub>DD</sub> = 3.0 V | -                     | 0.7  | V    |

|             |        |                                                                                                               | I <sub>IO</sub> = -2 mA,<br>V <sub>DD</sub> = 3.0 V  | V <sub>DD</sub> -0.45 | -    | V    |

|             |        |                                                                                                               | I <sub>IO</sub> = -1 mA,<br>V <sub>DD</sub> = 1.8 V  | V <sub>DD</sub> -0.45 | -    | V    |

|             |        |                                                                                                               | I <sub>IO</sub> = -10 mA,<br>V <sub>DD</sub> = 3.0 V | V <sub>DD</sub> -0.7  | -    | V    |

| Table 39. Output driving current (high sink por | 'ts) |

|-------------------------------------------------|------|

|-------------------------------------------------|------|

The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

| l/O<br>Type                      | Symbol                                                                | Parameter                                           | Conditions                                          | Min  | Max  | Unit |

|----------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|------|------|------|

| drain                            | $V_{\Omega I}$ <sup>(1)</sup> Output low level voltage for an I/O pin | I <sub>IO</sub> = +3 mA,<br>V <sub>DD</sub> = 3.0 V | -                                                   | 0.45 | V    |      |

| O V <sub>OL</sub> <sup>(1)</sup> | VOL                                                                   |                                                     | I <sub>IO</sub> = +1 mA,<br>V <sub>DD</sub> = 1.8 V | -    | 0.45 | V    |

#### Table 40. Output driving current (true open drain ports)

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

| I/О<br>Туре | Symbol                         | Parameter                               | Conditions                                           | Min | Max  | Unit |

|-------------|--------------------------------|-----------------------------------------|------------------------------------------------------|-----|------|------|

| R           | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin | I <sub>IO</sub> = +20 mA,<br>V <sub>DD</sub> = 2.0 V | -   | 0.45 | V    |

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

## 9.3.8 Communication interfaces

### SPI1 - Serial peripheral interface

Unless otherwise specified, the parameters given in *Table 43* are derived from tests performed under ambient temperature, f<sub>SYSCLK</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in *Section 9.3.1*. Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                     | Conditions <sup>(1)</sup>                                             | Min                       | Мах                      | Unit |

|----------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------|---------------------------|--------------------------|------|

| f <sub>SCK</sub>                                                           | SPI1 clock frequency          | Master mode                                                           | 0                         | 8                        |      |

| 1/t <sub>c(SCK)</sub>                                                      | SPTT Clock frequency          | Slave mode                                                            | 0                         | 8                        | MHz  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                                 | SPI1 clock rise and fall time | Capacitive load: C = 30 pF                                            | -                         | 30                       |      |

| t <sub>su(NSS)</sub> <sup>(2)</sup>                                        | NSS setup time                | Slave mode                                                            | 4 x 1/f <sub>SYSCLK</sub> | -                        |      |

| t <sub>h(NSS)</sub> <sup>(2)</sup>                                         | NSS hold time                 | Slave mode                                                            | 80                        | -                        |      |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time         | Master mode,<br>f <sub>MASTER</sub> = 8 MHz, f <sub>SCK</sub> = 4 MHz | 105                       | 145                      | -    |

| t <sub>su(MI)</sub> (2)                                                    | Data input setup time         | Master mode                                                           | 30                        | -                        |      |

| t <sub>su(MI)</sub> (2)<br>t <sub>su(SI)</sub> (2)                         |                               | Slave mode                                                            | 3                         | -                        |      |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Data input hold time          | Master mode                                                           | 15                        | -                        |      |

| t <sub>h(MI)</sub> (2)<br>t <sub>h(SI)</sub> (2)                           | Data input hold time          | Slave mode                                                            | 0                         | -                        | ns   |

| t <sub>a(SO)</sub> <sup>(2)(3)</sup>                                       | Data output access time       | Slave mode                                                            | -                         | 3x 1/f <sub>SYSCLK</sub> |      |

| $t_{dis(SO)}^{(2)(4)}$                                                     | Data output disable time      | Slave mode                                                            | 30                        | -                        |      |

| t <sub>v(SO)</sub> <sup>(2)</sup>                                          | Data output valid time        | Slave mode (after enable edge)                                        | -                         | 60                       |      |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time        | Master mode (after enable edge)                                       | -                         | 20                       |      |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          |                               | Slave mode (after enable edge)                                        | 15                        | -                        | 1    |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | Data output hold time         | Master mode (after enable edge)                                       | 1                         | -                        |      |

1. Parameters are given by selecting 10 MHz I/O output frequency.

2. Values based on design simulation and/or characterization results.

3. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

4. Min time is for the minimum time to invalidate the output and max time is for the maximum time to put the data in Hi-Z.

# 9.3.9 LCD controller (STM8L152xx only)

In the following table, data is guaranteed by design. Not tested in production.

| Symbol                         | Parameter                                         | Min | Тур                  | Max.              | Unit |

|--------------------------------|---------------------------------------------------|-----|----------------------|-------------------|------|

| $V_{LCD}$                      | LCD external voltage                              | -   | -                    | 3.6               | V    |

| V <sub>LCD0</sub>              | LCD internal reference voltage 0                  | -   | 2.6                  | -                 | V    |

| V <sub>LCD1</sub>              | LCD internal reference voltage 1                  | -   | 2.7                  | -                 | V    |

| V <sub>LCD2</sub>              | LCD internal reference voltage 2                  | -   | 2.8                  | -                 | V    |

| V <sub>LCD3</sub>              | LCD internal reference voltage 3                  | -   | 2.9                  | -                 | V    |

| V <sub>LCD4</sub>              | LCD internal reference voltage 4                  | -   | 3.0                  | -                 | V    |

| $V_{LCD5}$                     | LCD internal reference voltage 5                  | -   | 3.1                  | -                 | V    |

| V <sub>LCD6</sub>              | LCD internal reference voltage 6                  | -   | 3.2                  | -                 | V    |

| V <sub>LCD7</sub>              | LCD internal reference voltage 7                  | -   | 3.3                  | -                 | V    |

| C <sub>EXT</sub>               | V <sub>LCD</sub> external capacitance             | 0.1 | -                    | 2                 | μF   |

| I                              | Supply current <sup>(1)</sup> at $V_{DD}$ = 1.8 V | -   | 3                    | -                 | μA   |

| I <sub>DD</sub>                | Supply current <sup>(1)</sup> at $V_{DD}$ = 3 V   | -   | 3                    | -                 | μA   |

| R <sub>HN</sub> <sup>(2)</sup> | High value resistive network (low drive)          | -   | 6.6                  | -                 | MΩ   |

| $R_{LN}^{(3)}$                 | Low value resistive network (high drive)          | -   | 360                  | -                 | kΩ   |

| V <sub>33</sub>                | Segment/Common higher level voltage               | -   | -                    | V <sub>LCDx</sub> | V    |

| V <sub>23</sub>                | Segment/Common 2/3 level voltage                  | -   | 2/3V <sub>LCDx</sub> | -                 | V    |

| V <sub>12</sub>                | Segment/Common 1/2 level voltage                  | -   | 1/2V <sub>LCDx</sub> | -                 | V    |

| V <sub>13</sub>                | Segment/Common 1/3 level voltage                  | -   | 1/3V <sub>LCDx</sub> | -                 | V    |

| V <sub>0</sub>                 | Segment/Common lowest level voltage               | 0   | -                    | -                 | V    |

1. LCD enabled with 3 V internal booster (LCD\_CR1 = 0x08), 1/4 duty, 1/3 bias, division ratio= 64, all pixels active, no LCD connected.

2.  $\ R_{HN}$  is the total high value resistive network.

3. R<sub>LN</sub> is the total low value resistive network.

## VLCD external capacitor (STM8L152xx only)

The application can achieve a stabilized LCD reference voltage by connecting an external capacitor  $C_{EXT}$  to the  $V_{LCD}$  pin.  $C_{EXT}$  is specified in *Table 45*.

## 9.3.11 Temperature sensor

In the following table, data is based on characterization results, not tested in production, unless otherwise specified.

| Symbol                               | Parameter                                             | Min   | Тур   | Max.  | Unit  |

|--------------------------------------|-------------------------------------------------------|-------|-------|-------|-------|

| V <sub>90</sub> <sup>(1)</sup>       | Sensor reference voltage at 90°C ±5 °C,               | 0.580 | 0.597 | 0.614 | V     |

| TL                                   | V <sub>SENSOR</sub> linearity with temperature        | -     | ±1    | ±2    | °C    |

| Avg_slope (2)                        | Average slope                                         | 1.59  | 1.62  | 1.65  | mV/°C |

| I <sub>DD(TEMP)</sub> <sup>(2)</sup> | Consumption                                           | -     | 3.4   | 6     | μA    |

| T <sub>START</sub> <sup>(2)(3)</sup> | Temperature sensor startup time                       | -     | -     | 10    | μs    |

| T <sub>S_TEMP</sub> <sup>(2)</sup>   | ADC sampling time when reading the temperature sensor | 10    | -     | -     | μs    |

| Table 47.  | тs | characteristics |

|------------|----|-----------------|

| 10.010 111 |    |                 |

Tested in production at V<sub>DD</sub> = 3 V ±10 mV. The 8 LSB of the V<sub>90</sub> ADC conversion result are stored in the TS\_Factory\_CONV\_V90 byte.

- 2. Data guaranteed by design.

- 3. Defined for ADC output reaching its final value  $\pm 1/2LSB$ .

## 9.3.12 Comparator characteristics

In the following table, data is guaranteed by design, not tested in production, unless otherwise specified.

| Symbol              | Parameter                                                     | Min  | Тур   | Max <sup>(1)</sup> | Unit |  |

|---------------------|---------------------------------------------------------------|------|-------|--------------------|------|--|

| V <sub>DDA</sub>    | Analog supply voltage                                         | 1.65 | -     | 3.6                | V    |  |

| T <sub>A</sub>      | Temperature range                                             | -40  | -     | 125                | °C   |  |

| R <sub>400K</sub>   | R <sub>400K</sub> value                                       | 300  | 400   | 500                | kΩ   |  |

| R <sub>10K</sub>    | R <sub>10K</sub> value                                        | 7.5  | 10    | 12.5               | N22  |  |

| V <sub>IN</sub>     | Comparator 1 input voltage range                              | 0.6  | -     | V <sub>DDA</sub>   | V    |  |

| V <sub>REFINT</sub> | V <sub>REFINT</sub> Internal reference voltage <sup>(2)</sup> |      | 1.224 | 1.242              | v    |  |

| t <sub>START</sub>  | Comparator startup time                                       | -    | 7     | 10                 | 110  |  |

| t <sub>d</sub>      | t <sub>d</sub> Propagation delay <sup>(3)</sup>               |      | 3     | 10                 | μs   |  |

| V <sub>offset</sub> | Comparator offset error                                       | -    | ±3    | ±10                | mV   |  |

| I <sub>COMP1</sub>  | Current consumption <sup>(4)</sup>                            | -    | 160   | 260                | nA   |  |

#### Table 48. Comparator 1 characteristics

1. Based on characterization.

2. Tested in production at V<sub>DD</sub> = 3 V ±10 mV.

- 3. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the noninverting input set to the reference.

- 4. Comparator consumption only. Internal reference voltage not included.

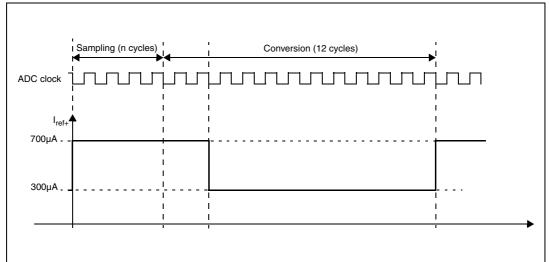

# Figure 40. Maximum dynamic current consumption on V<sub>REF+</sub> supply pin during ADC conversion

| Table 57. R <sub>AIN</sub> | max for f <sub>ADC</sub> = | = 16 MHz <sup>(1)</sup> |

|----------------------------|----------------------------|-------------------------|

|----------------------------|----------------------------|-------------------------|

|                |            | R <sub>AIN</sub> max (kohm)      |                                  |                                  |                                  |  |  |  |

|----------------|------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|--|--|--|

| Ts<br>(cycles) | Ts<br>(µs) | Slow cl                          | hannels                          | Fast channels                    |                                  |  |  |  |

|                | . ,        | 2.4 V < V <sub>DDA</sub> < 3.6 V | 1.8 V < V <sub>DDA</sub> < 2.4 V | 2.4 V < V <sub>DDA</sub> < 3.3 V | 1.8 V < V <sub>DDA</sub> < 2.4 V |  |  |  |

| 4              | 0.25       | Not allowed                      | Not allowed                      | 0.7                              | Not allowed                      |  |  |  |

| 9              | 0.5625     | 0.8                              | Not allowed                      | 2.0                              | 1.0                              |  |  |  |

| 16             | 1          | 2.0                              | 0.8                              | 4.0                              | 3.0                              |  |  |  |

| 24             | 1.5        | 3.0                              | 1.8                              | 6.0                              | 4.5                              |  |  |  |

| 48             | 3          | 6.8                              | 4.0                              | 15.0                             | 10.0                             |  |  |  |

| 96             | 6          | 15.0                             | 10.0                             | 30.0                             | 20.0                             |  |  |  |

| 192            | 12         | 32.0                             | 25.0                             | 50.0                             | 40.0                             |  |  |  |

| 384            | 24         | 50.0                             | 50.0                             | 50.0                             | 50.0                             |  |  |  |

1. Guaranteed by design.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 41* or *Figure 42*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. Good quality ceramic 10 nF capacitors should be used. They should be placed as close as possible to the chip.

## 9.3.15 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electromagnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                            | Conditions                                                                               |           | Level/<br>Class |

|-------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on<br>any I/O pin to induce a functional<br>disturbance | $V_{DD}$ = 3.3 V, $T_A$ = +25 °C,<br>f <sub>CPU</sub> = 16 MHz,<br>conforms to IEC 61000 |           | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on                  | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = +25 °C,<br>f <sub>CPU</sub> = 16 MHz,          | Using HSI | 4A              |

|                   | V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance          | conforms to IEC 61000                                                                    | Using HSE | 2B              |

Table 58. EMS data

### **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm IEC61967-2 which specifies the board and the loading of each pin.

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| E      | 8.800       | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| E1     | 6.800       | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -           | 5.500 | -     | -                     | 0.2165 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000 | -     | -                     | 0.0394 | -      |

| k      | 0°          | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| CCC    | -           | -     | 0.080 | -                     | -      | 0.0031 |

# Table 62. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat packagemechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

| 0h.al  | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Max    |  |

| А      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |

| D      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |  |

| E      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |  |

| D2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |

| Т      | -           | 0.152 | -     | -                     | 0.0060 | -      |  |

| b      | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

# Table 63. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

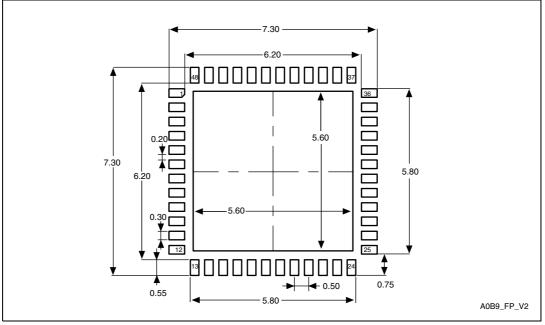

# Figure 47. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

|        |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |  |

| А      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217                | 0.0236 |  |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000 | 0.0008                | 0.0020 |  |

| A3     | -     | 0.152       | -     | -      | 0.0060                | -      |  |

| b      | 0.180 | 0.230       | 0.280 | 0.0071 | 0.0091                | 0.0110 |  |

| D      | 4.900 | 5.000       | 5.100 | 0.1929 | 0.1969                | 0.2008 |  |

| D1     | 3.400 | 3.500       | 3.600 | 0.1339 | 0.1378                | 0.1417 |  |

| D2     | 3.400 | 3.500       | 3.600 | 0.1339 | 0.1378                | 0.1417 |  |

| Е      | 4.900 | 5.000       | 5.100 | 0.1929 | 0.1969                | 0.2008 |  |

| E1     | 3.400 | 3.500       | 3.600 | 0.1339 | 0.1378                | 0.1417 |  |

| E2     | 3.400 | 3.500       | 3.600 | 0.1339 | 0.1378                | 0.1417 |  |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |  |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157                | 0.0197 |  |

| ddd    | -     | -           | 0.080 | -      | -                     | 0.0031 |  |

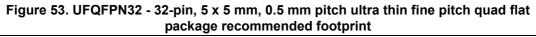

# Table 65. UFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

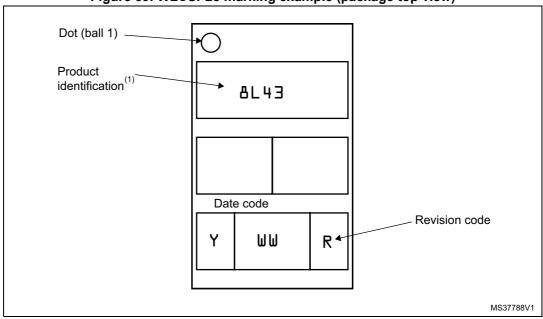

#### Figure 59. WLCSP28 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.