Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

|                                | ctive                                                                 |

|--------------------------------|-----------------------------------------------------------------------|

| Core Processor ST              |                                                                       |

| 51                             | TM8                                                                   |

| Core Size 8-E                  | Bit                                                                   |

| Speed 16                       | 6MHz                                                                  |

| Connectivity I <sup>2</sup> C  | C, IrDA, SPI, UART/USART                                              |

| Peripherals Bro                | rown-out Detect/Reset, DMA, IR, POR, PWM, WDT                         |

| Number of I/O 41               | 1                                                                     |

| Program Memory Size 32         | 2KB (32K x 8)                                                         |

| Program Memory Type FL         | LASH                                                                  |

| EEPROM Size 1K                 | K x 8                                                                 |

| RAM Size 2K                    | K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) 1.8 | 8V ~ 3.6V                                                             |

| Data Converters A/I            | /D 25x12b; D/A 1x12b                                                  |

| Oscillator Type Int            | ternal                                                                |

| Operating Temperature -40      | 10°C ~ 125°C (TA)                                                     |

| Mounting Type Su               | urface Mount                                                          |

| Package / Case 48              | 8-UFQFN Exposed Pad                                                   |

| Supplier Device Package 48     | 8-UFQFPN (7x7)                                                        |

| Purchase URL htt               | ttps://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151c6u3tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

IWDG: Independent watchdog LCD: Liquid crystal display POR/PDR: Power on reset / power down reset RTC: Real-time clock SPI: Serial peripheral interface SWIM: Single wire interface module USART: Universal synchronous asynchronous receiver transmitter WWDG: Window watchdog

# 3.1 Low-power modes

The medium-density STM8L151x4/6 and STM8L152x4/6 devices support five low power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

- Wait mode: The CPU clock is stopped, but selected peripherals keep running. An internal or external interrupt, event or a Reset can be used to exit the microcontroller from Wait mode (WFE or WFI mode). Wait consumption: refer to *Table 21*.

- Low power run mode: The CPU and the selected peripherals are running. Execution is done from RAM with a low speed oscillator (LSI or LSE). Flash and data EEPROM are stopped and the voltage regulator is configured in ultra-low-power mode. The microcontroller enters Low power run mode by software and can exit from this mode by software or by a reset.

All interrupts must be masked. They cannot be used to exit the microcontroller from this mode. Low power run mode consumption: refer to *Table 22*.

- Low power wait mode: This mode is entered when executing a Wait for event in Low power run mode. It is similar to Low power run mode except that the CPU clock is stopped. The wakeup from this mode is triggered by a Reset or by an internal or external event (peripheral event generated by the timers, serial interfaces, DMA controller (DMA1), comparators and I/O ports). When the wakeup is triggered by an event, the system goes back to Low power run mode. All interrupts must be masked. They cannot be used to exit the microcontroller from this mode. Low power wait mode consumption: refer to *Table 23*.

- Active-halt mode: CPU and peripheral clocks are stopped, except RTC. The wakeup can be triggered by RTC interrupts, external interrupts or reset. Active-halt consumption: refer to *Table 24* and *Table 25*.

- Halt mode: CPU and peripheral clocks are stopped, the device remains powered on. The RAM content is preserved. The wakeup is triggered by an external interrupt or reset. A few peripherals have also a wakeup from Halt capability. Switching off the internal reference voltage reduces power consumption. Through software configuration it is also possible to wake up the device without waiting for the internal reference voltage wakeup time to have a fast wakeup time of 5 µs. Halt consumption: refer to *Table 26*.

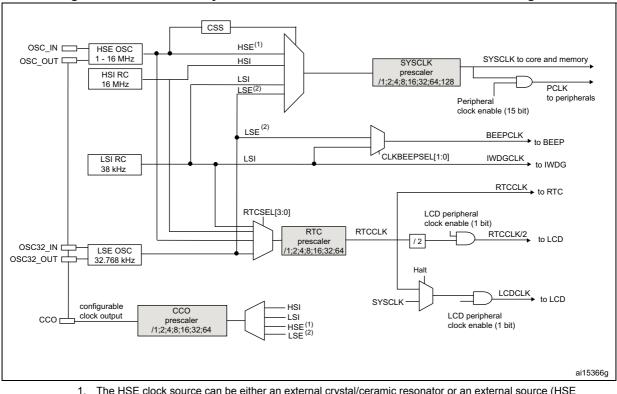

Figure 2. Medium-density STM8L151x4/6 and STM8L152x4/6 clock tree diagram

- The HSE clock source can be either an external crystal/ceramic resonator or an external source (HSE bypass). Refer to Section HSE clock in the STM8L15x and STM8L16x reference manual (RM0031).

- The LSE clock source can be either an external crystal/ceramic resonator or a external source (LSE bypass). Refer to Section LSE clock in the STM8L15x and STM8L16x reference manual (RM0031).

## 3.5 Low power real-time clock

The real-time clock (RTC) is an independent binary coded decimal (BCD) timer/counter.

Six byte locations contain the second, minute, hour (12/24 hour), week day, date, month, year, in BCD (binary coded decimal) format. Correction for 28, 29 (leap year), 30, and 31 day months are made automatically.

It provides a programmable alarm and programmable periodic interrupts with wakeup from Halt capability.

- Periodic wakeup time using the 32.768 kHz LSE with the lowest resolution (of 61 µs) is from min. 122 µs to max. 3.9 s. With a different resolution, the wakeup time can reach 36 hours

- Periodic alarms based on the calendar can also be generated from every second to every year

and STM8L152x4/6 devices, the acquisition sequence is managed by software and it involves analog I/O groups and the routing interface.

Reliable touch sensing solutions can be quickly and easily implemented using the free STM8 Touch Sensing Library.

# 3.14 Timers

Medium-density STM8L151x4/6 and STM8L152x4/6devices contain one advanced control timer (TIM1), two 16-bit general purpose timers (TIM2 and TIM3) and one 8-bit basic timer (TIM4).

All the timers can be served by DMA1.

Table 3 compares the features of the advanced control, general-purpose and basic timers.

| Timer | Counter resolution | Counter<br>type | Prescaler factor request          |     | Complementary<br>outputs |      |  |

|-------|--------------------|-----------------|-----------------------------------|-----|--------------------------|------|--|

| TIM1  |                    |                 | Any integer<br>from 1 to 65536    |     | 3 + 1                    | 3    |  |

| TIM2  | 16-bit             | up/down         | Any power of 2                    | Yes | 2                        |      |  |

| TIM3  |                    |                 | from 1 to 128                     | 103 | 2                        | None |  |

| TIM4  | 8-bit              | up              | Any power of 2<br>from 1 to 32768 |     | 0                        |      |  |

Table 3. Timer feature comparison

## 3.14.1 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver.

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- 3 independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- 1 additional capture/compare channel which is not connected to an external I/O

- Synchronization module to control the timer with external signals

- Break input to force timer outputs into a defined state

- 3 complementary outputs with adjustable dead time

- Encoder mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

# 3.19 Development support

### **Development tools**

Development tools for the STM8 microcontrollers include:

- The STice emulation system offering tracing and code profiling

- The STVD high-level language debugger including C compiler, assembler and integrated development environment

- The STVP Flash programming software

The STM8 also comes with starter kits, evaluation boards and low-cost in-circuit debugging/programming tools.

### Single wire data interface (SWIM) and debug module

The debug module with its single wire data interface (SWIM) permits non-intrusive real-time in-circuit debugging and fast memory programming.

The single-wire interface is used for direct access to the debugging module and memory programming. The interface can be activated in all device operation modes.

The non-intrusive debugging module features a performance close to a full-featured emulator. Beside memory and peripherals, CPU operation can also be monitored in real-time by means of shadow registers.

### Bootloader

A bootloader is available to reprogram the Flash memory using the USART1 interface. The reference document for the bootloader is *UM0560: STM8 bootloader user manual*.

| n               | Pin<br>umb      |          |         | s. Mealum-aensity STM                                                                            | _    |           |          | Input |                |                  | outpu            |    |                                |                                                                                                                                                                              |

|-----------------|-----------------|----------|---------|--------------------------------------------------------------------------------------------------|------|-----------|----------|-------|----------------|------------------|------------------|----|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP48/UFQFPN48 | LQFP32/UFQFPN32 | UFQFPN28 | WLCSP28 | Pin name                                                                                         | Type | I/O level | floating | ndw   | Ext. interrupt | High sink/source | OD               | ЪР | Main function<br>(after reset) | Default alternate<br>function                                                                                                                                                |

| 30              | -               | -        |         | PB6/[ <i>SPI1_MOSI]</i> <sup>(4)</sup> /<br>LCD_SEG16 <sup>(2)/</sup><br>ADC1_IN12/COMP1_INP     | I/O  | TT<br>(3) | x        | x     | x              | HS               | x                | х  | Port B6                        | [SPI1 master out/slave<br>in]/<br>LCD segment 16 /<br>ADC1_IN12 /<br>Comparator 1 positive<br>input                                                                          |

| -               | 19              | 18       | F1      | PB6/[SPI1_MOSI] <sup>(4)</sup> /<br>LCD_SEG16 <sup>(2)/</sup><br>ADC1_IN12/COMP1_INP/<br>DAC_OUT | I/O  | TT<br>(3) | x        | x     | х              | HS               | x                | х  | Port B6                        | [SPI1 master out]/<br>slave in / LCD segment<br>16 / ADC1_IN12 / DAC<br>output / Comparator 1<br>positive input                                                              |

| 31              | 20              | 19       | E1      | PB7/[SPI1_MISO] <sup>(4)</sup> /<br>LCD_SEG17 <sup>(2)/</sup><br>ADC1_IN11/COMP1_INP             | I/O  | TT<br>(3) | x        | x     | x              | HS               | x                | х  | Port B7                        | [SPI1 master in- slave<br>out] /<br>LCD segment 17 /<br>ADC1_IN11 /<br>Comparator 1 positive<br>input                                                                        |

| 37              | 25              | 21       | B1      | PC0 <sup>(5)</sup> /I2C1_SDA                                                                     | I/O  | FT        | X        |       | Х              |                  | T <sup>(7)</sup> |    | Port C0                        | I2C1 data                                                                                                                                                                    |

| 38              | 26              | 22       | A1      | PC1 <sup>(5)</sup> /I2C1_SCL                                                                     | I/O  | FT        | Х        |       | Х              |                  | T <sup>(7)</sup> |    | Port C1                        | I2C1 clock                                                                                                                                                                   |

| 41              | 27              | 23       | B2      | PC2/USART1_RX/<br>LCD_SEG22/ADC1_IN6/<br>COMP1_INP/VREFINT                                       | I/O  | TT<br>(3) | x        | x     | x              | HS               | x                | х  | Port C2                        | USART1 receive /<br>LCD segment 22 /<br>ADC1_IN6 / Comparator<br>1 positive input / Internal<br>voltage reference output                                                     |

| 42              | 28              | 24       | A2      | PC3/USART1_TX/<br>LCD_SEG23 <sup>(2)/</sup><br>ADC1_IN5/COMP1_INP/<br>COMP2_INM                  | I/O  | TT<br>(3) | x        | x     | x              | HS               | x                | x  | Port C3                        | USART1 transmit /<br>LCD segment 23 /<br>ADC1_IN5 / Comparator<br>1 positive input /<br>Comparator 2 negative<br>input                                                       |

| 43              | 29              | 25       | C2      | PC4/USART1_CK/<br>I2C1_SMB/CCO/<br>LCD_SEG24 <sup>(2)/</sup><br>ADC1_IN4/COMP2_INM/<br>COMP1_INP | I/O  | TT<br>(3) | x        | x     | х              | HS               | x                | х  | Port C4                        | USART1 synchronous<br>clock / I2C1_SMB /<br>Configurable clock<br>output / LCD segment 24<br>/ ADC1_IN4 /<br>Comparator 2 negative<br>input / Comparator 1<br>positive input |

### Table 5. Medium-density STM8L151x4/6, STM8L152x4/6 pin description (continued)

| Table 9. General hardware register map (continued) |                |                |                                   |                 |  |  |  |  |

|----------------------------------------------------|----------------|----------------|-----------------------------------|-----------------|--|--|--|--|

| Address                                            | Block          | Register label | Register name                     | Reset<br>status |  |  |  |  |

| 0x00 52D2                                          | <b>TIN 44</b>  | TIM1_DCR2      | TIM1 DMA1 control register 2      | 0x00            |  |  |  |  |

| 0x00 52D3                                          | TIM1           | TIM1_DMA1R     | TIM1 DMA1 address for burst mode  | 0x00            |  |  |  |  |

| 0x00 52D4<br>to<br>0x00 52DF                       |                | F              | Reserved area (12 bytes)          |                 |  |  |  |  |

| 0x00 52E0                                          |                | TIM4_CR1       | TIM4 control register 1           | 0x00            |  |  |  |  |

| 0x00 52E1                                          |                | TIM4_CR2       | TIM4 control register 2           | 0x00            |  |  |  |  |

| 0x00 52E2                                          |                | TIM4_SMCR      | TIM4 Slave mode control register  | 0x00            |  |  |  |  |

| 0x00 52E3                                          |                | TIM4_DER       | TIM4 DMA1 request enable register | 0x00            |  |  |  |  |

| 0x00 52E4                                          | <b>TIN</b> 4 4 | TIM4_IER       | TIM4 Interrupt enable register    | 0x00            |  |  |  |  |

| 0x00 52E5                                          | TIM4           | TIM4_SR1       | TIM4 status register 1            | 0x00            |  |  |  |  |

| 0x00 52E6                                          |                | TIM4_EGR       | TIM4 Event generation register    | 0x00            |  |  |  |  |

| 0x00 52E7                                          |                | TIM4_CNTR      | TIM4 counter                      | 0x00            |  |  |  |  |

| 0x00 52E8                                          |                | TIM4_PSCR      | TIM4 prescaler register           | 0x00            |  |  |  |  |

| 0x00 52E9                                          |                | TIM4_ARR       | TIM4 Auto-reload register         | 0x00            |  |  |  |  |

| 0x00 52EA<br>to<br>0x00 52FE                       |                | F              | Reserved area (21 bytes)          |                 |  |  |  |  |

| 0x00 52FF                                          | IRTIM          | IR_CR          | Infrared control register         | 0x00            |  |  |  |  |

| 0x00 5300<br>to<br>0x00 533F                       |                | F              | Reserved area (64 bytes)          |                 |  |  |  |  |

| 0x00 5340                                          |                | ADC1_CR1       | ADC1 configuration register 1     | 0x00            |  |  |  |  |

| 0x00 5341                                          |                | ADC1_CR2       | ADC1 configuration register 2     | 0x00            |  |  |  |  |

| 0x00 5342                                          |                | ADC1_CR3       | ADC1 configuration register 3     | 0x1F            |  |  |  |  |

| 0x00 5343                                          |                | ADC1_SR        | ADC1 status register              | 0x00            |  |  |  |  |

| 0x00 5344                                          | 1              | ADC1_DRH       | ADC1 data register high           | 0x00            |  |  |  |  |

| 0x00 5345                                          |                | ADC1_DRL       | ADC1 data register low            | 0x00            |  |  |  |  |

| 0x00 5346                                          |                | ADC1_HTRH      | ADC1 high threshold register high | 0x0F            |  |  |  |  |

| 0x00 5347                                          | ADC1           | ADC1_HTRL      | ADC1 high threshold register low  | 0xFF            |  |  |  |  |

| 0x00 5348                                          | 1              | ADC1_LTRH      | ADC1 low threshold register high  | 0x00            |  |  |  |  |

| 0x00 5349                                          | 1              | ADC1_LTRL      | ADC1 low threshold register low   | 0x00            |  |  |  |  |

| 0x00 534A                                          | 1              | ADC1_SQR1      | ADC1 channel sequence 1 register  | 0x00            |  |  |  |  |

| 0x00 534B                                          |                | ADC1_SQR2      | ADC1 channel sequence 2 register  | 0x00            |  |  |  |  |

| 0x00 534C                                          |                | ADC1_SQR3      | ADC1 channel sequence 3 register  | 0x00            |  |  |  |  |

| 0x00 534D                                          |                | ADC1_SQR4      | ADC1 channel sequence 4 register  | 0x00            |  |  |  |  |

### Table 9. General hardware register map (continued)

| IRQ<br>No. | Source<br>block   | Description                                                                                               | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |  |  |  |

|------------|-------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|--|--|--|

| 19         | TIM2              | TIM2 update/overflow/<br>trigger/break interrupt                                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8054         |  |  |  |

| 20         | TIM2              | TIM2 capture/<br>compare interrupt                                                                        | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8058         |  |  |  |

| 21         | TIM3              | TIM3 update/overflow/<br>trigger/break interrupt                                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 805C         |  |  |  |

| 22         | TIM3              | TIM3 capture/<br>compare interrupt                                                                        | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8060         |  |  |  |

| 23         | TIM1              | Update /overflow/trigger/<br>COM                                                                          | -                           | -                                     | -                                    | Yes                                                 | 0x00 8064         |  |  |  |

| 24         | TIM1              | Capture/compare                                                                                           | -                           | -                                     | -                                    | Yes                                                 | 0x00 8068         |  |  |  |

| 25         | TIM4              | TIM4 update/overflow/<br>trigger interrupt                                                                | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 806C         |  |  |  |

| 26         | SPI1              | SPI1 TX buffer empty/<br>RX buffer not empty/<br>error/wakeup interrupt                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8070         |  |  |  |

| 27         | USART1            | USART1 transmit data<br>register empty/<br>transmission complete<br>interrupt                             | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8074         |  |  |  |

| 28         | USART1            | USART1 received data<br>ready/overrun error/<br>idle line detected/parity<br>error/global error interrupt | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8078         |  |  |  |

| 29         | l <sup>2</sup> C1 | I <sup>2</sup> C1 interrupt <sup>(3)</sup>                                                                | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 807C         |  |  |  |

Table 11. Interrupt mapping (continued)

The Low power wait mode is entered when executing a WFE instruction in Low power run mode. In WFE mode, the

interrupt is served if it has been previously enabled. After processing the interrupt, the processor goes back to WFE mode.

When the interrupt is configured as a wakeup event, the CPU wakes up and resumes processing.

2. The interrupt from PVD is logically OR-ed with Port E and F interrupts. Register EXTI\_CONF allows to select between Port E and Port F interrupt (see *External interrupt port select register (EXTI\_CONF)* in the RM0031).

3. The device is woken up from Halt or Active-halt mode only when the address received matches the interface address.

| Symbol                | Ratings                                                                  | Max.     | Unit |

|-----------------------|--------------------------------------------------------------------------|----------|------|

| I <sub>VDD</sub>      | Total current into V <sub>DD</sub> power line (source)                   | 80       |      |

| I <sub>VSS</sub>      | Total current out of V <sub>SS</sub> ground line (sink)                  | 80       |      |

|                       | Output current sunk by IR_TIM pin (with high sink LED driver capability) | 80       | mA   |

| Ι <sub>ΙΟ</sub>       | Output current sunk by any other I/O and control pin                     | 25       |      |

|                       | Output current sourced by any I/Os and control pin                       | - 25     |      |

|                       | Injected current on true open-drain pins (PC0 and PC1) <sup>(1)</sup>    | - 5 / +0 |      |

| I                     | Injected current on five-volt tolerant (FT) pins (PA7 and PE0) $^{(1)}$  | - 5 / +0 | mA   |

| I <sub>INJ(PIN)</sub> | Injected current on 3.6 V tolerant (TT) pins <sup>(1)</sup>              | - 5 / +0 | ША   |

|                       | Injected current on any other pin <sup>(2)</sup>                         | - 5 / +5 |      |

| $\Sigma I_{INJ(PIN)}$ | Total injected current (sum of all I/O and control pins) $^{(3)}$        | ± 25     |      |

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 15*. for maximum allowed input voltage values.

2. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 15*. for maximum allowed input voltage values.

3. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |  |  |

|------------------|------------------------------|-------------|------|--|--|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 |      |  |  |

| ТJ               | Maximum junction temperature | 150         |      |  |  |

#### Table 17. Thermal characteristics

- 1. Data guaranteed by design.

- 2. Data based on characterization results.

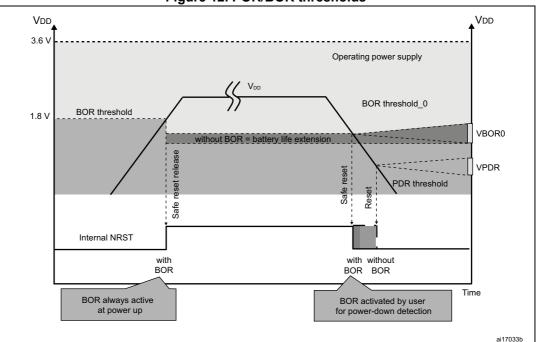

### Figure 12. POR/BOR thresholds

### 9.3.3 Supply current characteristics

### **Total current consumption**

The MCU is placed under the following conditions:

- I All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- I All peripherals are disabled except if explicitly mentioned.

In the following table, data is based on characterization results, unless otherwise specified. Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

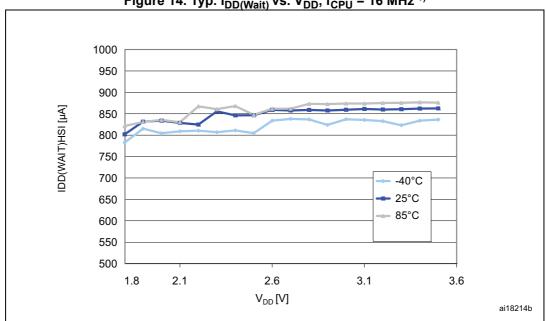

Figure 14. Typ. I<sub>DD(Wait)</sub> vs. V<sub>DD</sub>,  $f_{CPU}$  = 16 MHz <sup>1)</sup>

1. Typical current consumption measured with code executed from Flash memory.

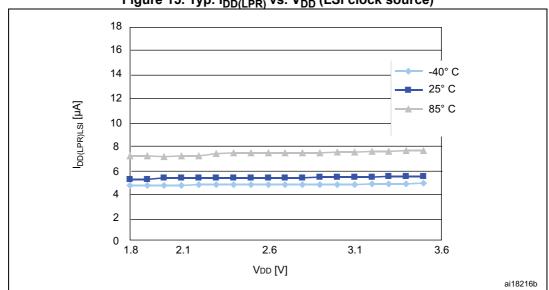

Figure 15. Typ. I<sub>DD(LPR)</sub> vs. V<sub>DD</sub> (LSI clock source)

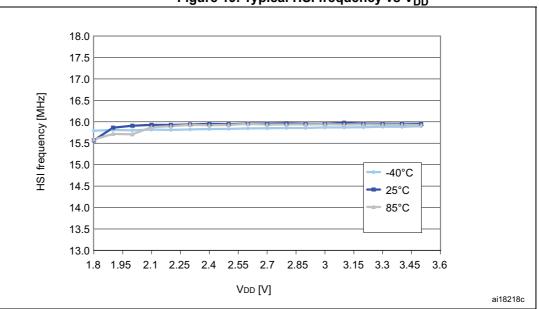

Figure 19. Typical HSI frequency vs V<sub>DD</sub>

### Low speed internal RC oscillator (LSI)

In the following table, data is based on characterization results, not tested in production.

|                      | 10,510                                        |                              | anaoton | 01100 |                    |      |

|----------------------|-----------------------------------------------|------------------------------|---------|-------|--------------------|------|

| Symbol               | Parameter <sup>(1)</sup>                      | Conditions <sup>(1)</sup>    | Min     | Тур   | Max                | Unit |

| f <sub>LSI</sub>     | Frequency                                     | -                            | 26      | 38    | 56                 | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time                    | -                            | -       | -     | 200 <sup>(2)</sup> | μs   |

| I <sub>DD(LSI)</sub> | LSI oscillator frequency drift <sup>(3)</sup> | 0 °C ≤T <sub>A</sub> ≤ 85 °C | -12     | -     | 11                 | %    |

Table 34. LSI oscillator characteristics

1.  $V_{DD}$  = 1.65 V to 3.6 V,  $T_A$  = -40 to 125  $^\circ C$  unless otherwise specified.

2. Guaranteed by design.

3. This is a deviation for an individual part, once the initial frequency has been measured.

### 9.3.5 Memory characteristics

$T_A$  = -40 to 125 °C unless otherwise specified.

| Symbol          | Parameter                          | Conditions           | Min  | Тур | Max | Unit |  |  |  |

|-----------------|------------------------------------|----------------------|------|-----|-----|------|--|--|--|

| V <sub>RM</sub> | Data retention mode <sup>(1)</sup> | Halt mode (or Reset) | 1.65 | -   | -   | V    |  |  |  |

Table 35. RAM and hardware registers

1. Minimum supply voltage without losing data stored in RAM (in Halt mode or under Reset) or in hardware registers (only in Halt mode). Guaranteed by characterization, not tested in production.

### **Flash memory**

| Symbol                          | Parameter                                                                                               | Conditions                                                   | Min                       | Тур | Max<br>(1) | Unit    |

|---------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------|-----|------------|---------|

| $V_{DD}$                        | Operating voltage<br>(all modes, read/write/erase)                                                      | f <sub>SYSCLK</sub> = 16 MHz                                 | 1.65                      | -   | 3.6        | V       |

| +                               | Programming time for 1 or 64 bytes (block)<br>erase/write cycles (on programmed byte)                   | -                                                            | -                         | 6   | -          | ms      |

| t <sub>prog</sub>               | Programming time for 1 to 64 bytes (block) write cycles (on erased byte)                                | -                                                            | -                         | 3   | -          | ms      |

| 1                               | Programming/ erasing consumption                                                                        | T <sub>A</sub> =+25 °C, V <sub>DD</sub> = 3.0 V              | -                         | 0.7 | -          | mA      |

| Iprog                           |                                                                                                         | T <sub>A</sub> =+25 °C, V <sub>DD</sub> = 1.8 V              | -                         | 0.7 | -          | IIIA    |

|                                 | Data retention (program memory) after 10000 erase/write cycles at $T_A$ = -40 to +85 °C (6 suffix)      | T <sub>RET</sub> = +85 °C                                    | 30 <sup>(1)</sup>         | -   | -          |         |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after 10000 erase/write cycles at $T_A$ = -40 to +125 °C (3 suffix)     | T <sub>RET</sub> = +125 °C                                   | 5 <sup>(1)</sup>          | -   | -          | Vooro   |

| 'RET` ′                         | Data retention (data memory) after 300000<br>erase/write cycles at $T_A$ = -40 to +85 °C<br>(6 suffix)  | T <sub>RET</sub> = +85 °C                                    | 30 <sup>(1)</sup>         | -   | -          | years   |

|                                 | Data retention (data memory) after 300000<br>erase/write cycles at $T_A$ = -40 to +125 °C<br>(3 suffix) | T <sub>RET</sub> = +125 °C                                   | 5 <sup>(1)</sup>          | -   | -          |         |

|                                 | Erase/write cycles (program memory)                                                                     | $T_{A} = -40 \text{ to } +85 \text{ °C}$                     | 10 <sup>(1)</sup>         | -   | -          |         |

| $N_{RW}^{(3)}$                  | Erase/write cycles (data memory)                                                                        | (6 suffix),<br>T <sub>A</sub> = -40 to +125 °C<br>(3 suffix) | 300 <sup>(1)</sup><br>(4) | -   | -          | kcycles |

### Table 36. Flash program and data EEPROM memory

1. Data based on characterization results.

2. Conforming to JEDEC JESD22a117

3. The physical granularity of the memory is 4 bytes, so cycling is performed on 4 bytes even when a write/erase operation addresses a single byte.

4. Data based on characterization performed on the whole data memory.

### 9.3.6 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error, out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation, LCD levels, etc.).

The test results are given in the following table.

|                  |                                                        | Functional s       |                    |      |

|------------------|--------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                            | Negative injection | Positive injection | Unit |

|                  | Injected current on true open-drain pins (PC0 and PC1) | -5                 | +0                 |      |

| I <sub>INJ</sub> | Injected current on all five-volt tolerant (FT) pins   | -5                 | +0                 | mA   |

|                  | Injected current on all 3.6 V tolerant (TT) pins       | -5                 | +0                 |      |

|                  | Injected current on any other pin                      | -5                 | +5                 |      |

### Table 37. I/O current injection susceptibility

## 9.3.7 I/O port pin characteristics

### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

R<sub>PU</sub> pull-up equivalent resistor based on a resistive transistor (corresponding I<sub>PU</sub> current characteristics described in Figure 24).

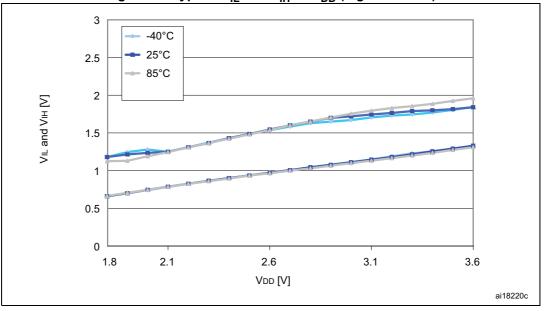

Figure 21. Typical  $V_{IL}$  and  $V_{IH}\, vs \, V_{DD}$  (high sink I/Os)

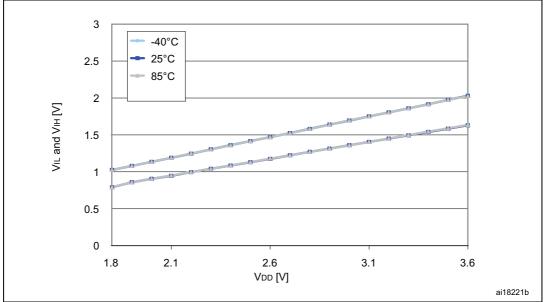

Figure 22. Typical V<sub>IL</sub> and V<sub>IH</sub> vs V<sub>DD</sub> (true open drain I/Os)

### **Output driving current**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified.

| l/O<br>Type | Symbol                         | Parameter                                | Conditions                                           | Min                   | Max     | Unit |

|-------------|--------------------------------|------------------------------------------|------------------------------------------------------|-----------------------|---------|------|

|             |                                |                                          | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 3.0 V  | 0.45                  | V       |      |

|             | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 1.8 V  | -                     | 0.45    | V    |

| High sink   |                                |                                          | I <sub>IO</sub> = +10 mA,<br>V <sub>DD</sub> = 3.0 V | -                     | - 0.7 V | V    |

|             |                                |                                          | I <sub>IO</sub> = -2 mA,<br>V <sub>DD</sub> = 3.0 V  | V <sub>DD</sub> -0.45 | -       | V    |

|             | V <sub>OH</sub> <sup>(2)</sup> | Output high level voltage for an I/O pin | I <sub>IO</sub> = -1 mA,<br>V <sub>DD</sub> = 1.8 V  | V <sub>DD</sub> -0.45 | -       | V    |

|             |                                |                                          | I <sub>IO</sub> = -10 mA,<br>V <sub>DD</sub> = 3.0 V | V <sub>DD</sub> -0.7  | -       | V    |

| Table 39. Output driving current (high sink por | 'ts) |

|-------------------------------------------------|------|

|-------------------------------------------------|------|

The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

| l/O<br>Type | Symbol                         | Parameter                                   | Conditions                                          | Min | Max  | Unit |

|-------------|--------------------------------|---------------------------------------------|-----------------------------------------------------|-----|------|------|

| drain       | V <sub>OL</sub> <sup>(1)</sup> | (1) Output low lovel veltage for on 1/0 nin | I <sub>IO</sub> = +3 mA,<br>V <sub>DD</sub> = 3.0 V | -   | 0.45 | V    |

| Open        | VOL                            | Output low level voltage for an I/O pin     | I <sub>IO</sub> = +1 mA,<br>V <sub>DD</sub> = 1.8 V | -   | 0.45 | v    |

#### Table 40. Output driving current (true open drain ports)

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

| I/О<br>Туре | Symbol                         | Parameter                               | Conditions                                           | Min | Max  | Unit |

|-------------|--------------------------------|-----------------------------------------|------------------------------------------------------|-----|------|------|

| R           | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin | I <sub>IO</sub> = +20 mA,<br>V <sub>DD</sub> = 2.0 V | -   | 0.45 | V    |

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

## 9.3.9 LCD controller (STM8L152xx only)

In the following table, data is guaranteed by design. Not tested in production.

| Symbol                         | Parameter                                         | Min | Тур                  | Max.              | Unit |

|--------------------------------|---------------------------------------------------|-----|----------------------|-------------------|------|

| $V_{LCD}$                      | LCD external voltage                              | -   | -                    | 3.6               | V    |

| V <sub>LCD0</sub>              | LCD internal reference voltage 0                  | -   | 2.6                  | -                 | V    |

| V <sub>LCD1</sub>              | LCD internal reference voltage 1                  | -   | 2.7                  | -                 | V    |

| V <sub>LCD2</sub>              | LCD internal reference voltage 2                  | -   | 2.8                  | -                 | V    |

| V <sub>LCD3</sub>              | LCD internal reference voltage 3                  | -   | 2.9                  | -                 | V    |

| V <sub>LCD4</sub>              | LCD internal reference voltage 4                  | -   | 3.0                  | -                 | V    |

| $V_{LCD5}$                     | LCD internal reference voltage 5                  | -   | 3.1                  | -                 | V    |

| V <sub>LCD6</sub>              | LCD internal reference voltage 6                  | -   | 3.2                  | -                 | V    |

| V <sub>LCD7</sub>              | LCD internal reference voltage 7                  | -   | 3.3                  | -                 | V    |

| C <sub>EXT</sub>               | V <sub>LCD</sub> external capacitance             | 0.1 | -                    | 2                 | μF   |

| I                              | Supply current <sup>(1)</sup> at $V_{DD}$ = 1.8 V | -   | 3                    | -                 | μA   |

| I <sub>DD</sub>                | Supply current <sup>(1)</sup> at $V_{DD}$ = 3 V   | -   | 3                    | -                 | μA   |

| R <sub>HN</sub> <sup>(2)</sup> | High value resistive network (low drive)          | -   | 6.6                  | -                 | MΩ   |

| $R_{LN}^{(3)}$                 | Low value resistive network (high drive)          | -   | 360                  | -                 | kΩ   |

| V <sub>33</sub>                | Segment/Common higher level voltage               | -   | -                    | V <sub>LCDx</sub> | V    |

| V <sub>23</sub>                | Segment/Common 2/3 level voltage                  | -   | 2/3V <sub>LCDx</sub> | -                 | V    |

| V <sub>12</sub>                | Segment/Common 1/2 level voltage                  | -   | 1/2V <sub>LCDx</sub> | -                 | V    |

| V <sub>13</sub>                | Segment/Common 1/3 level voltage                  | -   | 1/3V <sub>LCDx</sub> | -                 | V    |

| V <sub>0</sub>                 | Segment/Common lowest level voltage               | 0   | -                    | -                 | V    |

1. LCD enabled with 3 V internal booster (LCD\_CR1 = 0x08), 1/4 duty, 1/3 bias, division ratio= 64, all pixels active, no LCD connected.

2.  $\ R_{HN}$  is the total high value resistive network.

3. R<sub>LN</sub> is the total low value resistive network.

### VLCD external capacitor (STM8L152xx only)

The application can achieve a stabilized LCD reference voltage by connecting an external capacitor  $C_{EXT}$  to the  $V_{LCD}$  pin.  $C_{EXT}$  is specified in *Table 45*.

In the following table, data is guaranteed by design, not tested in production.

| Symbol              | Parameter                                     | Conditions                      | Min  | Тур | Max <sup>(1)</sup> | Unit |

|---------------------|-----------------------------------------------|---------------------------------|------|-----|--------------------|------|

| $V_{DDA}$           | Analog supply voltage                         | -                               | 1.65 | -   | 3.6                | V    |

| T <sub>A</sub>      | Temperature range                             | -                               | -40  | -   | 125                | °C   |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                               | 0    | -   | V <sub>DDA</sub>   | V    |

| t.                  | Comparator startup time                       | Fast mode                       | -    | 15  | 20                 | μs   |

| t <sub>START</sub>  |                                               | Slow mode                       | -    | 20  | 25                 |      |

| t <sub>d slow</sub> | Propagation delay in slow mode <sup>(2)</sup> | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V | -    | 1.8 | 3.5                |      |

|                     |                                               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V  | -    | 2.5 | 6                  |      |

| 4                   | Propagation delay in fast mode <sup>(2)</sup> | 1.65 V ≤V <sub>DDA</sub> ≤2.7 V | -    | 0.8 | 2                  |      |

| t <sub>d fast</sub> |                                               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V  | -    | 1.2 | 4                  |      |

| V <sub>offset</sub> | Comparator offset error                       | -                               | -    | ±4  | ±20                | mV   |

| 1                   | Current consumption <sup>(3)</sup>            | Fast mode                       | -    | 3.5 | 5                  | μA   |

| ICOMP2              |                                               | Slow mode                       | -    | 0.5 | 2                  | μΑ   |

#### Table 49. Comparator 2 characteristics

1. Based on characterization.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

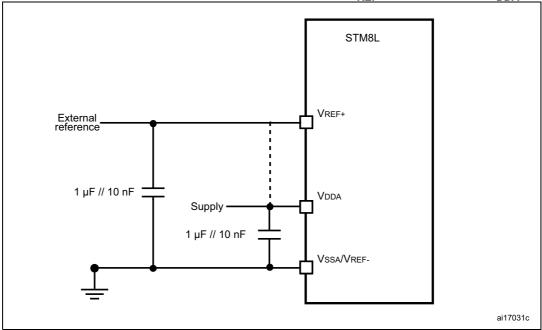

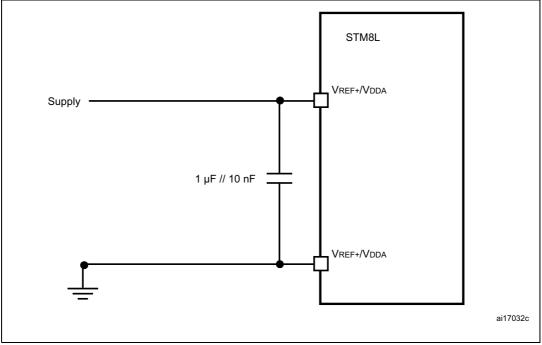

Figure 41. Power supply and reference decoupling ( $V_{REF+}$  not connected to  $V_{DDA}$ )

### Figure 42. Power supply and reference decoupling (V<sub>REF+</sub> connected to V<sub>DDA</sub>)

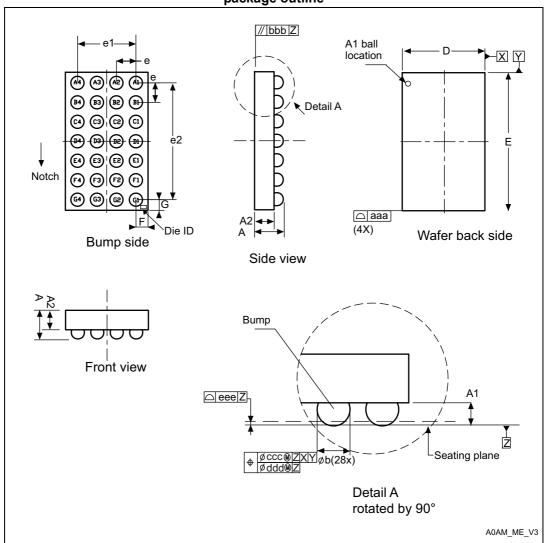

# 10.7 WLCSP28 package information

Figure 58. WLCSP28 - 28-pin, 1.703 x 2.841 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

DocID15962 Rev 15