Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, POR, PWM, WDT                       |

| Number of I/O              | 41                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 1K x 8                                                               |

| RAM Size                   | 2K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                          |

| Data Converters            | A/D 25x12b; D/A 1x12b                                                |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 48-UFQFN Exposed Pad                                                 |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151c6u6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This document describes the features, pinout, mechanical data and ordering information of the medium-density STM8L151x4/6 and STM8L152x4/6 devices (STM8L151Cx/Kx/Gx, STM8L152Cx/Kx microcontrollers with a 16-Kbyte or 32-Kbyte Flash memory density). These devices are referred to as medium-density devices in the STM8L15x and STM8L16x reference manual (RM0031) and in the STM8L Flash programming manual (PM0054).

For more details on the whole STMicroelectronics ultra-low-power family please refer to *Section 2.2: Ultra-low-power continuum on page 13.*

For information on the debug module and SWIM (single wire interface module), refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

The medium-density devices provide the following benefits:

- Integrated system

- Up to 32 Kbyte of medium-density embedded Flash program memory

- 1 Kbyte of data EEPROM

- Internal high speed and low-power low speed RC

- Embedded reset

- Ultra-low power consumption

- 195 μA/MHz + 440 μA (consumption)

- 0.9 µA with LSI in Active-halt mode

- Clock gated system and optimized power management

- Capability to execute from RAM for Low power wait mode and Low power run mode

- Advanced features

- Up to 16 MIPS at 16 MHz CPU clock frequency

- Direct memory access (DMA) for memory-to-memory or peripheral-to-memory access

- Short development cycles

- Application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals

- Wide choice of development tools

All devices offer 12-bit ADC, DAC, two comparators, Real-time clock three 16-bit timers, one 8-bit timer as well as standard communication interface such as SPI, I2C and USART. A 4x28-segment LCD is available on the medium-density STM8L152xx line. *Table 2: Medium-density STM8L151x4/6 and STM8L152x4/6 low-power device features and peripheral counts* and *Section 3: Functional overview* give an overview of the complete range of peripherals proposed in this family.

Figure 1 on page 14 shows the general block diagram of the device family.

and STM8L152x4/6 devices, the acquisition sequence is managed by software and it involves analog I/O groups and the routing interface.

Reliable touch sensing solutions can be quickly and easily implemented using the free STM8 Touch Sensing Library.

# 3.14 Timers

Medium-density STM8L151x4/6 and STM8L152x4/6devices contain one advanced control timer (TIM1), two 16-bit general purpose timers (TIM2 and TIM3) and one 8-bit basic timer (TIM4).

All the timers can be served by DMA1.

Table 3 compares the features of the advanced control, general-purpose and basic timers.

| Timer | Counter resolution | Counter<br>type | Prescaler factor                  | DMA1<br>request<br>generation | Capture/compare<br>channels    | Complementary<br>outputs |       |   |

|-------|--------------------|-----------------|-----------------------------------|-------------------------------|--------------------------------|--------------------------|-------|---|

| TIM1  |                    | up/down         |                                   |                               | Any integer<br>from 1 to 65536 |                          | 3 + 1 | 3 |

| TIM2  | 16-bit             |                 | Any power of 2                    | Yes                           | 2                              | None                     |       |   |

| TIM3  |                    |                 | from 1 to 128                     | 103                           | 2                              |                          |       |   |

| TIM4  | 8-bit              | up              | Any power of 2<br>from 1 to 32768 |                               | 0                              |                          |       |   |

Table 3. Timer feature comparison

# 3.14.1 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver.

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- 3 independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- 1 additional capture/compare channel which is not connected to an external I/O

- Synchronization module to control the timer with external signals

- Break input to force timer outputs into a defined state

- 3 complementary outputs with adjustable dead time

- Encoder mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

| n               | Pin<br>umb      |          |         | . Mealum-density STM                                                                                                   | _    |           | -        | nput |                |                  | utpu |    |                                |                                                                                                                                                           |

|-----------------|-----------------|----------|---------|------------------------------------------------------------------------------------------------------------------------|------|-----------|----------|------|----------------|------------------|------|----|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP48/UFQFPN48 | LQFP32/UFQFPN32 | UFQFPN28 | WLCSP28 | Pin name                                                                                                               | Type | I/O level | floating | ndw  | Ext. interrupt | High sink/source | OD   | ЧЧ | Main function<br>(after reset) | Default alternate<br>function                                                                                                                             |

| 44              | 30              | 26       |         | PC5/OSC32_IN<br>/[SPI1_NSS] <sup>(4)</sup> /<br>[USART1_TX] <sup>(4)</sup>                                             | I/O  |           | x        | x    | х              | HS               | х    | х  | Port C5                        | LSE oscillator input /<br>[SPI1 master/slave<br>select] / [USART1<br>transmit]                                                                            |

| 45              | 31              | 27       | B3      | PC6/OSC32_OUT/<br>[SPI1_SCK] <sup>(4)</sup> /<br>[USART1_RX] <sup>(4)</sup>                                            | I/O  |           | x        | x    | х              | нs               | x    | Х  | Port C6                        | LSE oscillator output /<br>[SPI1 clock] / [USART1<br>receive]                                                                                             |

| 46              | -               | -        | -       | PC7/LCD_SEG25 <sup>(2)/</sup><br>ADC1_IN3/COMP2_INM/<br>COMP1_INP                                                      | I/O  | TT<br>(3) | x        | x    | х              | HS               | x    | x  | Port C7                        | LCD segment 25<br>/ADC1_IN3/ Comparator<br>negative input /<br>Comparator 1 positive<br>input                                                             |

| 20              | -               | 8        | G3      | PD0/TIM3_CH2/<br><i>[ADC1_TRIG]<sup>(4)</sup>/</i><br>LCD_SEG7 <sup>(2)</sup> /ADC1_IN2<br>2/COMP2_INP/<br>COMP1_INP   | I/O  | TT<br>(3) | x        | x    | x              | HS               | x    | x  | Port D0                        | Timer 3 - channel 2 /<br>[ADC1_Trigger] / LCD<br>segment 7 / ADC1_IN22<br>/ Comparator 2 positive<br>input / Comparator 1<br>positive input               |

| -               | 9               | -        | -       | PD0/TIM3_CH2/<br><i>[ADC1_TRIG]<sup>(4)</sup>/</i><br>ADC1_IN22/COMP2_INP/<br>COMP1_INP                                | I/O  | TT<br>(3) | x        | x    | x              | HS               | x    | x  | Port<br>D0 <sup>(8)</sup>      | Timer 3 - channel 2 /<br>[ADC1_Trigger] /<br>ADC1_IN22 /<br>Comparator 2 positive<br>input / Comparator 1<br>positive input                               |

| 21              | -               | -        | -       | PD1/TIM3_ETR/<br>LCD_COM3 <sup>(2)</sup> /<br>ADC1_IN21/COMP2_INP/<br>COMP1_INP                                        | I/O  | TT<br>(3) | x        | x    | x              | HS               | x    | x  | Port D1                        | Timer 3 - external trigger<br>/ LCD_COM3 /<br>ADC1_IN21 /<br>comparator 2 positive<br>input / Comparator 1<br>positive input                              |

| -               | 10              | _        |         | PD1/TIM1_CH3N/[ <i>TIM3_<br/>ETR</i> ] <sup>(4)</sup> / LCD_COM3 <sup>(2)</sup> /<br>ADC1_IN21/COMP2_INP/<br>COMP1_INP | I/O  | TT<br>(3) | x        | x    | x              | HS               | x    | х  | Port D1                        | [Timer 3 - external<br>trigger]/ TIM1 inverted<br>channel 3 / LCD_COM3/<br>ADC1_IN21 /<br>Comparator 2 positive<br>input / Comparator 1<br>positive input |

# Table 5. Medium-density STM8L151x4/6, STM8L152x4/6 pin description (continued)

| Address   | Block  | Register label | Register name                     | Reset<br>status |

|-----------|--------|----------------|-----------------------------------|-----------------|

| 0x00 500A |        | PC_ODR         | Port C data output latch register | 0x00            |

| 0x00 500B |        | PC_IDR         | Port C input pin value register   | 0xXX            |

| 0x00 500C | Port C | PC_DDR         | Port C data direction register    | 0x00            |

| 0x00 500D | _      | PC_CR1         | Port C control register 1         | 0x00            |

| 0x00 500E |        | PC_CR2         | Port C control register 2         | 0x00            |

| 0x00 500F |        | PD_ODR         | Port D data output latch register | 0x00            |

| 0x00 5010 |        | PD_IDR         | Port D input pin value register   | 0xXX            |

| 0x00 5011 | Port D | PD_DDR         | Port D data direction register    | 0x00            |

| 0x00 5012 |        | PD_CR1         | Port D control register 1         | 0x00            |

| 0x00 5013 |        | PD_CR2         | Port D control register 2         | 0x00            |

| 0x00 5014 |        | PE_ODR         | Port E data output latch register | 0x00            |

| 0x00 5015 |        | PE_IDR         | Port E input pin value register   | 0xXX            |

| 0x00 5016 | Port E | PE_DDR         | Port E data direction register    | 0x00            |

| 0x00 5017 |        | PE_CR1         | Port E control register 1         | 0x00            |

| 0x00 5018 |        | PE_CR2         | Port E control register 2         | 0x00            |

| 0x00 5019 |        | PF_ODR         | Port F data output latch register | 0x00            |

| 0x00 501A | 1      | PF_IDR         | Port F input pin value register   | 0xXX            |

| 0x00 501B | Port F | PF_DDR         | Port F data direction register    | 0x00            |

| 0x00 501C | 1      | PF_CR1         | Port F control register 1         | 0x00            |

| 0x00 501D | 1      | PF_CR2         | Port F control register 2         | 0x00            |

| Table 8 1/O  | nort hardwara | rogistor man | (continued) |

|--------------|---------------|--------------|-------------|

| Table 6. I/O | port hardware | register map | (continuea) |

# Table 9. General hardware register map

| Address                      | Block | Register label           | Register name                                       | Reset<br>status |  |  |  |

|------------------------------|-------|--------------------------|-----------------------------------------------------|-----------------|--|--|--|

| 0x00 501E<br>to<br>0x00 5049 |       | Reserved area (28 bytes) |                                                     |                 |  |  |  |

| 0x00 5050                    |       | FLASH_CR1                | Flash control register 1                            | 0x00            |  |  |  |

| 0x00 5051                    |       | FLASH_CR2                | Flash control register 2                            | 0x00            |  |  |  |

| 0x00 5052                    | Flash | FLASH_PUKR               | Flash program memory unprotection key<br>register   | 0x00            |  |  |  |

| 0x00 5053                    |       | FLASH_DUKR               | Data EEPROM unprotection key register               | 0x00            |  |  |  |

| 0x00 5054                    |       | FLASH_IAPSR              | Flash in-application programming status<br>register | 0x00            |  |  |  |

| Address                      | Block | Register label           | Register name                                           | Reset<br>status |  |  |

|------------------------------|-------|--------------------------|---------------------------------------------------------|-----------------|--|--|

| 0x00 5055<br>to<br>0x00 506F |       | Reserved area (27 bytes) |                                                         |                 |  |  |

| 0x00 5070                    |       | DMA1_GCSR                | DMA1 global configuration & status<br>register          | 0xFC            |  |  |

| 0x00 5071                    |       | DMA1_GIR1                | DMA1 global interrupt register 1                        | 0x00            |  |  |

| 0x00 5072 to<br>0x00 5074    |       |                          | Reserved area (3 bytes)                                 |                 |  |  |

| 0x00 5075                    |       | DMA1_C0CR                | DMA1 channel 0 configuration register                   | 0x00            |  |  |

| 0x00 5076                    |       | DMA1_C0SPR               | DMA1 channel 0 status & priority register               | 0x00            |  |  |

| 0x00 5077                    |       | DMA1_C0NDTR              | DMA1 number of data to transfer register<br>(channel 0) | 0x00            |  |  |

| 0x00 5078                    |       | DMA1_C0PARH              | DMA1 peripheral address high register<br>(channel 0)    | 0x52            |  |  |

| 0x00 5079                    |       | DMA1_C0PARL              | DMA1 peripheral address low register<br>(channel 0)     | 0x00            |  |  |

| 0x00 507A                    | DMA1  |                          | Reserved area (1 byte)                                  |                 |  |  |

| 0x00 507B                    |       | DMA1_C0M0ARH             | DMA1 memory 0 address high register<br>(channel 0)      | 0x00            |  |  |

| 0x00 507C                    |       | DMA1_C0M0ARL             | DMA1 memory 0 address low register<br>(channel 0)       | 0x00            |  |  |

| 0x00 507D to<br>0x00 507E    |       |                          | Reserved area (2 bytes)                                 |                 |  |  |

| 0x00 507F                    |       | DMA1_C1CR                | DMA1 channel 1 configuration register                   | 0x00            |  |  |

| 0x00 5080                    |       | DMA1_C1SPR               | DMA1 channel 1 status & priority register               | 0x00            |  |  |

| 0x00 5081                    |       | DMA1_C1NDTR              | DMA1 number of data to transfer register<br>(channel 1) | 0x00            |  |  |

| 0x00 5082                    |       | DMA1_C1PARH              | DMA1 peripheral address high register<br>(channel 1)    | 0x52            |  |  |

| 0x00 5083                    |       | DMA1_C1PARL              | DMA1 peripheral address low register<br>(channel 1)     | 0x00            |  |  |

Table 9. General hardware register map (continued)

| Table 9. General hardware register map (continued) |              |                |                                           |                 |  |  |  |

|----------------------------------------------------|--------------|----------------|-------------------------------------------|-----------------|--|--|--|

| Address                                            | Block        | Register label | Register name                             | Reset<br>status |  |  |  |

| 0x00 50A0                                          |              | EXTI_CR1       | External interrupt control register 1     | 0x00            |  |  |  |

| 0x00 50A1                                          |              | EXTI_CR2       | External interrupt control register 2     | 0x00            |  |  |  |

| 0x00 50A2                                          |              | EXTI_CR3       | External interrupt control register 3     | 0x00            |  |  |  |

| 0x00 50A3                                          | - ITC - EXTI | EXTI_SR1       | External interrupt status register 1      | 0x00            |  |  |  |

| 0x00 50A4                                          |              | EXTI_SR2       | External interrupt status register 2      | 0x00            |  |  |  |

| 0x00 50A5                                          |              | EXTI_CONF1     | External interrupt port select register 1 | 0x00            |  |  |  |

| 0x00 50A6                                          |              | WFE_CR1        | WFE control register 1                    | 0x00            |  |  |  |

| 0x00 50A7                                          | WFE          | WFE_CR2        | WFE control register 2                    | 0x00            |  |  |  |

| 0x00 50A8                                          |              | WFE_CR3        | WFE control register 3                    | 0x00            |  |  |  |

| 0x00 50A9<br>to<br>0x00 50AF                       |              | F              | Reserved area (7 bytes)                   |                 |  |  |  |

| 0x00 50B0                                          | RST          | RST_CR         | Reset control register                    | 0x00            |  |  |  |

| 0x00 50B1                                          | - KOT        | RST_SR         | Reset status register                     | 0x01            |  |  |  |

| 0x00 50B2                                          | PWR          | PWR_CSR1       | Power control and status register 1       | 0x00            |  |  |  |

| 0x00 50B3                                          |              | PWR_CSR2       | Power control and status register 2       | 0x00            |  |  |  |

| 0x00 50B4<br>to<br>0x00 50BF                       |              | R              | Reserved area (12 bytes)                  |                 |  |  |  |

| 0x00 50C0                                          |              | CLK_DIVR       | Clock master divider register             | 0x03            |  |  |  |

| 0x00 50C1                                          |              | CLK_CRTCR      | Clock RTC register                        | 0x00            |  |  |  |

| 0x00 50C2                                          |              | CLK_ICKR       | Internal clock control register           | 0x11            |  |  |  |

| 0x00 50C3                                          |              | CLK_PCKENR1    | Peripheral clock gating register 1        | 0x00            |  |  |  |

| 0x00 50C4                                          |              | CLK_PCKENR2    | Peripheral clock gating register 2        | 0x80            |  |  |  |

| 0x00 50C5                                          |              | CLK_CCOR       | Configurable clock control register       | 0x00            |  |  |  |

| 0x00 50C6                                          |              | CLK_ECKR       | External clock control register           | 0x00            |  |  |  |

| 0x00 50C7                                          | CLK          | CLK_SCSR       | System clock status register              | 0x01            |  |  |  |

| 0x00 50C8                                          |              | CLK_SWR        | System clock switch register              | 0x01            |  |  |  |

| 0x00 50C9                                          |              | CLK_SWCR       | Clock switch control register             | 0bxxxx0000      |  |  |  |

| 0x00 50CA                                          |              | CLK_CSSR       | Clock security system register            | 0x00            |  |  |  |

| 0x00 50CB                                          | 1            | CLK_CBEEPR     | Clock BEEP register                       | 0x00            |  |  |  |

| 0x00 50CC                                          | 1            | CLK_HSICALR    | HSI calibration register                  | 0xxx            |  |  |  |

| 0.00.5000                                          | 1            | CLK_HSITRIMR   | HSI clock calibration trimming register   | 0x00            |  |  |  |

| 0x00 50CD                                          |              |                |                                           |                 |  |  |  |

| 0x00 50CD<br>0x00 50CE                             | -            | CLK_HSIUNLCKR  | HSI unlock register                       | 0x00            |  |  |  |

| Table 9. General | hardware | register ma | ap ( | (continued) |

|------------------|----------|-------------|------|-------------|

| Address                      | Block  | Register label           | Register name               | Reset<br>status |  |  |

|------------------------------|--------|--------------------------|-----------------------------|-----------------|--|--|

| 0x00 5230                    |        | USART1_SR                | USART1 status register      | 0xC0            |  |  |

| 0x00 5231                    |        | USART1_DR                | USART1 data register        | undefined       |  |  |

| 0x00 5232                    |        | USART1_BRR1              | USART1 baud rate register 1 | 0x00            |  |  |

| 0x00 5233                    |        | USART1_BRR2              | USART1 baud rate register 2 | 0x00            |  |  |

| 0x00 5234                    |        | USART1_CR1               | USART1 control register 1   | 0x00            |  |  |

| 0x00 5235                    | USART1 | USART1_CR2               | USART1 control register 2   | 0x00            |  |  |

| 0x00 5236                    |        | USART1_CR3               | USART1 control register 3   | 0x00            |  |  |

| 0x00 5237                    |        | USART1_CR4               | USART1 control register 4   | 0x00            |  |  |

| 0x00 5238                    |        | USART1_CR5               | USART1 control register 5   | 0x00            |  |  |

| 0x00 5239                    |        | USART1_GTR               | USART1 guard time register  | 0x00            |  |  |

| 0x00 523A                    |        | USART1_PSCR              | USART1 prescaler register   | 0x00            |  |  |

| 0x00 523B<br>to<br>0x00 524F |        | Reserved area (21 bytes) |                             |                 |  |  |

|         | -         |                 |          |     |             |  |

|---------|-----------|-----------------|----------|-----|-------------|--|

| Table 9 | General   | hardware        | register | man | (continued) |  |

|         | Contortai | indi di titul c | register | map | (continued) |  |

| Address                      | Block              | Register Label | Register Name                          | Reset<br>Status |  |  |

|------------------------------|--------------------|----------------|----------------------------------------|-----------------|--|--|

| 0x00 7F00                    |                    | А              | Accumulator                            | 0x00            |  |  |

| 0x00 7F01                    |                    | PCE            | Program counter extended               | 0x00            |  |  |

| 0x00 7F02                    |                    | PCH            | Program counter high                   | 0x00            |  |  |

| 0x00 7F03                    |                    | PCL            | Program counter low                    | 0x00            |  |  |

| 0x00 7F04                    |                    | ХН             | X index register high                  | 0x00            |  |  |

| 0x00 7F05                    | CPU <sup>(1)</sup> | XL             | X index register low                   | 0x00            |  |  |

| 0x00 7F06                    |                    | YH             | Y index register high                  | 0x00            |  |  |

| 0x00 7F07                    |                    | YL             | Y index register low                   | 0x00            |  |  |

| 0x00 7F08                    |                    | SPH            | Stack pointer high                     | 0x03            |  |  |

| 0x00 7F09                    |                    | SPL            | Stack pointer low                      | 0xFF            |  |  |

| 0x00 7F0A                    |                    | CCR            | Condition code register                | 0x28            |  |  |

| 0x00 7F0B to<br>0x00 7F5F    | CPU                |                | Reserved area (85 byte)                |                 |  |  |

| 0x00 7F60                    |                    | CFG_GCR        | Global configuration register          | 0x00            |  |  |

| 0x00 7F70                    |                    | ITC_SPR1       | Interrupt Software priority register 1 | 0xFF            |  |  |

| 0x00 7F71                    |                    | ITC_SPR2       | Interrupt Software priority register 2 | 0xFF            |  |  |

| 0x00 7F72                    |                    | ITC_SPR3       | Interrupt Software priority register 3 | 0xFF            |  |  |

| 0x00 7F73                    | ITC-SPR            | ITC_SPR4       | Interrupt Software priority register 4 | 0xFF            |  |  |

| 0x00 7F74                    | IIC-SPR            | ITC_SPR5       | Interrupt Software priority register 5 | 0xFF            |  |  |

| 0x00 7F75                    |                    | ITC_SPR6       | Interrupt Software priority register 6 | 0xFF            |  |  |

| 0x00 7F76                    |                    | ITC_SPR7       | Interrupt Software priority register 7 | 0xFF            |  |  |

| 0x00 7F77                    |                    | ITC_SPR8       | Interrupt Software priority register 8 | 0xFF            |  |  |

| 0x00 7F78<br>to<br>0x00 7F79 |                    |                | Reserved area (2 byte)                 |                 |  |  |

| 0x00 7F80                    | SWIM               | SWIM_CSR       | SWIM control status register           | 0x00            |  |  |

| 0x00 7F81<br>to<br>0x00 7F8F |                    |                | Reserved area (15 byte)                |                 |  |  |

Table 10. CPU/SWIM/debug module/interrupt controller registers

# 6 Interrupt vector mapping

| IRQ<br>No. | Source<br>block                 | Description                                                                                            | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |

|------------|---------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|

| -          | RESET                           | Reset                                                                                                  | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8000         |

| -          | TRAP                            | Software interrupt                                                                                     | -                           | -                                     | -                                    | -                                                   | 0x00 8004         |

| 0          |                                 |                                                                                                        | Reserved                    |                                       |                                      |                                                     | 0x00 8008         |

| 1          | FLASH                           | FLASH end of programing/<br>write attempted to<br>protected page interrupt                             | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 800C         |

| 2          | DMA1 0/1                        | DMA1 channels 0/1 half<br>transaction/transaction<br>complete interrupt                                | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8010         |

| 3          | DMA1 2/3                        | DMA1 channels 2/3 half<br>transaction/transaction<br>complete interrupt                                | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8014         |

| 4          | RTC                             | RTC alarm A/<br>wakeup                                                                                 | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8018         |

| 5          | EXTI E/F/<br>PVD <sup>(2)</sup> | External interrupt port E/F<br>PVD interrupt                                                           | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 801C         |

| 6          | EXTIB/G                         | External interrupt port B/G                                                                            | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8020         |

| 7          | EXTID/H                         | External interrupt port D/H                                                                            | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8024         |

| 8          | EXTI0                           | External interrupt 0                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8028         |

| 9          | EXTI1                           | External interrupt 1                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 802C         |

| 10         | EXTI2                           | External interrupt 2                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8030         |

| 11         | EXTI3                           | External interrupt 3                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8034         |

| 12         | EXTI4                           | External interrupt 4                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8038         |

| 13         | EXTI5                           | External interrupt 5                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 803C         |

| 14         | EXTI6                           | External interrupt 6                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8040         |

| 15         | EXTI7                           | External interrupt 7                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8044         |

| 16         | LCD                             | LCD interrupt                                                                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8048         |

| 17         | CLK/TIM1/<br>DAC                | CLK system clock switch/<br>CSS interrupt/<br>TIM 1 break/DAC                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 804C         |

| 18         | COMP1/<br>COMP2/<br>ADC1        | COMP1 interrupt<br>COMP2 interrupt<br>ACD1 end of conversion/<br>analog watchdog/<br>overrun interrupt | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8050         |

#### Table 11. Interrupt mapping

# 7 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated memory block.

All option bytes can be modified in ICP mode (with SWIM) by accessing the EEPROM address. See *Table 12* for details on option byte addresses.

The option bytes can also be modified 'on the fly' by the application in IAP mode, except for the ROP and UBC values which can only be taken into account when they are modified in ICP mode (with the SWIM).

Refer to the STM8L15x Flash programming manual (PM0054) and STM8 SWIM and Debug Manual (UM0470) for information on SWIM programming procedures.

| Addr.     | Ontion nome                                                                  | Option        |                        | Option bits |   |                               |             | Factory default |             |         |         |

|-----------|------------------------------------------------------------------------------|---------------|------------------------|-------------|---|-------------------------------|-------------|-----------------|-------------|---------|---------|

| Addr.     | Option name                                                                  | byte<br>No.   | 7                      | 6           | 5 | 4                             | 3           | 2               | 1           | 0       | setting |

| 0x00 4800 | Read-out<br>protection<br>(ROP)                                              | OPT0          |                        | ROP[7:0]    |   |                               |             | 0xAA            |             |         |         |

| 0x00 4802 | UBC (User<br>Boot code size)                                                 | OPT1          |                        | UBC[7:0]    |   |                               |             | 0x00            |             |         |         |

| 0x00 4807 |                                                                              |               |                        | Reserved    |   |                               |             | 0x00            |             |         |         |

| 0x00 4808 | Independent<br>watchdog<br>option                                            | OPT3<br>[3:0] |                        | Reserved    |   | WWDG<br>_HALT                 | WWDG<br>_HW | IWDG<br>_HALT   | IWDG<br>_HW | 0x00    |         |

| 0x00 4809 | Number of<br>stabilization<br>clock cycles for<br>HSE and LSE<br>oscillators | OPT4          | Reserved               |             |   | Reserved LSECNT[1:0] HSECNT[1 |             |                 |             | NT[1:0] | 0x00    |

| 0x00 480A | Brownout reset<br>(BOR)                                                      | OPT5<br>[3:0] | Reserved BOR_TH BOR_ON |             |   |                               | 0x00        |                 |             |         |         |

| 0x00 480B | Bootloader                                                                   | OPTBL         | ·                      |             |   |                               | 0x00        |                 |             |         |         |

| 0x00 480C | option bytes<br>(OPTBL)                                                      | [15:0]        |                        |             |   | OF                            | PTBL[15:0   | נכ              |             |         | 0x00    |

Table 12. Option byte addresses

In the following table, data is based on characterization results, unless otherwise specified.

|                       |                                        |                                                            |                                                      |                                     |                           |              | Ν                       | lax                        |                          |             |       |       |       |

|-----------------------|----------------------------------------|------------------------------------------------------------|------------------------------------------------------|-------------------------------------|---------------------------|--------------|-------------------------|----------------------------|--------------------------|-------------|-------|-------|-------|

| Symbol                | Parameter                              |                                                            | Conditions <sup>(1)</sup>                            |                                     |                           | 55°C         | 85<br>°C <sup>(2)</sup> | 105 °C<br>(3)              | 125 °C<br>(4)            | Unit        |       |       |       |

|                       |                                        |                                                            |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.33                      | 0.39         | 0.41                    | 0.43                       | 0.45                     |             |       |       |       |

|                       |                                        |                                                            |                                                      | f <sub>CPU</sub> = 1 MHz            | 0.35                      | 0.41         | 0.44                    | 0.45                       | 0.48                     |             |       |       |       |

|                       |                                        |                                                            | HSI                                                  | f <sub>CPU</sub> = 4 MHz            | 0.42                      | 0.51         | 0.52                    | 0.54                       | 0.58                     |             |       |       |       |

|                       | CPU not<br>clocked,<br>all peripherals |                                                            | f <sub>CPU</sub> = 8 MHz                             | 0.52                                | 0.57                      | 0.58         | 0.59                    | 0.62                       |                          |             |       |       |       |

|                       |                                        |                                                            |                                                      | f <sub>CPU</sub> = 16 MHz           | 0.68                      | 0.76         | 0.79                    | 0.82<br>(7)                | 0.85<br>(7)              |             |       |       |       |

|                       |                                        | all peripherals                                            | Il peripherals<br>DFF,<br>code executed HSE external | HSE external                        | HSE external              | HSE external | HSE external            | f <sub>CPU</sub> = 125 kHz | 0.032                    | 0.056       | 0.068 | 0.072 | 0.093 |

|                       | Supply                                 | OFF, code executed                                         |                                                      |                                     |                           |              |                         | HSE external               | f <sub>CPU</sub> = 1 MHz | 0.078       | 0.121 | 0.144 | 0.163 |

| I <sub>DD(Wait)</sub> | current in<br>Wait mode                |                                                            |                                                      | f <sub>CPU</sub> = 4 MHz            | 0.218                     | 0.26         | 0.30                    | 0.36                       | 0.40                     | mA          |       |       |       |

|                       |                                        | I <sub>DDQ</sub> mode <sup>(5)</sup> ,                     | (6)                                                  | f <sub>CPU</sub> = 8 MHz            | 0.40                      | 0.52         | 0.57                    | 0.62                       | 0.66                     |             |       |       |       |

|                       | V <sub>DD</sub> from                   | V <sub>DD</sub> from<br>1.65 V to 3.6 V                    |                                                      |                                     | f <sub>CPU</sub> = 16 MHz | 0.760        | 1.01                    | 1.05                       | 1.09<br>(7)              | 1.16<br>(7) |       |       |       |

|                       |                                        |                                                            | LSI                                                  | $f_{CPU} = f_{LSI}$                 | 0.035                     | 0.044        | 0.046                   | 0.049                      | 0.054                    |             |       |       |       |

|                       |                                        | LSE <sup>(8)</sup><br>external<br>clock<br>(32.768<br>kHz) | external<br>clock<br>(32.768                         | f <sub>CPU</sub> = f <sub>LSE</sub> | 0.032                     | 0.036        | 0.038                   | 0.044                      | 0.051                    |             |       |       |       |

Table 21. Total current consumption in Wait mode

| Symbol               | Parameter | Conditions                                      |                         | Тур | Unit |

|----------------------|-----------|-------------------------------------------------|-------------------------|-----|------|

|                      |           |                                                 | V <sub>DD</sub> = 1.8 V | 48  |      |

| I <sub>DD(RST)</sub> |           | All pins are externally tied to V <sub>DD</sub> | V <sub>DD</sub> = 3 V   | 76  | μA   |

|                      |           |                                                 | V <sub>DD</sub> = 3.6 V | 91  |      |

Table 28. Current consumption under external reset

1. All pins except PA0, PB0 and PB4 are floating under reset. PA0, PB0 and PB4 are configured with pull-up under reset.

# 9.3.4 Clock and timing characteristics

## HSE external clock (HSEBYP = 1 in CLK\_ECKCR)

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol                | Parameter                                      | Conditions                 | Min                   | Тур | Мах                   | Unit |

|-----------------------|------------------------------------------------|----------------------------|-----------------------|-----|-----------------------|------|

| f <sub>HSE_ext</sub>  | External clock source frequency <sup>(1)</sup> |                            | 1                     | -   | 16                    | MHz  |

| V <sub>HSEH</sub>     | OSC_IN input pin high level voltage            | _                          | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub>       | V    |

| V <sub>HSEL</sub>     | OSC_IN input pin low level voltage             |                            | V <sub>SS</sub>       | -   | 0.3 x V <sub>DD</sub> | v    |

| C <sub>in(HSE)</sub>  | OSC_IN input<br>capacitance <sup>(1)</sup>     | -                          | -                     | 2.6 | -                     | pF   |

| I <sub>LEAK_HSE</sub> | OSC_IN input leakage<br>current                | $V_{SS} < V_{IN} < V_{DD}$ | -                     | -   | ±1                    | μΑ   |

#### Table 29. HSE external clock characteristics

1. Data guaranteed by design.

## LSE external clock (LSEBYP=1 in CLK\_ECKCR)

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

#### Table 30. LSE external clock characteristics

| Symbol                           | Parameter                                      | Min             | Тур    | Мах                   | Unit |

|----------------------------------|------------------------------------------------|-----------------|--------|-----------------------|------|

| f <sub>LSE_ext</sub>             | External clock source frequency <sup>(1)</sup> | -               | 32.768 | -                     | kHz  |

| V <sub>LSEH</sub> <sup>(2)</sup> | (2) OSC32_IN input pin high level voltage      |                 | -      | V <sub>DD</sub>       | V    |

| V <sub>LSEL</sub> <sup>(2)</sup> | OSC32_IN input pin low level voltage           | V <sub>SS</sub> | -      | 0.3 x V <sub>DD</sub> | v    |

| C <sub>in(LSE)</sub>             | OSC32_IN input capacitance <sup>(1)</sup>      | -               | 0.6    | -                     | pF   |

| I <sub>LEAK_LSE</sub>            | OSC32_IN input leakage current                 | -               | -      | ±1                    | μA   |

1. Data guaranteed by design.

2. Data based on characterization results.

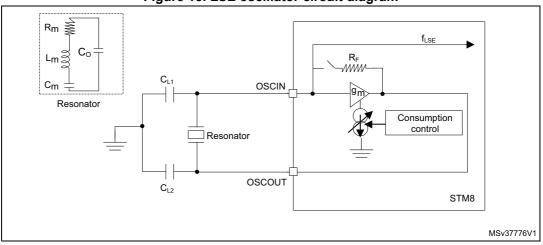

Figure 18. LSE oscillator circuit diagram

#### Internal clock sources

Subject to general operating conditions for  $V_{DD}$ , and  $T_A$ .

#### High speed internal RC oscillator (HSI)

In the following table, data is based on characterization results, not tested in production, unless otherwise specified.

| Symbol               | Parameter                               | Conditions <sup>(1)</sup>                                           | Min               | Тур | Max                | Unit |

|----------------------|-----------------------------------------|---------------------------------------------------------------------|-------------------|-----|--------------------|------|

| f <sub>HSI</sub>     | Frequency                               | V <sub>DD</sub> = 3.0 V                                             | -                 | 16  | -                  | MHz  |

|                      |                                         | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C                     | -1 <sup>(2)</sup> | -   | 1 <sup>(2)</sup>   | %    |

|                      |                                         | $V_{DD}$ = 3.0 V, 0 °C $\leq T_{A} \leq$ 55 °C                      | -1.5              | -   | 1.5                | %    |

|                      | Accuracy of HSI                         | $V_{DD}$ = 3.0 V, -10 °C $\leq T_{A} \leq$ 70 °C                    | -2                | -   | 2                  | %    |

| ACC <sub>HSI</sub>   | oscillator (factory calibrated)         | V <sub>DD</sub> = 3.0 V, -10 °C ≤T <sub>A</sub> ≤ 85 °C             | -2.5              | -   | 2                  | %    |

|                      |                                         | V <sub>DD</sub> = 3.0 V, -10 °C ≤T <sub>A</sub> ≤ 125 °C            | -4.5              | -   | 2                  | %    |

|                      |                                         | 1.65 V ≤V <sub>DD</sub> ≤ 3.6 V,<br>-40 °C ≤T <sub>A</sub> ≤ 125 °C | -4.5              | -   | 3                  | %    |

| TRIM                 | HSI user trimming                       | Trimming code ≠ multiple of 16                                      | -                 | 0.4 | 0.7                | %    |

|                      | step <sup>(3)</sup>                     | Trimming code = multiple of 16                                      | -                 |     | ± 1.5              | %    |

| t <sub>su(HSI)</sub> | HSI oscillator setup time (wakeup time) | -                                                                   | -                 | 3.7 | 6 <sup>(4)</sup>   | μs   |

| I <sub>DD(HSI)</sub> | HSI oscillator power<br>consumption     | -                                                                   | -                 | 100 | 140 <sup>(4)</sup> | μA   |

#### Table 33. HSI oscillator characteristics

1.  $V_{DD}$  = 3.0 V,  $T_A$  = -40 to 125 °C unless otherwise specified.

2. Tested in production.

The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0). Refer to the AN3101 "STM8L15x internal RC oscillator calibration" application note for more details.

4. Guaranteed by design.

## 9.3.6 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error, out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation, LCD levels, etc.).

The test results are given in the following table.

|                  |                                                        | Functional s       |                    |      |

|------------------|--------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                            | Negative injection | Positive injection | Unit |

|                  | Injected current on true open-drain pins (PC0 and PC1) |                    | +0                 |      |

| I <sub>INJ</sub> | Injected current on all five-volt tolerant (FT) pins   | -5                 | +0                 | mA   |

|                  | Injected current on all 3.6 V tolerant (TT) pins       | -5                 | +0                 |      |

|                  | Injected current on any other pin                      |                    | +5                 |      |

#### Table 37. I/O current injection susceptibility

# 9.3.7 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

# NRST pin

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                                                             | Parameter                                    | Conditions                                                       | Min                       | Тур | Max             | Unit |

|--------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------|---------------------------|-----|-----------------|------|

| V <sub>IL(NRST)</sub>                                              | NRST input low level voltage <sup>(1)</sup>  | -                                                                | V <sub>SS</sub>           | -   | 0.8             |      |

| V <sub>IH(NRST)</sub>                                              | NRST input high level voltage <sup>(1)</sup> | -                                                                | 1.4                       | -   | V <sub>DD</sub> |      |

| V <sub>OL(NRST)</sub> NRST output low level voltage <sup>(1)</sup> |                                              | $I_{OL} = 2 \text{ mA}$<br>for 2.7 V $\leq V_{DD} \leq 3.6$<br>V | -                         | -   | 0.4             | V    |

|                                                                    |                                              | I <sub>OL</sub> = 1.5 mA<br>for V <sub>DD</sub> < 2.7 V          | -                         | -   |                 |      |

| V <sub>HYST</sub>                                                  | NRST input hysteresis <sup>(3)</sup>         | -                                                                | 10%V <sub>DD</sub><br>(2) | -   | -               | mV   |

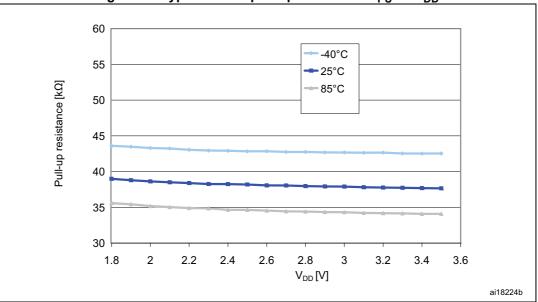

| R <sub>PU(NRST)</sub>                                              | NRST pull-up equivalent resistor             | -                                                                | 30                        | 45  | 60              | kΩ   |

| V <sub>F(NRST)</sub>                                               | NRST input filtered pulse (3)                | -                                                                | -                         | -   | 50              | ns   |

| V <sub>NF(NRST)</sub>                                              | NRST input not filtered pulse (3)            | -                                                                | 300                       | -   | -               | 115  |

|           |      | -   |                 |

|-----------|------|-----|-----------------|

| Table 42. | NRST | pin | characteristics |

1. Data based on characterization results.

2. 200 mV min.

3. Data guaranteed by design.

### Figure 31. Typical NRST pull-up resistance $R_{PU}$ vs $V_{DD}$

DocID15962 Rev 15

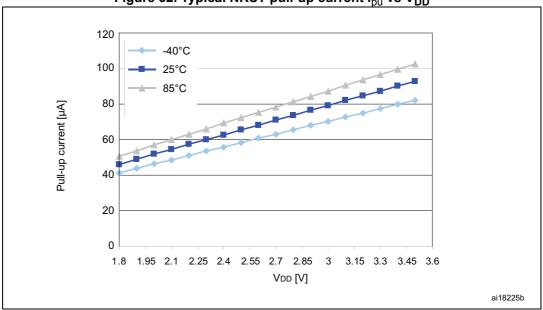

Figure 32. Typical NRST pull-up current I<sub>pu</sub> vs V<sub>DD</sub>

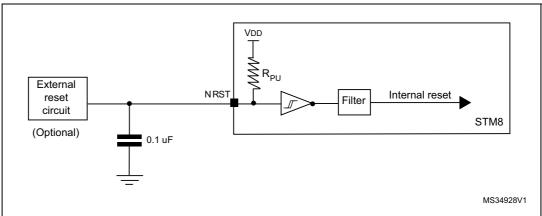

The reset network shown in *Figure 33* protects the device against parasitic resets. The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max. level specified in *Table 42*. Otherwise the reset is not taken into account internally.

For power consumption sensitive applications, the external reset capacitor value can be reduced to limit the charge/discharge current. If the NRST signal is used to reset the external circuitry, attention must be paid to the charge/discharge time of the external capacitor to fulfill the external devices reset timing conditions. The minimum recommended capacity is 10 nF.

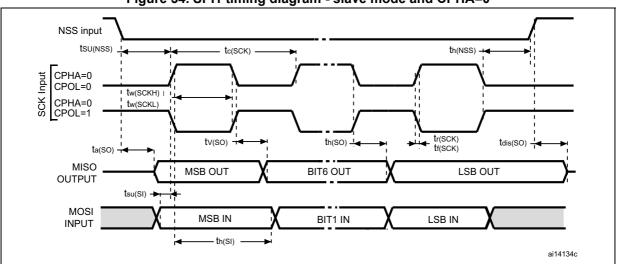

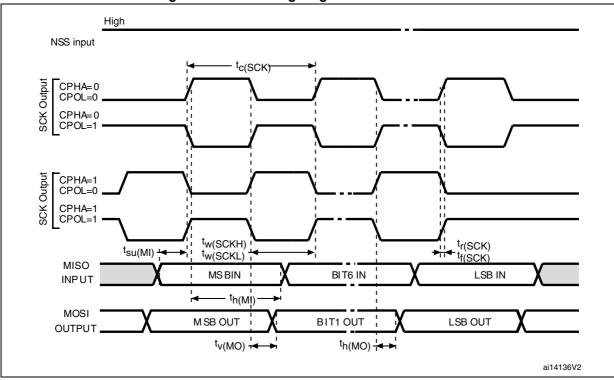

Figure 34. SPI1 timing diagram - slave mode and CPHA=0

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

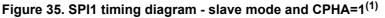

Figure 36. SPI1 timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

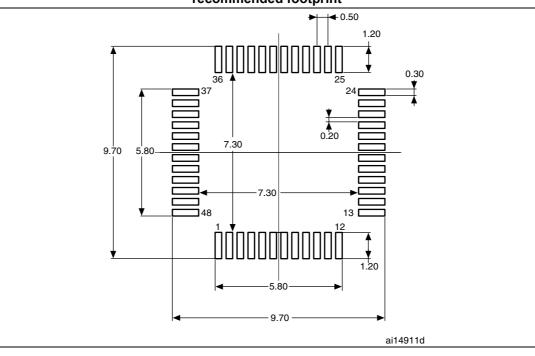

# Figure 44. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

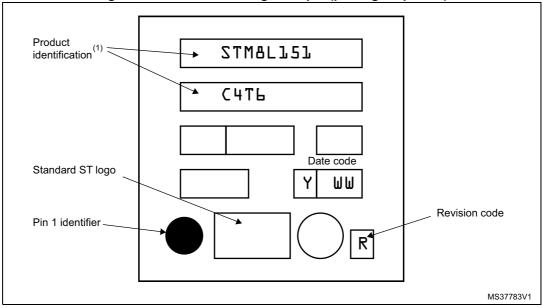

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location. Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.