Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, POR, PWM, WDT                         |

| Number of I/O              | 26                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 18x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 28-UFBGA, WLCSP                                                        |

| Supplier Device Package    | 28-WLCSP (1.7x2.84)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151g4y6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Ultra-low-power continuum

The ultra-low-power medium-densitySTM8L151x4/6 and STM8L152x4/6 devices are fully pin-to-pin, software and feature compatible. Besides the full compatibility within the family, the devices are part of STMicroelectronics microcontrollers ultra-low-power strategy which also includes STM8L101xx and STM8L15xxx. The STM8L and STM32L families allow a continuum of performance, peripherals, system architecture, and features.

They are all based on STMicroelectronics 0.13 µm ultra-low leakage process.

- Note: 1 The STM8L151xx and STM8L152xx are pin-to-pin compatible with STM8L101xx devices.

- 2 The STM32L family is pin-to-pin compatible with the general purpose STM32F family. Please refer to STM32L15x documentation for more information on these devices.

### Performance

All families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-low-power performance to range from 5 up to 33.3 DMIPs.

#### Shared peripherals

STM8L151xx/152xx and STM8L15xxx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC1, DAC, and comparators COMP1/COMP2

- Digital peripherals: RTC and some communication interfaces

### Common system strategy

To offer flexibility and optimize performance, the STM8L151xx/152xx and STM8L15xxx devices use a common architecture:

- Same power supply range from 1.8 to 3.6 V, down to 1.65 V at power down

- Architecture optimized to reach ultra-low consumption both in low power modes and Run mode

- Fast startup strategy from low power modes

- Flexible system clock

- Ultra-safe reset: same reset strategy for both STM8L15x and STM32L15xxx including power-on reset, power-down reset, brownout reset and programmable voltage detector.

#### Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 10 packages with pin count from 20 to 100 pins and size down to 3 x 3 mm

- Memory density ranging from 4 to 128 Kbyte

# 3.2 Central processing unit STM8

## 3.2.1 Advanced STM8 Core

The 8-bit STM8 core is designed for code efficiency and performance with an Harvard architecture and a 3-stage pipeline.

It contains 6 internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing, and 80 instructions.

### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16 Mbyte linear memory space

- 16-bit stack pointer access to a 64 Kbyte level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for lookup tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

#### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

## 3.2.2 Interrupt controller

The medium-density STM8L151x4/6 and STM8L152x4/6 feature a nested vectored interrupt controller:

- Nested interrupts with 3 software priority levels

- 32 interrupt vectors with hardware priority

- Up to 40 external interrupt sources on 11 vectors

- Trap and reset interrupts

| nı              | Pin<br>umb      |          |         | . Medium-density 51M                                                                         |      |           |          | Input |                |                  | utpu |    |                                |                                                                                                                                                        |  |

|-----------------|-----------------|----------|---------|----------------------------------------------------------------------------------------------|------|-----------|----------|-------|----------------|------------------|------|----|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LQFP48/UFQFPN48 | LQFP32/UFQFPN32 | UFQFPN28 | WLCSP28 | Pin name                                                                                     | Type | I/O level | floating | ndw   | Ext. interrupt | High sink/source | OD   | РР | Main function<br>(after reset) | Default alternate<br>function                                                                                                                          |  |

| 36              | 24              | -        | -       | PD7/TIM1_CH1N<br>/LCD_SEG21 <sup>(2)</sup> /<br>ADC1_IN7/RTC_ALARM/<br>VREFINT/<br>COMP1_INP | I/O  | TT<br>(3) | x        | x     | x              | HS               | x    | x  | Port D7                        | Timer 1 - inverted<br>channel 1/ LCD segment<br>21 / ADC1_IN7 / RTC<br>alarm / Internal voltage<br>reference output<br>/Comparator 1 positive<br>input |  |

| 14              | -               | -        | -       | PE0 <sup>(5)</sup> /LCD_SEG1 <sup>(2)</sup>                                                  | I/O  | FT        | Х        | Х     | Х              | HS               | Х    | Х  | Port E0                        | LCD segment 1                                                                                                                                          |  |

| 15              | -               | -        | -       | PE1/TIM1_CH2N<br>/LCD_SEG2 <sup>(2)</sup>                                                    | I/O  | TT<br>(3) | x        | x     | х              | нs               | x    | х  | Port E1                        | Timer 1 - inverted<br>channel 2 / LCD<br>segment 2                                                                                                     |  |

| 16              | -               | -        | -       | PE2/TIM1_CH3N<br>/LCD_SEG3 <sup>(2)</sup>                                                    | I/O  | TT<br>(3) | x        | x     | х              | HS               | х    | х  | Port E2                        | Timer 1 - inverted<br>channel 3 / LCD<br>segment 3                                                                                                     |  |

| 17              | -               | -        | -       | PE3/LCD_SEG4 <sup>(2)</sup>                                                                  | I/O  | TT<br>(3) | x        | х     | Х              | HS               | х    | х  | Port E3                        | LCD segment 4                                                                                                                                          |  |

| 18              | -               | -        | -       | PE4/LCD_SEG5 <sup>(2)</sup>                                                                  | I/O  | TT<br>(3) | x        | х     | Х              | HS               | х    | х  | Port E4                        | LCD segment 5                                                                                                                                          |  |

| 19              | -               | -        | -       | PE5/LCD_SEG6 <sup>(2)</sup> /<br>ADC1_IN23/COMP2_INP/<br>COMP1_INP                           | I/O  | TT<br>(3) | x        | x     | x              | HS               | x    | x  | Port E5                        | LCD segment 6 /<br>ADC1_IN23<br>/ Comparator 2 positive<br>input / Comparator 1<br>positive input                                                      |  |

| 47              | -               | -        | -       | PE6/LCD_SEG26 <sup>(2)</sup> /<br>PVD_IN                                                     | I/O  | TT<br>(3) | x        | х     | Х              | HS               | х    | х  | Port E6                        | LCD segment<br>26/PVD_IN                                                                                                                               |  |

| 48              | -               | -        | -       | PE7/LCD_SEG27 <sup>(2)</sup>                                                                 | I/O  | TT<br>(3) | x        | х     | Х              | HS               | х    | х  | Port E7                        | LCD segment 27                                                                                                                                         |  |

| 32              | -               | -        | -       | PF0/ADC1_IN24/<br>DAC_OUT                                                                    | I/O  | TT<br>(3) | x        | х     | Х              | HS               | х    | х  | Port F0                        | ADC1_IN24 / DAC_OUT                                                                                                                                    |  |

| 13              | 9               | -        | -       | VLCD <sup>(2)</sup>                                                                          | S    | -         | -        | -     | -              | -                | -    | -  | LCD booster external capacitor |                                                                                                                                                        |  |

| 13              | -               | -        | -       | Reserved <sup>(8)</sup>                                                                      | -    | -         | -        | -     | -              | -                | -    | -  | Reserved                       | d. Must be tied to V <sub>DD</sub>                                                                                                                     |  |

| 10              | -               | -        | -       | V <sub>DD</sub>                                                                              | S    | -         | -        | -     | -              | -                | -    | -  | Digital po                     | wer supply                                                                                                                                             |  |

| 11              | -               | -        | -       | V <sub>DDA</sub>                                                                             | S    | -         | -        | -     | -              | -                | -    | -  | Analog sı                      | upply voltage                                                                                                                                          |  |

| 12              | -               | -        | -       | V <sub>REF+</sub>                                                                            | S    | -         | -        | -     | -              | -                | -    | -  | ADC1 an reference              | d DAC positive voltage                                                                                                                                 |  |

## Table 5. Medium-density STM8L151x4/6, STM8L152x4/6 pin description (continued)

# 4.1 System configuration options

As shown in *Table 5: Medium-density STM8L151x4/6, STM8L152x4/6 pin description*, some alternate functions can be remapped on different I/O ports by programming one of the two remapping registers described in the "Routing interface (RI) and system configuration controller" section in the STM8L15xxx and STM8L16xxx reference manual (RM0031).

| Address                      | Block  | Register label                   | Register name                       | Reset  |

|------------------------------|--------|----------------------------------|-------------------------------------|--------|

| Audress                      | BIOCK  | Register laber                   |                                     | status |

| 0x00 5200                    |        | SPI1_CR1                         | SPI1 control register 1             | 0x00   |

| 0x00 5201                    | ]      | SPI1_CR2                         | SPI1 control register 2             | 0x00   |

| 0x00 5202                    | ]      | SPI1_ICR                         | SPI1 interrupt control register     | 0x00   |

| 0x00 5203                    | SPI1   | SPI1_SR                          | SPI1 status register                | 0x02   |

| 0x00 5204                    | - 3511 | SPI1_DR                          | SPI1 data register                  | 0x00   |

| 0x00 5205                    |        | SPI1_CRCPR                       | SPI1 CRC polynomial register        | 0x07   |

| 0x00 5206                    |        | SPI1_RXCRCR SPI1 Rx CRC register |                                     | 0x00   |

| 0x00 5207                    |        | SPI1_TXCRCR                      | SPI1 Tx CRC register                | 0x00   |

| 0x00 5208<br>to<br>0x00 520F |        | I                                | Reserved area (8 bytes)             |        |

| 0x00 5210                    |        | I2C1_CR1                         | I2C1 control register 1             | 0x00   |

| 0x00 5211                    |        | I2C1_CR2                         | I2C1 control register 2             | 0x00   |

| 0x00 5212                    |        | I2C1_FREQR                       | I2C1 frequency register             | 0x00   |

| 0x00 5213                    |        | I2C1_OARL                        | I2C1 own address register low       | 0x00   |

| 0x00 5214                    |        | I2C1_OARH                        | I2C1 own address register high      | 0x00   |

| 0x00 5215                    |        |                                  | Reserved (1 byte)                   |        |

| 0x00 5216                    |        | I2C1_DR                          | I2C1 data register                  | 0x00   |

| 0x00 5217                    | I2C1   | I2C1_SR1                         | I2C1 status register 1              | 0x00   |

| 0x00 5218                    |        | I2C1_SR2                         | I2C1 status register 2              | 0x00   |

| 0x00 5219                    |        | I2C1_SR3                         | I2C1 status register 3              | 0x0x   |

| 0x00 521A                    |        | I2C1_ITR                         | I2C1 interrupt control register     | 0x00   |

| 0x00 521B                    | ]      | I2C1_CCRL                        | I2C1 clock control register low     | 0x00   |

| 0x00 521C                    | ]      | I2C1_CCRH                        | I2C1 clock control register high    | 0x00   |

| 0x00 521D                    | 1      | I2C1_TRISER                      | I2C1 TRISE register                 | 0x02   |

| 0x00 521E                    | 1      | I2C1_PECR                        | I2C1 packet error checking register | 0x00   |

| 0x00 521F<br>to<br>0x00 522F |        | ٦<br>٦                           | Reserved area (17 bytes)            |        |

|                  | h                   |                |

|------------------|---------------------|----------------|

| Table 9. General | hardware register m | ap (continued) |

| IRQ<br>No. | Source<br>block   | Description                                                                                               | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |  |  |  |  |

|------------|-------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|--|--|--|--|

| 19         | TIM2              | TIM2 update/overflow/<br>trigger/break interrupt                                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8054         |  |  |  |  |

| 20         | TIM2              | TIM2 capture/<br>compare interrupt                                                                        | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8058         |  |  |  |  |

| 21         | TIM3              | TIM3 update/overflow/<br>trigger/break interrupt                                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 805C         |  |  |  |  |

| 22         | TIM3              | TIM3 capture/<br>compare interrupt                                                                        | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8060         |  |  |  |  |

| 23         | TIM1              | Update /overflow/trigger/<br>COM                                                                          | -                           | -                                     | -                                    | Yes                                                 | 0x00 8064         |  |  |  |  |

| 24         | TIM1              | Capture/compare                                                                                           | -                           | -                                     | -                                    | Yes                                                 | 0x00 8068         |  |  |  |  |

| 25         | TIM4              | TIM4 update/overflow/<br>trigger interrupt                                                                | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 806C         |  |  |  |  |

| 26         | SPI1              | SPI1 TX buffer empty/<br>RX buffer not empty/<br>error/wakeup interrupt                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8070         |  |  |  |  |

| 27         | USART1            | USART1 transmit data<br>register empty/<br>transmission complete<br>interrupt                             | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8074         |  |  |  |  |

| 28         | USART1            | USART1 received data<br>ready/overrun error/<br>idle line detected/parity<br>error/global error interrupt | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8078         |  |  |  |  |

| 29         | l <sup>2</sup> C1 | I <sup>2</sup> C1 interrupt <sup>(3)</sup>                                                                | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 807C         |  |  |  |  |

Table 11. Interrupt mapping (continued)

The Low power wait mode is entered when executing a WFE instruction in Low power run mode. In WFE mode, the

interrupt is served if it has been previously enabled. After processing the interrupt, the processor goes back to WFE mode.

When the interrupt is configured as a wakeup event, the CPU wakes up and resumes processing.

2. The interrupt from PVD is logically OR-ed with Port E and F interrupts. Register EXTI\_CONF allows to select between Port E and Port F interrupt (see *External interrupt port select register (EXTI\_CONF)* in the RM0031).

3. The device is woken up from Halt or Active-halt mode only when the address received matches the interface address.

# 8 Unique ID

STM8 devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory.

- To activate secure boot processes

| Addrooo | Content          |                            |            |             | Uniq | ue ID bits | 6 |   |   |  |

|---------|------------------|----------------------------|------------|-------------|------|------------|---|---|---|--|

| Address | description      | 7                          | 6          | 5           | 4    | 3          | 2 | 1 | 0 |  |

| 0x4926  | X co-ordinate on |                            |            |             | U_   | _ID[7:0]   |   |   |   |  |

| 0x4927  | the wafer        |                            | U_ID[15:8] |             |      |            |   |   |   |  |

| 0x4928  | Y co-ordinate on |                            |            |             | U_I  | D[23:16]   |   |   |   |  |

| 0x4929  | the wafer        |                            |            | U_ID[31:24] |      |            |   |   |   |  |

| 0x492A  | Wafer number     | U_ID[39:32]                |            |             |      |            |   |   |   |  |

| 0x492B  |                  |                            |            |             | U_I  | D[47:40]   |   |   |   |  |

| 0x492C  |                  |                            |            |             | U_I  | D[55:48]   |   |   |   |  |

| 0x492D  |                  |                            |            |             | U_I  | D[63:56]   |   |   |   |  |

| 0x492E  | Lot number       |                            |            |             | U_I  | D[71:64]   |   |   |   |  |

| 0x492F  |                  |                            |            |             | U_I  | D[79:72]   |   |   |   |  |

| 0x4930  |                  | U_ID[87:80]<br>U_ID[95:88] |            |             |      |            |   |   |   |  |

| 0x4931  |                  |                            |            |             |      |            |   |   |   |  |

#### Table 14. Unique ID registers (96 bits)

# 9 Electrical parameters

## 9.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

## 9.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A$ = 25 °C and  $T_A$  =  $T_A$  max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics is indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 9.1.2 Typical values

Unless otherwise specified, typical data is based on  $T_A = 25$  °C,  $V_{DD} = 3$  V. It is given only as design guidelines and is not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

## 9.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 9.1.4 Loading capacitor

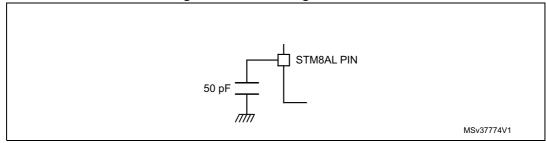

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

In the following table, data is based on characterization results, unless otherwise specified.

|                       |                                   | Conditions <sup>(1)</sup>                                                                    |                                                                       |                                     | Мах   |                         |               |               |             |    |

|-----------------------|-----------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------|-------|-------------------------|---------------|---------------|-------------|----|

| Symbol                | Parameter                         |                                                                                              |                                                                       | Тур                                 | 55°C  | 85<br>°C <sup>(2)</sup> | 105 °C<br>(3) | 125 °C<br>(4) | Unit        |    |

|                       |                                   |                                                                                              |                                                                       | f <sub>CPU</sub> = 125 kHz          | 0.33  | 0.39                    | 0.41          | 0.43          | 0.45        |    |

|                       |                                   |                                                                                              |                                                                       | f <sub>CPU</sub> = 1 MHz            | 0.35  | 0.41                    | 0.44          | 0.45          | 0.48        |    |

|                       |                                   |                                                                                              | HSI                                                                   | f <sub>CPU</sub> = 4 MHz            | 0.42  | 0.51                    | 0.52          | 0.54          | 0.58        |    |

|                       |                                   |                                                                                              |                                                                       | f <sub>CPU</sub> = 8 MHz            | 0.52  | 0.57                    | 0.58          | 0.59          | 0.62        |    |

|                       |                                   | CPU not<br>clocked,<br>all peripherals<br>OFF,<br>code executed<br>from RAM<br>with Flash in |                                                                       | f <sub>CPU</sub> = 16 MHz           | 0.68  | 0.76                    | 0.79          | 0.82<br>(7)   | 0.85<br>(7) | mA |

|                       |                                   |                                                                                              | HSE external<br>clock<br>(f <sub>CPU</sub> =f <sub>HSE</sub> )<br>(6) | f <sub>CPU</sub> = 125 kHz          | 0.032 | 0.056                   | 0.068         | 0.072         | 0.093       |    |

|                       | Supply<br>current in<br>Wait mode |                                                                                              |                                                                       | f <sub>CPU</sub> = 1 MHz            | 0.078 | 0.121                   | 0.144         | 0.163         | 0.197       |    |

| I <sub>DD(Wait)</sub> |                                   |                                                                                              |                                                                       | f <sub>CPU</sub> = 4 MHz            | 0.218 | 0.26                    | 0.30          | 0.36          | 0.40        |    |

|                       |                                   | I <sub>DDQ</sub> mode <sup>(5)</sup> ,                                                       |                                                                       | f <sub>CPU</sub> = 8 MHz            | 0.40  | 0.52                    | 0.57          | 0.62          | 0.66        |    |

|                       |                                   | V <sub>DD</sub> from<br>1.65 V to 3.6 V                                                      |                                                                       | f <sub>CPU</sub> = 16 MHz           | 0.760 | 1.01                    | 1.05          | 1.09<br>(7)   | 1.16<br>(7) |    |

|                       |                                   |                                                                                              | LSI                                                                   | $f_{CPU} = f_{LSI}$                 | 0.035 | 0.044                   | 0.046         | 0.049         | 0.054       |    |

|                       |                                   |                                                                                              | LSE <sup>(8)</sup><br>external<br>clock<br>(32.768<br>kHz)            | f <sub>CPU</sub> = f <sub>LSE</sub> | 0.032 | 0.036                   | 0.038         | 0.044         | 0.051       |    |

Table 21. Total current consumption in Wait mode

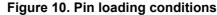

Figure 14. Typ. I<sub>DD(Wait)</sub> vs. V<sub>DD</sub>,  $f_{CPU}$  = 16 MHz <sup>1)</sup>

1. Typical current consumption measured with code executed from Flash memory.

| Symbol                                        | Parameter                                                                    |                     | Conditio                          | ns <sup>(1)</sup>                        | Тур  | Max  | Unit |

|-----------------------------------------------|------------------------------------------------------------------------------|---------------------|-----------------------------------|------------------------------------------|------|------|------|

|                                               |                                                                              |                     |                                   | $T_A$ = -40 °C to 25 °C                  | 0.5  | 1.2  |      |

|                                               |                                                                              |                     |                                   | T <sub>A</sub> = 55 °C                   | 0.62 | 1.4  |      |

|                                               |                                                                              |                     | LCD OFF <sup>(7)</sup>            | T <sub>A</sub> = 85 °C                   | 0.88 | 2.1  |      |

|                                               |                                                                              |                     |                                   | T <sub>A</sub> = 105 °C                  | 2.1  | 4.85 |      |

|                                               |                                                                              |                     |                                   | T <sub>A</sub> = 125 °C                  | 4.8  | 11   |      |

|                                               |                                                                              |                     |                                   | $T_A = -40 \degree C$ to 25 $\degree C$  | 0.85 | 1.9  |      |

|                                               |                                                                              |                     | LCD ON<br>(static duty/           | T <sub>A</sub> = 55 °C                   | 0.95 | 2.2  |      |

|                                               |                                                                              |                     | external                          | T <sub>A</sub> = 85 °C                   | 1.3  | 3.2  |      |

|                                               |                                                                              | LSE external        | V <sub>LCD</sub> ) <sup>(3)</sup> | T <sub>A</sub> = 105 °C                  | 2.3  | 5.3  |      |

| I                                             | Supply current in                                                            | clock               |                                   | T <sub>A</sub> = 125 °C                  | 5.0  | 12   |      |

| I <sub>DD(AH)</sub>                           | Active-halt mode                                                             | (32.768 kHz)<br>(6) | LCD ON<br>(1/4 duty/<br>external  | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 1.5  | 2.5  | μΑ   |

|                                               |                                                                              |                     |                                   | T <sub>A</sub> = 55 °C                   | 1.6  | 3.8  |      |

|                                               |                                                                              |                     |                                   | T <sub>A</sub> = 85 °C                   | 1.8  | 4.2  |      |

|                                               |                                                                              |                     | V <sub>LCD</sub> ) <sup>(4)</sup> | T <sub>A</sub> = 105 °C                  | 2.9  | 7.0  |      |

|                                               |                                                                              |                     |                                   | T <sub>A</sub> = 125 °C                  | 5.7  | 14   |      |

|                                               |                                                                              |                     | LCD ON<br>(1/4 duty/<br>internal  | $T_A = -40 \degree C$ to 25 $\degree C$  | 3.4  | 7.6  |      |

|                                               |                                                                              |                     |                                   | T <sub>A</sub> = 55 °C                   | 3.7  | 8.3  |      |

|                                               |                                                                              |                     |                                   | T <sub>A</sub> = 85 °C                   | 3.9  | 9.2  |      |

|                                               |                                                                              |                     | V <sub>LCD</sub> ) <sup>(5)</sup> | T <sub>A</sub> = 105 °C                  | 5.0  | 14.5 |      |

|                                               |                                                                              |                     |                                   | T <sub>A</sub> = 125 °C                  | 6.3  | 15.2 |      |

| I <sub>DD(WUFAH)</sub>                        | Supply current during<br>wakeup time from<br>Active-halt mode<br>(using HSI) |                     |                                   | -                                        | 2.4  | -    | mA   |

| t <sub>WU_HSI(AH)</sub> <sup>(8)(9)</sup>     | Wakeup time from<br>Active-halt mode to<br>Run mode (using HSI)              |                     |                                   | -                                        | 4.7  | 7    | μs   |

| t <sub>WU_LSI(AH)</sub> <sup>(8)</sup><br>(9) | Wakeup time from<br>Active-halt mode to<br>Run mode (using LSI)              | -                   | -                                 | -                                        | 150  | -    | μs   |

### Table 24. Total current consumption and timing in Active-halt mode at $V_{DD}$ = 1.65 V to 3.6 V

1. No floating I/O, unless otherwise specified.

2. RTC enabled. Clock source = LSI

3. RTC enabled, LCD enabled with external V<sub>LCD</sub> = 3 V, static duty, division ratio = 256, all pixels active, no LCD connected.

4. RTC enabled, LCD enabled with external  $V_{LCD}$ , 1/4 duty, 1/3 bias, division ratio = 64, all pixels active, no LCD connected.

LCD enabled with internal LCD booster V<sub>LCD</sub> = 3 V, 1/4 duty, 1/3 bias, division ratio = 64, all pixels active, no LCD connected.

Oscillator bypassed (LSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the LSE consumption (I<sub>DD LSE</sub>) must be added. Refer to *Table 32*.

7. RTC enabled. Clock source = LSE.

8. Wakeup time until start of interrupt vector fetch.

The first word of interrupt routine is fetched 4 CPU cycles after  $t_{WU}$ .

9. ULP=0 or ULP=1 and FWU=1 in the PWR\_CSR2 register.

DocID15962 Rev 15

| Symbol               | Parameter | Condition                                       | Тур                     | Unit |    |

|----------------------|-----------|-------------------------------------------------|-------------------------|------|----|

|                      |           |                                                 | V <sub>DD</sub> = 1.8 V | 48   |    |

| I <sub>DD(RST)</sub> |           | All pins are externally tied to V <sub>DD</sub> | V <sub>DD</sub> = 3 V   | 76   | μA |

|                      |           |                                                 | V <sub>DD</sub> = 3.6 V | 91   |    |

Table 28. Current consumption under external reset

1. All pins except PA0, PB0 and PB4 are floating under reset. PA0, PB0 and PB4 are configured with pull-up under reset.

## 9.3.4 Clock and timing characteristics

## HSE external clock (HSEBYP = 1 in CLK\_ECKCR)

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Symbol                | Parameter                                      | Conditions                 | Min                   | Тур | Мах                   | Unit |  |

|-----------------------|------------------------------------------------|----------------------------|-----------------------|-----|-----------------------|------|--|

| f <sub>HSE_ext</sub>  | External clock source frequency <sup>(1)</sup> |                            | 1                     | -   | 16                    | MHz  |  |

| V <sub>HSEH</sub>     | OSC_IN input pin high level voltage            | _                          | 0.7 x V <sub>DD</sub> | -   | V <sub>DD</sub>       | V    |  |

| V <sub>HSEL</sub>     | OSC_IN input pin low level voltage             |                            | V <sub>SS</sub>       | -   | 0.3 x V <sub>DD</sub> | v    |  |

| C <sub>in(HSE)</sub>  | OSC_IN input<br>capacitance <sup>(1)</sup>     | -                          | -                     | 2.6 | -                     | pF   |  |

| I <sub>LEAK_HSE</sub> | OSC_IN input leakage<br>current                | $V_{SS} < V_{IN} < V_{DD}$ | -                     | -   | ±1                    | μΑ   |  |

### Table 29. HSE external clock characteristics

1. Data guaranteed by design.

## LSE external clock (LSEBYP=1 in CLK\_ECKCR)

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

#### Table 30. LSE external clock characteristics

| Symbol                           | Parameter                                      | Min                   | Тур    | Мах                   | Unit |

|----------------------------------|------------------------------------------------|-----------------------|--------|-----------------------|------|

| f <sub>LSE_ext</sub>             | External clock source frequency <sup>(1)</sup> | -                     | 32.768 | -                     | kHz  |

| V <sub>LSEH</sub> <sup>(2)</sup> | OSC32_IN input pin high level voltage          | 0.7 x V <sub>DD</sub> | -      | V <sub>DD</sub>       | V    |

| V <sub>LSEL</sub> <sup>(2)</sup> | OSC32_IN input pin low level voltage           | V <sub>SS</sub>       | -      | 0.3 x V <sub>DD</sub> | v    |

| C <sub>in(LSE)</sub>             | OSC32_IN input capacitance <sup>(1)</sup>      | -                     | 0.6    | -                     | pF   |

| I <sub>LEAK_LSE</sub>            | OSC32_IN input leakage current                 | -                     | -      | ±1                    | μΑ   |

1. Data guaranteed by design.

2. Data based on characterization results.

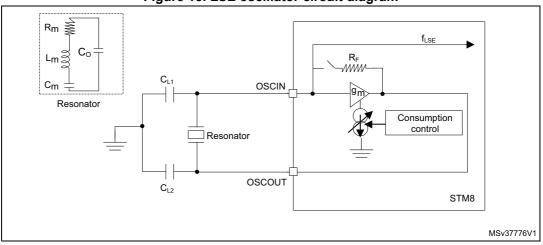

Figure 18. LSE oscillator circuit diagram

#### Internal clock sources

Subject to general operating conditions for  $V_{DD}$ , and  $T_A$ .

#### High speed internal RC oscillator (HSI)

In the following table, data is based on characterization results, not tested in production, unless otherwise specified.

| Symbol               | Parameter                               | Conditions <sup>(1)</sup>                                           | Min               | Тур | Max                | Unit |

|----------------------|-----------------------------------------|---------------------------------------------------------------------|-------------------|-----|--------------------|------|

| f <sub>HSI</sub>     | Frequency                               | V <sub>DD</sub> = 3.0 V                                             | -                 | 16  | -                  | MHz  |

|                      |                                         | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 25 °C                     | -1 <sup>(2)</sup> | -   | 1 <sup>(2)</sup>   | %    |

| ACC <sub>HSI</sub>   |                                         | $V_{DD}$ = 3.0 V, 0 °C $\leq T_{A} \leq$ 55 °C                      | -1.5              | -   | 1.5                | %    |

|                      | Accuracy of HSI                         | $V_{DD}$ = 3.0 V, -10 °C $\leq T_{A} \leq$ 70 °C                    | -2                | -   | 2                  | %    |

|                      | oscillator (factory calibrated)         | $V_{DD}$ = 3.0 V, -10 °C $\leq T_A \leq 85$ °C                      | -2.5              | -   | 2                  | %    |

|                      |                                         | V <sub>DD</sub> = 3.0 V, -10 °C ≤T <sub>A</sub> ≤ 125 °C            | -4.5              | -   | 2                  | %    |

|                      |                                         | 1.65 V ≤V <sub>DD</sub> ≤ 3.6 V,<br>-40 °C ≤T <sub>A</sub> ≤ 125 °C | -4.5              | -   | 3                  | %    |

| f <sub>HSI</sub>     | HSI user trimming                       | Trimming code ≠ multiple of 16                                      | -                 | 0.4 | 0.7                | %    |

|                      | step <sup>(3)</sup>                     | Trimming code = multiple of 16                                      | -                 |     | ± 1.5              | %    |

| t <sub>su(HSI)</sub> | HSI oscillator setup time (wakeup time) | -                                                                   | -                 | 3.7 | 6 <sup>(4)</sup>   | μs   |

| I <sub>DD(HSI)</sub> | HSI oscillator power<br>consumption     | -                                                                   | -                 | 100 | 140 <sup>(4)</sup> | μA   |

#### Table 33. HSI oscillator characteristics

1.  $V_{DD}$  = 3.0 V,  $T_A$  = -40 to 125 °C unless otherwise specified.

2. Tested in production.

The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0). Refer to the AN3101 "STM8L15x internal RC oscillator calibration" application note for more details.

4. Guaranteed by design.

## NRST pin

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                | Parameter                                    | Conditions                                                       | Min                       | Тур | Max             | Unit |  |

|-----------------------|----------------------------------------------|------------------------------------------------------------------|---------------------------|-----|-----------------|------|--|

| V <sub>IL(NRST)</sub> | NRST input low level voltage <sup>(1)</sup>  | -                                                                | V <sub>SS</sub>           | -   | 0.8             |      |  |

| V <sub>IH(NRST)</sub> | NRST input high level voltage <sup>(1)</sup> | -                                                                | 1.4                       | -   | V <sub>DD</sub> |      |  |

| V <sub>OL(NRST)</sub> | NRST output low level voltage <sup>(1)</sup> | $I_{OL} = 2 \text{ mA}$<br>for 2.7 V $\leq V_{DD} \leq 3.6$<br>V | -                         | -   | 0.4             | V    |  |

|                       |                                              | I <sub>OL</sub> = 1.5 mA<br>for V <sub>DD</sub> < 2.7 V          | -                         | -   |                 |      |  |

| V <sub>HYST</sub>     | NRST input hysteresis <sup>(3)</sup>         | -                                                                | 10%V <sub>DD</sub><br>(2) | -   | -               | mV   |  |

| R <sub>PU(NRST)</sub> | NRST pull-up equivalent resistor             | -                                                                | 30                        | 45  | 60              | kΩ   |  |

| V <sub>F(NRST)</sub>  | NRST input filtered pulse (3)                | -                                                                | -                         | -   | 50              | 20   |  |

| V <sub>NF(NRST)</sub> | NRST input not filtered pulse (3)            | -                                                                | 300                       | -   | -               | - ns |  |

|           |      | -   |                 |

|-----------|------|-----|-----------------|

| Table 42. | NRST | pin | characteristics |

1. Data based on characterization results.

2. 200 mV min.

3. Data guaranteed by design.

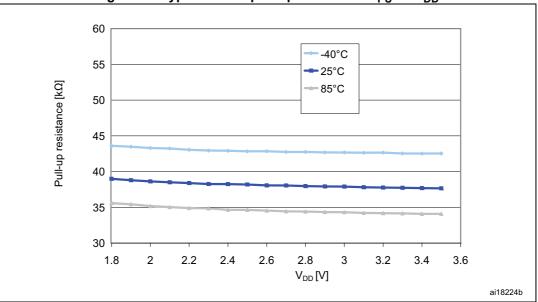

## Figure 31. Typical NRST pull-up resistance $R_{PU}$ vs $V_{DD}$

DocID15962 Rev 15

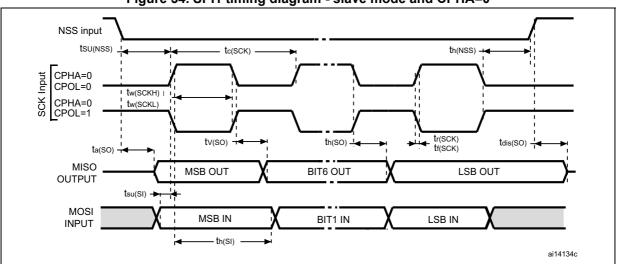

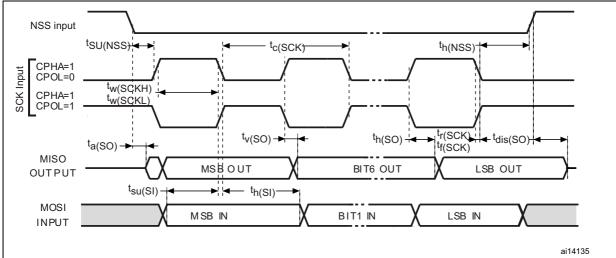

Figure 34. SPI1 timing diagram - slave mode and CPHA=0

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

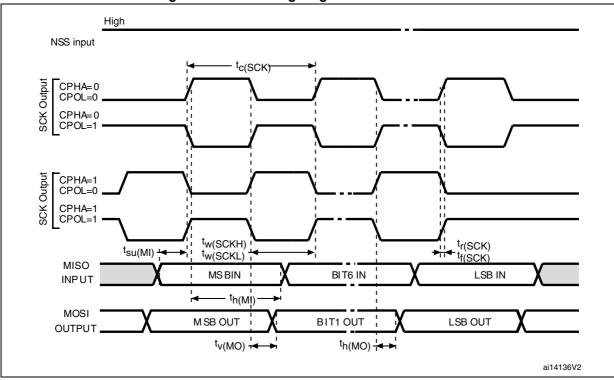

Figure 36. SPI1 timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

## 9.3.13 12-bit DAC characteristics

In the following table, data is guaranteed by design, not tested in production.

| Symbol                | Parameter                                                                                                                                                             | Conditions                                                    | Min | Тур | Max                      | Unit |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|-----|--------------------------|------|

| V <sub>DDA</sub>      | Analog supply voltage                                                                                                                                                 | -                                                             | 1.8 | -   | 3.6                      | V    |

| V <sub>REF+</sub>     | Reference supply voltage                                                                                                                                              | -                                                             | 1.8 | -   | V <sub>DDA</sub>         |      |

| I <sub>VREF</sub>     | Current consumption on V <sub>REF+</sub> supply                                                                                                                       | V <sub>REF+</sub> = 3.3 V, no<br>load, middle code<br>(0x800) | -   | 130 | 220                      |      |

|                       |                                                                                                                                                                       | V <sub>REF+</sub> = 3.3 V, no<br>load, worst code<br>(0x000)  | -   | 220 | 350                      | μA   |

| I <sub>VDDA</sub>     | Current consumption on V <sub>DDA</sub> supply                                                                                                                        | V <sub>DDA</sub> = 3.3 V, no load,<br>middle code (0x800)     | -   | 210 | 320                      |      |

|                       |                                                                                                                                                                       | V <sub>DDA</sub> = 3.3 V, no load,<br>worst code (0x000)      | -   | 320 | 520                      |      |

| Τ <sub>Α</sub>        | Temperature range                                                                                                                                                     | -                                                             | -40 | -   | 125                      | °C   |

| R <sub>L</sub>        | Resistive load <sup>(1) (2)</sup>                                                                                                                                     | DACOUT buffer ON                                              | 5   | -   | -                        | kΩ   |

| R <sub>O</sub>        | Output impedance                                                                                                                                                      | DACOUT buffer OFF                                             | -   | 8   | 10                       | kΩ   |

| CL                    | Capacitive load <sup>(3)</sup>                                                                                                                                        | -                                                             | -   | -   | 50                       | pF   |

|                       | DAC_OUT voltage <sup>(4)</sup>                                                                                                                                        | DACOUT buffer ON                                              | 0.2 | -   | V <sub>DDA</sub> -0.2    | V    |

| DAC_OUT               |                                                                                                                                                                       | DACOUT buffer OFF                                             | 0   | -   | V <sub>REF+</sub> -1 LSB | V    |

| t <sub>settling</sub> | Settling time (full scale: for a 12-<br>bit input code transition between<br>the lowest and the highest input<br>codes when DAC_OUT reaches<br>the final value ±1LSB) | R <sub>L</sub> ≥5 kΩ, C <sub>L</sub> ≤ 50 pF                  | -   | 7   | 12                       | μs   |

| Update rate           | Max frequency for a correct<br>DAC_OUT (@95%) change<br>when small variation of the input<br>code (from code i to i+1LSB).                                            | R <sub>L</sub> ≥ 5 kΩ, C <sub>L</sub> ≤50 pF                  | -   |     | 1                        | Msps |

| t <sub>WAKEUP</sub>   | Wakeup time from OFF state.<br>Input code between lowest and<br>highest possible codes.                                                                               | R <sub>L</sub> ≥5 kΩ, C <sub>L</sub> ≤50 pF                   | -   | 9   | 15                       | μs   |

| PSRR+                 | Power supply rejection ratio (to VDDA) (static DC measurement)                                                                                                        | R <sub>L</sub> ≥ 5 kΩ, C <sub>L</sub> ≤50 pF                  | -   | -60 | -35                      | dB   |

Table 50. DAC characteristics

1. Resistive load between DACOUT and GNDA.

2. Output on PF0 (48-pin package only).

3. Capacitive load at DACOUT pin.

4. It gives the output excursion of the DAC.

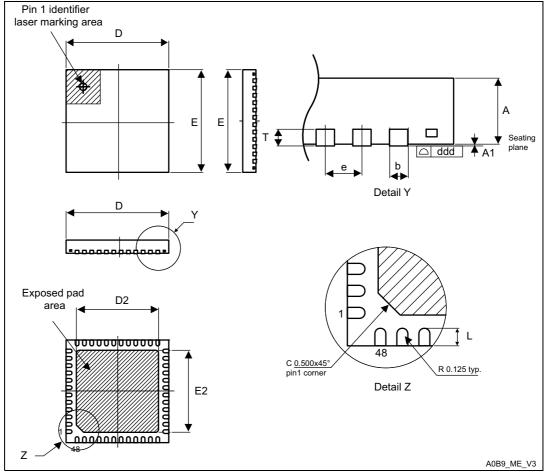

# 10.3 UFQFPN48 package information

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 23-Jul-2010 | 5        | Modified Introduction and Description.         Modified Table: Legend/abbreviation for table 5 and         Table: Medium density STM8L15x pin description (for         PA0, PA1, PB0 and PB4 and for reset states in the         floating input column)         Modified Figure: Low density STM8L151xx device block         diagram, Figure: Low density STM8L151xx device block         diagram, Figure: Low power modes and Figure : Low         power real-time clock.         Modified CLK_PCKENR2 and CLK_HSICALR reset         values in Table: General hardware register map.         Modified notes below Figure: Memory map.         Modified Table: Voltage characteristics and Table:         Current characteristics.         Modified Table: Voltage characteristics and Table:         Current characteristics.         Modified Table: Total current consumption in Wait mode.         Modified Figure Typical application with I2C bus and         timing diagram 1).         Modified R <sub>H</sub> and R <sub>L</sub> in Table: LCD characteristics.         Added graphs in Section: Electrical parameters.         Modified note 3 below Table: Reference voltage         characteristics.         Modified note 1 below Table: TS characteristics.         Changed V <sub>ESD(CDM)</sub> value in Table: ESD absolute         maximum ratings.         Updated notes for UFQFPN32 and UFQFPN48 |  |

| 11-Mar-2011 | 6        | Modified note on true open drain I/Os and I/O level<br>columns in <i>Table: Medium density STM8L15x pin</i><br><i>description.</i><br>Remapping option removed for USART1_TX,<br>USART1_RX, and USART1_CK on PC2, PC3 and PC4<br>in <i>Table: Medium density STM8L15x pin description.</i><br>Modified IDWDG_KR reset value in <i>Table: General</i><br><i>hardware register map.</i><br>Replaced VREF_OUT with VREFINT and TIMx_TRIG<br>with TIMx_ETR.<br>Added <i>Table: Factory conversion registers.</i> Modified<br>reset values for TIM1_DCR1, IWDG_KR, RTC_DR1,<br>RTC_APRER, RTC_WUTRH, and RTC_WUTRL in<br><i>Table: General hardware register map.</i><br>Added notes to certain values in <i>Section: Embedded</i><br><i>reference voltage</i> and <i>Section: Temperature sensor.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Apr-2015 | 14       | <ul> <li>Added:</li> <li>Figure 45: LQFP48 marking example (package top view),</li> <li>Figure 48: UFQFPN48 marking example (package top view),</li> <li>Figure 51: LQFP32 marking example (package top view),</li> <li>Figure 54: UFQFPN32 marking example (package top view),</li> <li>Figure 57: UFQFPN28 marking example (package top view),</li> <li>Figure 59: WLCSP28 marking example (package top view).</li> </ul>                                                                                                                                                                                                                            |

| 07-Apr-2017 | 15       | Changed symbol $V_{125}$ to $V_{90}$ in <i>Table 47: TS</i><br>characteristics and updated related Min/Typ/Max values.<br>Updated Section 9.2: Absolute maximum ratings.<br>Updated table notes for <i>Table 30</i> , <i>Table 31</i> , <i>Table 32</i> ,<br><i>Table 33</i> , <i>Table 34</i> , <i>Table 36</i> , <i>Table 38</i> , <i>Table 42</i> ,<br><i>Table 43</i> , <i>Table 46</i> , <i>Table 47</i> , <i>Table 48</i> , <i>Table 49</i> ,<br><i>Table 53</i> , <i>Table 57</i> , and <i>Table 60</i> . Updated device<br>marking paragraphs in Section 10.2, Section 10.3,<br>Section 10.4, Section 10.5, Section 10.6, and<br>Section 10.7. |